Instruction scheduling optimization method for coarse-grained reconfigurable architecture complier

An instruction scheduling and optimization method technology, applied in the instruction scheduling optimization of the coarse-grained reconfigurable architecture compiler, the compilation process of the reconfigurable processor, and the parallel computing field, which can solve the problems affecting the computing performance, long compilation time, lack of data Analysis and optimization of flow graph systems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings.

[0029] Based on the analysis of the present situation, the present invention proposes a brand-new instruction scheduling optimization method for a coarse-grained reconfigurable compiler, which is specifically developed from the following two aspects.

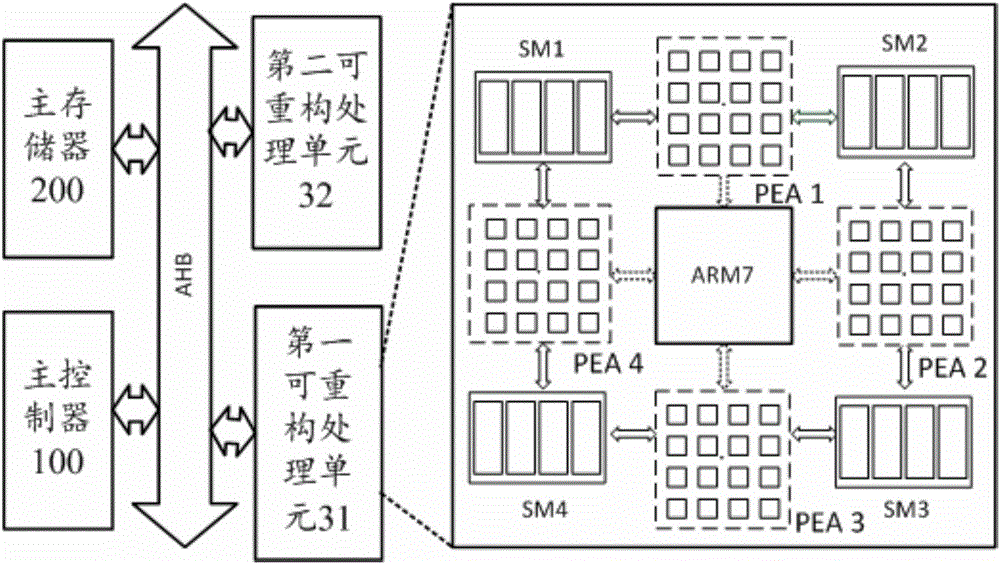

[0030] 1. Configure a multi-layer heterogeneous coarse-grained reconfigurable processor architecture that follows global synchronization

[0031] The present invention adopts a coarse-grained reconfigurable processor with a new architecture, which includes a three-layer heterogeneous structure such as figure 1 shown.

[0032] First, the multi-layer heterogeneous coarse-grained reconfigurable processor architecture includes: a single main controller 100 (for example, the main controller is impleme...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More