Chip packaging structure and manufacture method thereof

A technology of chip packaging structure and manufacturing method, which is applied in the fields of printed circuit manufacturing, semiconductor/solid-state device manufacturing, circuit heating device, etc., can solve problems such as occupied volume and design restrictions, and achieve improved reliability, reduced stress, and improved heat dissipation effect of effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

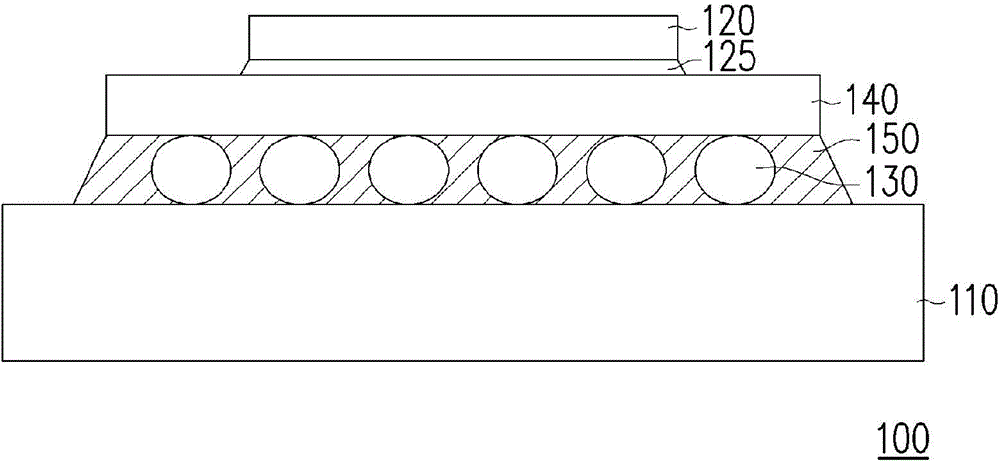

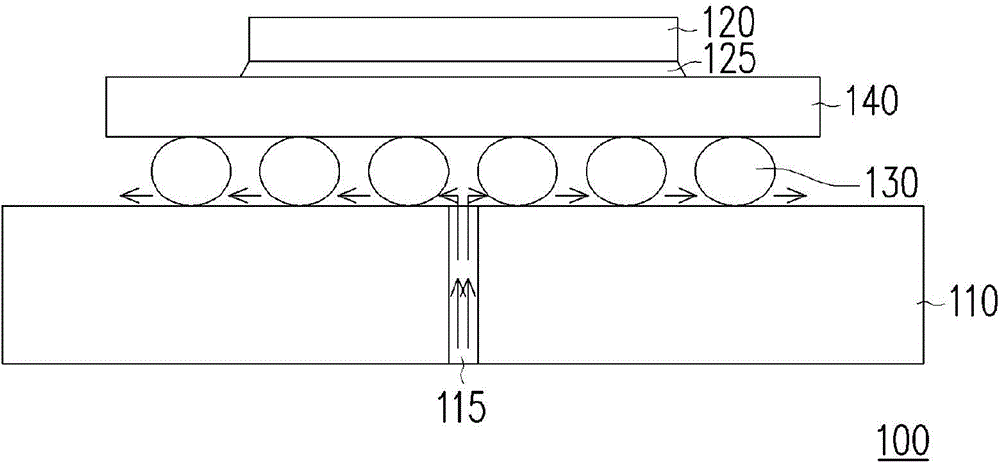

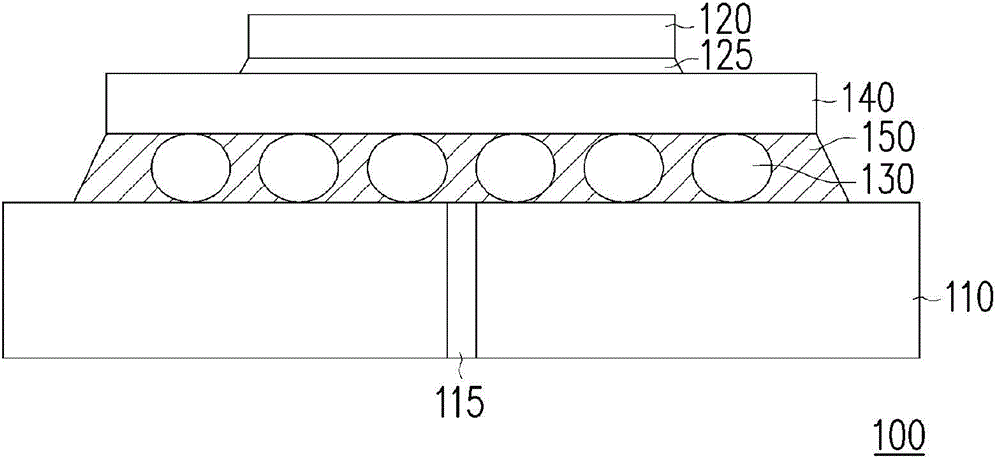

[0047] figure 1 is a schematic diagram of a chip package structure according to an embodiment of the present invention. Please refer to figure 1The chip packaging structure 100 includes a substrate 110 , at least one chip 120 , a plurality of conductive bumps 130 and an insulating and thermally conductive material 150 . In this embodiment, the chip 120 is disposed on the chip carrier 140 , and the chip carrier 140 is disposed on the substrate 110 . In addition, the conductive bump 130 is disposed between the substrate 110 and the chip carrier 140 to electrically connect the substrate 110 and the chip 120 . Furthermore, the insulating and thermally conductive material 150 is disposed between the conductive bumps 130 and covers the conductive bumps 130 . In this embodiment, the substrate 110 is, for example, a printed circuit board (PCB) or a flexible circuit board (flexible circuit board). The conductive bumps 130 are, for example, solder bumps, copper pillars, copper stud ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More