FPGA-based deep convolution neural network realizing method

A technology of deep convolution and implementation method, applied in biological neural network model, physical implementation, speech analysis, etc., can solve the problems of low efficiency and high power consumption, achieve high efficiency, low power consumption, and improve algorithm efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

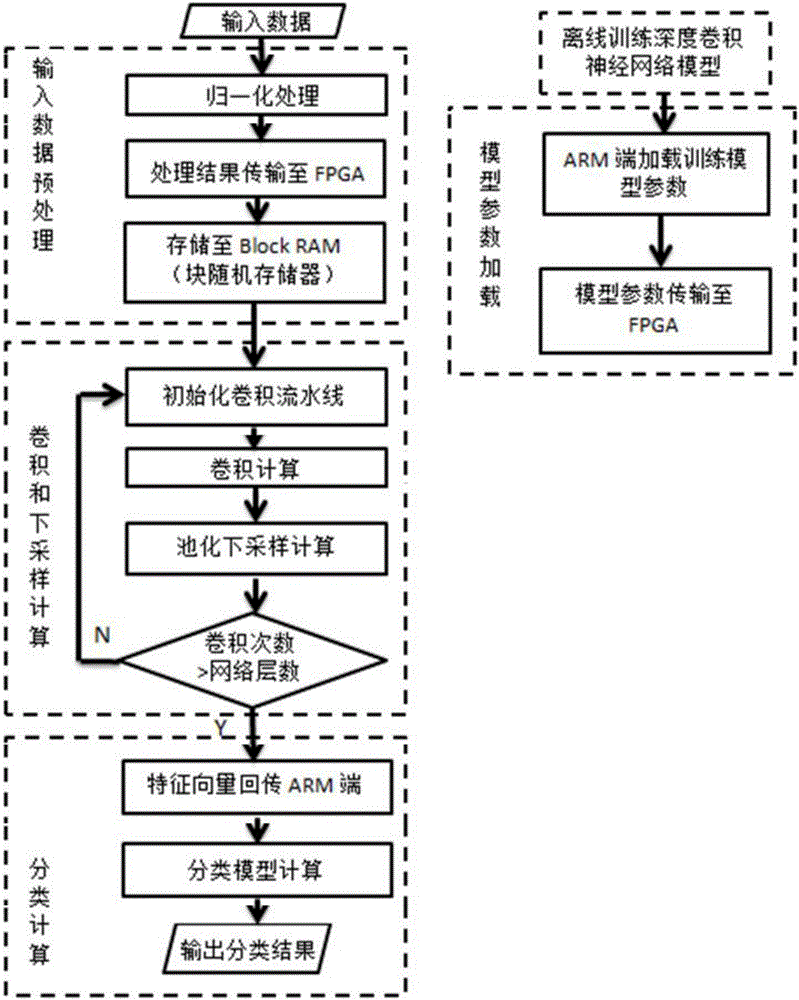

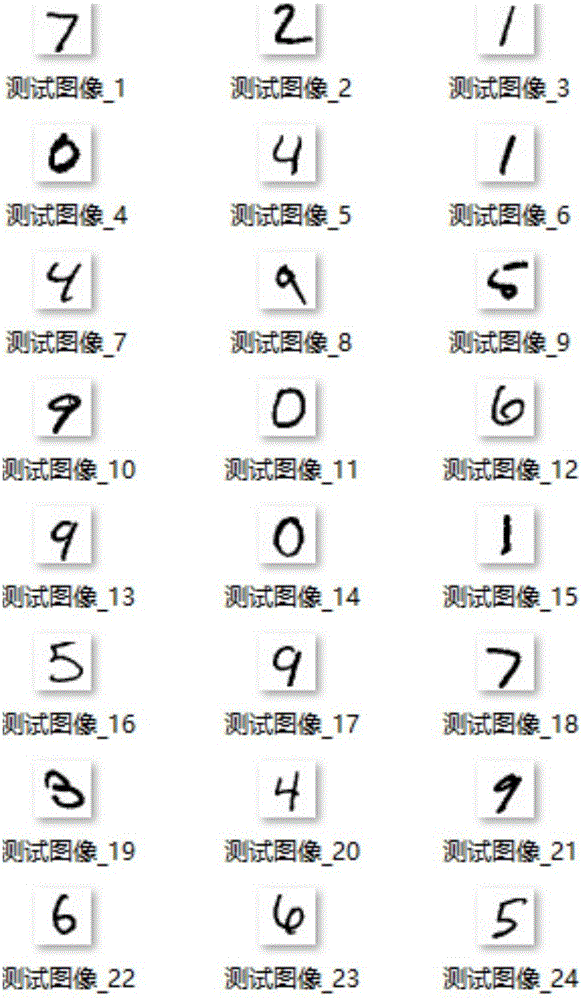

[0073] The method of the present invention is explained below in conjunction with the accompanying drawings, and the specific implementation of the handwritten character recognition algorithm is realized on the FPGA hardware platform using a deep convolutional neural network model. (The deep convolutional neural network model consists of the input layer I, the first convolutional layer C1, the first downsampling layer S1, the second convolutional layer C2, the second downsampling layer S2 and the full connection layer Softmax The input image size is 28×28, the first convolutional layer contains a convolution kernel with a size of 5×5, and the second convolutional layer contains three convolution kernels with a size of 5×5).

[0074] The specific operation steps of the handwritten character recognition algorithm implemented on the FPGA using the deep convolutional neural network model are as follows: figure 1 shown.

[0075] 1. Load the trained model parameters

[0076] First...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More