Bidirectional FIFO and bus bridging system

A dual-port, reverser technology, applied in the field of communication, can solve the problem of consuming large hardware resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments of the present invention. It should be understood that the present invention is not limited to the specific embodiments described below, and those skilled in the art may make various variations or modifications within the scope of the appended claims.

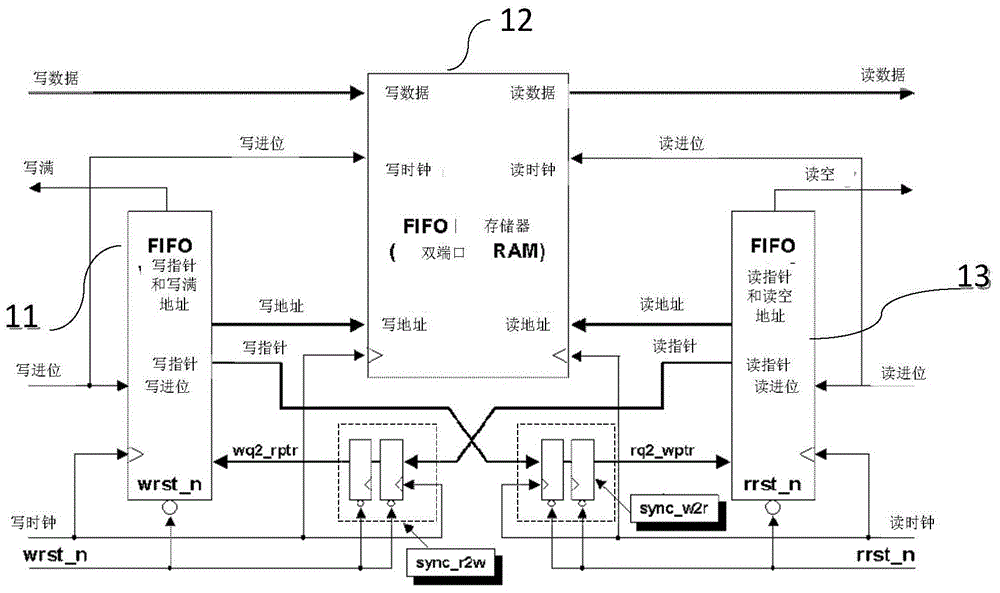

[0031] The present invention provides a kind of new two-way FIFO, and this structure comprises:

[0032] Dual-port random access memory, the first set of ports and the second set of ports, wherein,

[0033] The first set of ports includes a first clock signal input end, a first enable signal input end, a first read / write control signal input end, a first operation address input end, a first data input end, and a first data output end;

[0034] The second set of ports includes a second clock signal input end, a second enable signal input end, a second read / write control signal input end, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com