FPGA system having Camera Link interface

A technology of interface and output port, which is applied in the field of FPGA system, can solve the problems of PLL resource consumption and poor portability, and achieve the effect of saving resources, avoiding phase inconsistency, and good scalability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] In order to enable those skilled in the art to better understand the technical solutions in the present invention, the technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the drawings in the embodiments of the present invention. Obviously, the described The embodiments are only some of the embodiments of the present invention, not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts shall fall within the protection scope of the present invention.

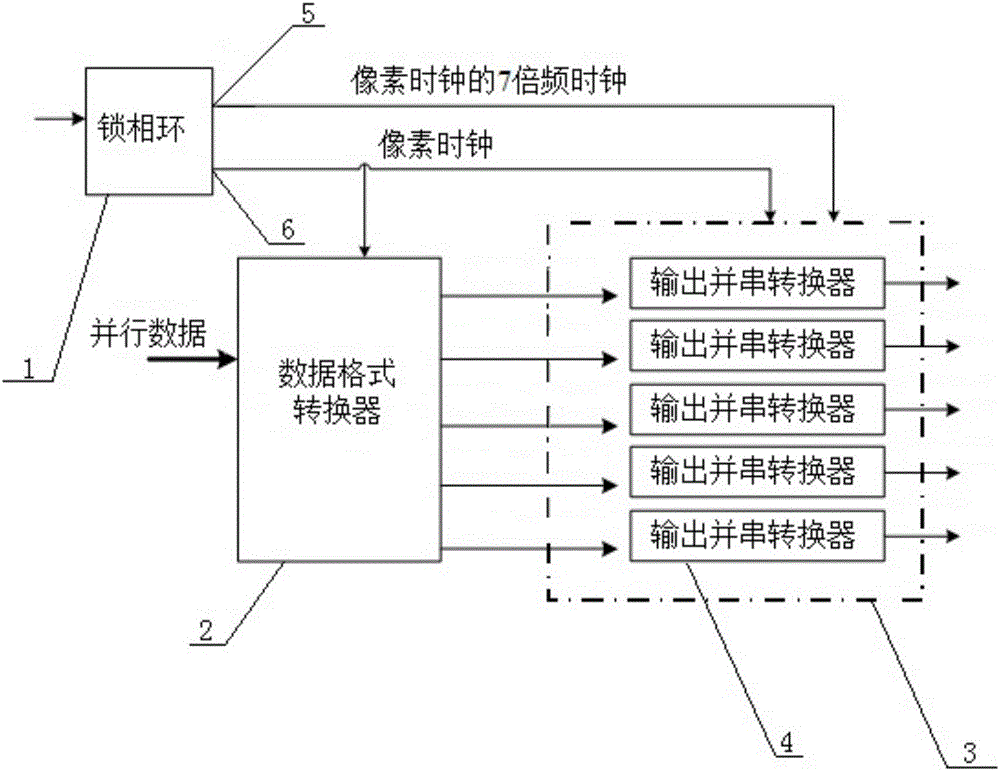

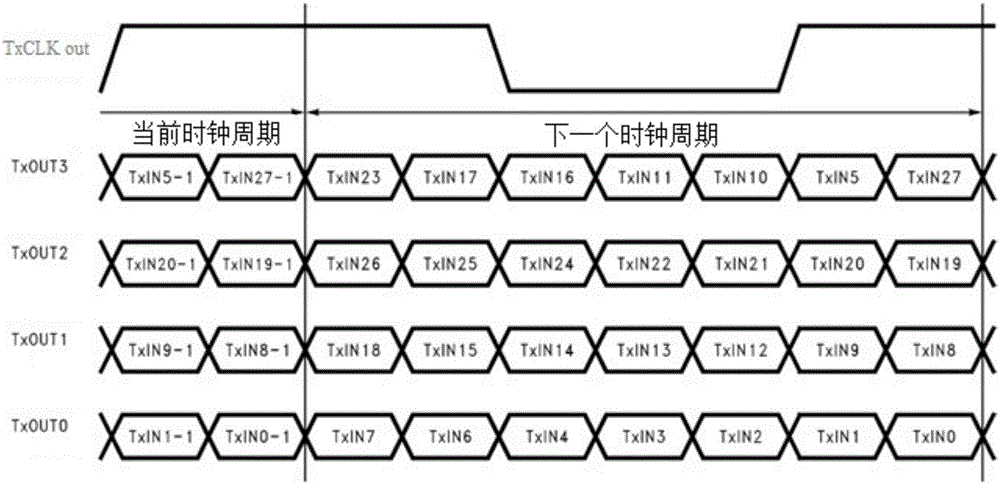

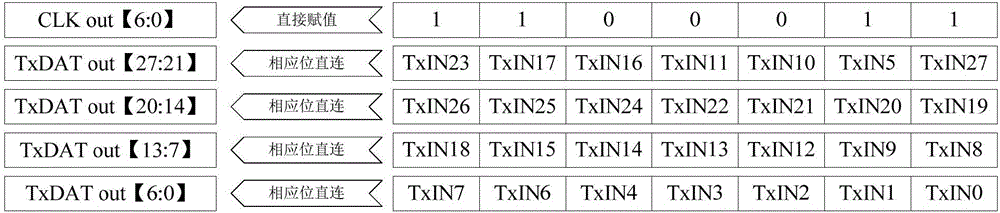

[0024]The present invention provides a kind of FPGA system with Camera Link interface, in this FPGA system, be provided with PLL, data format converter and output parallel-to-serial conversion device, wherein, PLL is used for generating pixel clock and input preset clock wherein The pixel clock is a 7-multiplier clock, and the data form...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More