Multi-ADC high-speed crossing sampling calibration device and method

A calibration device and calibration method technology, applied in the direction of analog/digital conversion calibration/testing, electrical components, code conversion, etc., can solve the problems of reconstruction waveform distortion, jitter increase, and the reduction of the analog bandwidth of the whole machine, so as to improve the calibration efficiency , the effect of reducing the uncertainty problem

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

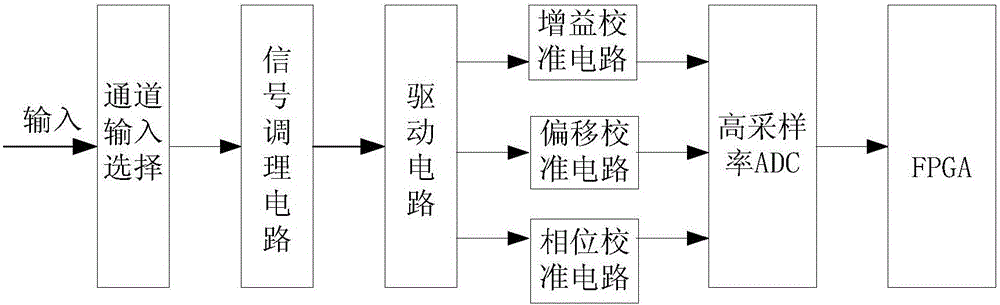

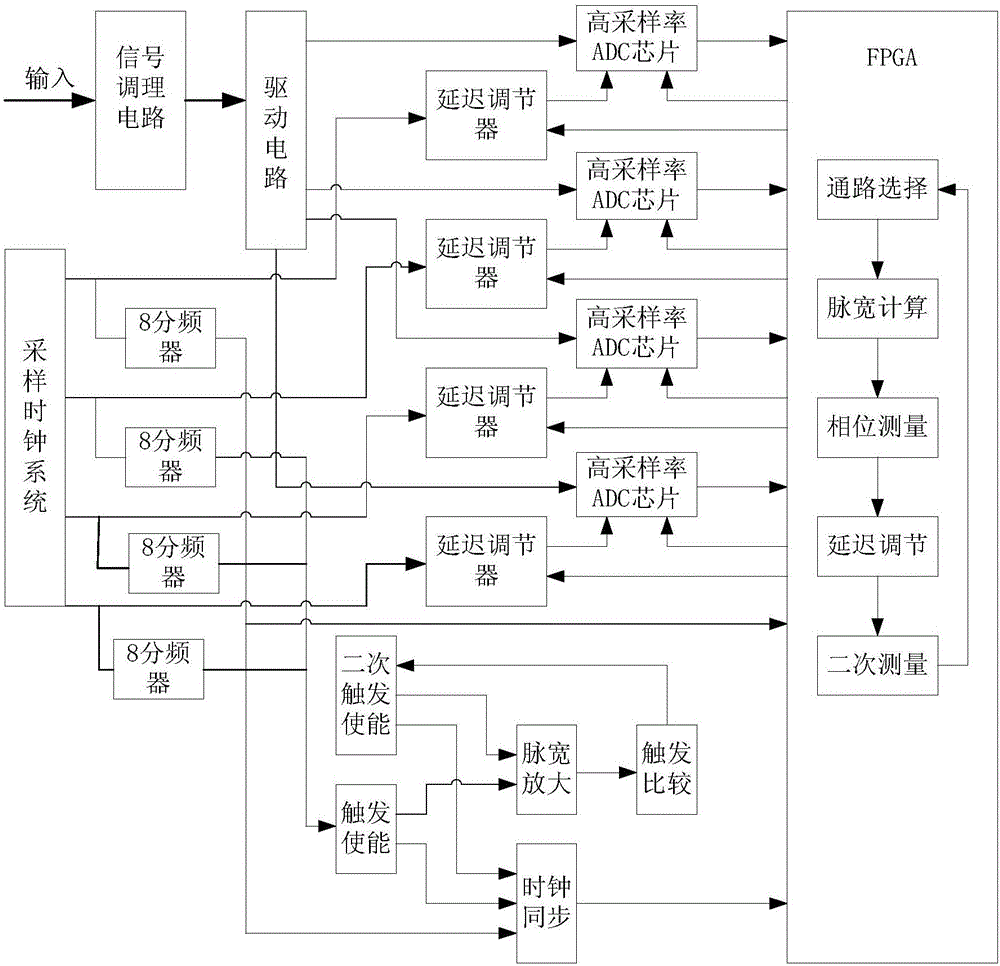

[0039] combine Figure 1 to Figure 7 , a multi-ADC high-speed cross-sampling calibration device, including a channel input selection module, the channel input selection module is connected with a signal conditioning circuit, the signal conditioning circuit is connected with a driving circuit, and the driving circuit is respectively connected with a phase calibration circuit, a gain calibration circuit and an offset The calibration circuit, the phase calibration circuit, the gain calibration circuit and the offset calibration circuit are all connected with a high sampling rate ADC module, and the high sampling rate ADC module is connected with an FPGA, and the FPGA is a field programmable gate array, wherein the high sampling rate ADC module includes Four high sampling rate ADC chips.

[0040]The phase calibration circuit includes a sampling clock system. The sampling clock system outputs four 1.25GHz sampling clocks. The four 1.25GHz sampling clocks are respectively connected ...

Embodiment 2

[0044] The calibration method of a multi-ADC high-speed cross-sampling calibration device in the above-mentioned embodiment 1 includes a phase calibration method, a gain calibration method and an offset calibration method.

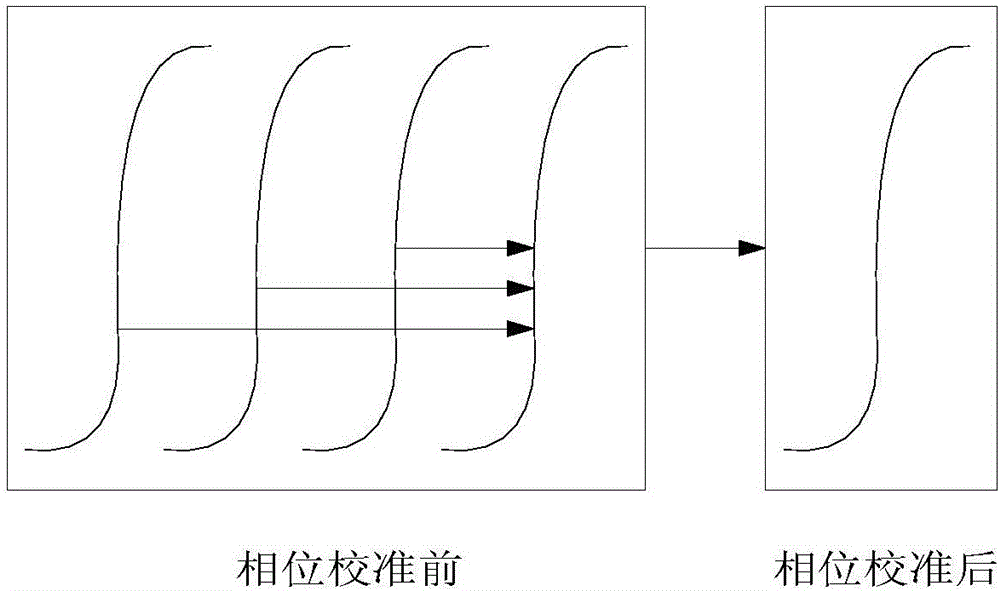

[0045] Among them, the phase calibration method uses DDR clock sampling, and outputs four-phase 1.25GHz sampling clocks with a difference of 45 degrees. One channel is used as the reference, and the other three channels are respectively connected with delay regulators to adjust the delay time, so that the clock difference between two adjacent channels is 100 ps, and the four ADCs are alternately sampled to obtain an equivalent sampling rate of 10GSa / s. Use the first frequency-divided clock as the interpolation clock, and solve the problem of high-precision testing by amplifying the difference twice. The phase measurement results are used for coarse adjustment and fine adjustment. The coarse adjustment adjusts the delay regulator, and the fine adjustment a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More