Low-temperature polysilicon array substrate and manufacturing method thereof

A technology of low-temperature polysilicon and manufacturing methods, applied to semiconductor devices, electrical components, circuits, etc., can solve problems such as increased process complexity and uneven threshold voltage of polysilicon thin film transistors, and achieve the effect of increasing process complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

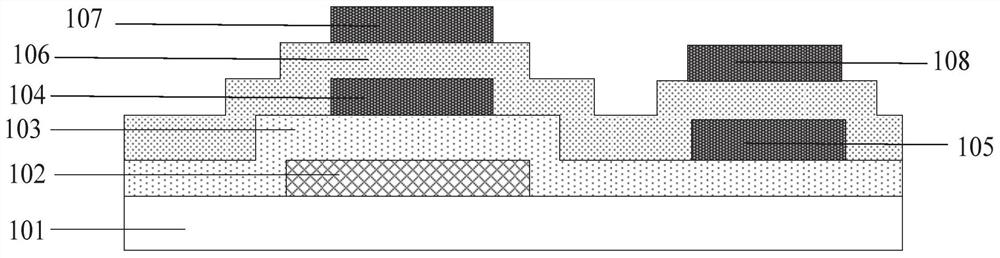

[0024] This embodiment provides a low-temperature polysilicon array substrate, figure 1 The structure of the low temperature polysilicon array substrate according to the embodiment of the present invention is shown.

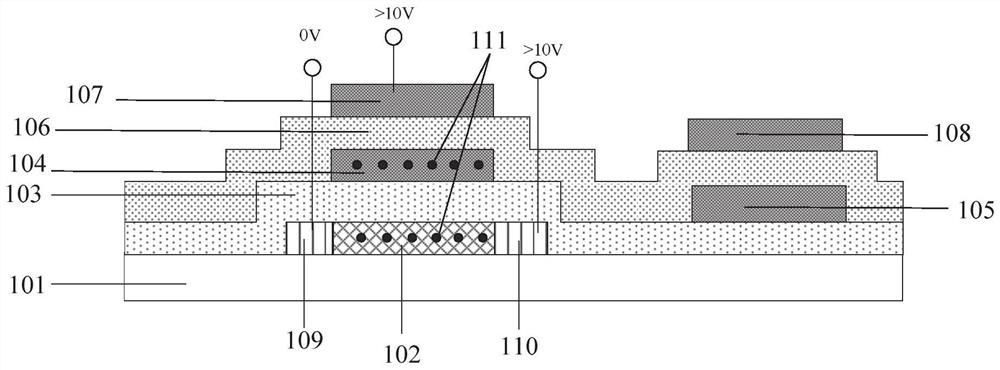

[0025] Such as figure 1 As shown, the low-temperature polysilicon array substrate according to this embodiment includes: a substrate 101; an active layer 102 disposed on the substrate 101; a first gate insulating layer 103 disposed on the active layer 102, and the first insulating layer 103 covers The active layer 102 extends on the substrate 101; the first gate layer 104 formed on the first insulating layer 103, the first gate layer 104 is above the active layer 102, and also includes on the first insulating layer 103 The first capacitive electrode layer 105, the first capacitive electrode layer 105 is formed on the side of the substrate 101 away from the active layer 102; the second gate insulating layer 106 covers the first gate layer 104 and the first capaci...

Embodiment 2

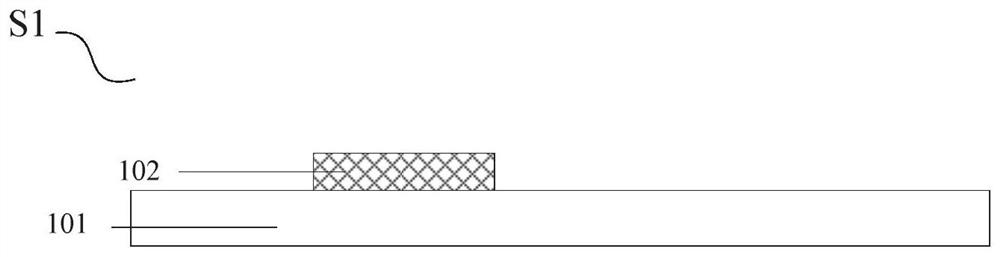

[0031] This embodiment provides a method for manufacturing a low-temperature polysilicon array substrate, which is used to manufacture the low-temperature polysilicon array substrate described in Embodiment 1. Figure 3 to Figure 8 A process flow chart of manufacturing a low-temperature polysilicon array substrate according to an embodiment of the present invention is shown.

[0032] Such as Figure 3 to Figure 8 As shown, the method for manufacturing a polysilicon array substrate according to this embodiment includes the following steps.

[0033] Such as image 3 As shown, first, in step S1, a transparent substrate such as glass that has been cleaned in advance is provided as the substrate 101, and a buffer layer including silicon oxide, silicon nitride, or a stack of the two can be formed on the substrate 101 to prevent the transparent substrate from The impurity of metal ions diffuses into the active layer and affects the working characteristics of TFT. Or a flexible subst...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More