Via hole chamfer prediction method

A prediction method and via technology, which is applied in the direction of semiconductor/solid-state device testing/measurement, electrical components, circuits, etc., can solve the problems of long time consumption and high cost, and achieve the effect of short time consumption, low cost and simple judgment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] In order to make the purpose, technical solutions and advantages of the present invention clearer, the following will further describe in detail the embodiments of the present invention in conjunction with the accompanying drawings.

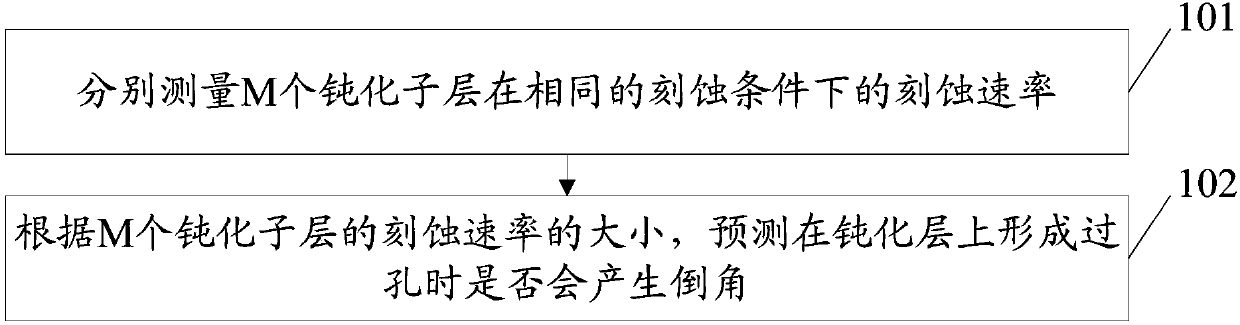

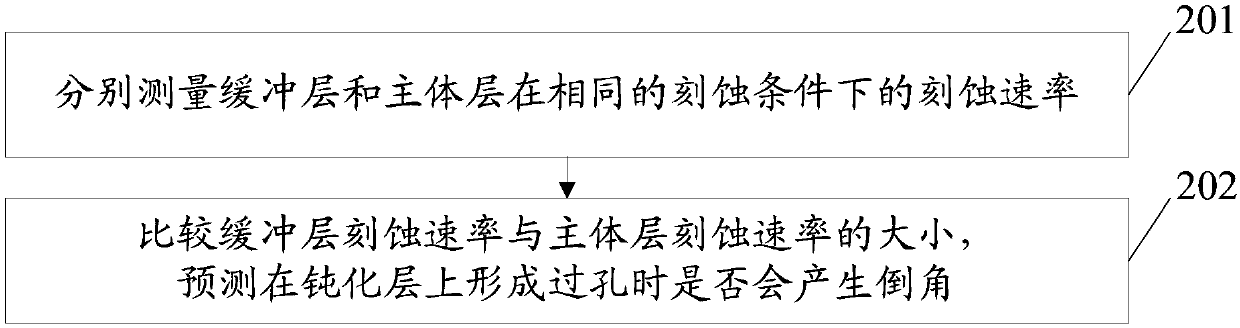

[0026] figure 1 It is a flow chart of a via hole chamfer prediction method provided by an embodiment of the present invention, see figure 1 , the method includes:

[0027] Step 101: Measure the etching rates of M passivation sub-layers under the same etching conditions, M>1, and M is a positive integer.

[0028] In the embodiment of the present invention, the etching rate measurement method of each passivation sub-layer in the M passivation sub-layers is the same, and measuring the etching rate of each passivation sub-layer may include: forming a passivation sub-layer on the substrate layer, and measure the initial film thickness of the passivation sub-layer; etch the passivation sub-layer, and measure the final film thickness of the pas...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More