Array substrate, manufacturing method thereof and display device

An array substrate and manufacturing method technology, applied in the display field, can solve the problems of increasing the parasitic capacitance of gate lines and data lines, reducing the aperture ratio of products, etc., and achieve the effects of reducing parasitic capacitance, ensuring aperture ratio, and reducing line resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] In order for those skilled in the art to better understand the technical solution of the present invention, the array substrate, its manufacturing method, and display device provided by the present invention will be described in detail below with reference to the accompanying drawings.

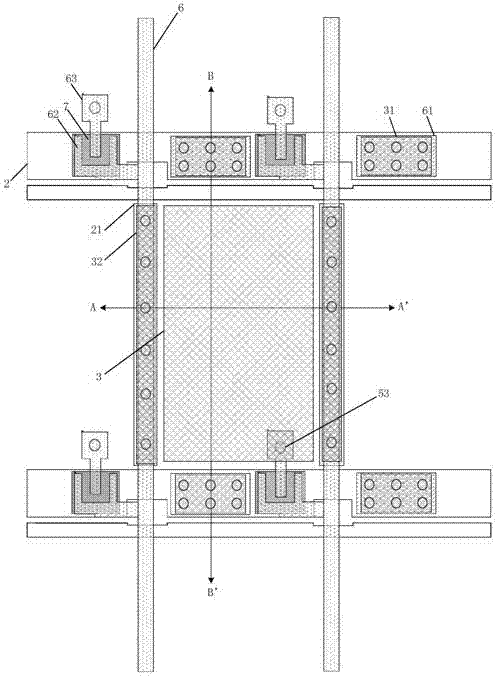

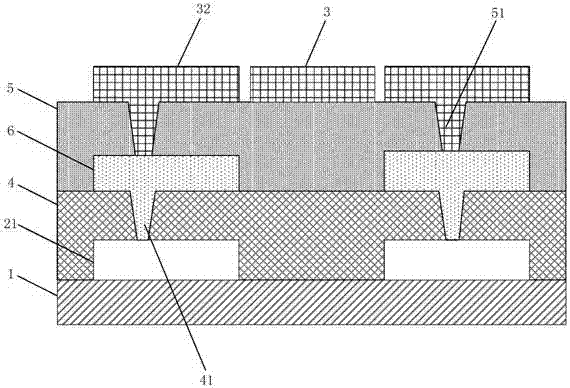

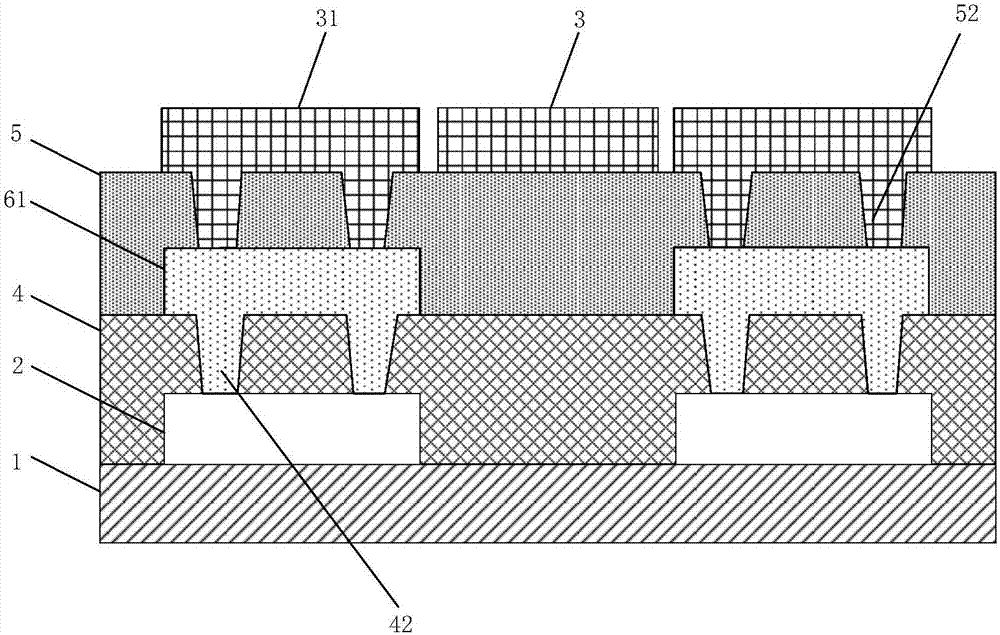

[0030] figure 1 It is a schematic structural diagram of an array substrate provided in Embodiment 1 of the present invention, figure 2 for figure 1 The A-A' cross-sectional view of the array substrate in image 3 for figure 1 The B-B' cross-sectional view of the medium array substrate, such as Figure 1 to Figure 3 As shown, the array substrate includes a base substrate 1, a signal line on the base substrate 1 and at least one connection pattern, and the connection pattern is connected in parallel with the signal line.

[0031] In this embodiment, the signal lines include gate lines or data lines. The number of signal lines is plural. Wherein, preferably, the multiple signal line...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More