High-speed custom floating point divider of complex numbers

A floating-point complex number and self-defined technology, which is applied in the direction of instruments, electrical digital data processing, digital data processing components, etc., can solve the problem of consuming large resources, achieve overall performance enhancement, fast calculation, balance algorithm accuracy and resource consumption Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

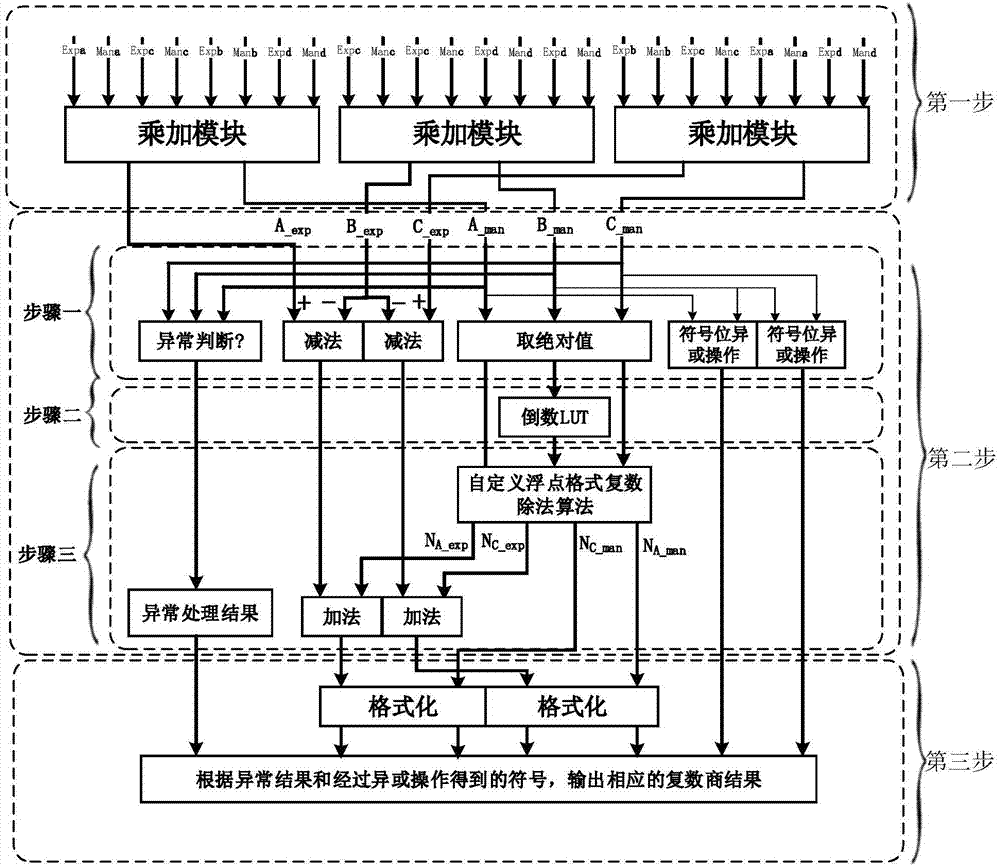

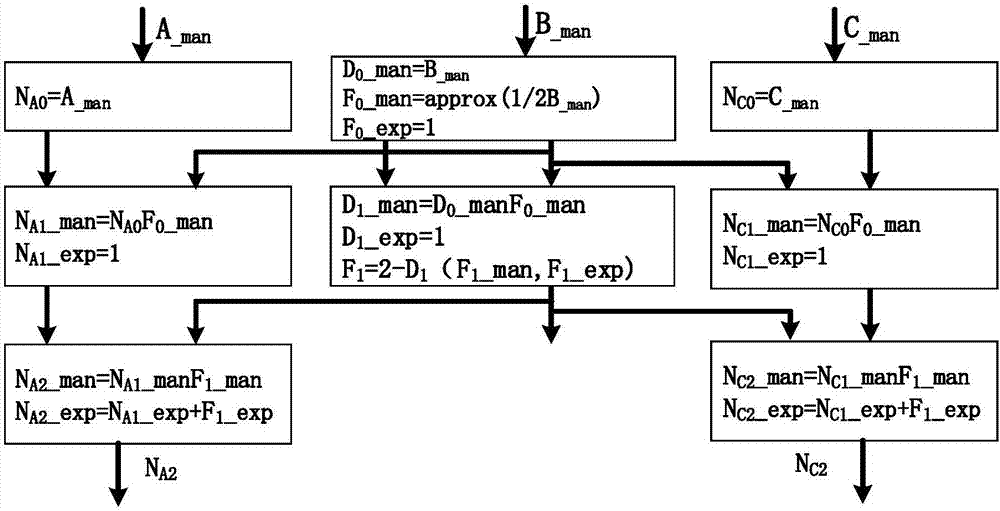

[0040] The following uses a specific example of a 64-bit custom floating-point format complex number divider to illustrate the implementation of the present invention, wherein the bit width of the exponent part is 12, and the bit width of the mantissa part is 52. figure 1 It is an overall flowchart of the present invention, and the whole flow process can be divided into three major steps:

[0041] In the first step, implement A, B, and C using a custom floating-point multiply-accumulate unit:

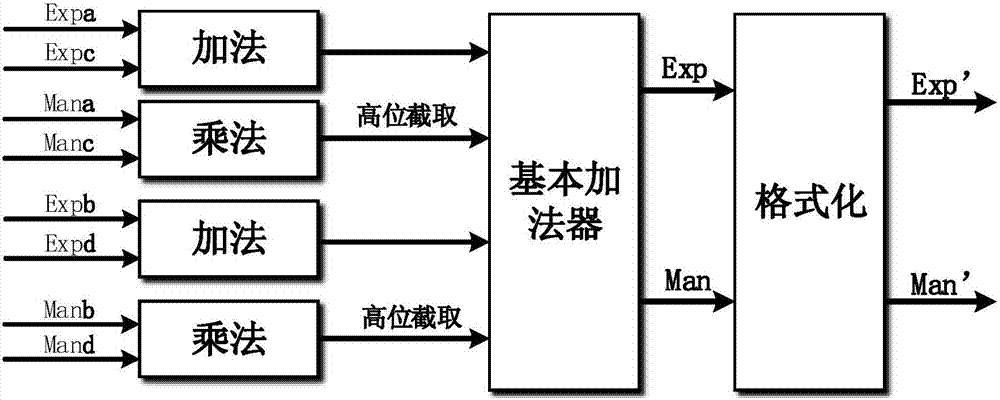

[0042] figure 2 It is an illustration of A=a×c+b×d. a=Man(a)×2 Exp(a) ,b=Man(b)×2 Exp(b) ,c=Man(c)×2 Exp(c) ,d=Man(d)×2 Exp(d) .

[0043] After multiplying the mantissa, the high bit of the obtained product is intercepted to 52 bits, and the obtained result and the exponent part are used as the input of the basic adder at the same time, that is, the bit width of the mantissa part of the basic adder is 52, and the bit width of the exponent part for 12. Then perform high-order in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com