Information processing method and electronic equipment

An electronic device and processor technology, applied in the computer field, can solve the problems of NVMe storage devices that cannot be managed by SAS controllers, and that there are no NVMe storage devices.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

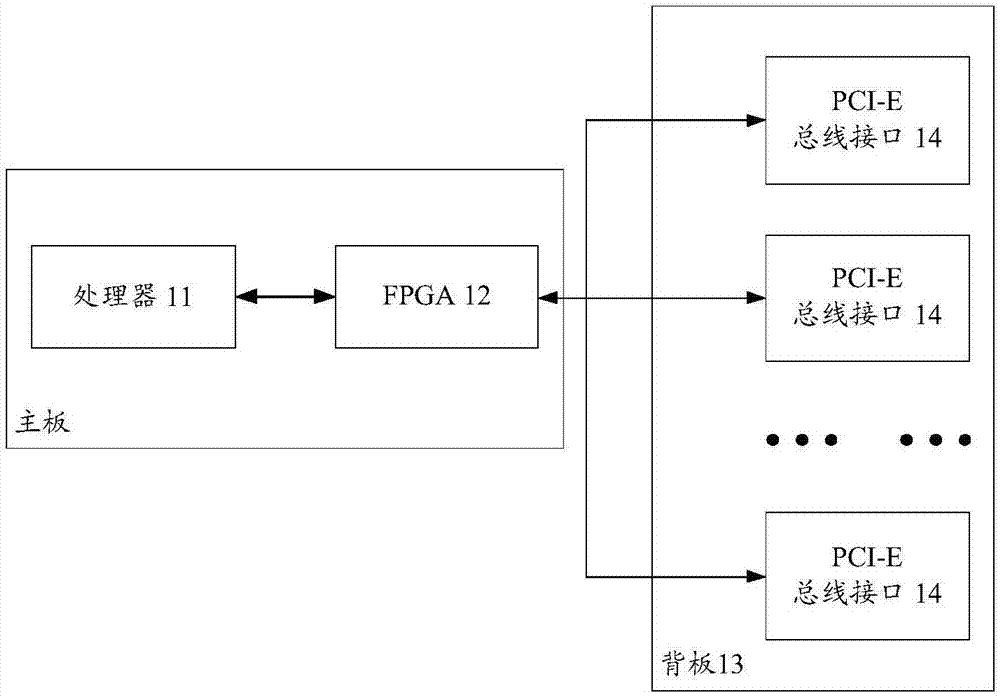

[0029] Picture 1-1 It is a schematic diagram of the structure of the electronic device in the embodiment of the present invention, see Picture 1-1 As shown, the electronic device 10 includes: a processor 11, an FPGA 12, a backplane 13, at least one PCI-E bus interface 14 arranged on the backplane 13;

[0030] Here, the above-mentioned processor and FPGA are arranged on the motherboard of the electronic equipment; the above-mentioned backplane is provided with at least one backplane slot (Bay), and at least one PCI-E bus interface is provided on each backplane slot, and the PCI-E The E-bus interface connects to NVMe storage devices.

[0031] The information processing method according to the embodiment of the present invention will be described below in conjunction with the above-mentioned electronic device.

[0032] figure 2 It is a schematic flow chart of the information processing method in the embodiment of the present invention, see figure 2 As shown, the method incl...

Embodiment 2

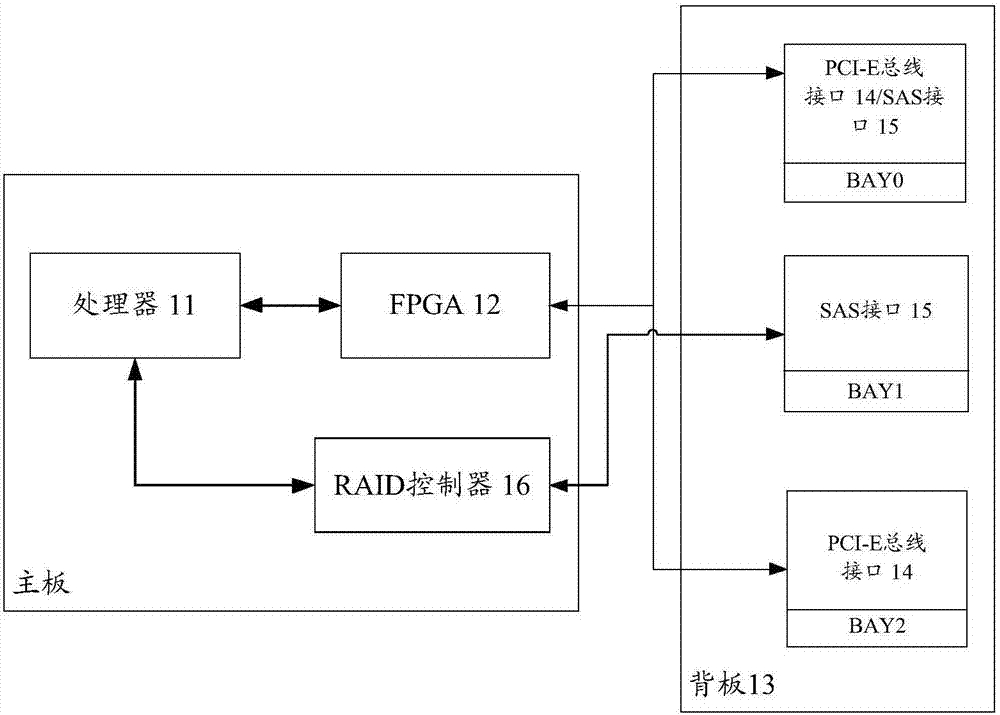

[0046] Based on the foregoing embodiments, in practical applications, Figure 1-2 It is a schematic diagram of the structure of the electronic equipment in the embodiment of the present invention Figure II , see Figure 1-2 As shown, in addition to being provided with a PCI-E bus interface 14 on the backplane slot, a SAS interface 15 can also be arranged at the same time, and the PCI-E bus interface 14 and the SAS interface 15 can be set on the same backplane slot, or can be Set in different backplane slots. When numbering the bus slots, no matter what kind of interface they are, their corresponding Slot IDs are numbered sequentially.

[0047] still see Figure 1-2 As shown, in order to manage the SAS storage device, the electronic device further includes: a RAID controller 16 .

[0048] image 3 It is a schematic flow chart of the information processing method in the embodiment of the present invention Figure II , see image 3 As shown, the method includes:

[0049]...

Embodiment 3

[0061] Based on the foregoing embodiments, the information processing method on the processor side will be described below.

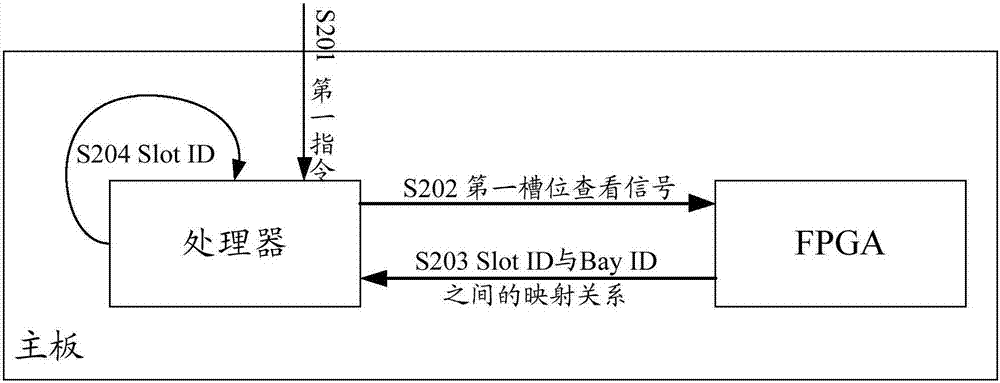

[0062] Figure 4 It is a schematic flow chart of the processor-side information processing method in the embodiment of the present invention, see Figure 4 As shown, the method includes:

[0063] S401: Obtain a first instruction;

[0064] Wherein, the first instruction is used to obtain the bus slot number corresponding to the PCI-E bus interface on the backplane;

[0065] S402: Execute the first instruction, and send the first slot check signal to the FPGA;

[0066] S403: Receive the mapping relationship between the pre-stored Slot ID and Bay ID from the FPGA;

[0067] Among them, the mapping relationship is sent by the FPGA in response to the first slot view signal;

[0068] S404: Obtain the Slot ID corresponding to the backplane slot where the PCI-E bus interface is located according to the mapping relationship.

[0069] In other embodiments of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More