Shift register unit, driving method thereof, display panel and display device

A technology for shifting register units and potentials, which is applied in information storage, static memory, static indicators, etc., and can solve problems such as circuit instability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

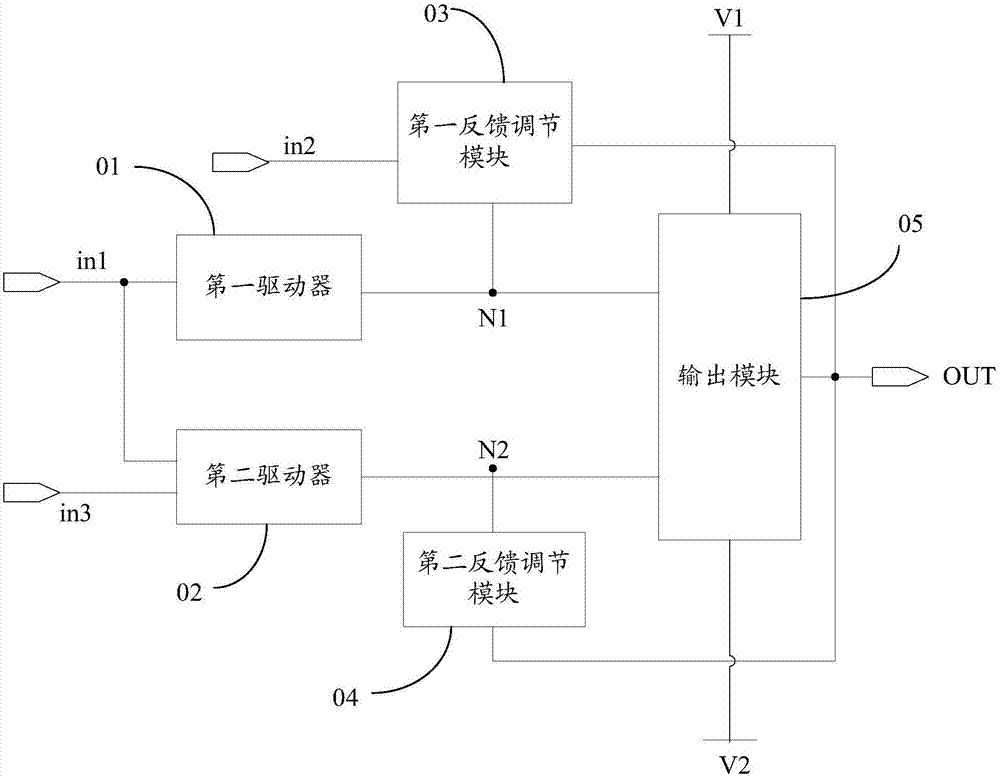

Method used

Image

Examples

example 1

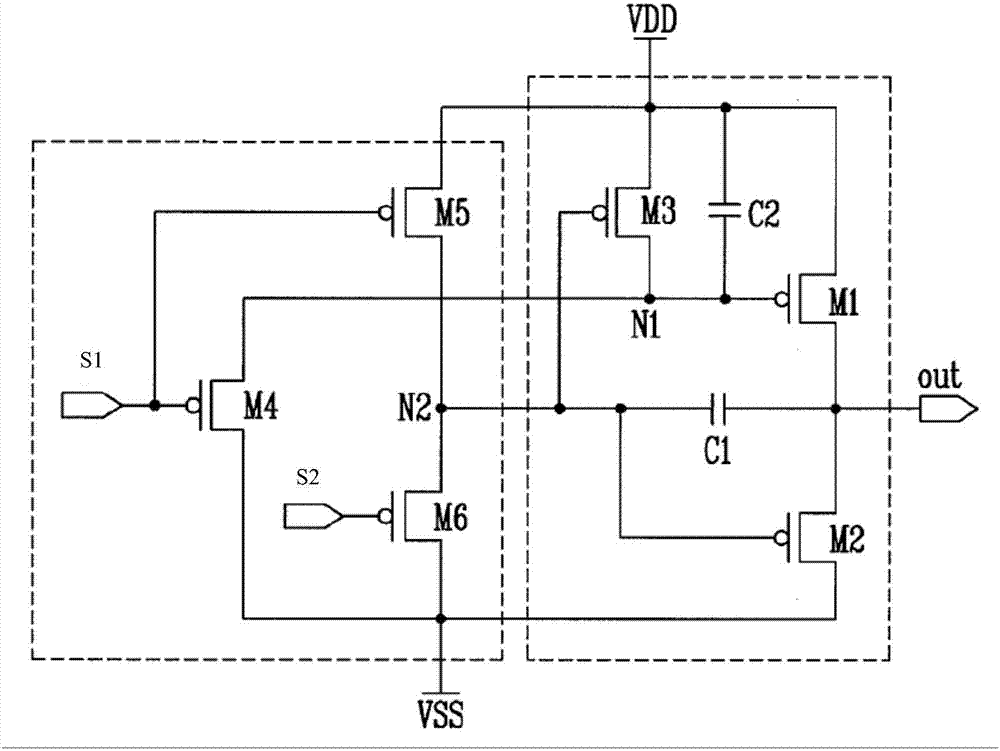

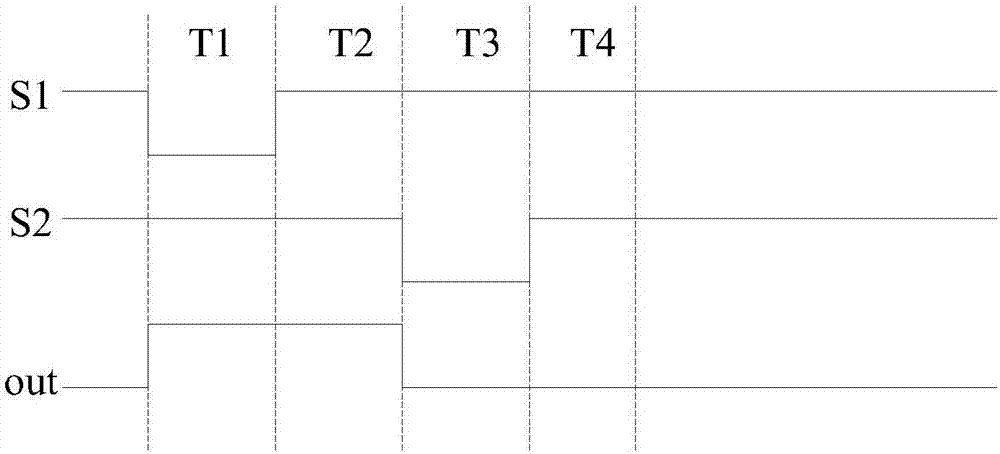

[0101] by image 3 Take the shift register unit shown as an example, all transistors in the shift register unit are P-type transistors, and the corresponding input and output timings are as follows: Figure 7 as shown, Figure 7 An input and output timing diagram corresponding to the shift register unit provided by the embodiment of the present invention; specifically, select such as Figure 7 The four stages T1, T2, T3 and T4 in the input timing diagram shown.

[0102] In the T1 stage, S1=0, S2=1, and S3=1.

[0103] Such as Figure 8a as shown, Figure 8a A schematic diagram of the working state of each transistor of the shift register unit in the T1 stage provided for the embodiment of the present invention; since S1=0, the first transistor M1 and the second transistor M2 are turned on. Since S3=1, the third transistor M3 is turned off. The high potential signal of the first signal terminal V1 is transmitted to the second node N2 through the second transistor M2, so th...

example 2

[0115] by Figure 5 Take the shift register unit shown as an example, all transistors in the shift register unit are N-type transistors, and the corresponding input and output timing is as follows Figure 9 as shown, Figure 9 Another input and output timing diagram corresponding to the shift register unit provided by the embodiment of the present invention; specifically, select such as Figure 9 The four stages T1, T2, T3 and T4 in the input timing diagram shown.

[0116] In the T1 stage, S1=1, S3=0.

[0117] Since S1=1, the first transistor M1 and the second transistor M2 are turned on. Since S3=0, the third transistor M3 is turned off. The low potential signal of the first signal terminal V1 is transmitted to the second node N2 through the second transistor M2, so the potential of the second node N2 is low, and the seventh transistor M7 is turned off. The high potential signal of the second signal terminal V2 is transmitted to the first node N1 through the first transi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More