Impedance test method based on de-embedding

An impedance test and de-embedding technology, applied in the field of testing, can solve the problems of long cycle time, high price, and decreased design efficiency of chip test probes, and achieve the effect of avoiding test limitations, reducing costs, and reducing cycles.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings, but the present invention can be implemented in many different ways defined and covered by the claims.

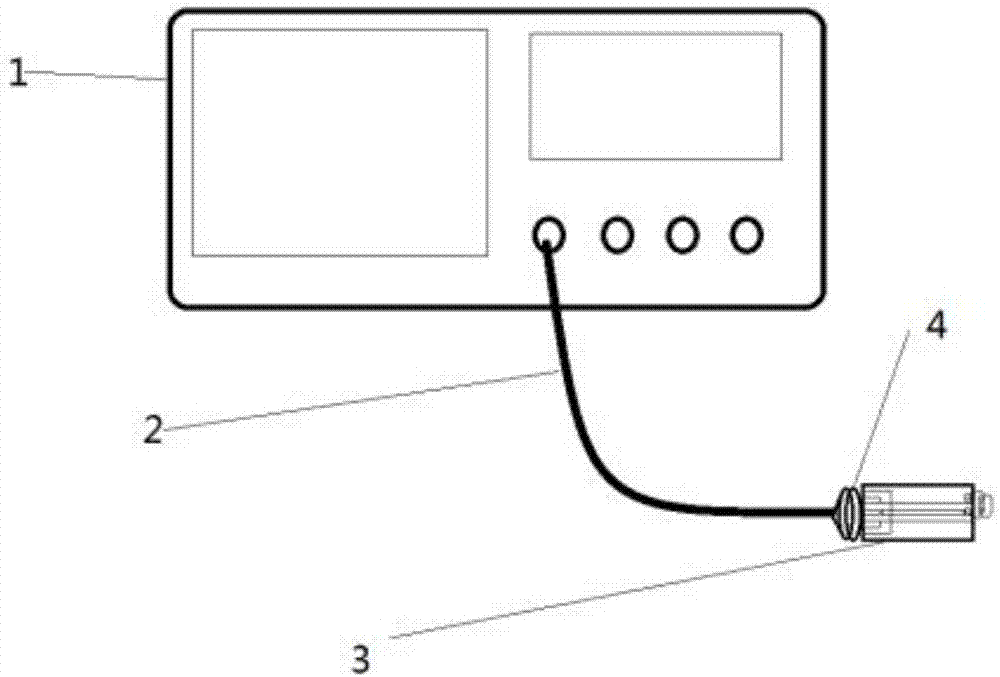

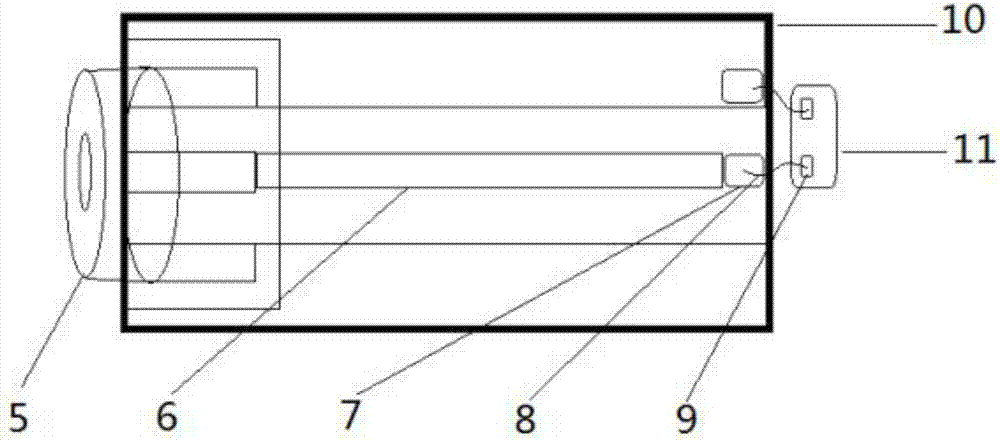

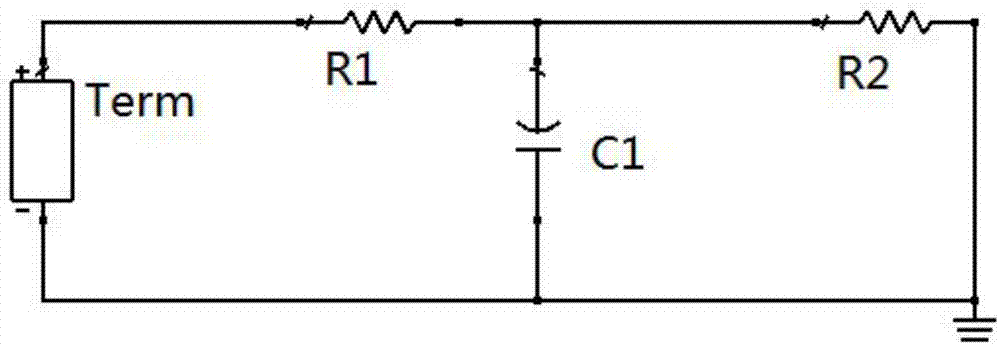

[0033] Such as Figure 1-9 As shown, among them, 1-vector network analyzer, 2-transmission cable, 3-tested sample, 4-cable conversion interface, 5-SMA adapter A, 6-video transmission line, 7-PCB binding PAD, 8-chip bonding wire, 9-the tested chip is bound to the PAD, 10-PAB test circuit board, 11-the chip to be tested, 12-SMA adapter B, 13-microstrip lines of different lengths.

[0034] An impedance testing method in a de-embedding manner, comprising the following steps:

[0035] (1) Hardware preparation:

[0036] PCB board for bonding required for testing;

[0037] (2) Consistency measurement:

[0038] Measure the COB of the bonded chip, record and compare its S11 file, and observe its consistency; according to the label sensitivity provided ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More