Neural network accelerator for bit width partitioning and implementation method of neural network accelerator

A technology of neural network and implementation method, which is applied in the field of computer vision, can solve the problem of sacrificing hardware area indicators, and achieve the effects of increasing DSP utilization, increasing resource utilization efficiency, and improving computing throughput

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

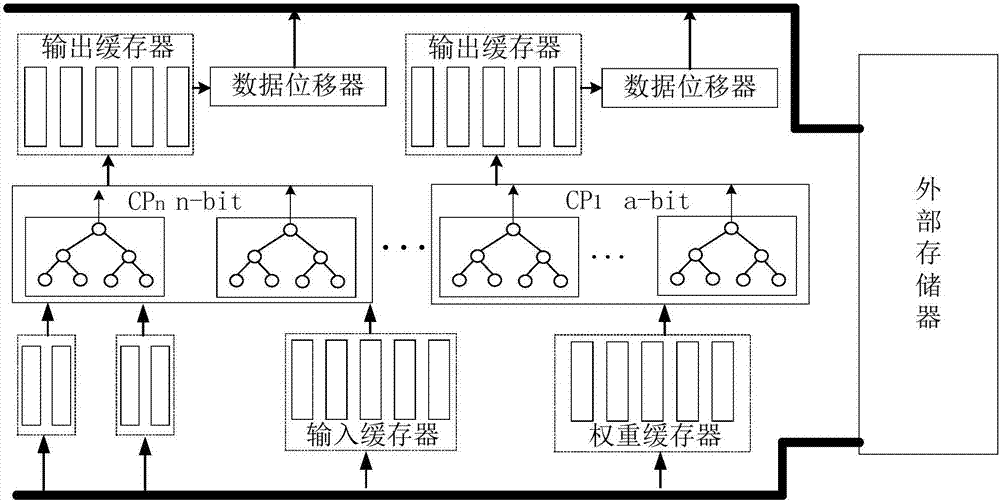

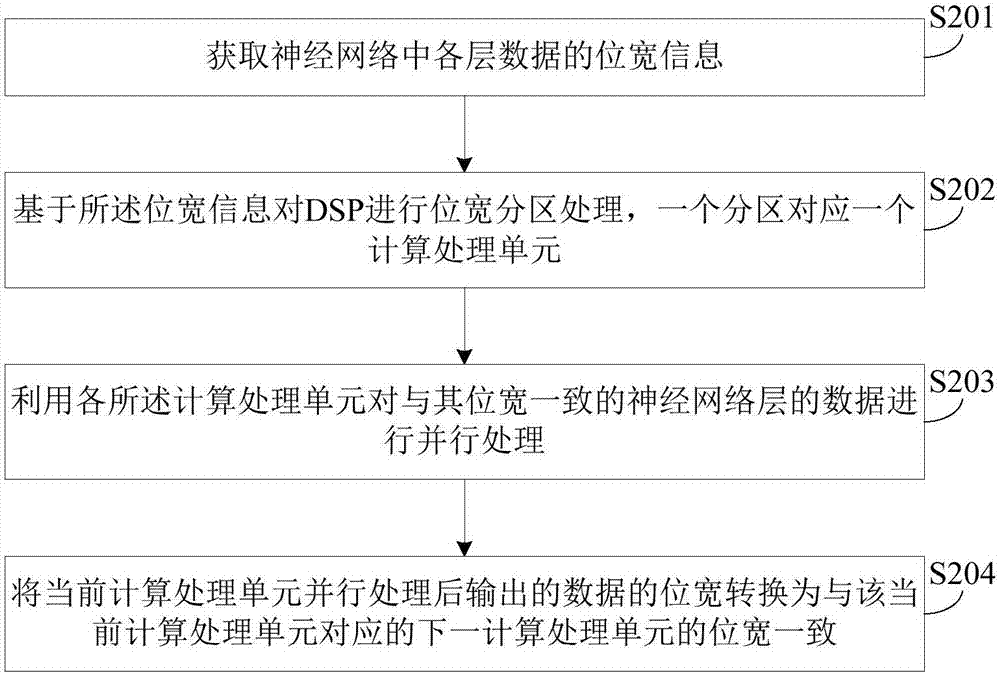

[0036] In the prior art, mainstream CNN accelerators use a single bit-width computing processing unit (CP) to iteratively calculate each layer of CNN. However, due to the different data bit width requirements of each layer of CNN, such a design will lead to a lot of problems. Big waste of resources. Based on this, the embodiment of the present invention provides a neural network accelerator for bit width partitioning and its implementation method. According to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More