Memory device, memory system and memory control method

A technology of a memory system and a memory unit, which is applied in static memory, digital memory information, information storage, etc., and can solve the problems of increased floor area and difficult expansion of capacity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0053] Hereinafter, some embodiments of the present disclosure are described in detail with reference to the accompanying drawings. Note that descriptions are made in the following order.

[0054] 1. Example

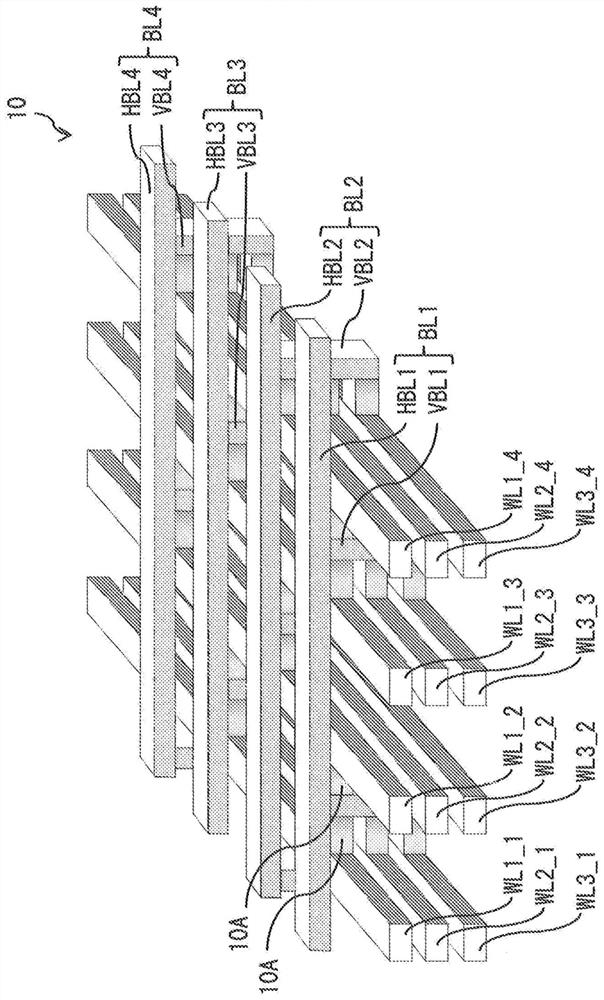

[0055] Examples including arrays of memory cells arranged in stacks ( Figure 1 to Figure 19 )

[0056] 2. Modification example

[0057] Modification A: Example where precharge is omitted ( Figure 21 to Figure 25 )

[0058] Modification B: Example of performing precharge when writing fails ( Figure 26 )

[0059] Modification C: Example of performing precharge according to the write position ( Figure 27 )

[0060] Modification D: Modification of the precharge circuit ( Figure 28 to Figure 30 )

[0061] Modification E: An example including a memory cell array in a single-layer arrangement ( Figure 31 and Figure 32 )

[0062] [1. Example]

[0063] [structure]

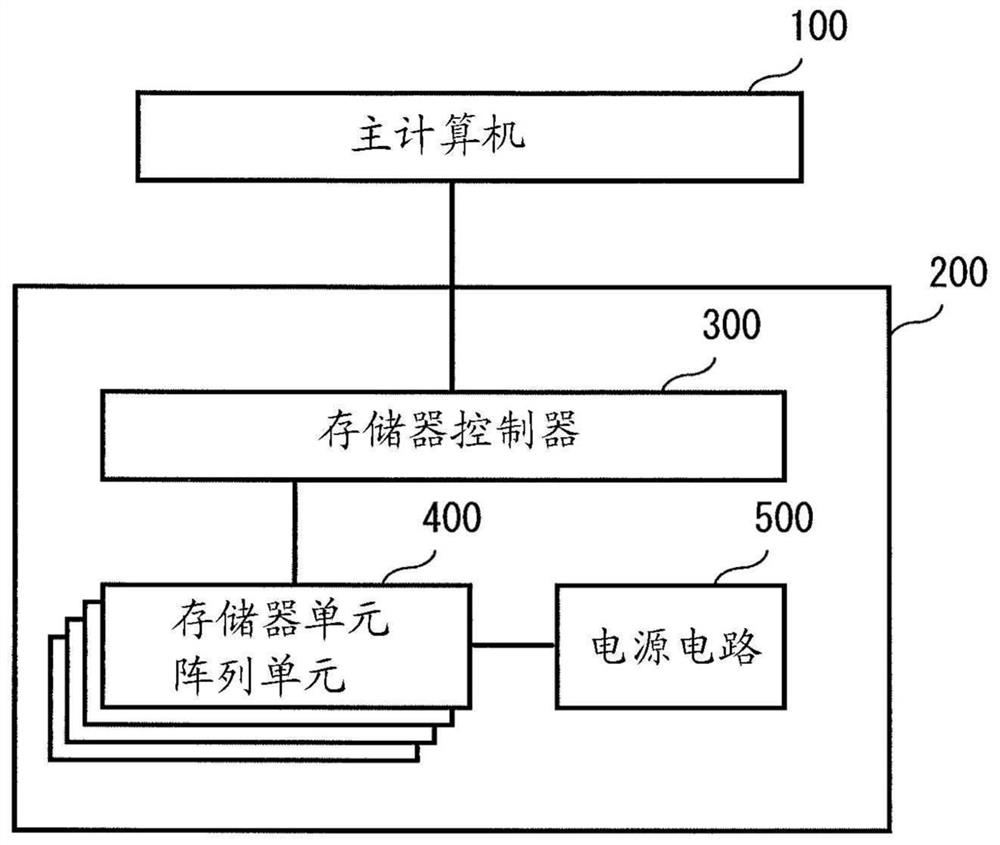

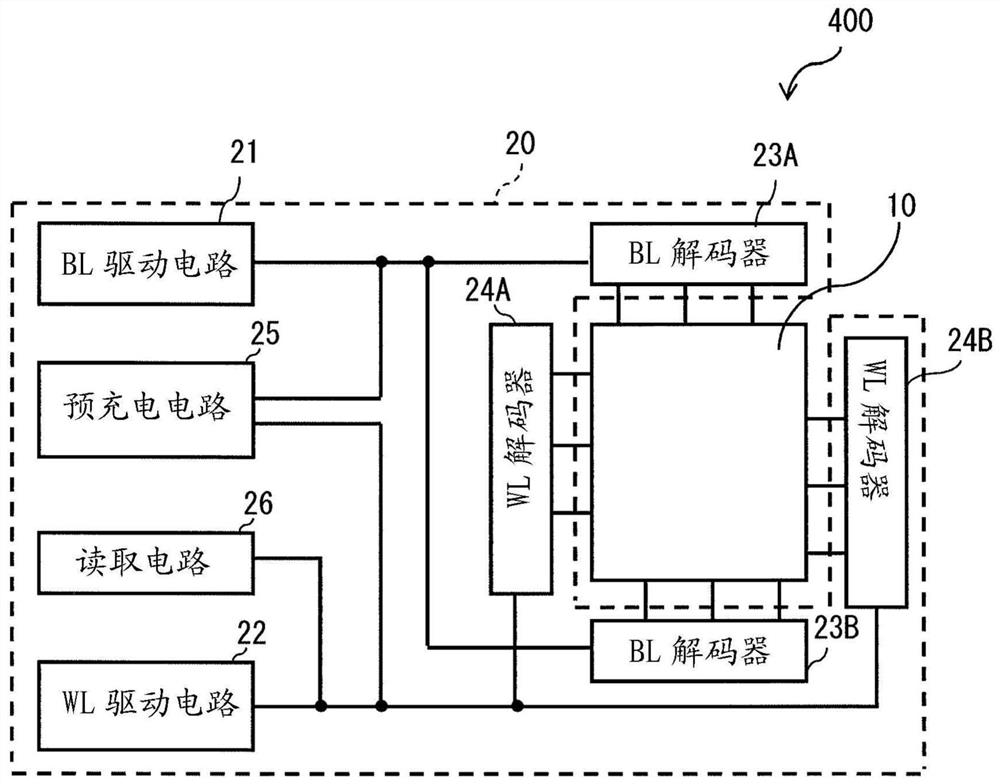

[0064] figure 1 One example of functional blocks of an information processing system accordi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More