CPLD/FPGA-based clock frequency division module design method

A technology of clock frequency division and module design, applied in the field of frequency division, can solve the problems of high resource consumption, odd frequency division not 50% duty cycle, etc., to achieve the effect of less hardware resource consumption, flexible cutting, and fast update speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

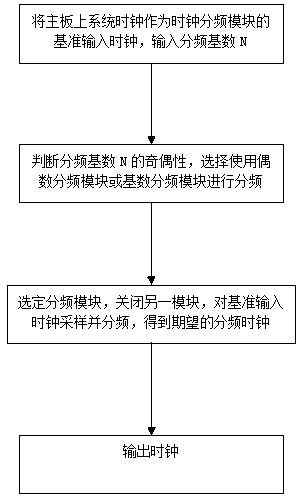

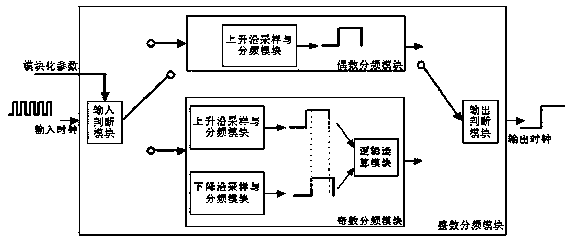

[0030] Such as figure 2 As shown, the system clock on the motherboard is used as the reference input clock of the integer frequency division module, and the given module input parameters are used as the frequency division base N of the integer frequency division module according to actual needs. Select an even frequency division module or an odd frequency division module according to the frequency division base N, and at the same time, turn off the other frequency division module, sample and divide the reference input clock to obtain the desired frequency division clock; according to the frequency division base N, select an even number The N-divided clock obtained by the frequency division module or the odd frequency division module is used as an output frequency division clock and as an input clock of other modules.

[0031] Even frequency division module:

[0032] In order to divide the reference clock by even numbers, an even frequency division module is designed, and its...

Embodiment 2

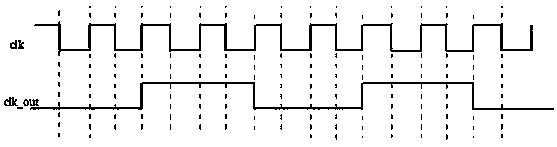

[0036] In order to verify the effectiveness of any integer frequency divider based on CPLD / FPGA, in the ModelSim environment, by giving different frequency division numbers N, the frequency divider is verified. The integer frequency divider realizes 4 (N is an even number) division Frequency simulation results such as Figure 6As shown, the simulation results of frequency division by 5 (N is an odd number) implemented by an integer frequency divider are as follows Figure 7 shown. It can be seen from the simulation results that the present invention is based on CPLD / FPGA oriented to any integer 50% duty ratio frequency frequency clock modular implementation method can output high-quality frequency division clock according to the N value, which verifies that the present invention is oriented to any integer number based on CPLD or FPGA. 50% duty cycle divided clock availability.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More