Patents

Literature

123results about How to "Flexible expansion" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

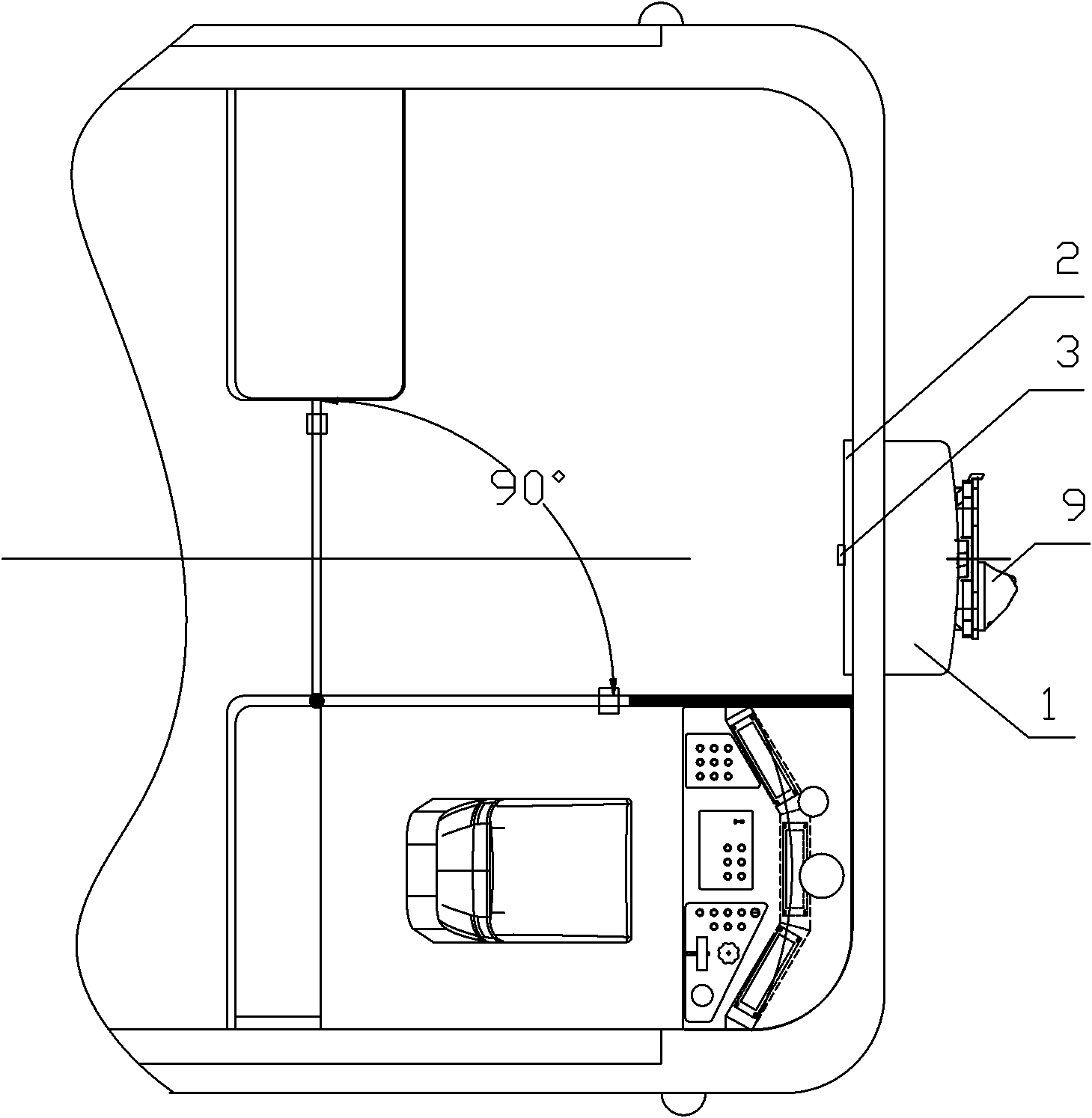

Method of controlling holder camera to automatically track target

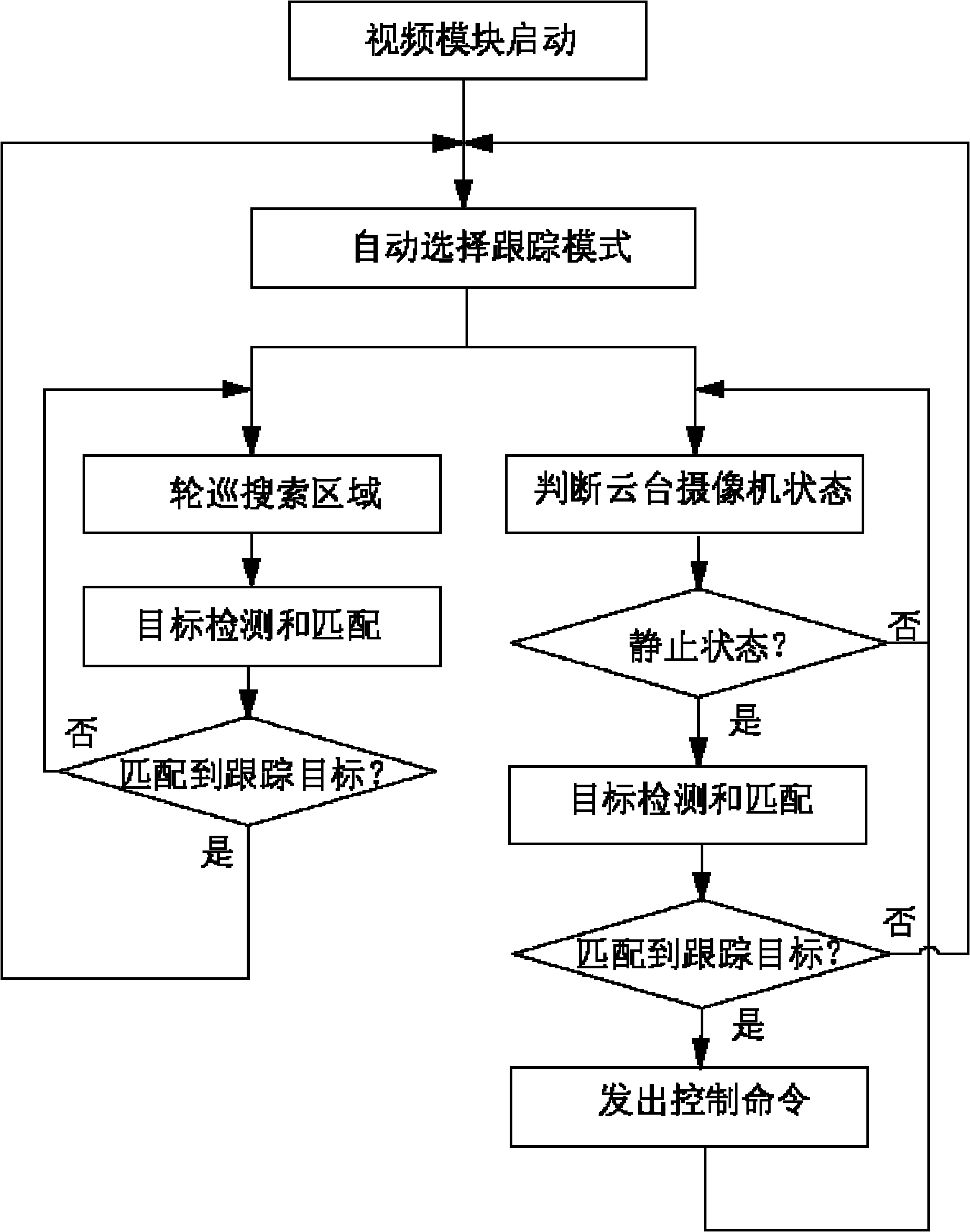

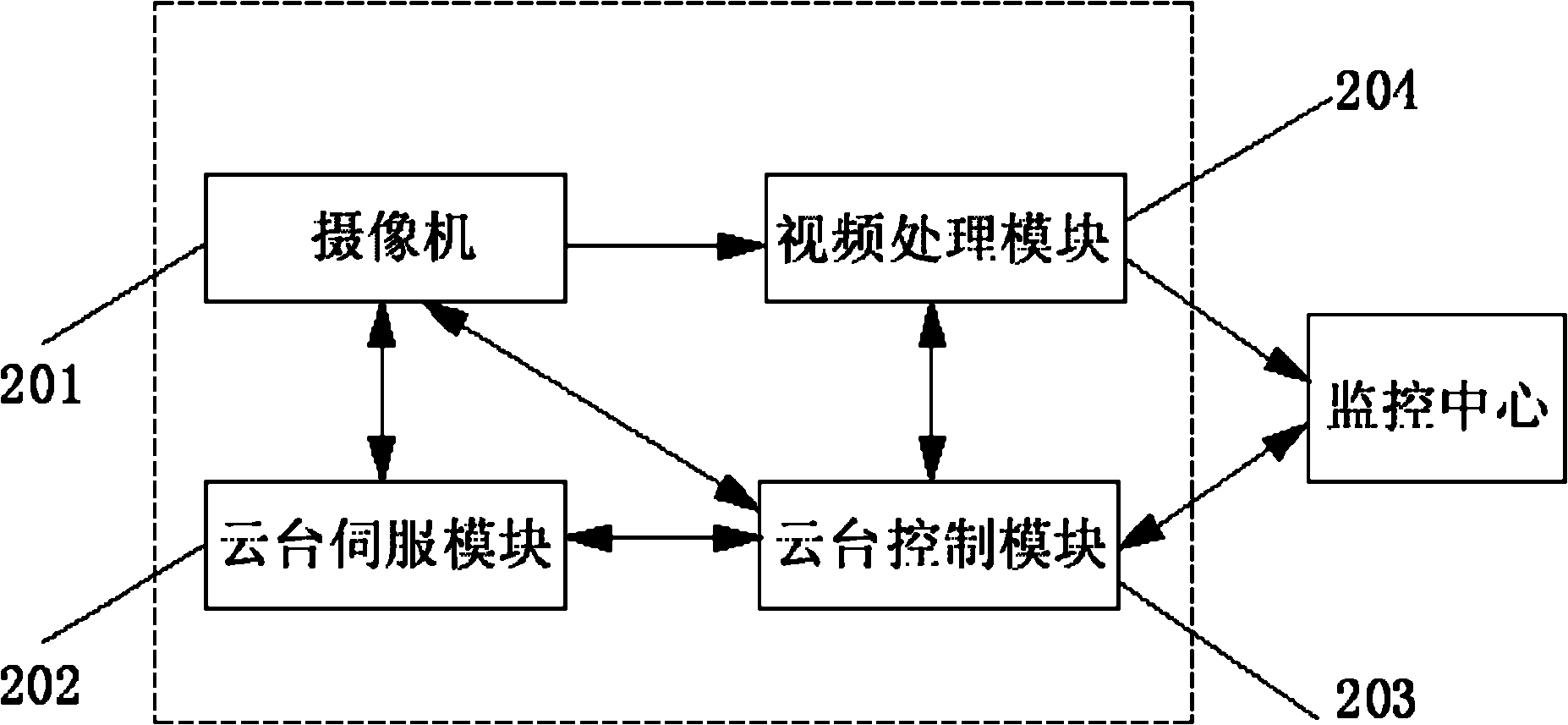

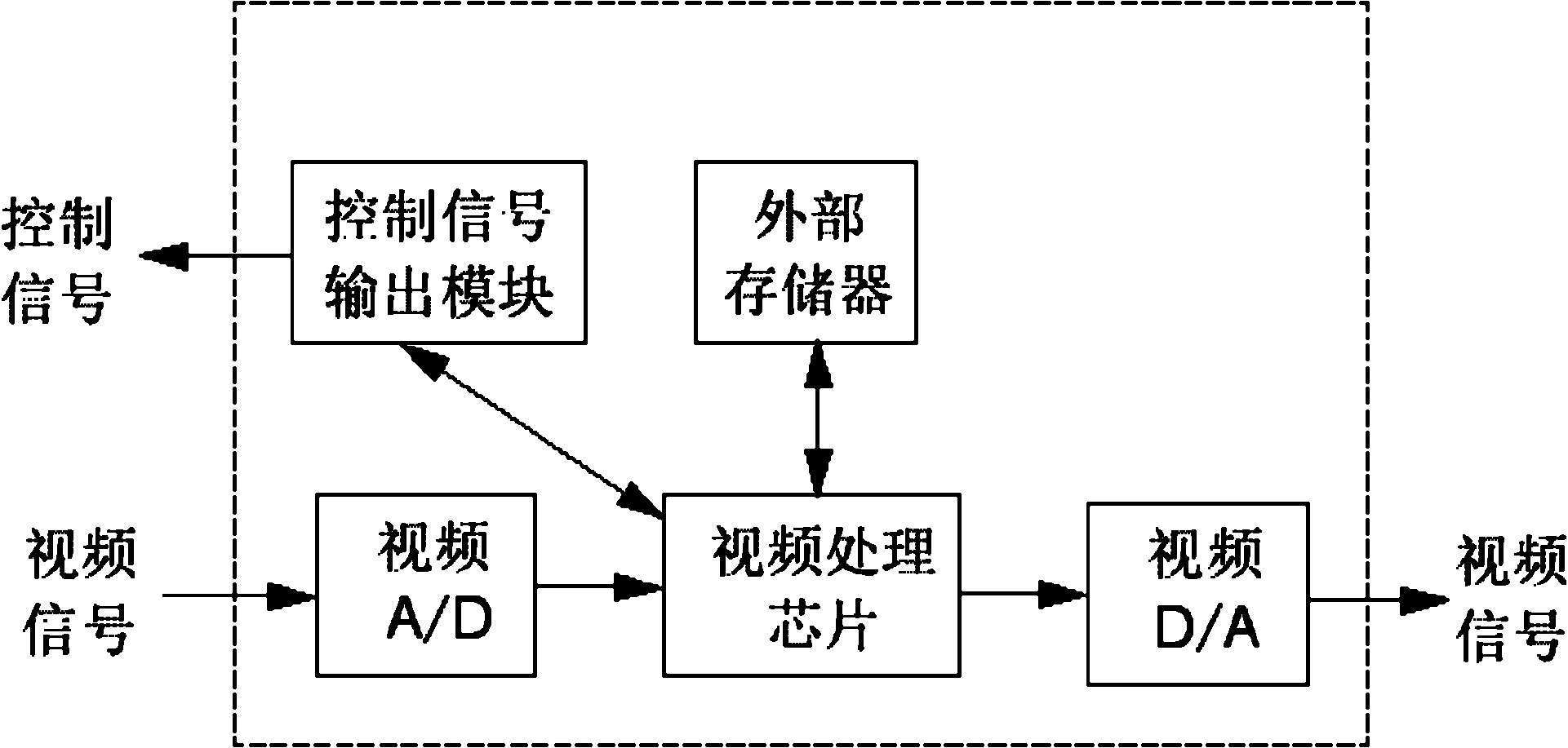

ActiveCN101860732ARealize automatic tracking of target tasksImprove tracking accuracyTelevision system detailsColor television detailsTracking modelProcess module

The invention relates to a method of controlling a holder camera to automatically track a target. The method comprises the following steps. A tracking model is automatically chosen. A video frequency processing module automatically chooses an automatic tracking model and a global search model according to the tracking state of the target. The processing process of the automatic tracking model is that the video frequency processing module judges the state of the holder camera and after the tracked target is matched, control orders are sent according to the position and size of the target to regulate the position and the focal distance of the camera. The processing process of the global search model is that the video frequency processing module detects and matches the target through a taking turn manner in a plurality of search areas of a monitored area until the tracked target is found. The invention has reasonable design, realizes the automatic tracking function of the camera on the target, ensures that the position and size of the target are suitable for monitoring, has the advantages of high tracking precision, strong real-time property, low cost, flexible expansion and the like, facilitates the use of monitoring staff and improves the work efficiency of the monitoring staff.

Owner:TIANJIN YAAN TECH CO LTD

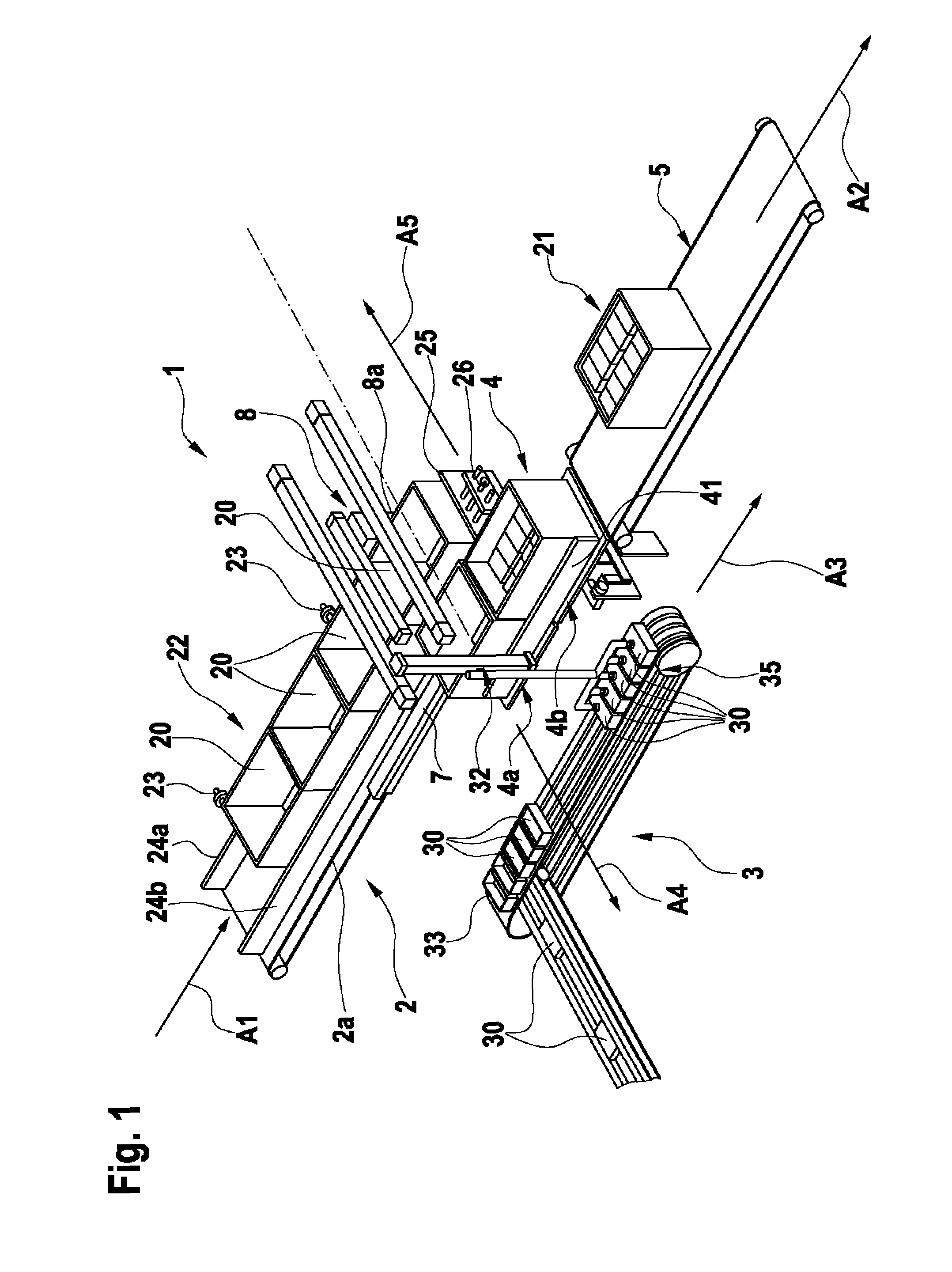

Packaging device

InactiveUS20130283731A1Easy to convertEasy to adaptSolid materialLiquid materialEngineeringMechanical engineering

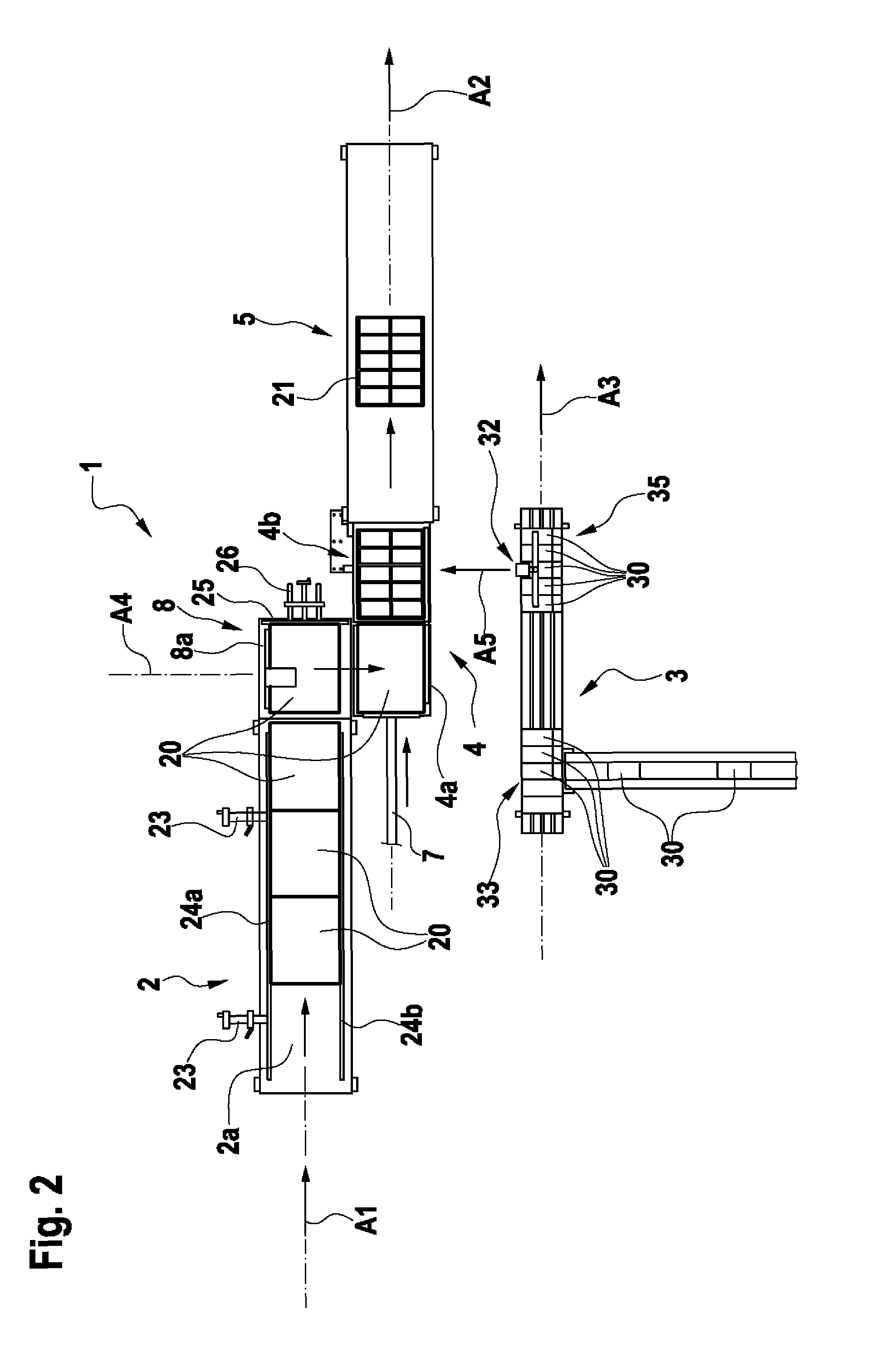

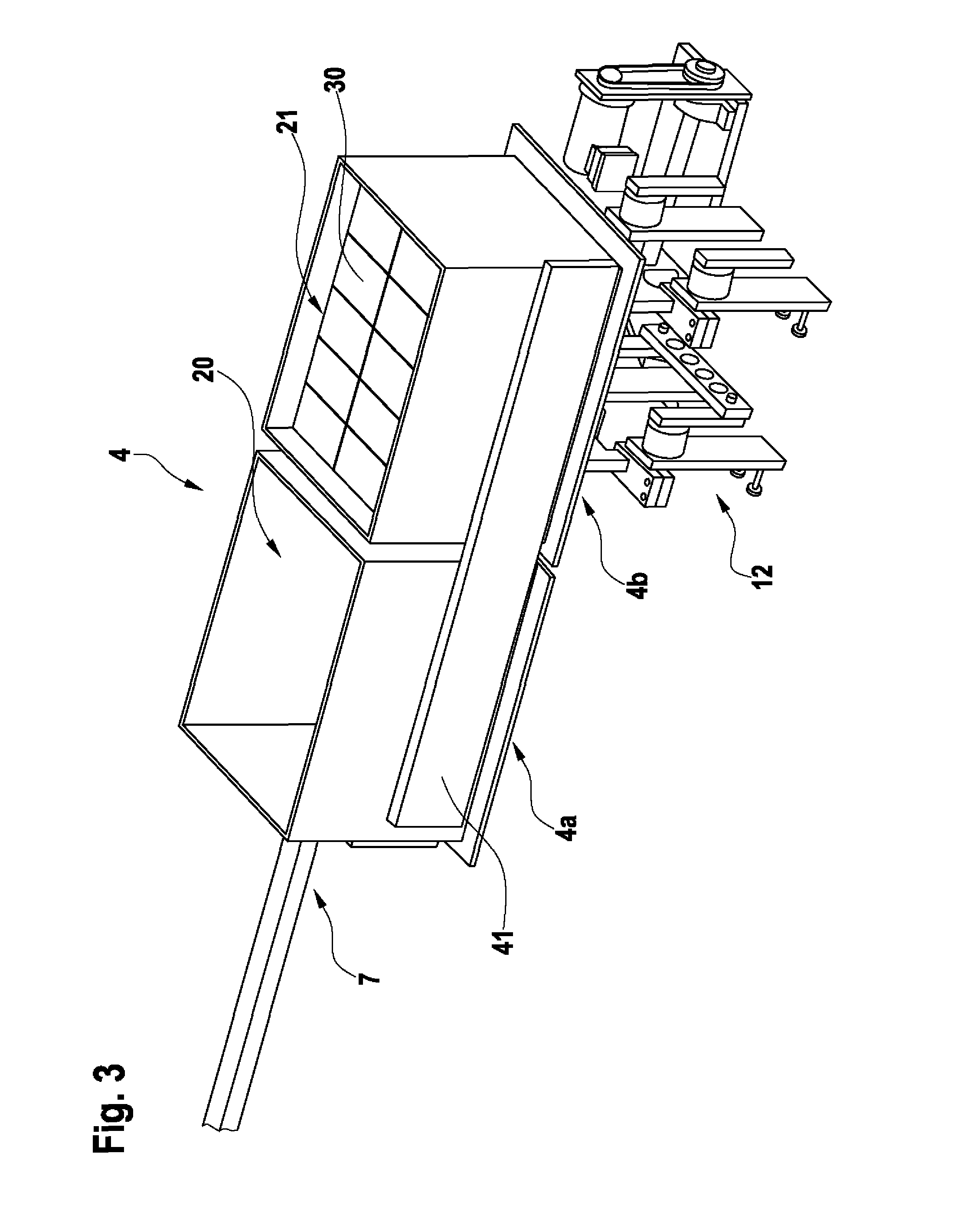

The invention relates to a modularly constructed packaging device, comprising: a package feed (2) for feeding empty packages (20), a product feed (3) for feeding products (30, 40), a loading station (4), in which the products are packed into the empty package in order to provide a packaging container (21), and a cardboard-box discharge (5), which leads away the packaging container.

Owner:ROBERT BOSCH GMBH

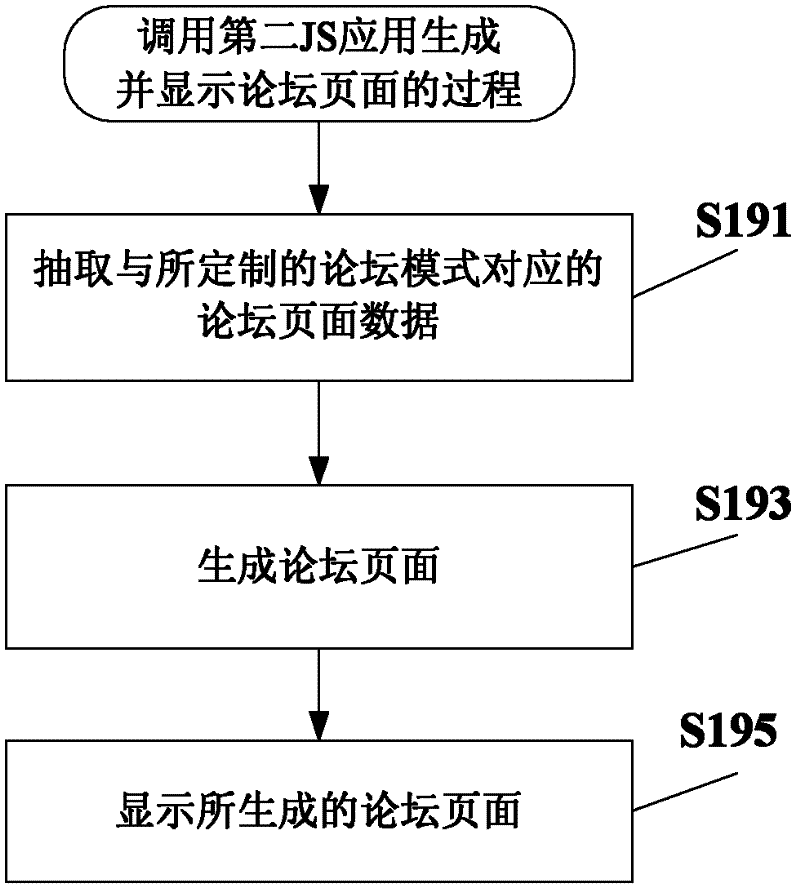

Webpage browsing method, WebApp framework, method and device for executing JavaScript, and mobile terminal

ActiveCN102693280AReduce waiting timeImprove experienceDigital data information retrievalText processingStart upOpen API

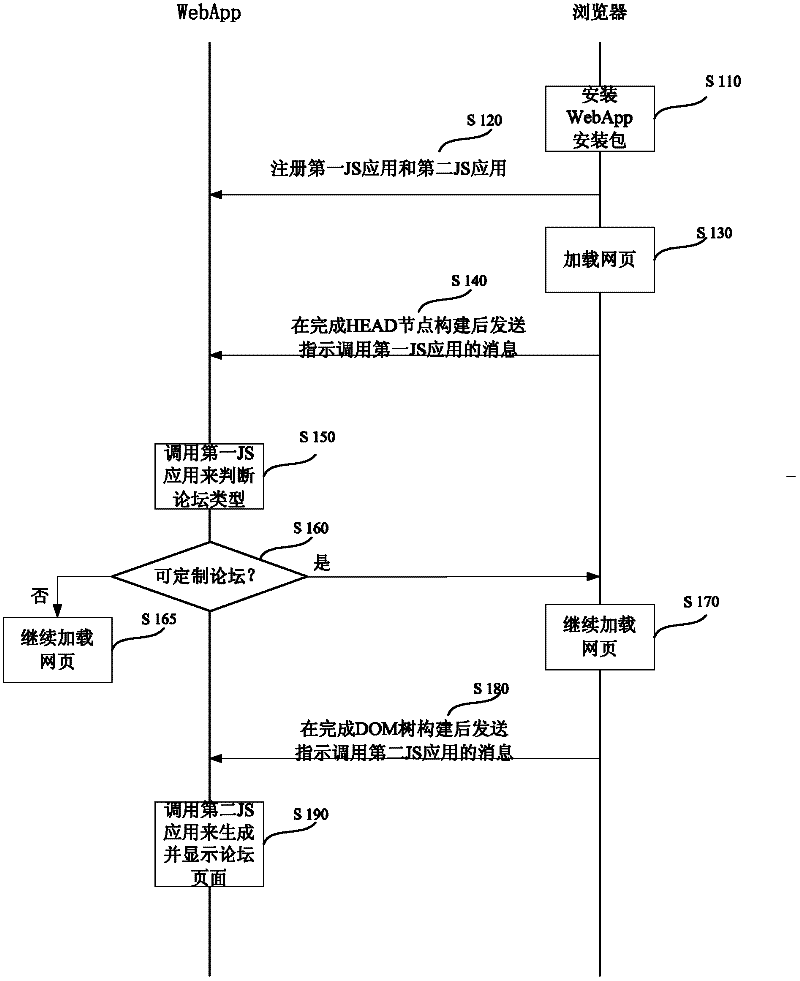

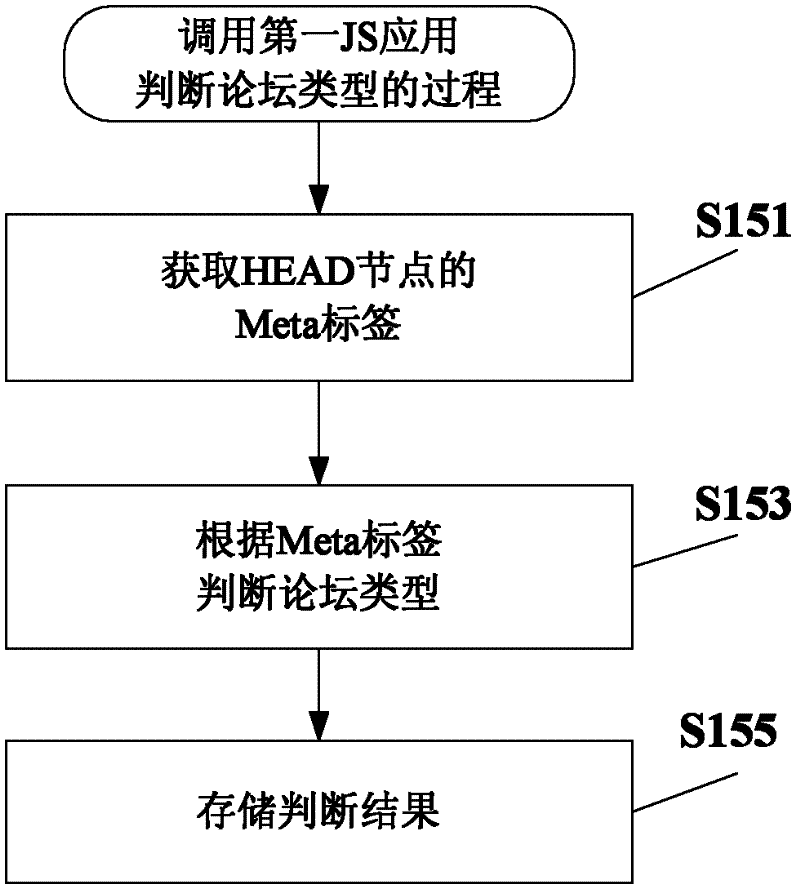

The invention provides a method for executing an extended JavaScript by using an extended JS interface. The method comprises the following the steps: inquiring an extension program whether to execute the extended JavaScript at a predetermined time when a webpage is loaded, wherein the extension program is loaded when a browser is started up; the browser assembles the extended JS interface according to an open API when determining that the extended JavaScript is needed to be executed; executing the extended JavaScript by using the extended JS interface. According to the invention, browsing mode and layout mode of a browser can be changed dynamically according to content requirements of a webpage in the form of extension programs, so that browsing experience of users is improved.

Owner:ALIBABA (CHINA) CO LTD

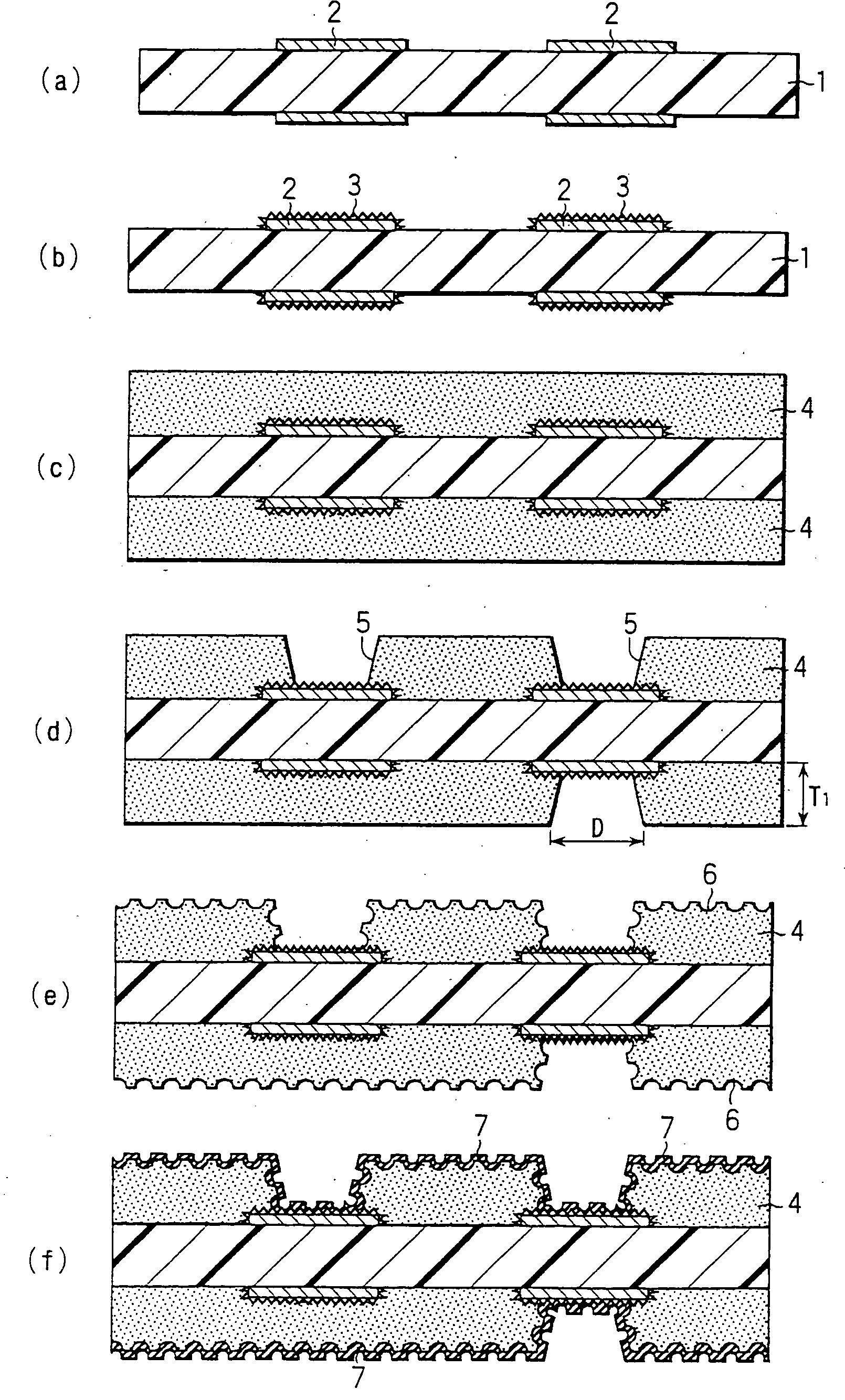

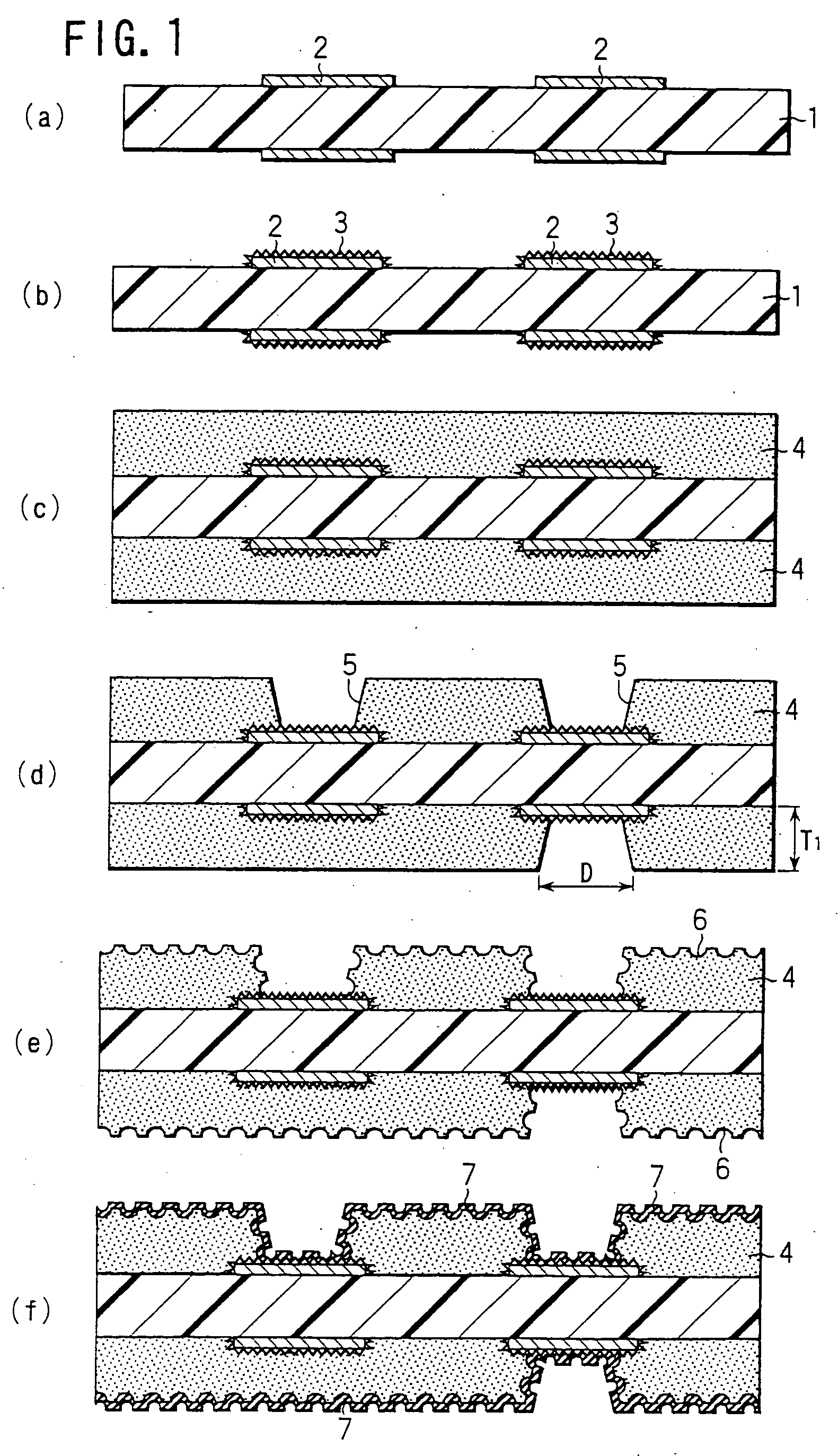

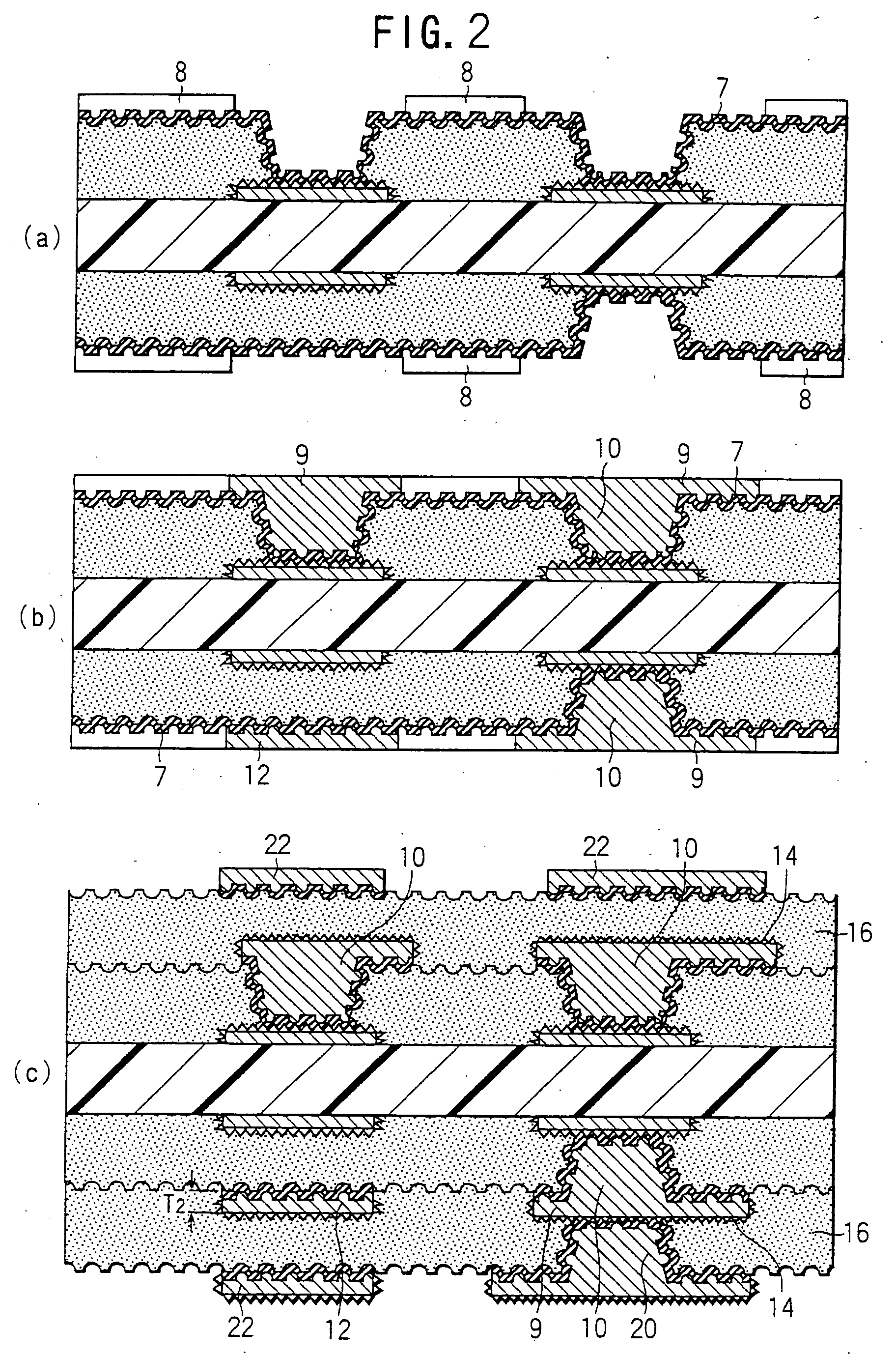

Multilayer printed wiring board with filled viahole structure

InactiveUS20050100720A1Large malleabilityAdhesionInsulating substrate metal adhesion improvementDielectric materialsElectrical conductorHigh fracture

The present invention provides a multilayer printed wiring board having a filled viahole structure advantageously usable for forming a fine circuit pattern thereon, and having an excellent resistance against cracking under a thermal shock or due to heat cycle. The multilayer printed wiring board is comprised of conductor circuitry layers and interlaminar insulative resin layers deposited alternately one on another, the interlaminar insulative resin layers each having formed through them holes each filled with a plating layer to form a viahole. The surface of the plating layer exposed out of the hole for the viahole is formed substantially flat and lies at a substantially same level as the surface of the conductor circuit disposed in the interlaminar insulative resin layer. The thickness of the conductor circuitry layer is less than a half of the viahole diameter and less than 25 μm. The inner wall of the hole formed in the interlaminar insulative resin layer is roughened and an electroless plating layer is deposited on the roughened surface. An electroplating layer is filled in the hole including the electroless plating layer to form the viahole. The interlaminar insulative resin layer is formed from a composite of a fluororesin showing a high fracture toughness and a heat-resistant thermoplastic resin, a composite of fluororesin and thermosetting resin or a composite of thermosetting and thermoplastic resins.

Owner:IBIDEN CO LTD

Public service platform and usage method thereof

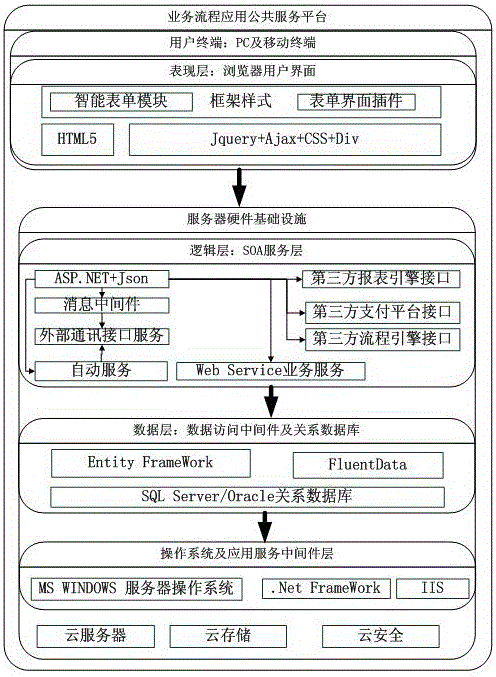

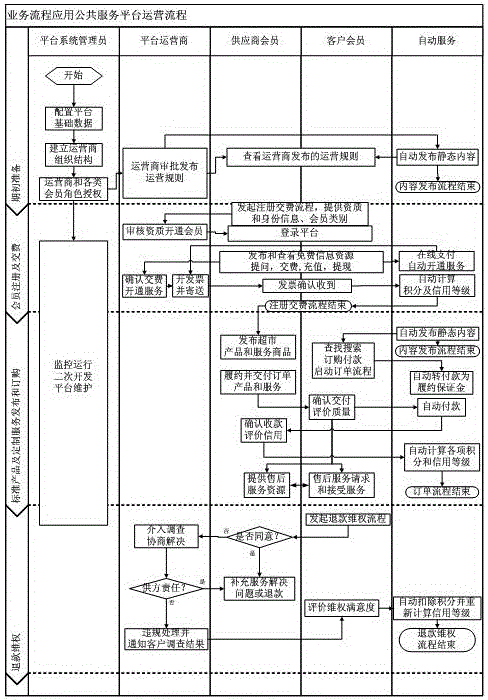

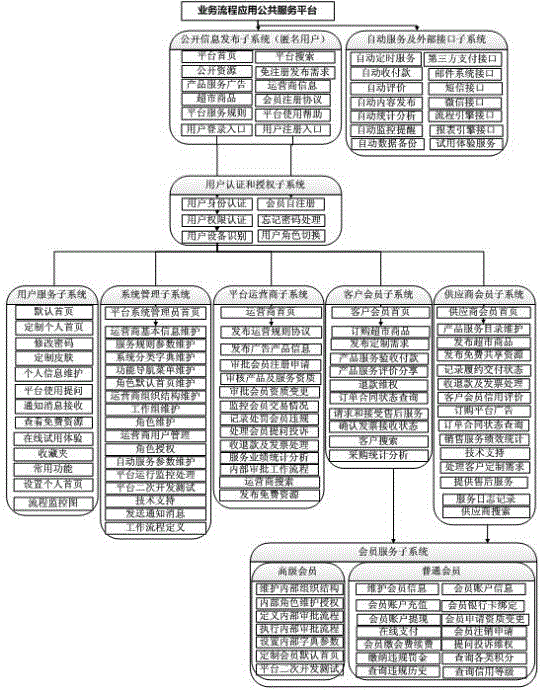

InactiveCN106169987AGuaranteed safety and reliabilityGuaranteed uninterrupted service capabilityTransmissionService flowOrder processing

The present invention relates to a platform and a usage method thereof, concretely to a public service platform and a usage method thereof. The platform comprises a terminal and a cloud server; the terminal includes a PC terminal and a mobile terminal, wherein the PC terminal and the mobile terminal form a presentation layer; the cloud server includes a logic layer and a data layer; and the data layer, the logic layer and the representation layer form the whole framework of the public service platform, and the whole framework of the public service platform includes two processes of content publishing and order processing. The present invention provides a product display and selling mode similar to a traditional supermarket, and divide a large-scale application business flow management software implementation process with long period, high cost and big risk into a gradually advanced iterative implementation process with short period, low cost and small risk; and moreover, through providing a service platform, the normalized flow correlation product selling, the standardized requirement customization service, standardized order processing and the pre-sales and after-sales service flows, the problem of the traditional offline implementation service of the BPM industrial field is solved, and the cost and risk of supplying to both parties are reduced.

Owner:山东达创网络科技股份有限公司

Method implementing sub-conference using medium service apparatus

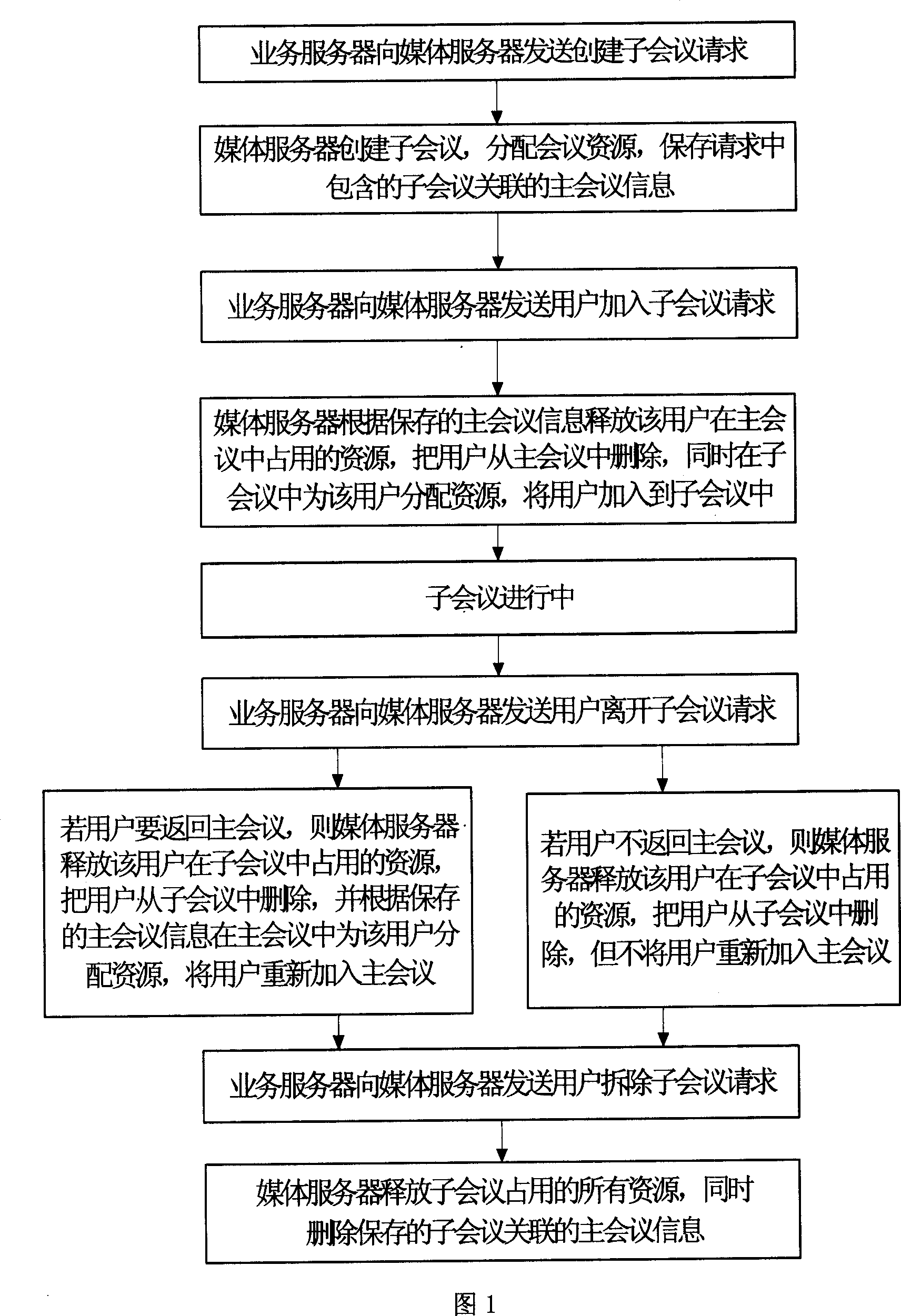

InactiveCN101110686AEasy accessImprove playbackSpecial service provision for substationSpecial service for subscribersMedia serverRequest distribution

The present invention discloses a method using a media server to realize a sub-conference, which includes procedures below: A service server transmits a request indicating to initiate a sub-conference to a media server. The media server distributes resource needed for the sub-conference and saves information of a main conference correlative with the sub-conference in the request. The service server sends a request to the media server to make users join the sub-conference. The media server releases resource distributed by the main conference for the user according to information contained in the request and saved in the main conference. Meanwhile, resource needed for the user is distributed in the sub-conference and the user is added into the sub-conference user list. Besides, the media server provides a conference function to users joining the sub-conference. The present invention only slightly changes original conference flows, has the advantages of easy execution, simple rule, flexible expansion, plays and records media to a single user or a specific quantity of users during conference, meet demands of conference for private user chat and group discussion and solely notifies specific contents to users participating in the conference midway.

Owner:ZTE CORP

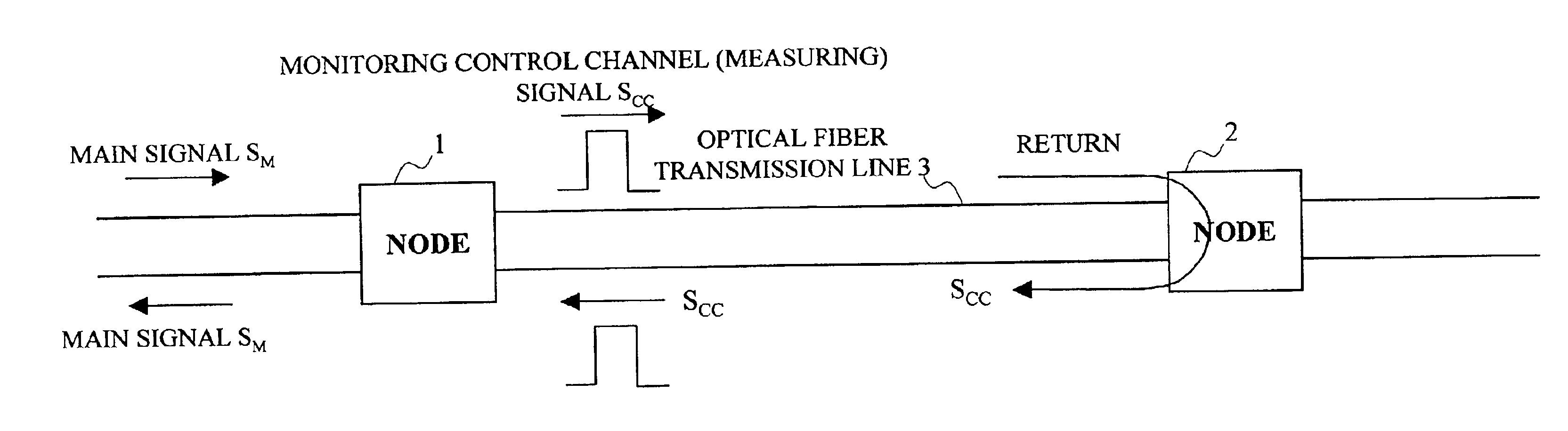

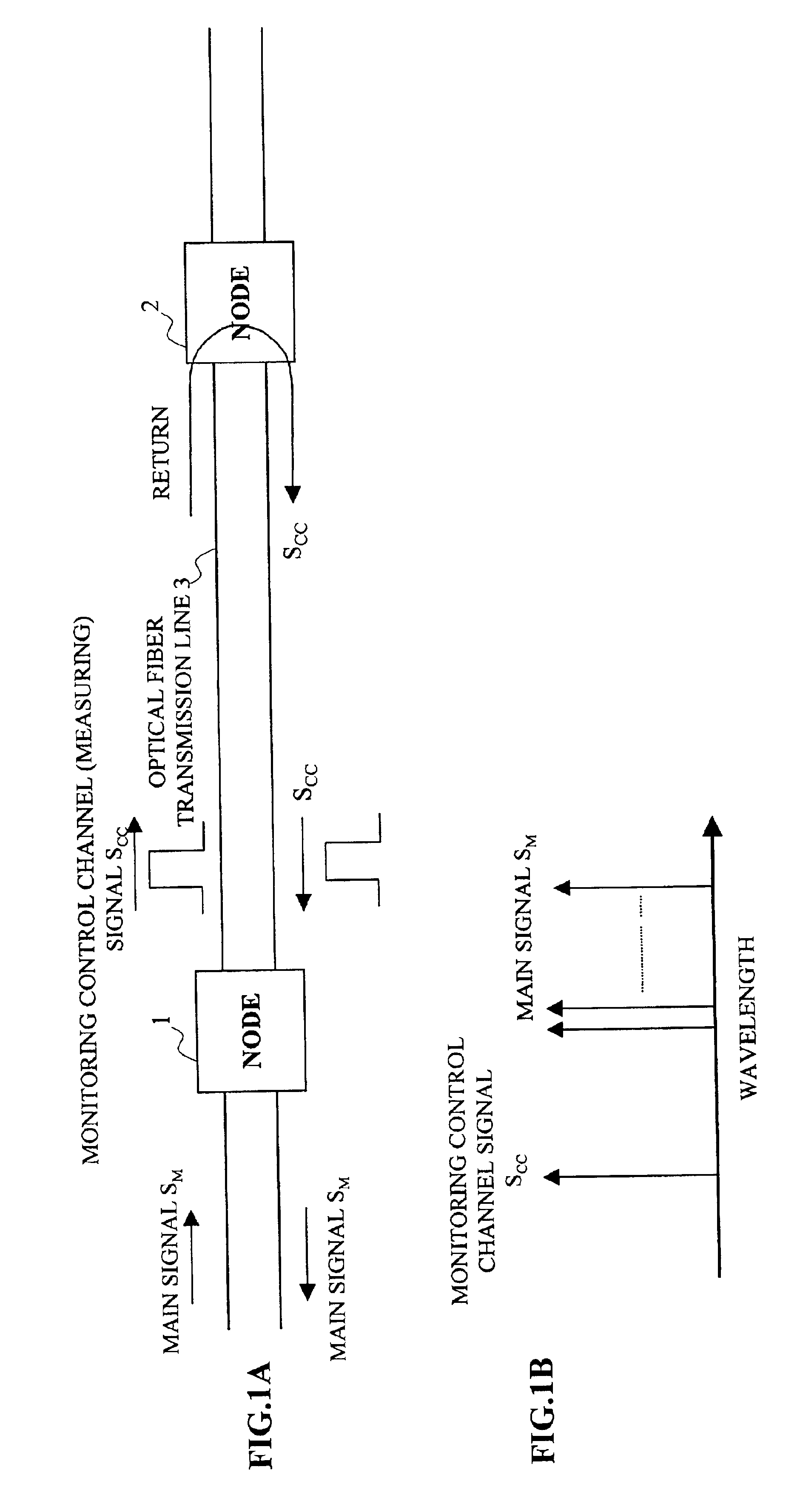

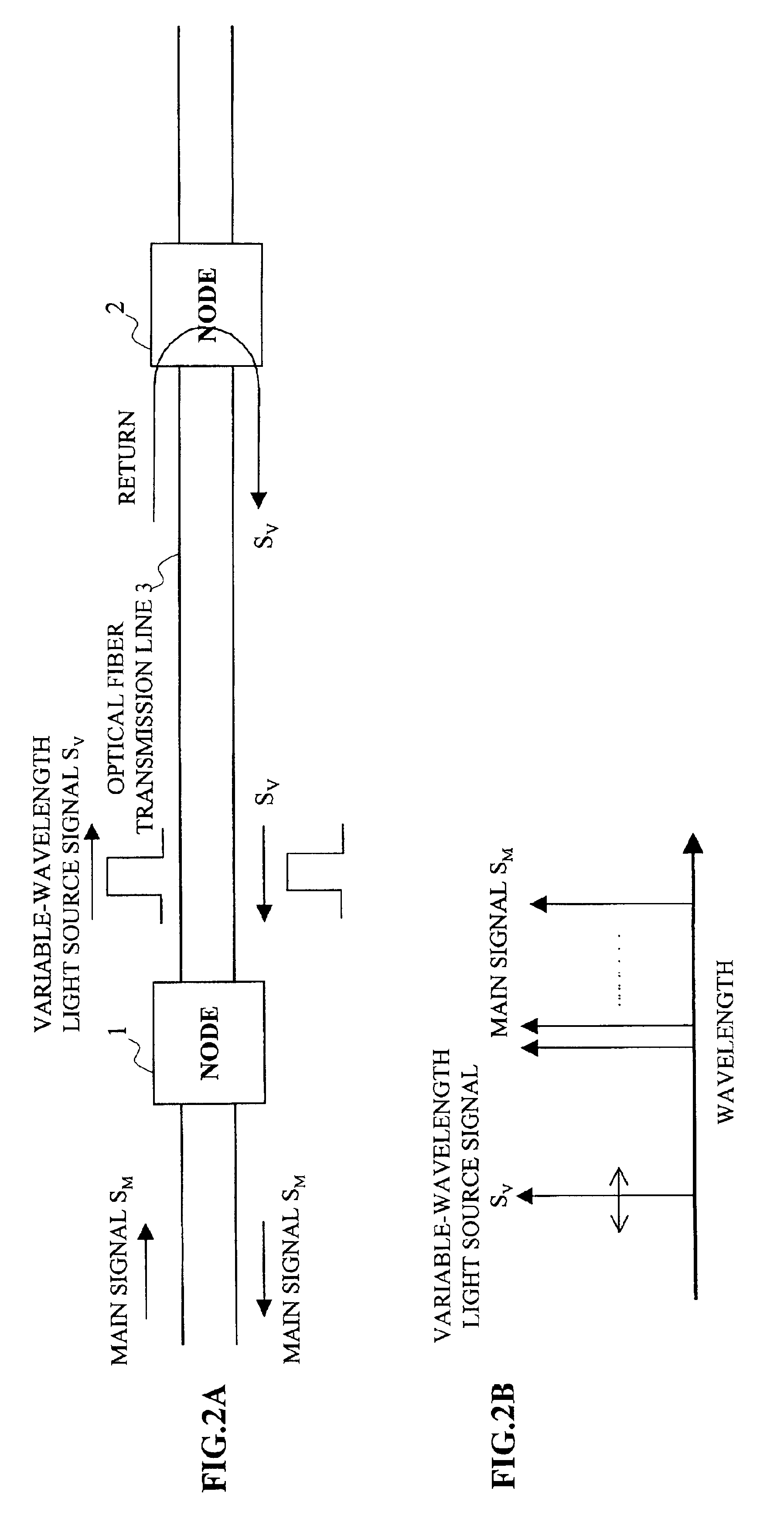

Method of measuring wavelength dispersion amount and optical transmission system

InactiveUS6864968B2Improve transmission qualityFlexible expansionWavelength-division multiplex systemsMaterial analysis by optical meansLength waveTransmission system

Measuring a wavelength dispersion amount of an optical transmission line without disconnecting the optical transmission line. A measuring signal is transmitted together with a main signal from a first node while the optical transmission line is in operation. The measuring signal is extracted and returned at an opposing node. A delay time required for the measuring signal to return is measured. A length of optical transmission line between the nodes is calculated from the measured delay time. A wavelength dispersion amount of the optical transmission line is calculated based on the calculated length.

Owner:FUJITSU LTD

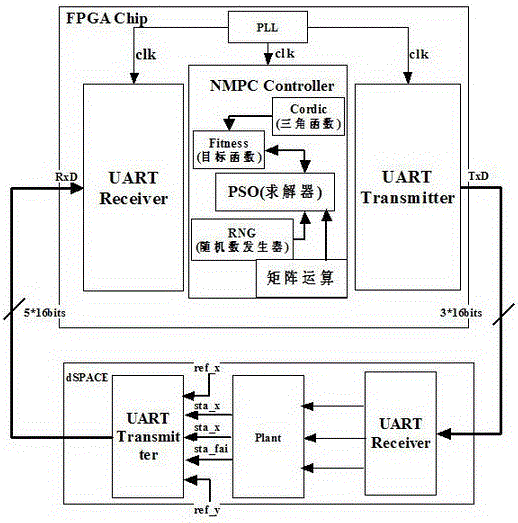

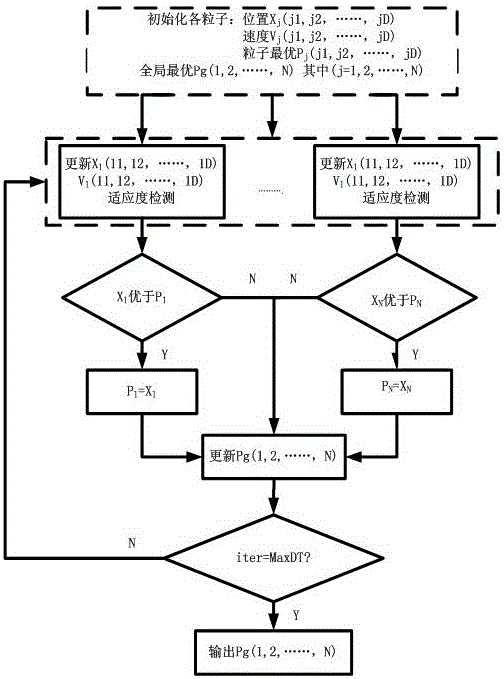

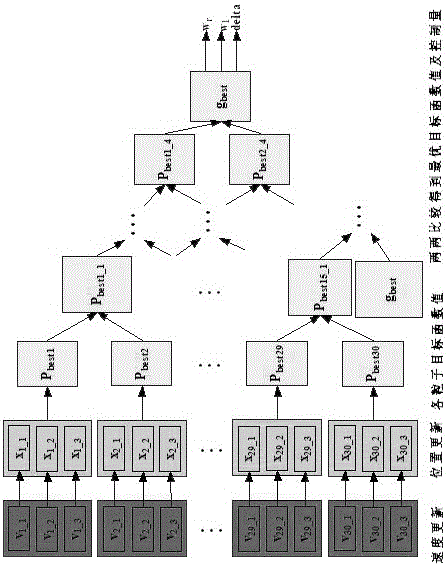

Non-linear-model-predictive-control FPGA hardware acceleration controller and acceleration realization method

ActiveCN105955031AExtended ValidationImprove fast computing powerAdaptive controlFpga implementationsAcceleration control

The invention, which belongs to the field of the FPGA realization technology, relates to a non-linear-model-predictive-control-based FPGA hardware acceleration controller and an acceleration realization method. The invention aims at extending application of non-linear model predictive control (NMPC) in rapid dynamic system; and a non-linear-model-predictive-control-based FPGA hardware acceleration controller and an acceleration realization method in non-linear planning can be realized by using a PSO algorithm. For a hardware acceleration controller, a WMR prediction control model is established; according to a control requirement of target model WMR trajectory tracking, an optimization problem is solved; and an NMPC-PSO algorithm flow is executed. According to the invention, on the basis of a one-to-one correspondence relationship between codes and bottom circuits, the parallel computing structure of the FPGA and the parallel computing characteristics of the PSO algorithm can be combined well, so that the rapid computing capability of the NMPC is improved, the real-time requirement of the controller can be met well, and NMPC application in the actual rapid dynamic system can be extended. Meanwhile, on-line flexible reducing, extending, and upgrading of the scheme can be realized; and thus the controller and the realization method can adapt to the current situation of the fast product updating speed; and the controller can be verified rapidly.

Owner:JILIN UNIV

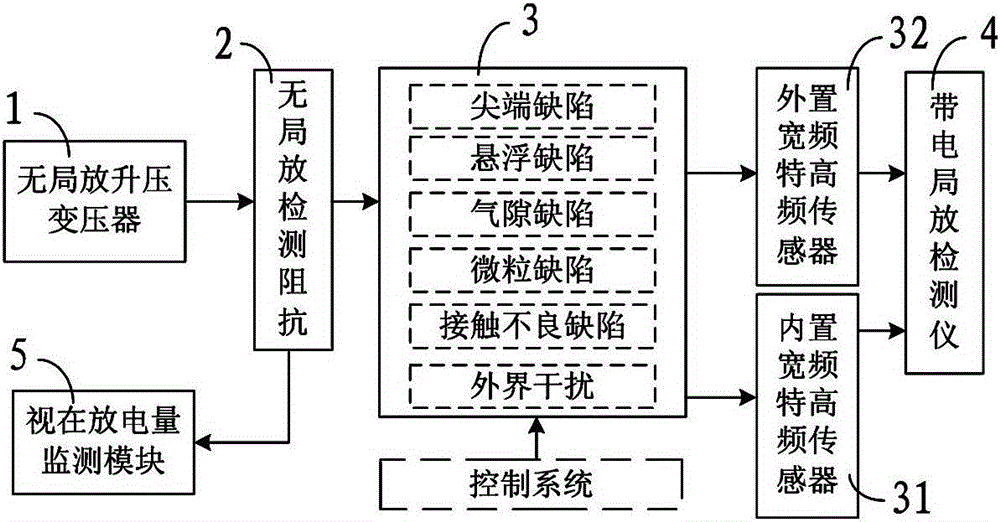

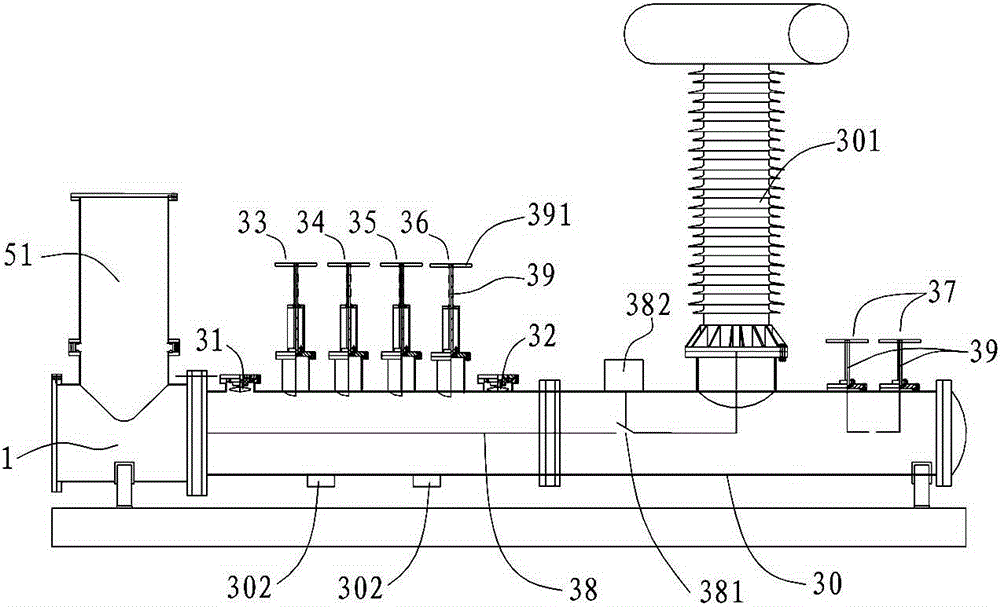

GIS partial discharge charged detection test device based on defect simulation

InactiveCN105223478AImprove reliabilitySimple structure and principleTesting dielectric strengthTransformerCharge detection

The invention discloses a GIS partial discharge charged detection test device based on defect simulation, comprising a no-partial-discharge test transformer, a no-partial-discharge detection impedor, GIS defect simulation equipment, and a charged partial discharge detector. The no-partial-discharge test transformer is connected with defective components pre-arranged in the GIS defect simulation equipment through the no-partial-discharge detection impedor. A built-in broadband ultrahigh-frequency sensor is arranged inside the GIS defect simulation equipment, an external broadband ultrahigh-frequency sensor is arranged outside the GIS defect simulation equipment, and the built-in broadband ultrahigh-frequency sensor and the external broadband ultrahigh-frequency sensor are connected with the input end of the charged partial discharge detector. The device of the invention can be applicable to GIS partial discharge charged detection test under all kinds of defect simulation, can be used for simulating various defects truly and conducting charged detection test of local discharge signals for the defects, and has the advantages of simple structure principle, low cost and high reliability of test results.

Owner:STATE GRID CORP OF CHINA +2

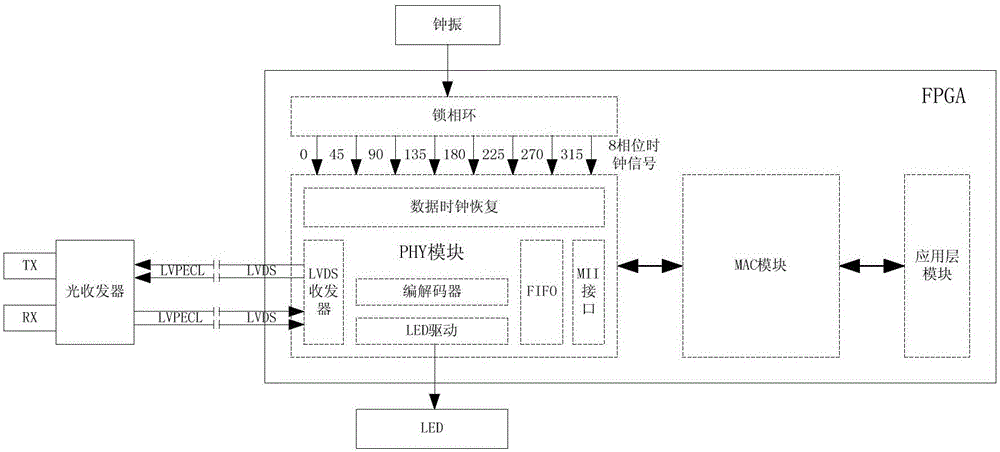

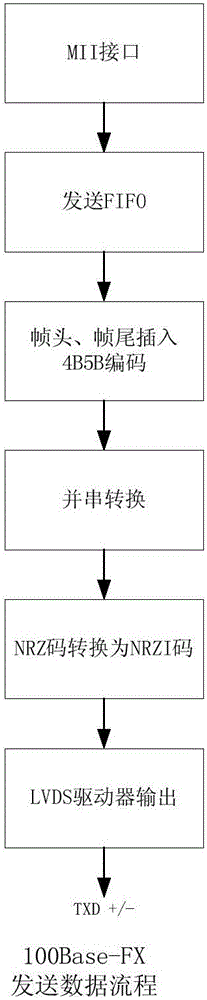

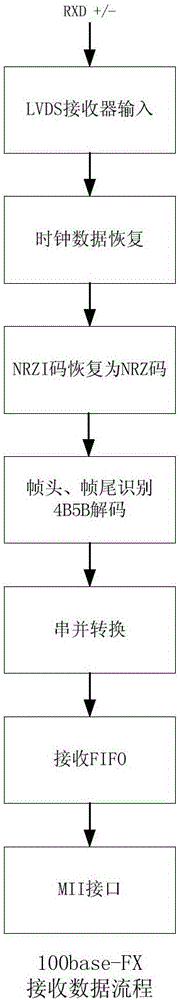

Ethernet realization system of FPGA chip internally provided with PHY transceiver function

InactiveCN104993982AEasy to manageReduce typesData switching by path configurationTransceiverDifferential signaling

The invention discloses an Ethernet realization system of an FPGA chip internally provided with a PHY transceiver function. The Ethernet realization system comprises the FPGA chip and an FPGA external transceiver. The FPGA chip comprises an MAC module and a PHY module. In a data transmitting process, data of the MAC module is cached to a memory, Ethernet frame head frame tail insertion and encoding are performed, parallel-serial conversion and encoding are performed, and difference signals are sent to the external transceiver through an internal transceiver; and in a data receiving process, the difference signals are converted into sing-end signals, serial asynchronous data signal clock data recovery is performed, encoding is carried out on recovered data, frame head frame tail identification and decoding are performed, the data is arranged as byte aligned data after serial-parallel conversion, the byte aligned data is stored into the memory, and finally the data is transmitted to the MAC module for processing. According to the invention, the FPGA chip is internally provided with the PHY transceiver and MAC controller functions, and in this way, the Ethernet is realized, so that the integration and the reliability are improved.

Owner:NANJING GUODIAN NANZI POWER GRID AUTOMATION CO LTD

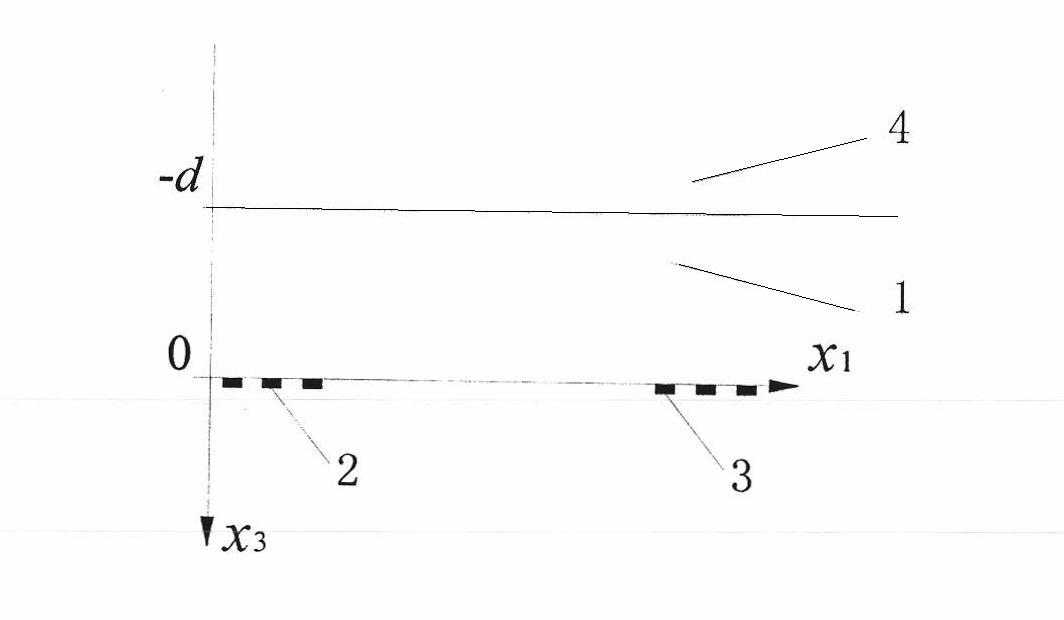

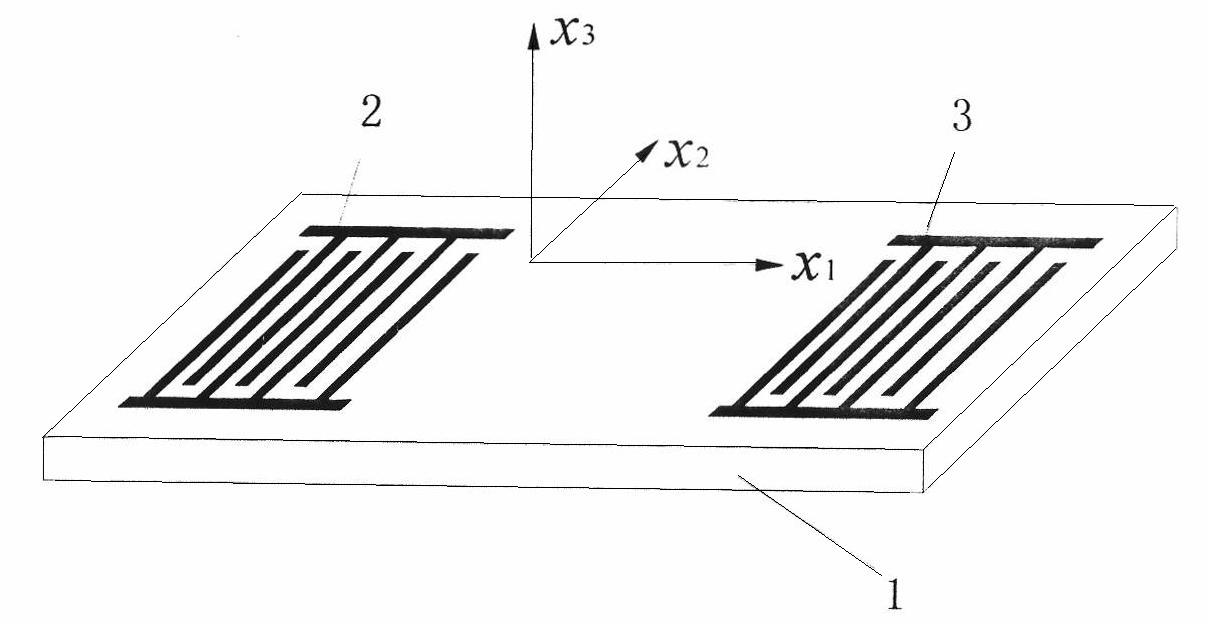

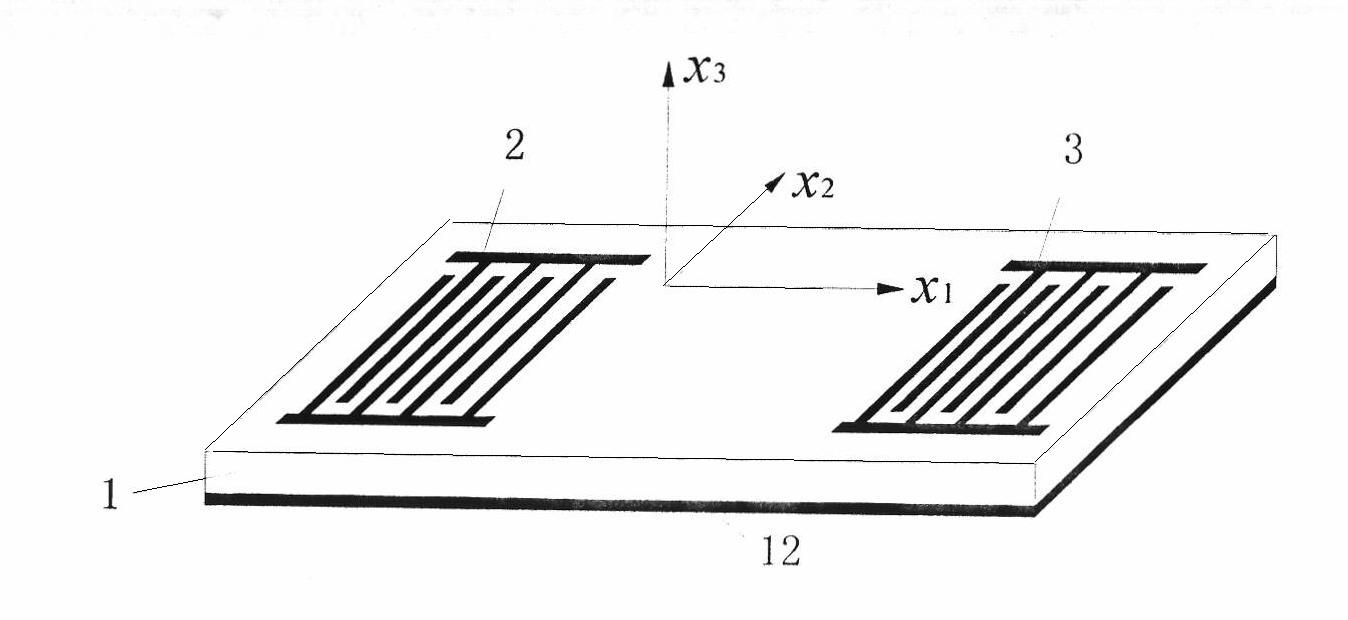

Acoustic plate mode wave virtual array sensor system and liquid detection method based on same

InactiveCN101806776AReduce signal interferenceFlexible choiceAnalysing fluids using sonic/ultrasonic/infrasonic wavesResistance/reactance/impedencePhase differenceEngineering

The invention provides an acoustic plate mode wave virtual array sensor system and a liquid detection method based on the system. The system comprises a micro controller module, a signal stimulation module, an acoustic plate mode wave virtual array apparatus module and a signal acquisition module. The method comprises the following steps: controlling the signal stimulation module to generate a high-frequency sinusoidal voltage signal with a certain frequency through the micro controller module; applying the signal to the input end of the acoustic plate mode wave virtual array apparatus module; generating an acoustic plate mode wave by using inverse piezoelectric effect; converting the acoustic plate mode wave transmitted to the output end of the acoustic plate mode wave virtual array apparatus module into a voltage signal with the inverse piezoelectric effect, wherein the propagation characteristic of the acoustic plate mode wave is affected by a liquid characteristic parameter loaded on the acoustic plate mode wave virtual array apparatus module; and measuring a phase difference and an amplitude ratio between an input voltage signal and an output voltage signal of the acoustic plate mode wave virtual array apparatus module through the signal acquisition module to detect the characteristic parameter of liquid. The system has the characteristics of small detection apparatus, small signal disturbance and the like.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

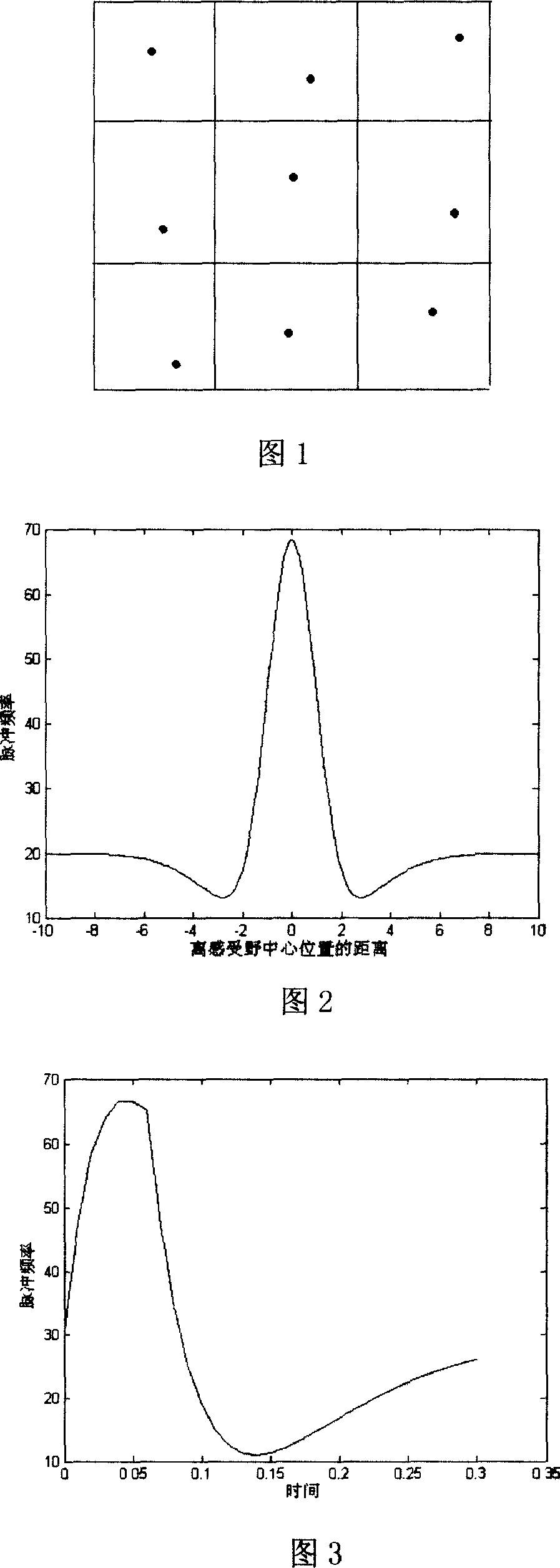

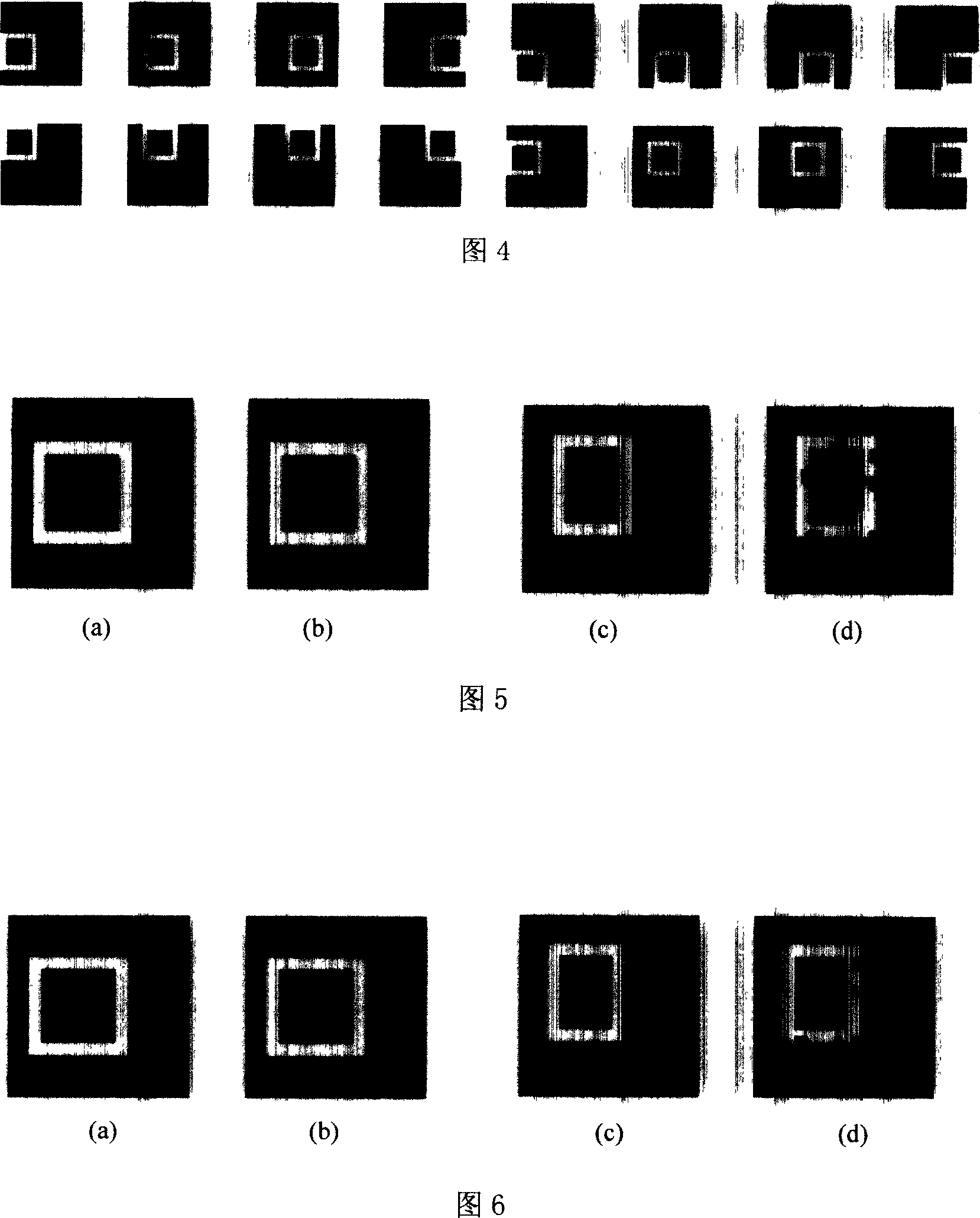

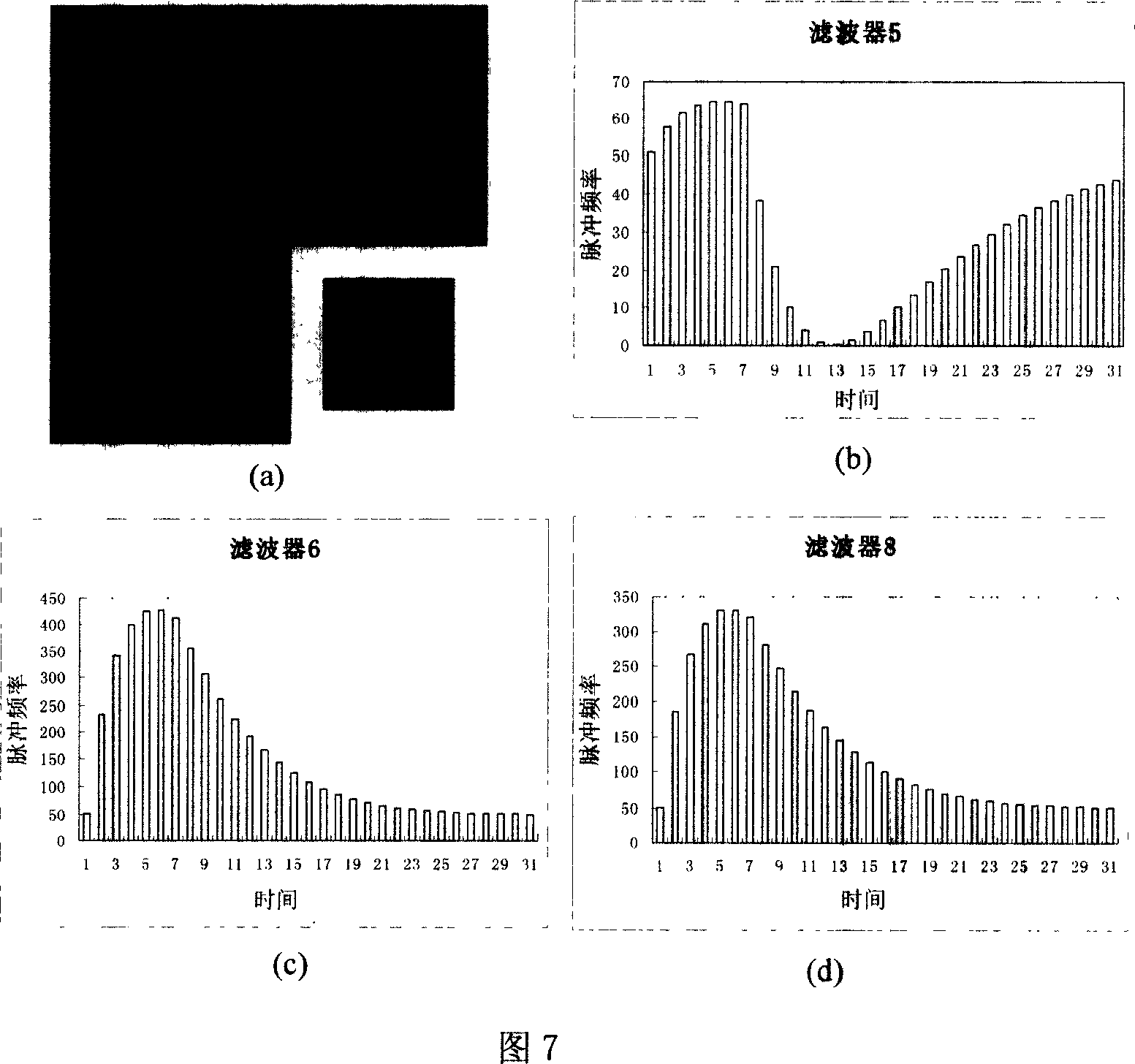

Implementation method of retina encoder using space time filter

InactiveCN101017535AIncrease flexibilityImprove adjustabilityEye implantsBiological neural network modelsRetinaTime space

This invention relates to one visual film coding method in computer application field, which comprises the following steps: inputting specimen image into time and space filter to get the BP human neural network input, train BP human neural net and to determine human neural net weight value; then inputting specimen any image and taking one random set of filter parameters by use of particle set or strategy method in filter parameter range for optimization; through multiple overlap, outputting image converged to input image and the parameters of the filter are determined with output impulse excitation is relative to input image film codes.

Owner:SHANGHAI JIAO TONG UNIV

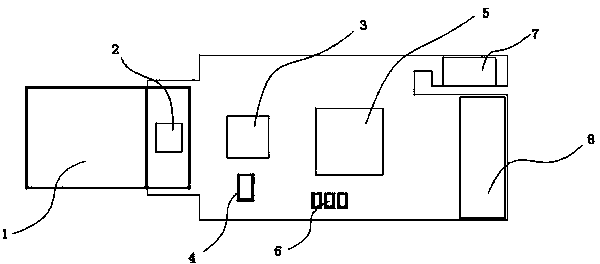

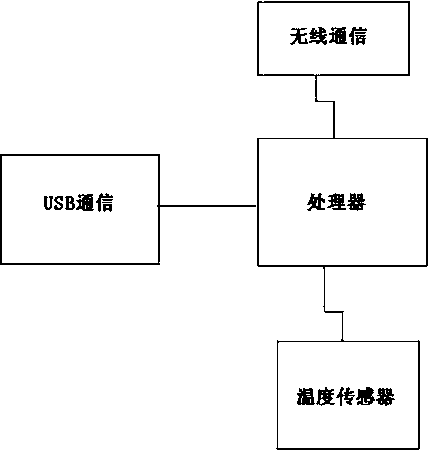

Intelligent home system containing intelligent home central control U shield

ActiveCN104079457ASlow responseFlexible expansionData switching by path configurationOperational systemSingle chip

The invention relates to an intelligent home system containing an intelligent home central control U shield. The intelligent home system is obtained by utilizing existing hardware resources and USB interfaces of a set top box. The intelligent home system comprises an intelligent home central control program, an intelligent home operation application program and the intelligent home central control U shield, wherein the intelligent home central control program and the intelligent home operation application program operate in the set top box, and the intelligent home central control U shield has a temperature measuring function and is provided with an intelligent home coordination center. The U shield contains a USB communication module and a wireless communication module, a temperature detection sensor and a wireless receiving and dispatching module of an integrated single-chip processor. Processing programs in the single-chip processor comprise a set top box data communication program, a protocol conversion program, a wireless network program and a temperature data processing program. Hardware and operation system are arranged in the set top box. The intelligent home central control program and the intelligent home operation application program are set in the set top box. The complex intelligent home central control device is transformed into a hardware form of the U shield, so that the intelligent home central control function is achieved at the lowest cost, and intelligent life is experienced at the lowest cost.

Owner:SHANGHAI FAME INTELLIGENT TECH

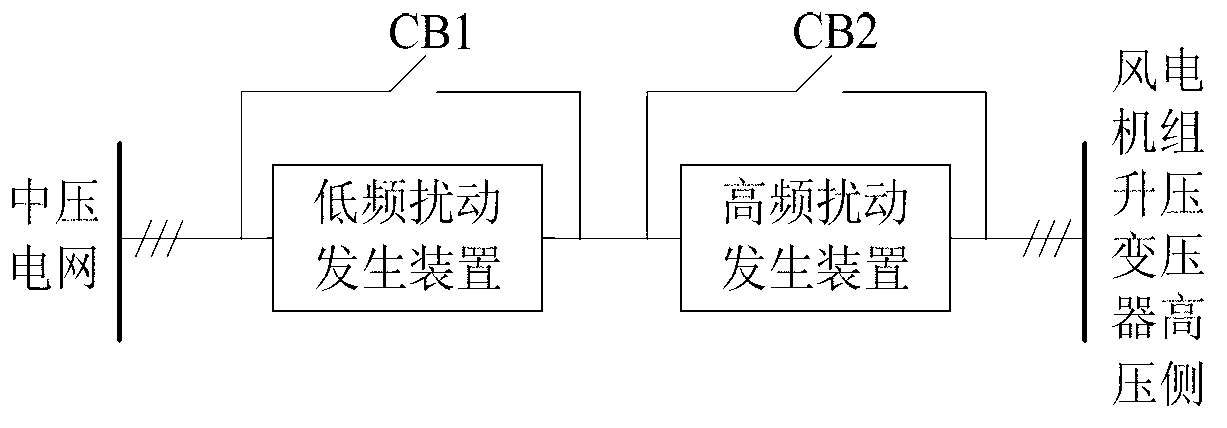

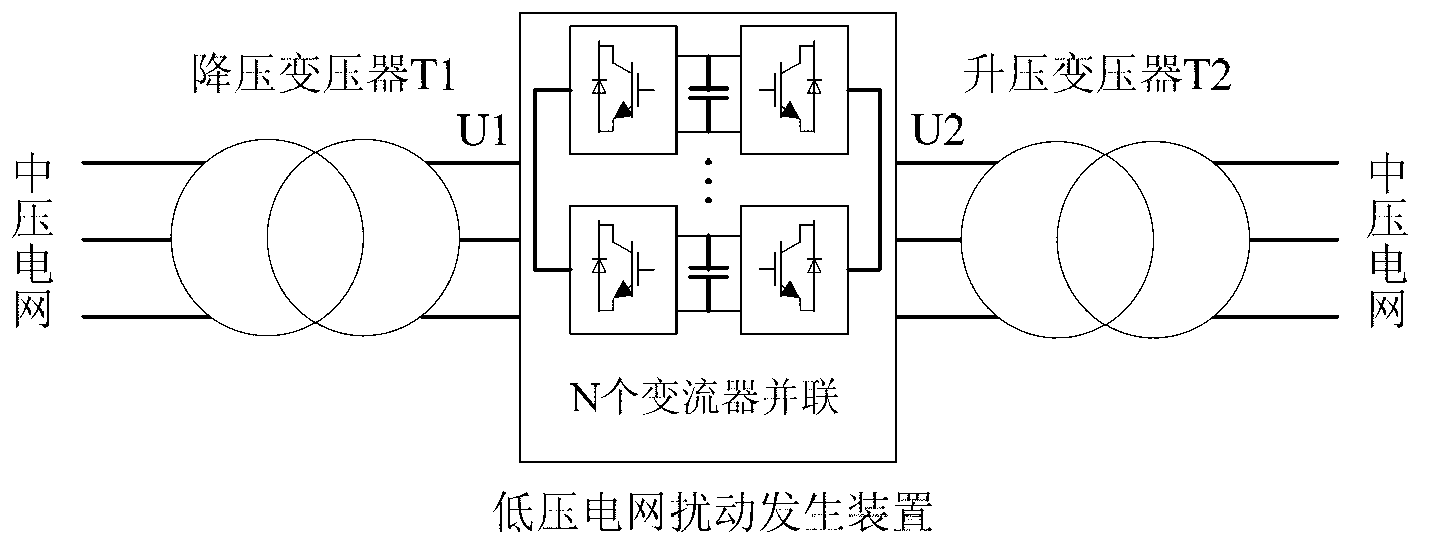

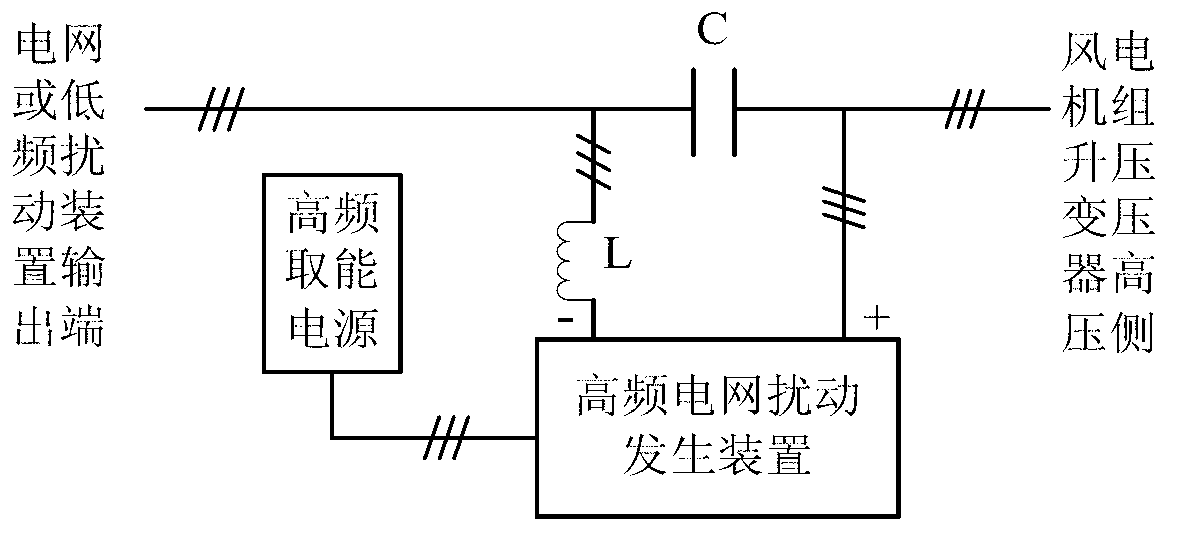

Power grid adaptability testing system of mobile wind turbine generator

ActiveCN103257314AHighly integratedImplement mobile testingClimate change adaptationWind energy generationTerrainTransformer

The invention relates to the field of new energy connecting and controlling, in particular to a power grid adaptability testing system of a mobile wind turbine generator. The power grid adaptability testing system comprises a power grid disturbance generating device and an integrated measuring and controlling device which are connected through an optical fiber, and the power grid disturbance generating device is connected between a medium-voltage power grid and the high-voltage side of a boosting transformer of the wind turbine generator. The power grid disturbance generating device and the integrated measuring and controlling device are mounted in a container after being integrally designed. A radiating system is arranged inside the container, and the radiating system comprises a water cooling device and an air cooling device. According to the power grid adaptability testing system of the mobile wind turbine generator, on-line real simulation is conducted on the high-voltage side of the boosting transformer of the wind turbine generator to generate common power grid disturbance, the actual operation data of the wind turbine generator is collected and analyzed, and the power grid adaptability of the wind turbine generator is experimented and evaluated. A mobile structure enables the power grid adaptability testing system to be transported and mounted among different wind power plants conveniently, and the difficult problems of field test and measurement of the power grid adaptability of the wind turbine generator under the conditions of complex terrains and traffic are solved.

Owner:CHINA ELECTRIC POWER RES INST +2

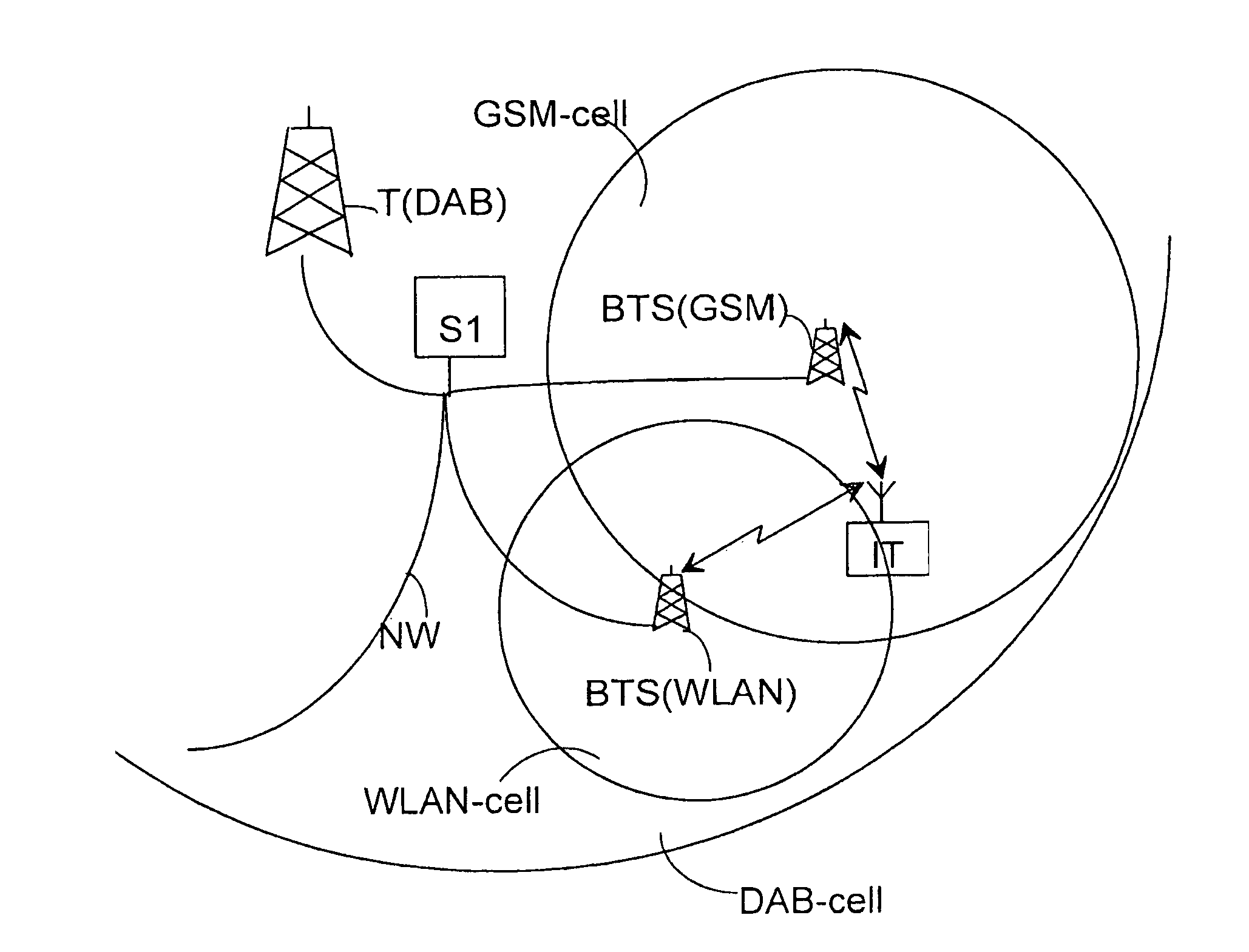

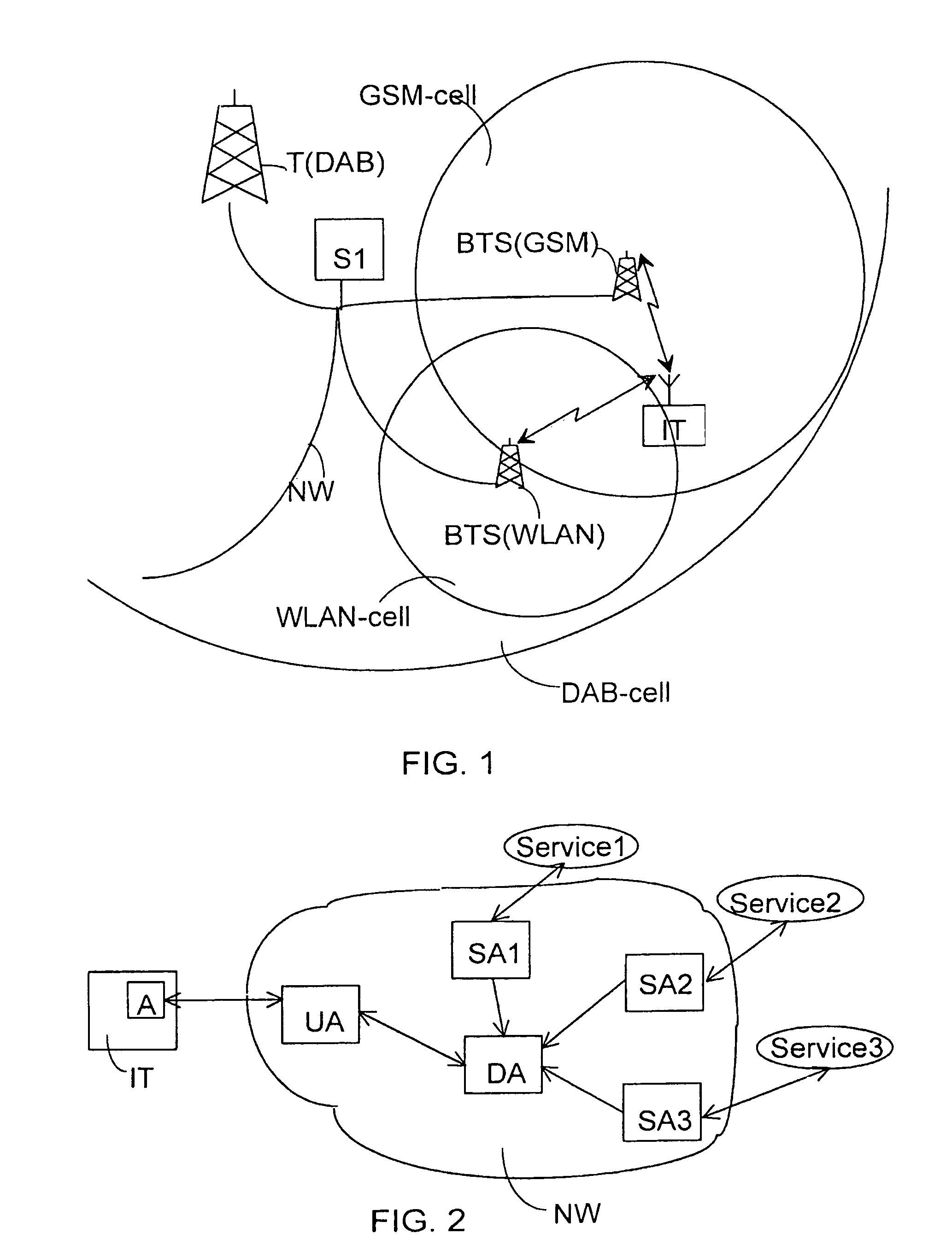

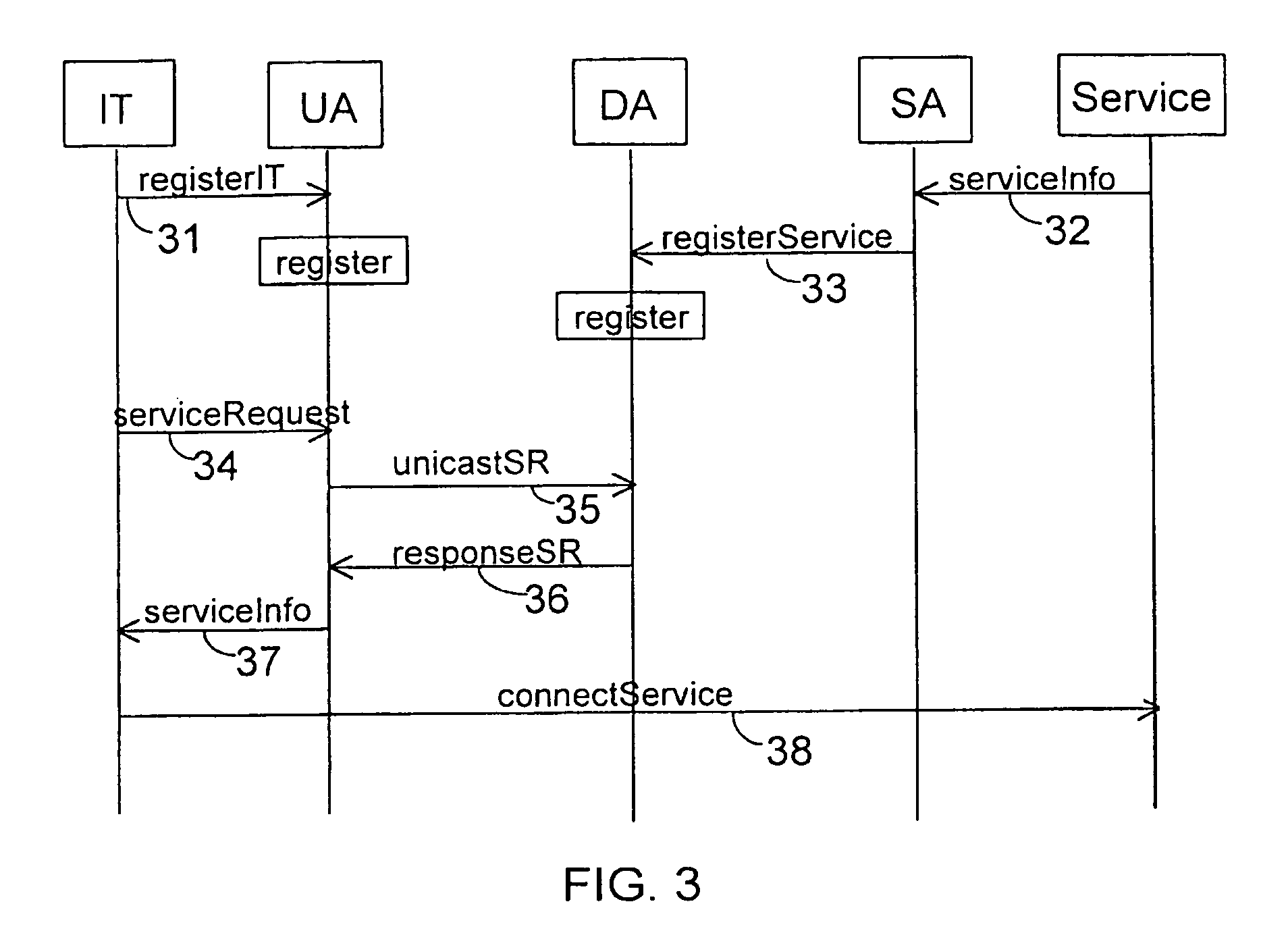

Centralized management of telecommunications parameters

InactiveUS7953407B1OptimizationFlexible expansionSubstation equipmentCommunication jammingTransceiverTelecommunications link

A method of managing telecommunications parameters in a telecommunications system which comprises base transceiver stations of several wireless telecommunications networks and a terminal which is capable of establishing a wireless data transmission connection to said base transceiver stations wherein the base transceiver stations are connected to a fixed network which comprises a server for storing services and telecommunications parameters transmitted by the base transceiver stations of the telecommunications networks.

Owner:DOMIRAS

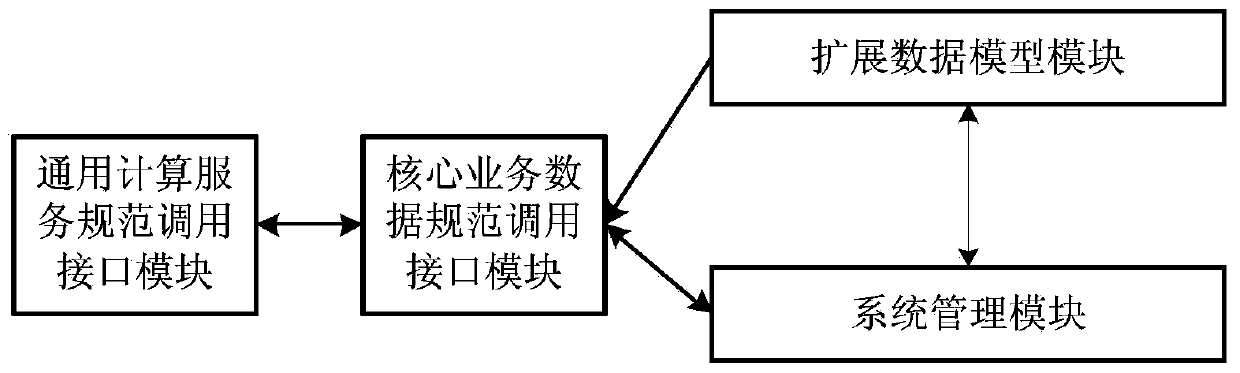

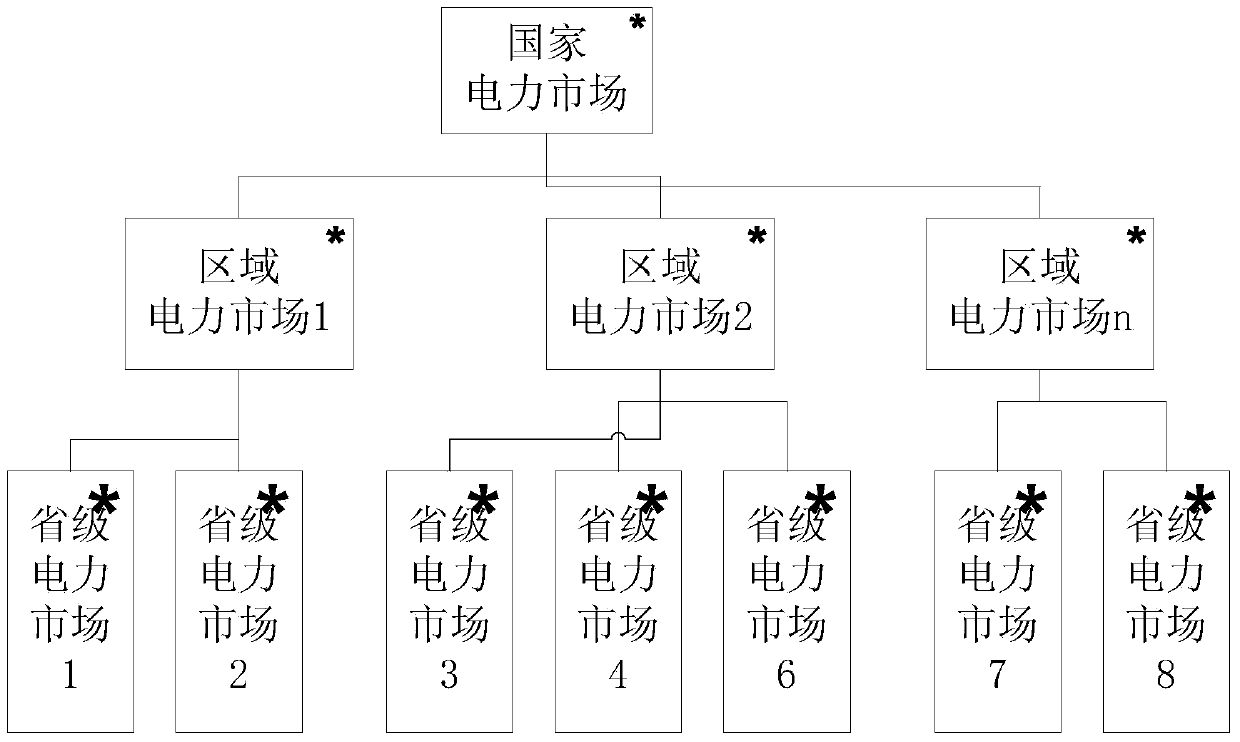

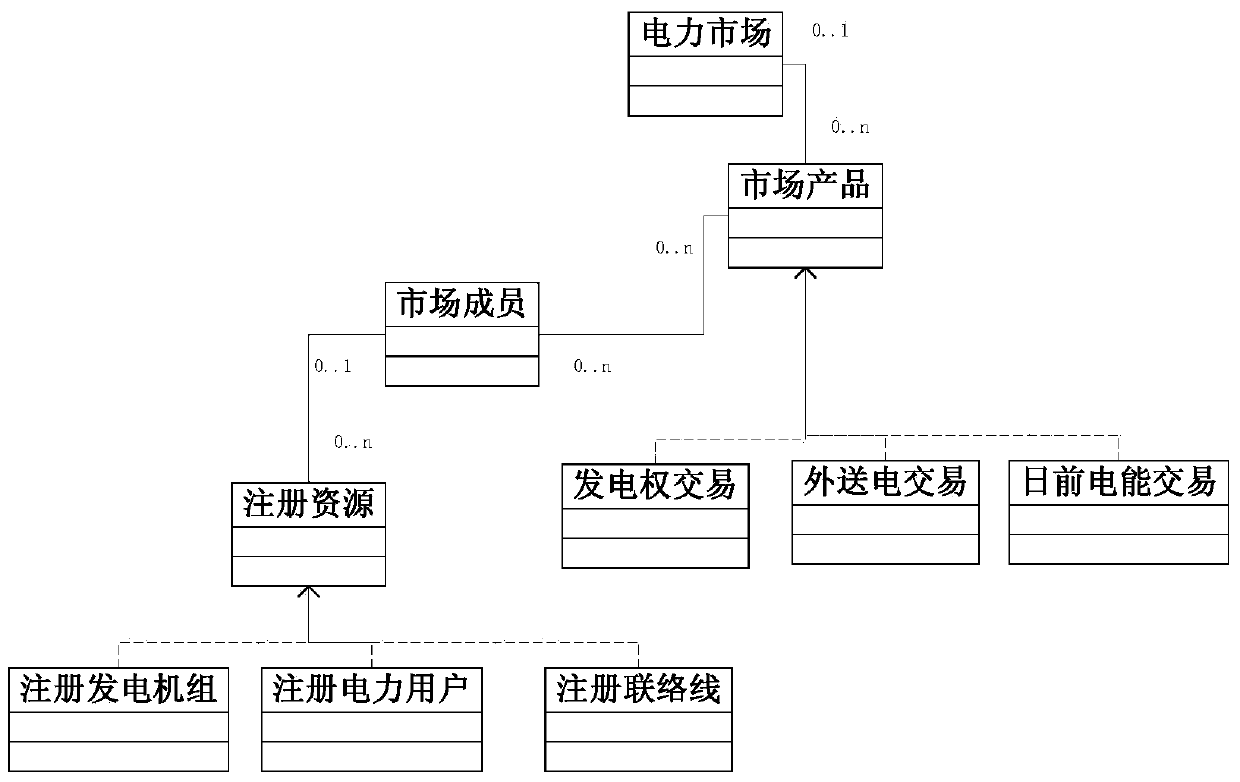

Centralized operation system adapted to multiple electricity markets

InactiveCN103473711AFlexible expansionImplement automatic instantiationData processing applicationsGeneral purposeSystems management

The invention provides a centralized operation system adapted to multiple electricity markets. The system comprises a system management module, an extended data model module, a core service data specification calling interface module and a general-purpose computing service specification calling interface module, wherein the system management module interacts with a user and is used for controlling all the modules to carry out scene configuration according to the service type selected by the user, processing the service request of the user and returning the processing result to the user; the extended data model module is used for storing the corresponding relation between the types of transaction and the members of the market in an electricity market model; the core service data specification calling interface module is used for providing interfaces of all service processing processes; the general-purpose computing service specification calling interface module is used for providing a computing service calling interface in the electricity market service processing process. The centralized operation system adapted to the multiple electricity markets can support the concurrent operation of the multiple electricity markets on the same platform, thus being suitable for the integration and the unified operation of the electricity markets in a larger scope.

Owner:STATE GRID CORP OF CHINA +1

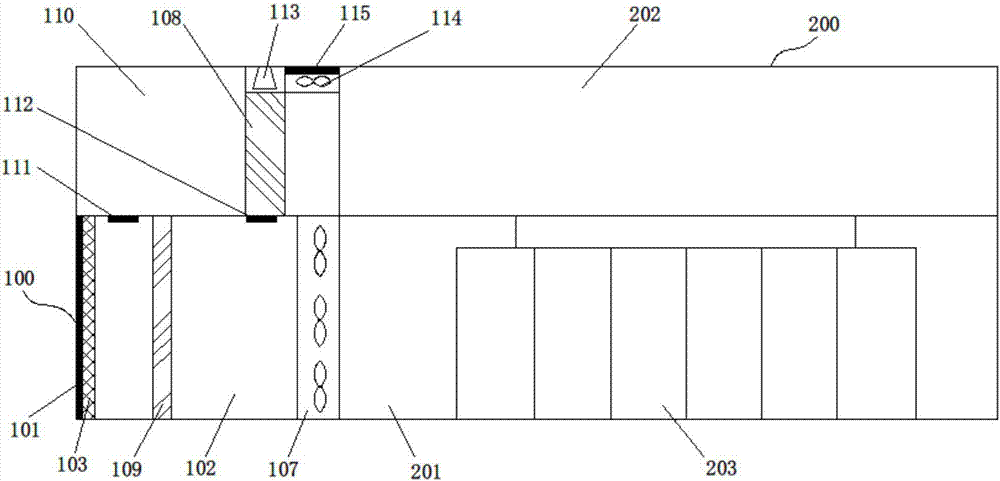

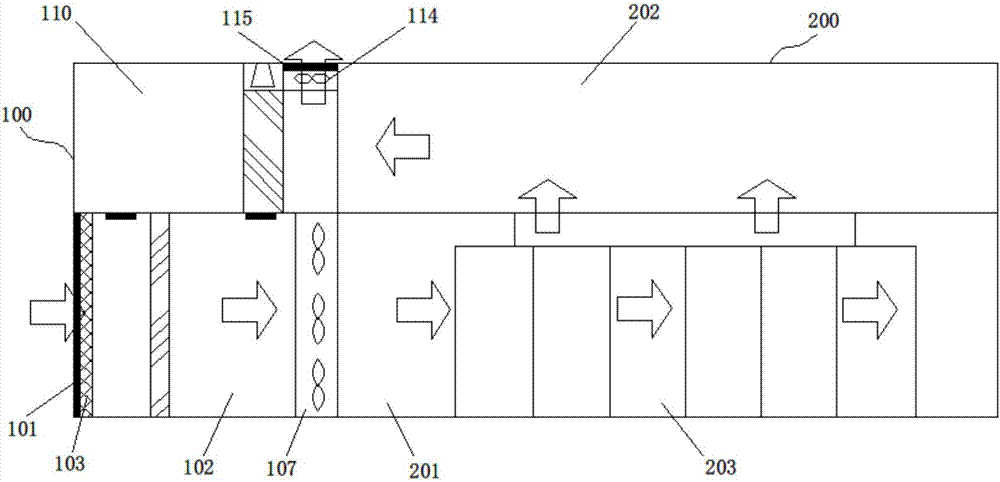

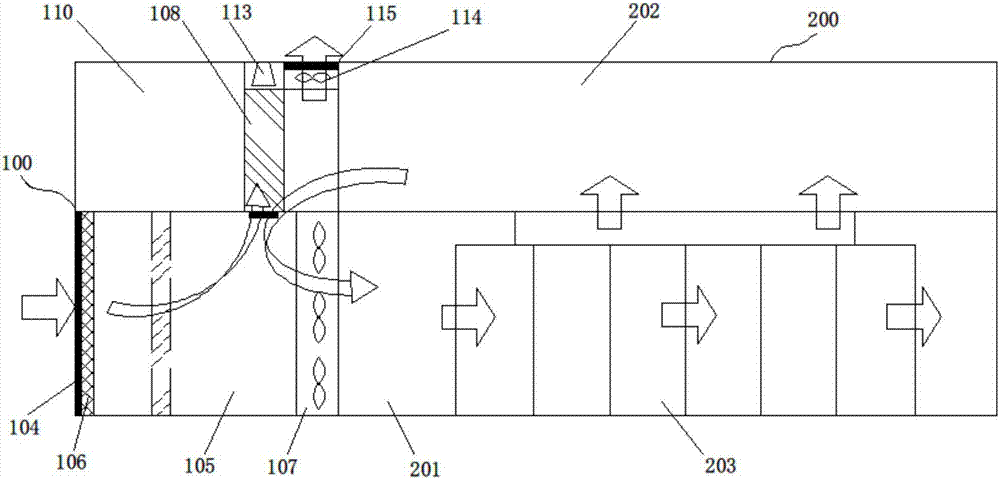

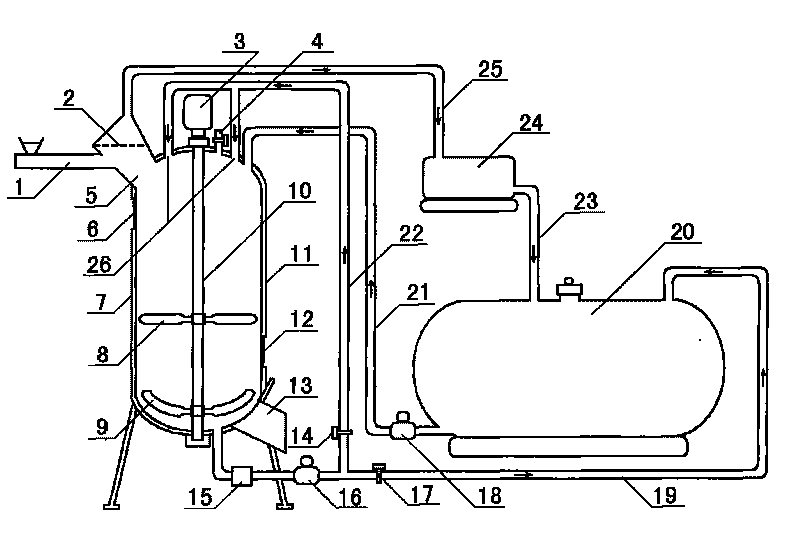

Outdoor modular refrigerating module and installation method thereof

ActiveCN107461836AImprove construction efficiencyReduce on-site construction workloadLighting and heating apparatusAir conditioning systemsRefrigerationWaste management

The invention provides an outdoor modular refrigerating module used for conducting refrigeration on a cabinet module. The cabinet module comprises a shell, wherein the side face of the shell is provided with an opening, and the shell is internally provided with a cold channel and a hot channel which are isolated through a cabinet. The refrigerating module comprises a case and a refrigerating module body arranged in the case, wherein the case is provided with an air inlet, an exhaust outlet and an air outlet which is connected with the opening in the shell in a butted manner, and the refrigerating module body comprises an air inlet cavity which communicates the air inlet with the cold channel, an air return cavity which communicates with the hot channel, a direct air inlet unit which is arranged at an inlet of the air inlet cavity, an air wall unit which is arranged at an outlet of the air inlet cavity and an air exhaust unit arranged at the exhaust outlet. The refrigerating module is manufactured, assembled and adjusted in a factory in advance and then conveyed to the scene, and then butt-joint installation of the refrigerating module and the cabinet module is completed, so that the building efficiency of a refrigerating system is greatly improved, the on-site construction workload is reduced, and thorough decoupling with a machine room is achieved.

Owner:TENCENT TECH (SHENZHEN) CO LTD

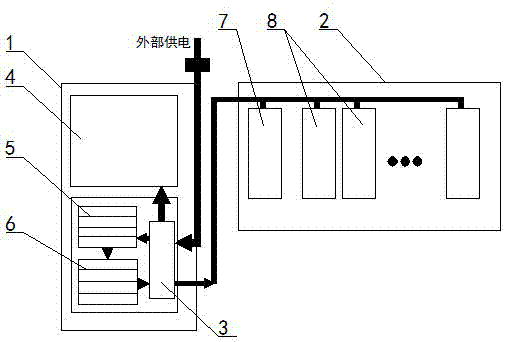

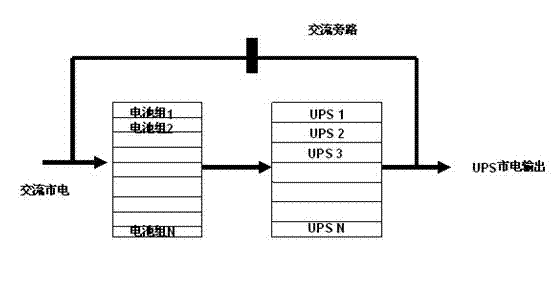

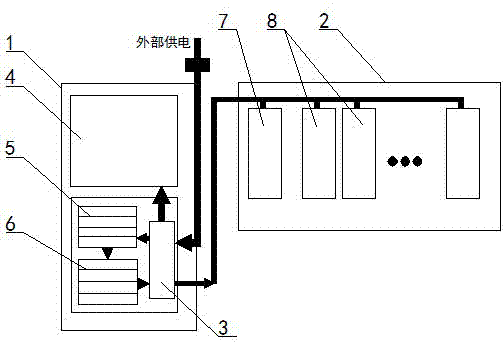

Power supply method for container data centre

InactiveCN102403778AFlexible Power Distribution DeploymentRapid positioningBatteries circuit arrangementsElectric powerMaintainabilityData center

The invention discloses a power supply method for a container data centre, belonging to a data centre power supply technology. The method comprises the following steps: a step that a head power distribution cabinet is used to distribute an external power supply into a water cooling unit power supply part and an auxiliary power supply part, wherein the auxiliary power supply part provides alternating-current input to an IT (Information Technology) device power supply part by a distribution electric cabinet; the water cooling unit power supply part provides electric energy to a refrigerating system for the container data centre; the IT device power supply part provides electric energy to a server system and a storage system which form a data processing core unit; and the auxiliary power supply system part provides redundancy to the whole system, so that the whole container data centre system can be ensured to continue the power supply work by the auxiliary power supply system after the external electric supply has a power failure. Compared with the prior art, the power supply method for the container data centre has the characteristics of flexible power distribution, strong maintainability and the like, and has a very good popularization and application value.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

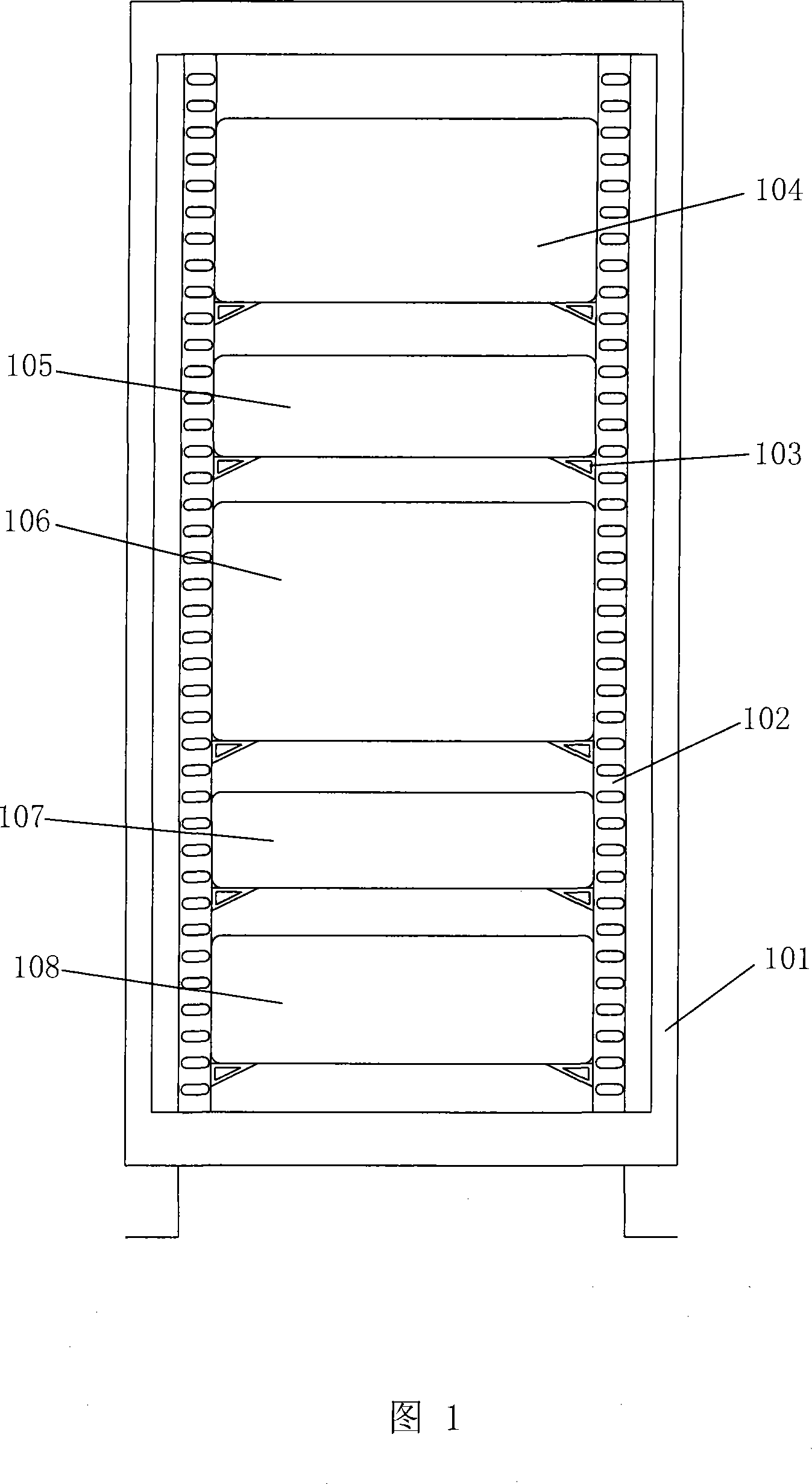

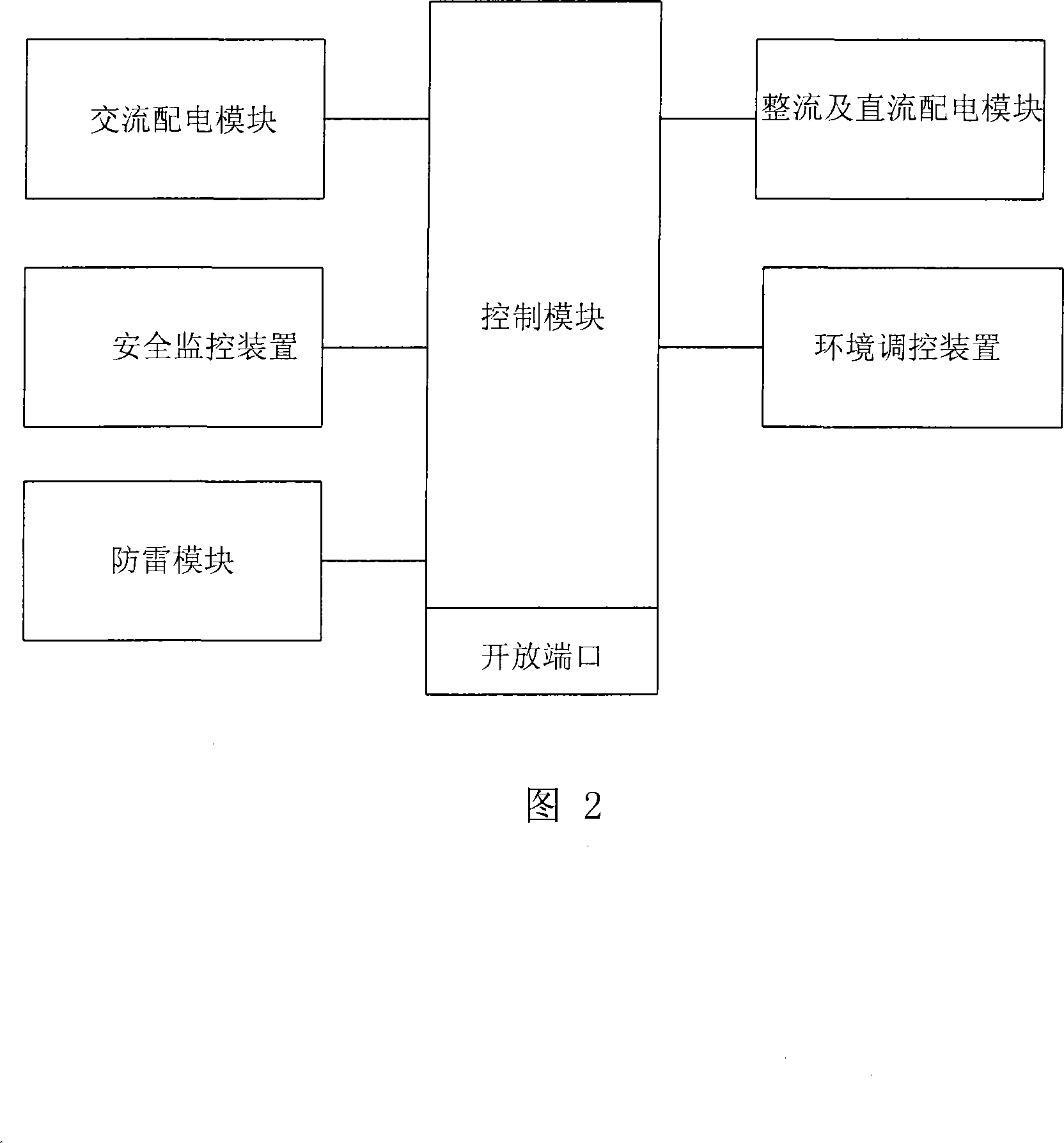

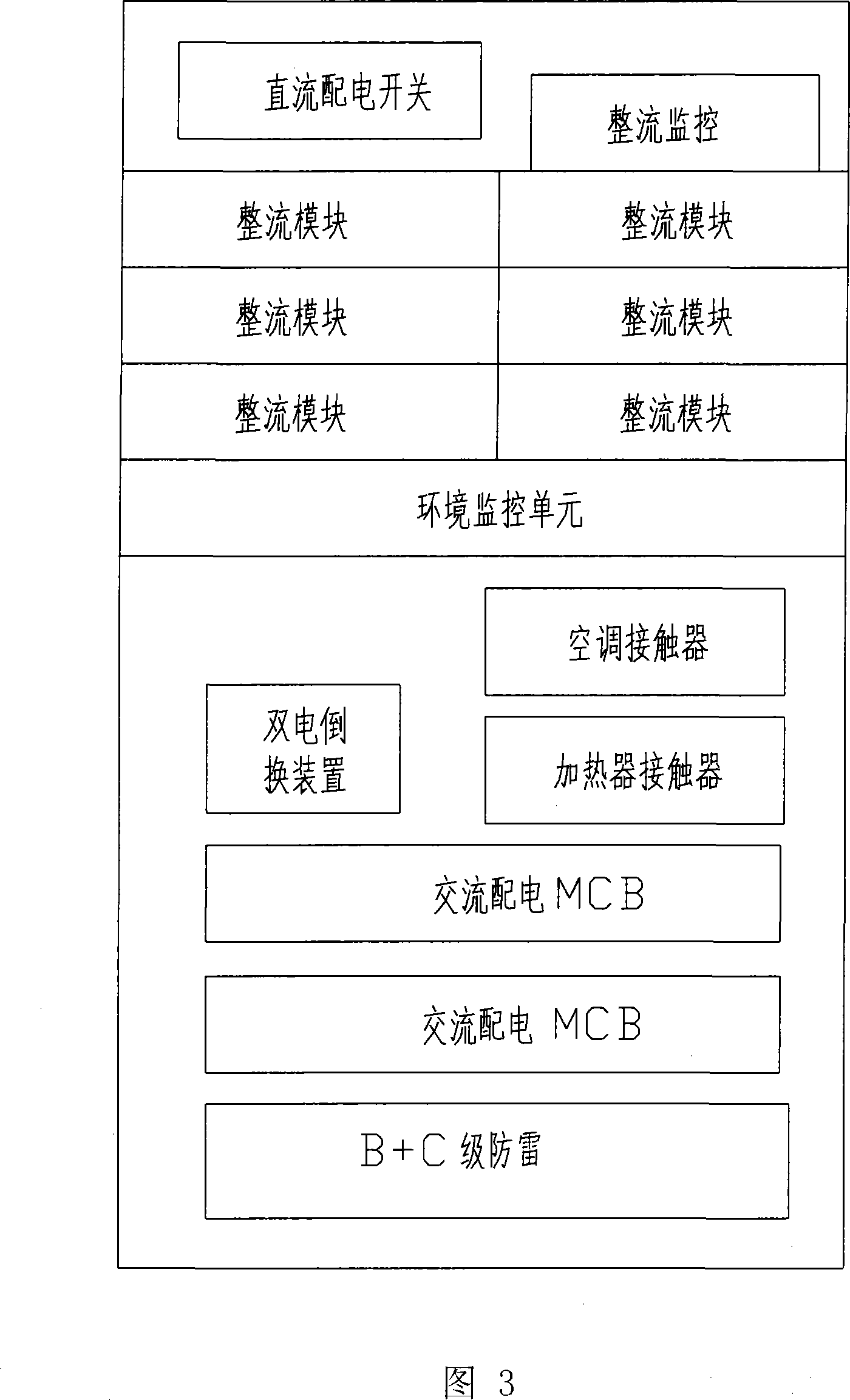

Integrated monitoring system integration

The invention relates to communication device, in particular to an outdoor room / cabinet circulated control energy integral detect system, comprising a cabinet, in which a distributing module and a control module are arranged, wherein the control module is electrically connected with the distributing module to detect the distributing module, the control module is electrically connected with an environment adjuster in the room, to detect the temperature and humidity, the control module comprises an open port and a protocol for communicating with a superior device, the distributing module and the cabinet, the control module and the cabinet are detachably connected, the distributing module is direct-current distributing module and / or alternative-current distributing module. The detachable connection is drawer connection. The open port is 485-interface, and / or 422-interface, and / or 232-interface. The invention provides a circulated control energy integral detect system with integrated distributing module and control module.

Owner:SUS TELECOMM

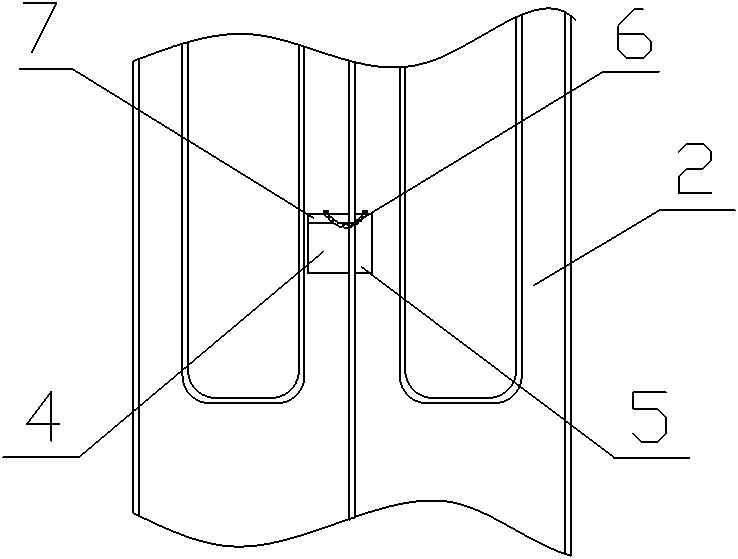

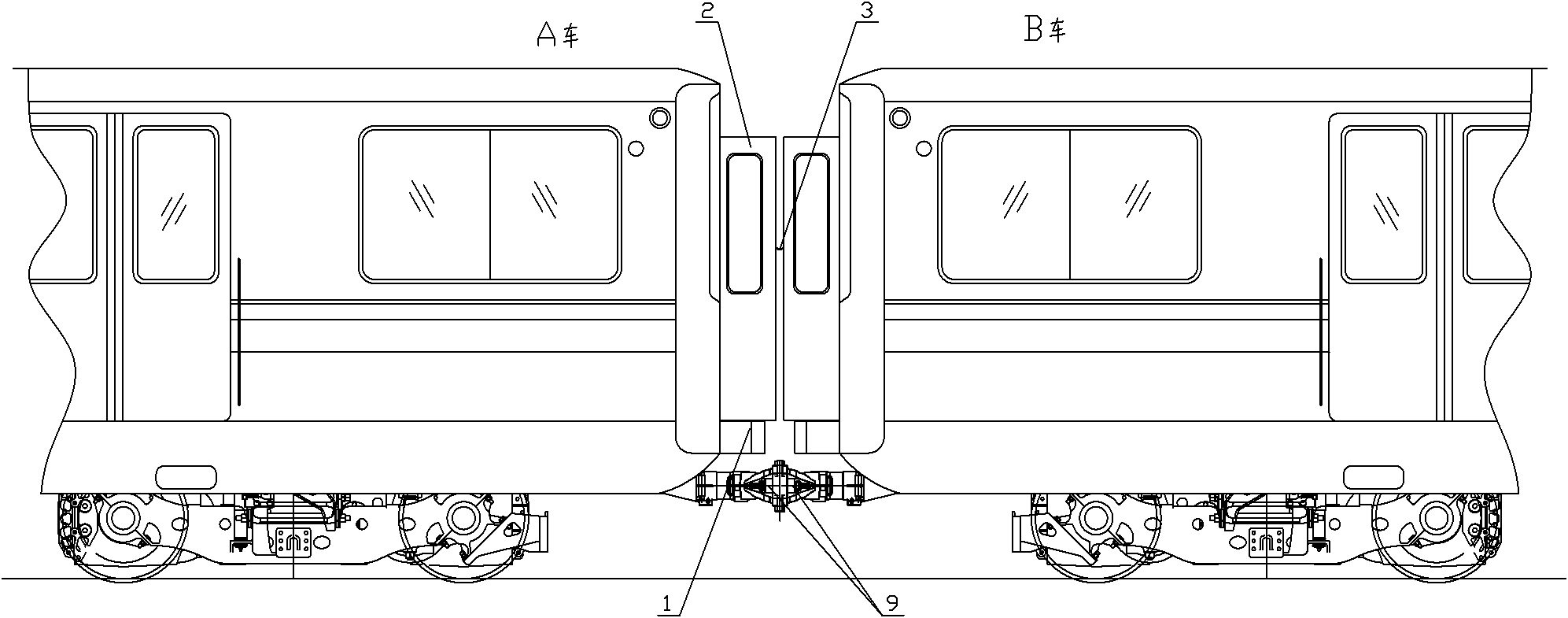

Through type cab emergency door

ActiveCN102303619AEnsure safe passageServe as safety redundancyDoor arrangementAxle-box lubricationEngineeringEmergency evacuation

The invention discloses a through type cab emergency door. A pair of cab emergency end doors capable of being opened oppositely outwards is arranged in the center of the front end of a cab; door lock devices are arranged at the inner sides of the cab emergency end doors; the door lock device comprise a door lock, and a lock groove and a lock chain groove formed at the corresponding positions of two door leaves respectively; a lock chain, the movable end of which is matched with the lock chain groove, is fixed in the lock groove; and a ground arc cab apron extended forwards is arranged at the front end of the cab. When a train is temporarily enlarged, the through type cab emergency door structure of a head vehicle is opened and butted with a through passage of a middle vehicle, or the through type cab emergency door structures of two head vehicles are connected, so that the purposes of transferring or evacuating passengers and temporarily improving the delivery capacity are fulfilled; and if a sudden accident (particularly a subway vehicle catches a fire in a tunnel and the like) happens in the transport process, the through emergency evacuation structure is provided, and the passengers in the fault train can be quickly evacuated to a rescue train, so that life and wealth safety of the passengers is ensured.

Owner:CRRC NANJING PUZHEN CO LTD

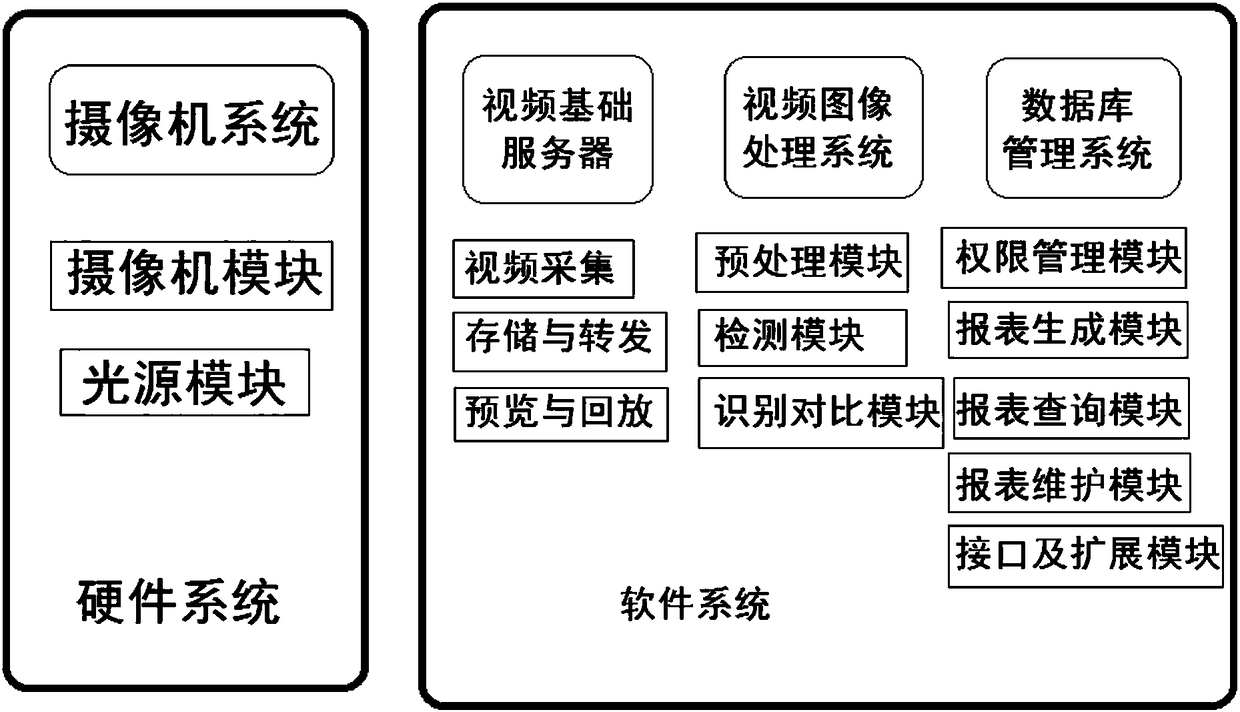

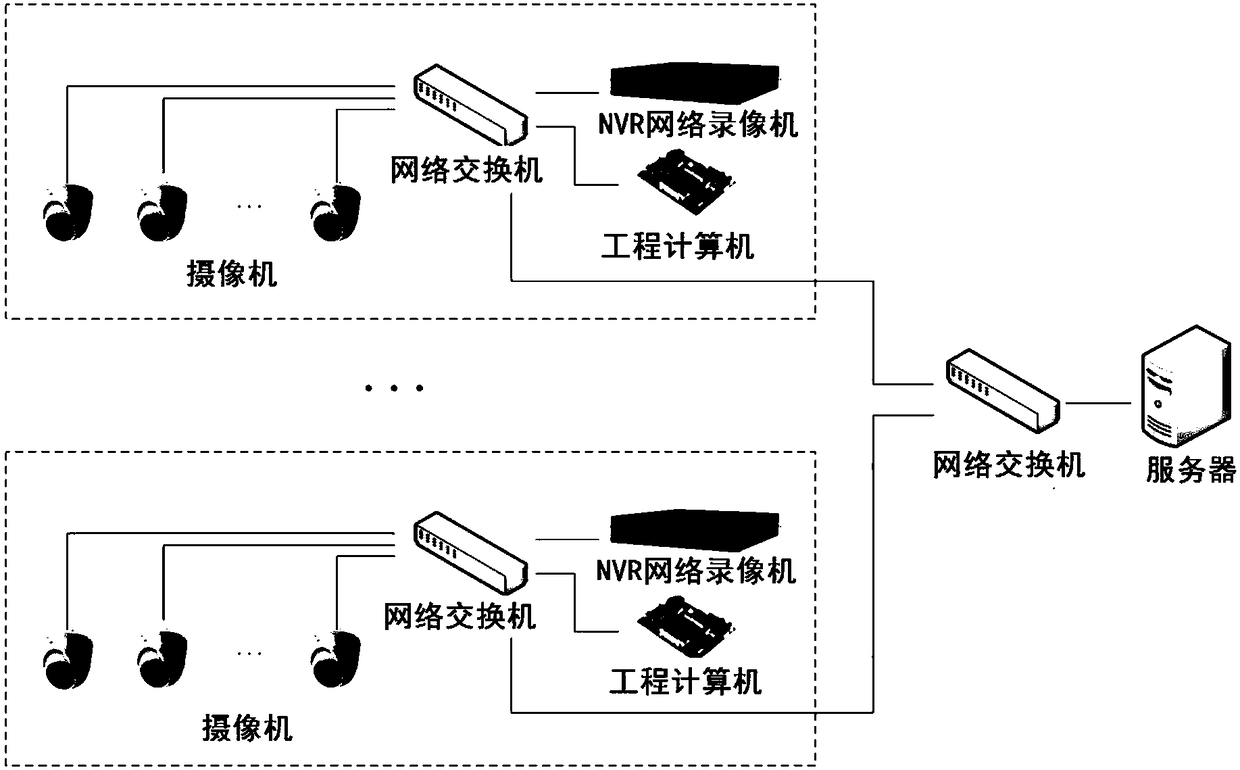

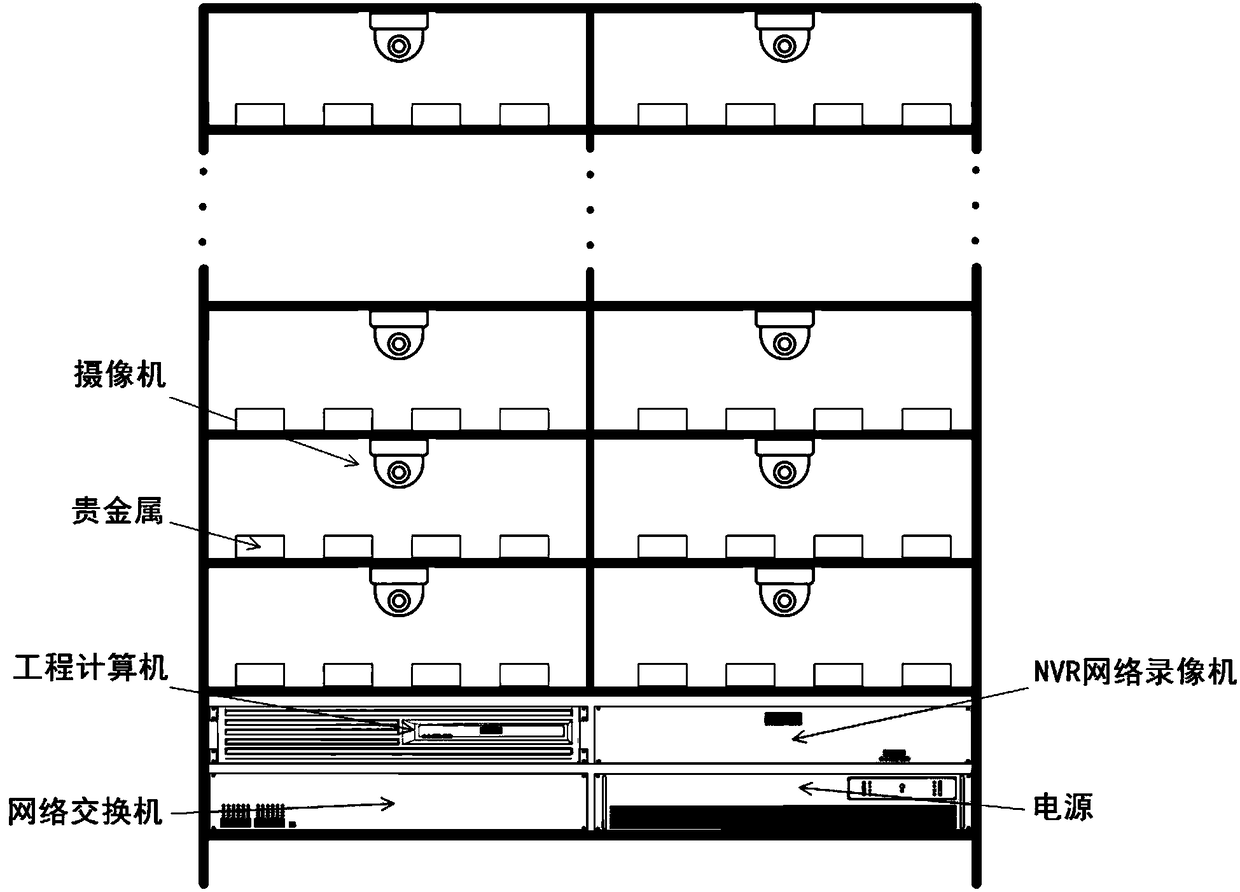

Bank precious metal intelligent inventory management system and method

ActiveCN108550002ARealize electronicFully automatedCharacter and pattern recognitionLogisticsDigital videoData information

The invention relates to a bank precious metal intelligent inventory management system and method. The technical problems of complex operation and low efficiency can be solved by adopting the technical schemes, the technical schemes are as follows: the intelligent bank precious metal inventory system can be built through computer vision, image understanding, industrial automation and database technologies; the system does not depend on any tags, and can perform precise identification on the precious metals with different sizes and shapes (circle, ellipse, rectangle) on shelves in a warehouse by using a digital video camera to simulate human vision to obtain the kind, quantity and position data information of articles placed on the shelves; and dynamic management and automatic update can beperformed on information data by a background warehouse service management system, and precise quantity and category statistics and storage position management of precious metal articles can be accomplished by using supporting application software. The system and method can be used for bank precious metal inventory management.

Owner:GUILIN UNIV OF ELECTRONIC TECH

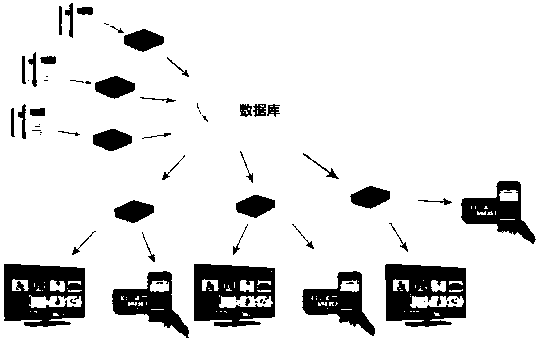

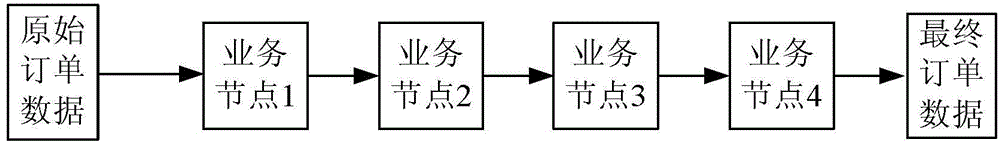

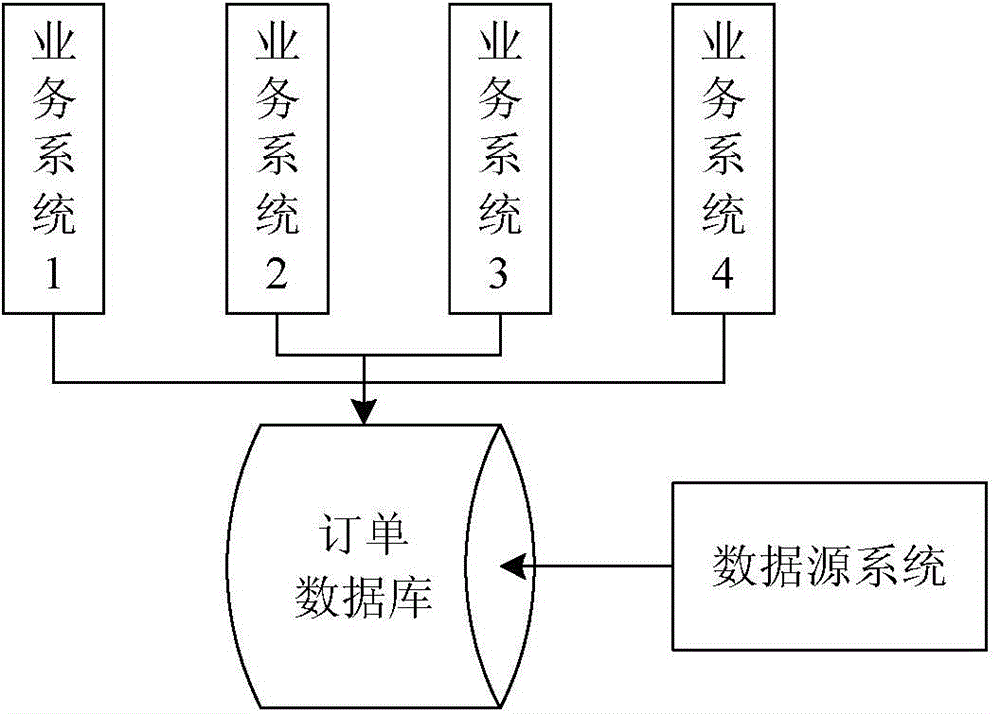

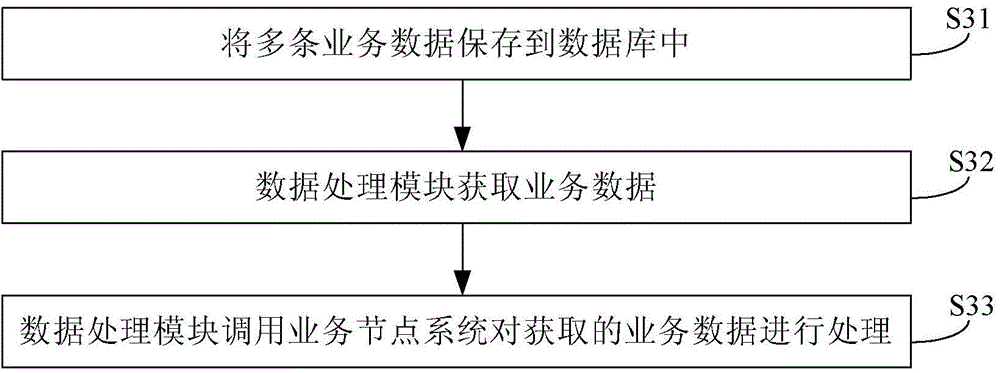

Method and system for processing service data

ActiveCN104391932AFlexible expansionAvoid reading and writing slow or even failureDatabase distribution/replicationWebsite content managementExtensibilityData Applied

The invention provides a method and system for processing service data. The service data can be efficiently and reliably processed, database resources can be reasonably utilized, and the system for processing the service data has high expandability. The method includes the steps of storing the service data in a database; making a data processing module obtain multiple service data applied to the data processing module from the database according to configuration information, wherein the state and the number of the service data corresponding to the data processing module are recorded in the configuration information; sequentially calling all service node systems to process the obtained service data according to the execution sequence of service nodes once the data processing module obtains the state of the service data.

Owner:BEIJING JINGDONG SHANGKE INFORMATION TECH CO LTD +1

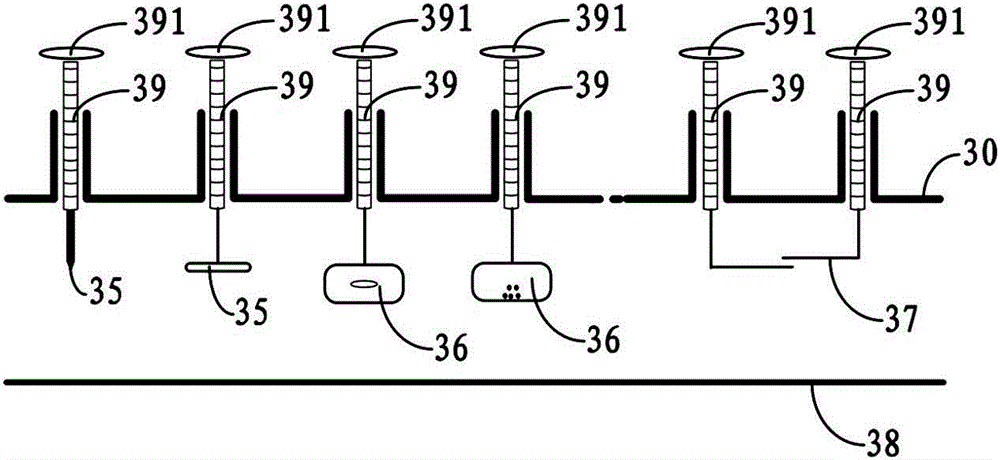

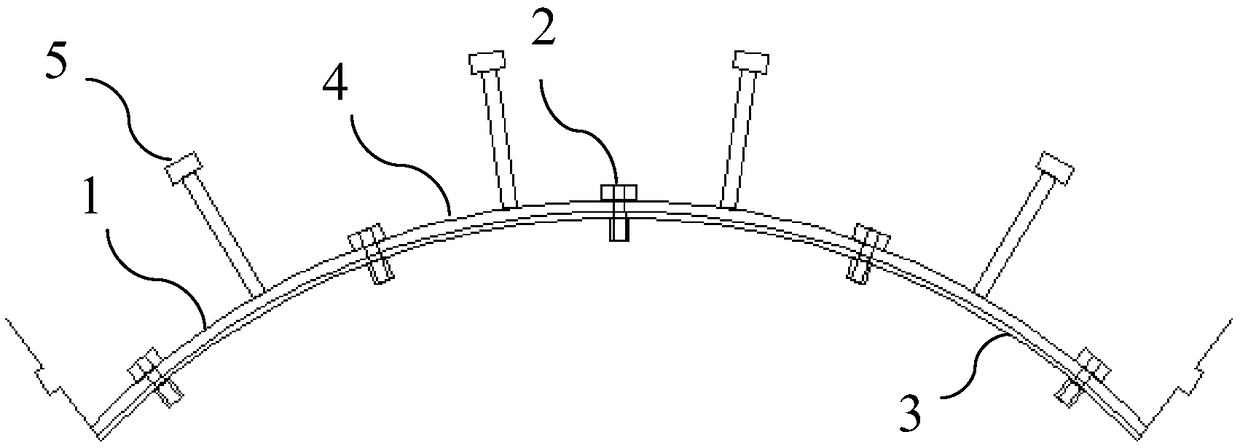

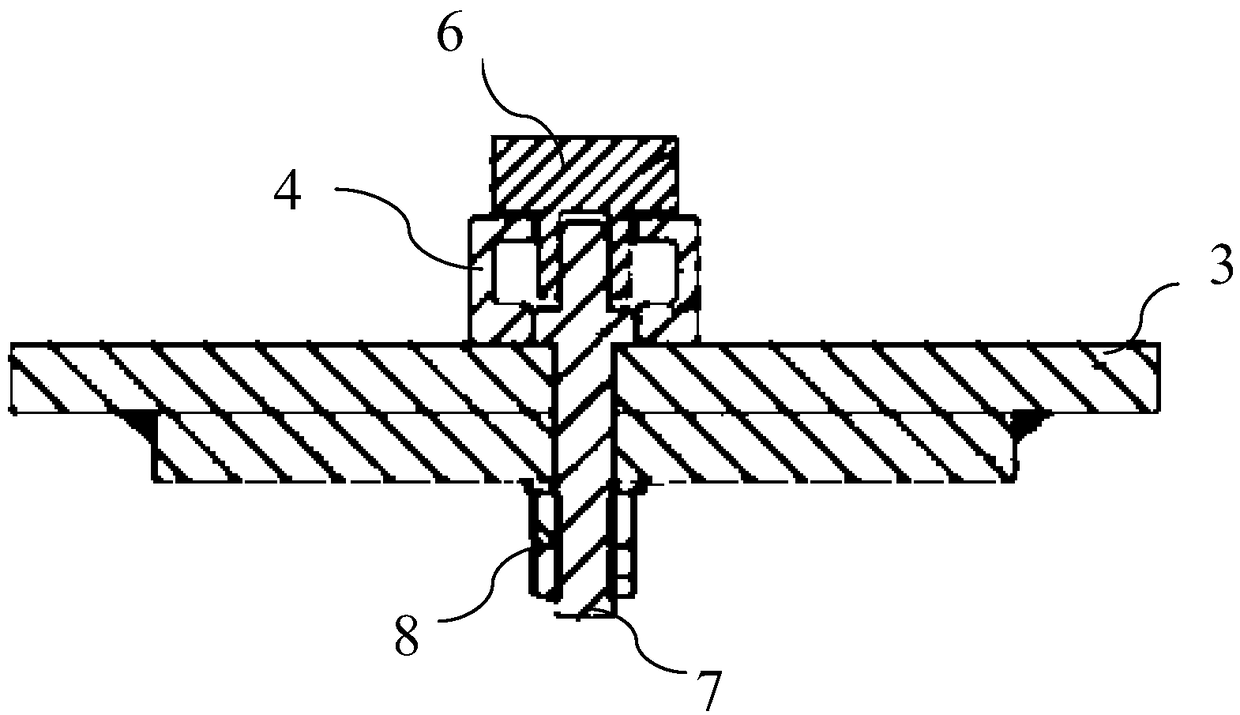

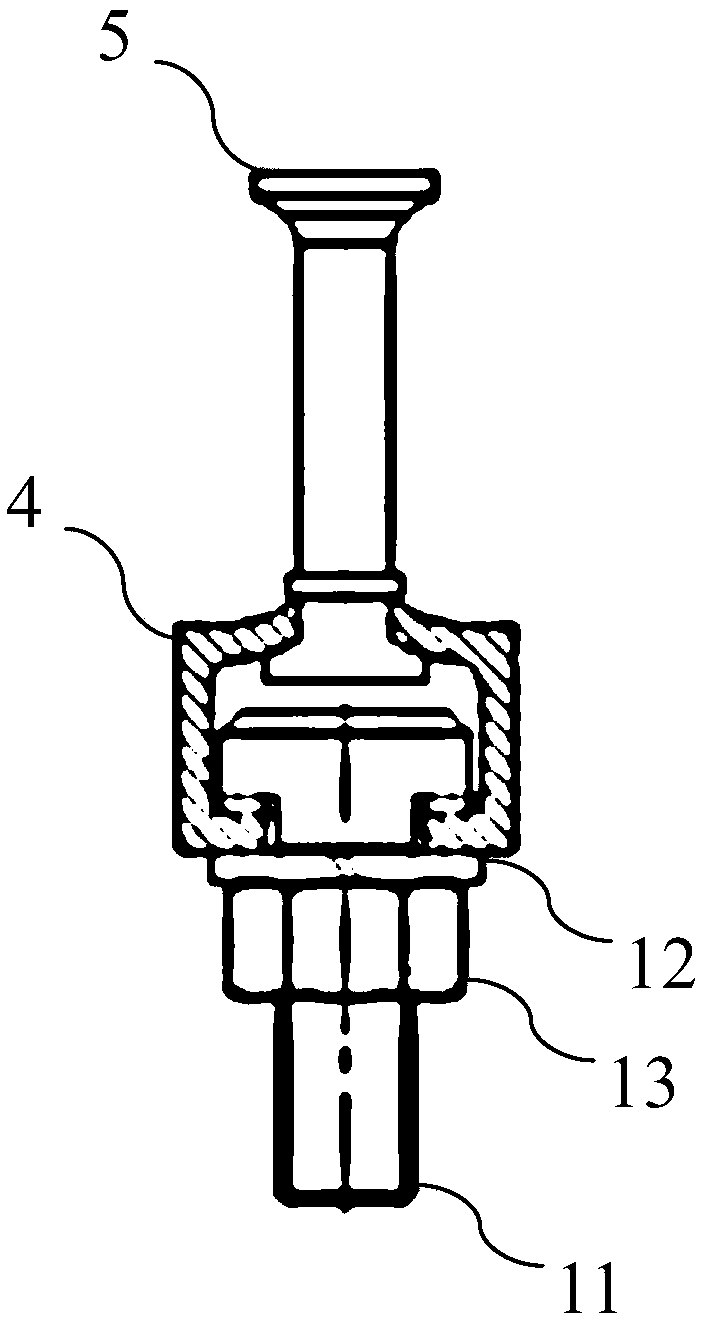

Fixing structure and pre-embedment construction method for pre-embedded channel for duct piece in subway shield zone

InactiveCN109159275AAvoid damageIntegrity guaranteedAuxillary shaping apparatusArchitectural engineeringPre embedding

The invention provides a fixing structure for a pre-embedded channel for a duct piece in a subway shield zone. The pre-embedded channel can be fixedly mounted on a duct piece mold bottom arc plate bythe aid of multiple fixing structures; the pre-embedded channel comprises arc-shaped channel steel and multiple anchor rods fixed to the closed end of the arc-shaped channel steel; each fixing structure comprises a positioning nut, a positioning threaded rod and a locking screw; the positioning threaded rods penetrate through corresponding mounting holes in the arc-shaped channel steel and corresponding positioning holes in the duct piece mold bottom arc plate during mounting; each positioning nut penetrates through the corresponding mounting hole in the arc-shaped channel steel to screw and position one end of the corresponding positioning threaded rod on the closed end surface of the arc-shaped channel steel during mounting; and each locking screw is in threaded connection with the otherend of the corresponding positioning threaded rod in a sleeving manner to lock the other end of the corresponding positioning threaded rod on the duct piece mold bottom arc plate during mounting. Theinvention further provides a pre-embedment construction method for the pre-embedded channel for the duct piece in the subway shield zone. Hole drilling on the duct piece is avoided, the integrity ofthe duct piece structure is guaranteed, and the life of the project is prolonged.

Owner:中铁十二局集团山西建筑构件有限公司 +2

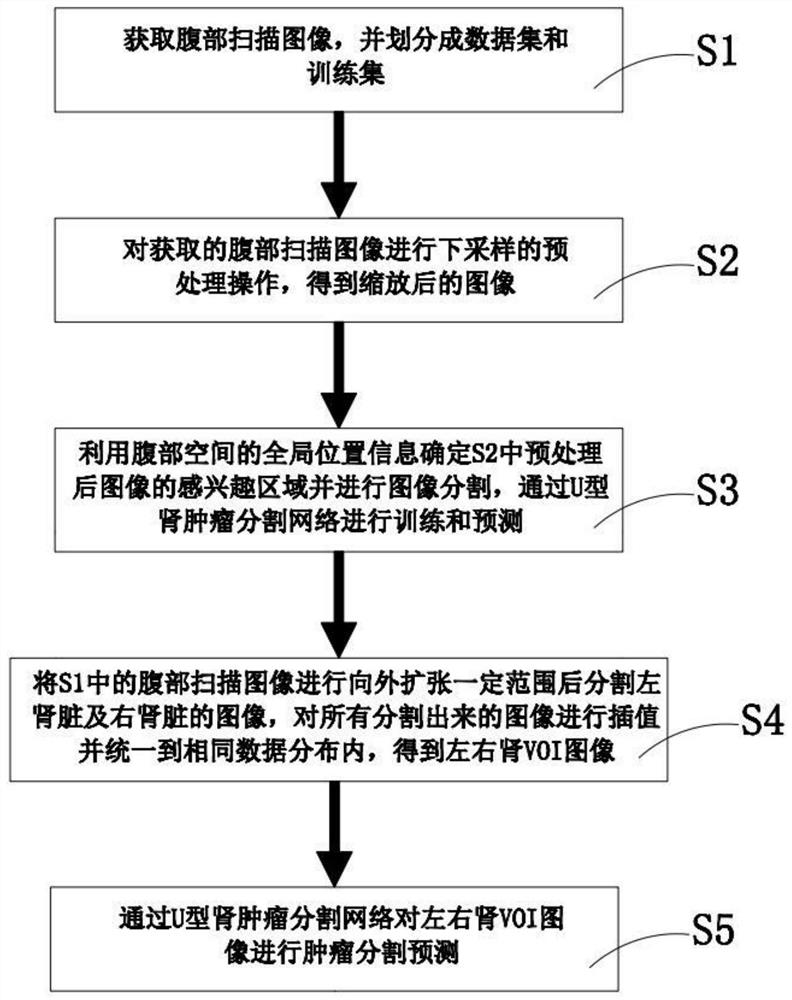

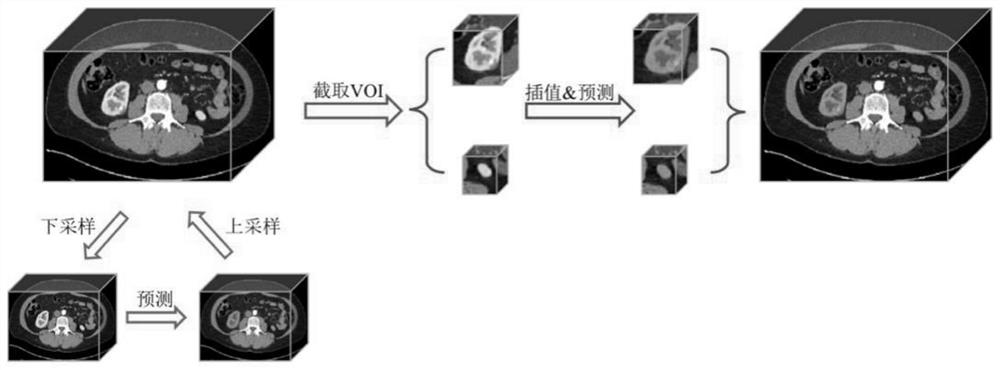

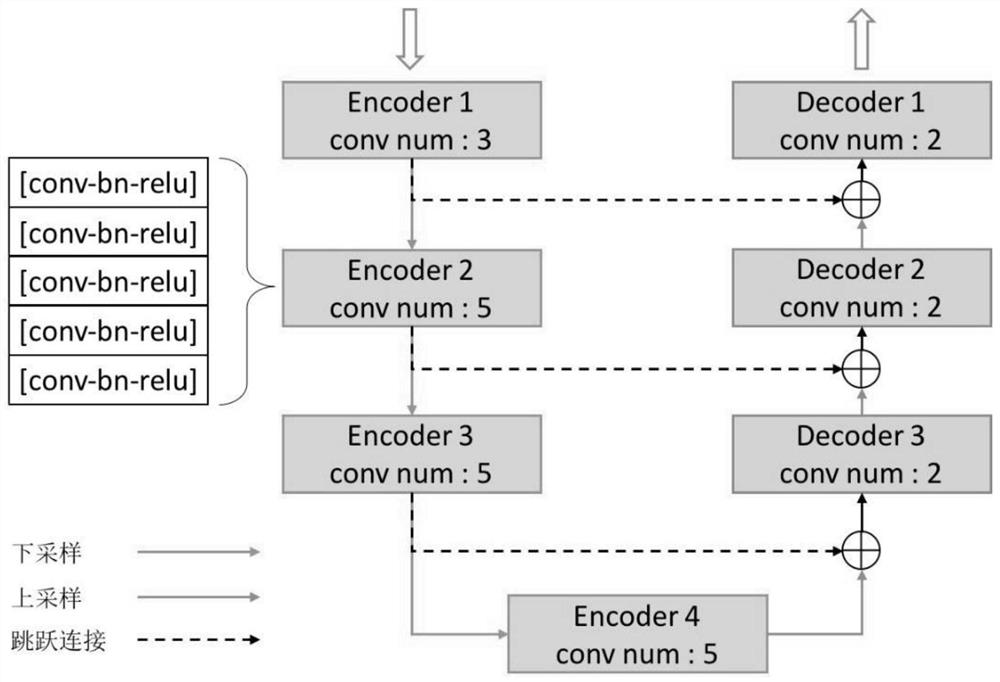

Image segmentation method for kidney tumor

PendingCN112085743ANarrow down the search spaceAvoid interferenceImage enhancementImage analysisImage segmentationImage pair

The invention discloses an image segmentation method for a kidney tumor, and the method comprises the following steps: S1, obtaining an abdomen scanning image, and dividing the abdomen scanning imageinto a data set and a training set; S2, performing down-sampling preprocessing on the acquired abdomen scanning image to obtain a scaled image; S3, determining an area of interest of the preprocessedimage in the step S2 by using global position information of the abdominal space, performing image segmentation, and performing training and prediction by a U-shaped kidney tumor segmentation network;S4, outwards expanding the abdomen scanning image in the step S1 for a certain range, segmenting images of the left kidney and the right kidney, interpolating all segmented images, and unifying the interpolated images into the same data distribution to obtain left and right kidney VOI images; S5, performing tumor segmentation prediction on the left and right kidney VOI images by a U-shaped kidneytumor segmentation network. Interference of other organs and tissues is effectively avoided, the accuracy of kidney tumor identification and image segmentation is improved, and efficiency is higher.

Owner:XIAMEN UNIV

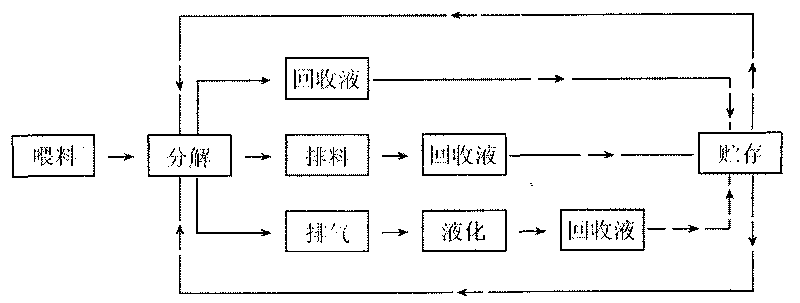

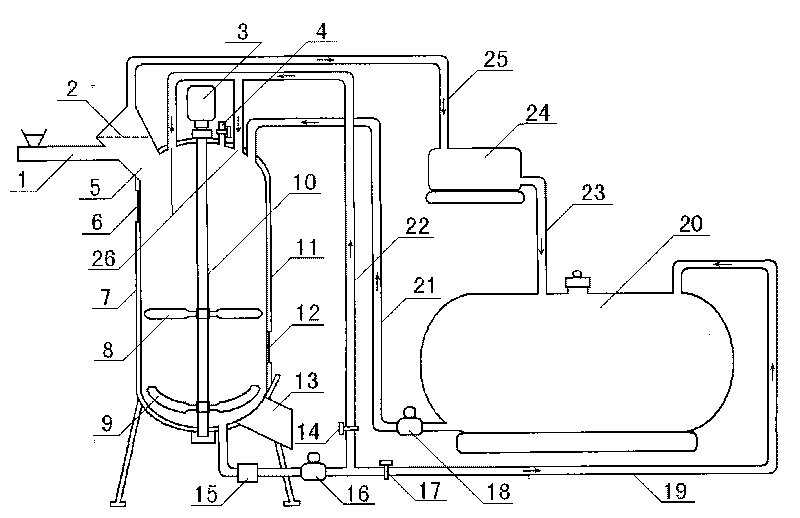

Decomposition process of aluminum composite

The invention discloses a decomposition process of an aluminum composite and relates to the field of the recovery and utilization of waste materials. The process comprises the following steps: delivering a material into an reaction kettle; adding decomposing solution into the material to perform decomposition at 60 to 130 DEG C for 10 to 50 minutes, wherein the weight of the decomposing solution is 2 to 5 times that of the material; and after the decomposition is finished, recovering the decomposing solution and discharging the material. Furthermore, during decomposition, the decomposing solution is pumped by a lower end liquid outlet pump to a plurality of spray openings on the upper end of the reaction kettle to be sprayed in the reaction kettle, and the volatilizing vapor of the decomposing solution is collected to a liquefying and recovering device to be liquefied and recovered; and after the material discharge, the decomposing solution is removed from the decomposed material and collected. The process has the advantages that: the decomposing speed is as high as 3 to 4 times the speed of open decomposition; and pollution is avoided, chemical raw materials recovered after the decomposition are all recycled, and production of any wastewater, waste materials and waste gases is avoided.

Owner:巨锋

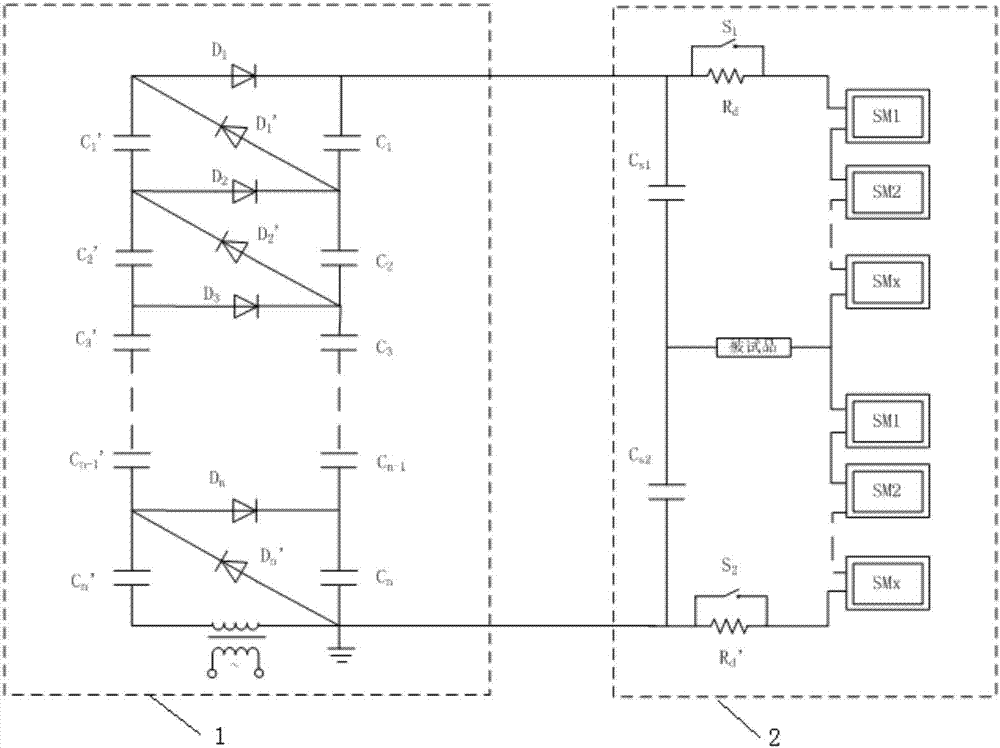

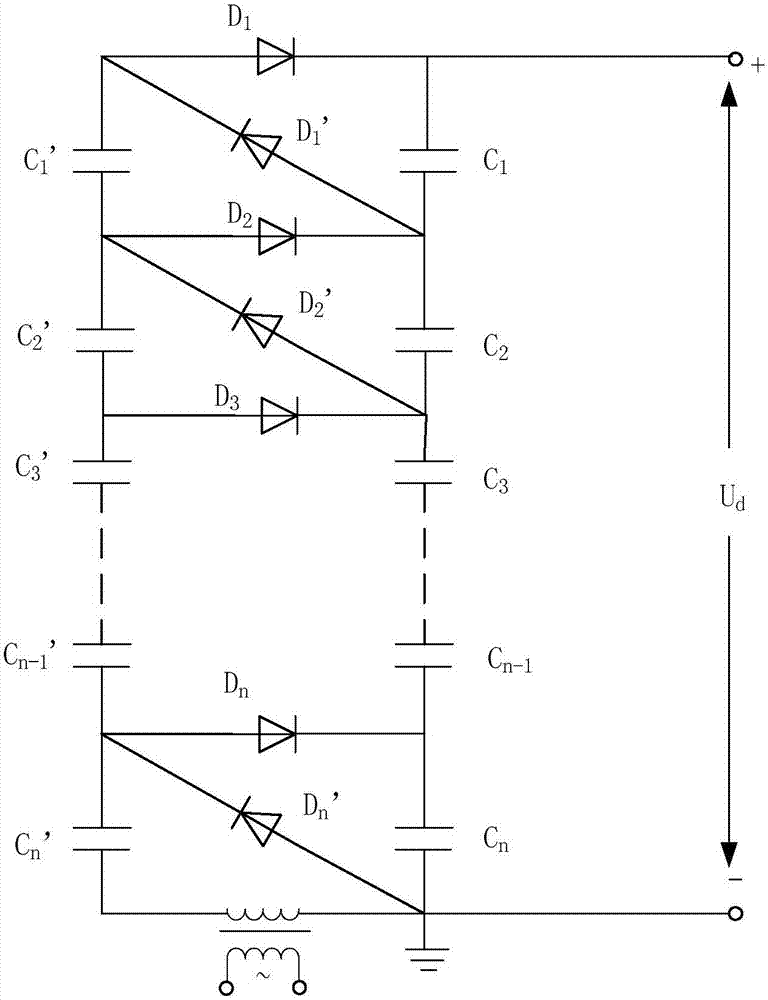

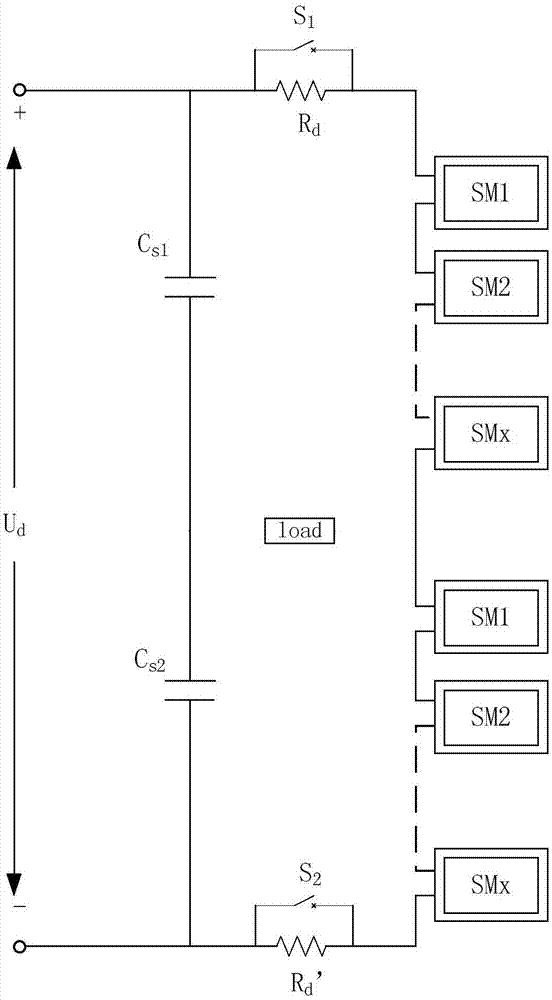

Modular multi-level structure impulse voltage generating device and method thereof

ActiveCN107070289AEasy to expandFlexible controlPulse generation by energy-accumulating elementTest objectModular structure

The invention belongs to the power and electronics technical field and relates to a modular multi-level structure impulse voltage generating device and a method thereof. The device comprises a direct-current power source, a modular multi-level converter and a tested object; the modular multi-level converter is connected with the direct-current power source; and the tested object is connected onto the modular multi-level converter. The impulse voltage generating method includes the following steps of: step 1, charging: before impulse voltage is generated, sub-module capacitors are charged when the tested object is electrically connected with the modular multi-level converter; and step 2, impulse voltage generation: the modulation signals of upper half bridge arms and lower half bridge arms are compared with step waves, so that the control signals of each sub-module can be obtained, and so that required impact voltages can be generated under control. According to the device, full-controlled switching devices are adopted, a modular structure is adopted, and therefore, the device has excellent control performance in an impact voltage generating process and can generate impact voltages of arbitrary waveforms.

Owner:WUHAN UNIV

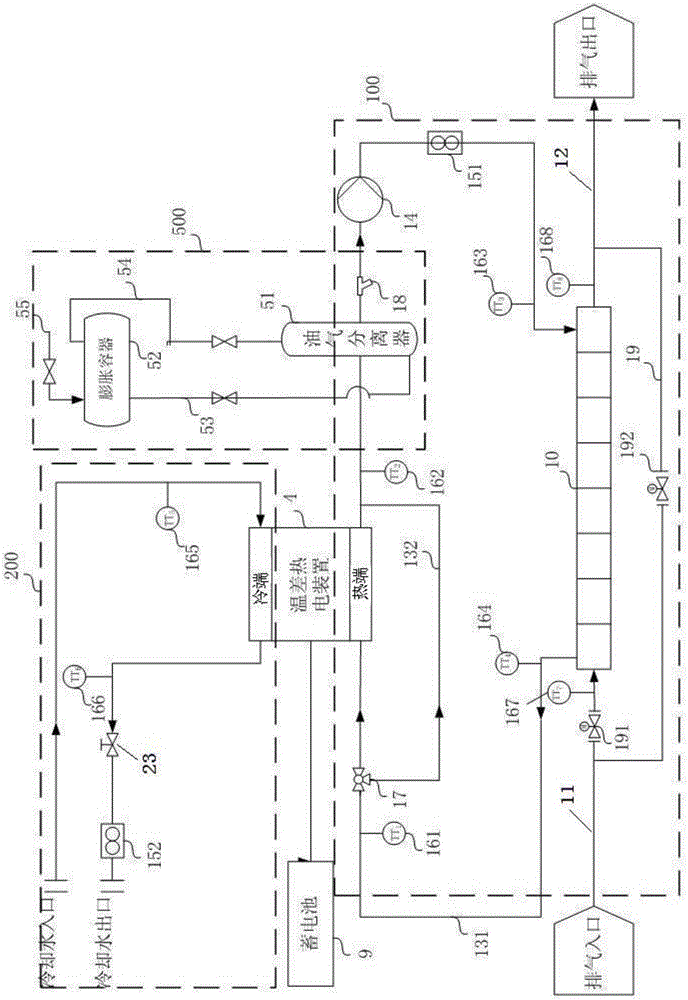

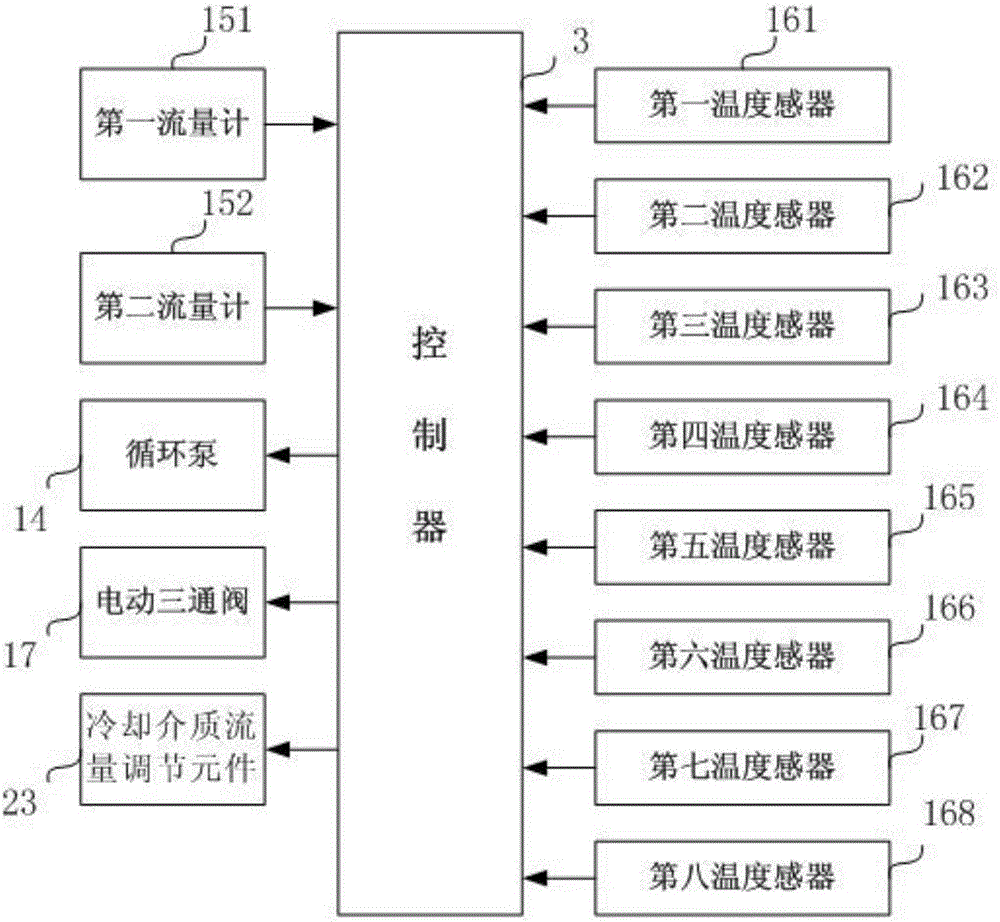

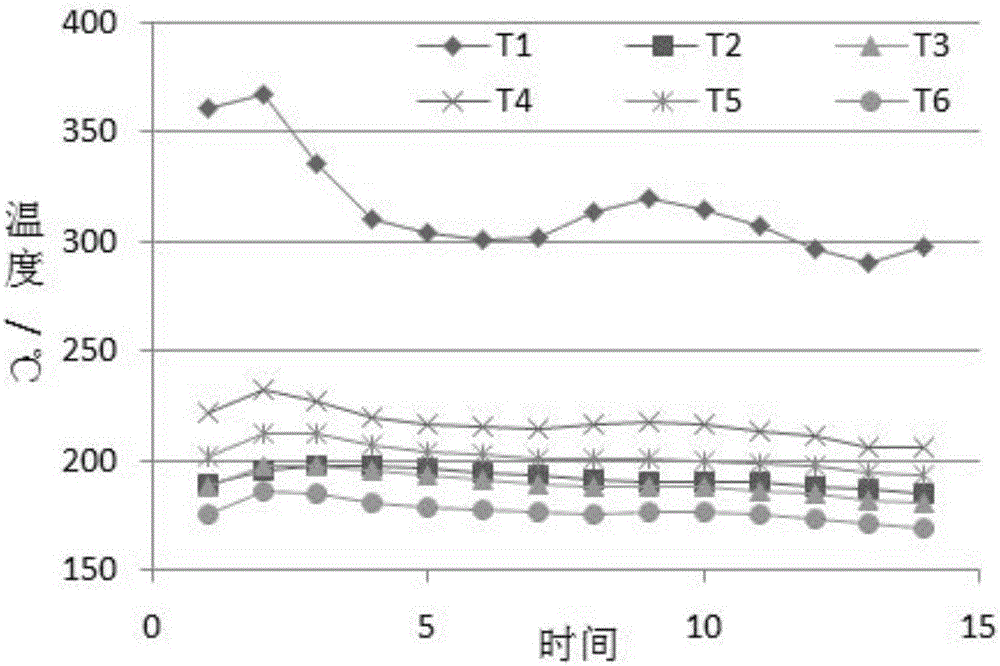

Medium circulation system for exhaust heat indirect type temperature-difference thermoelectric device for marine diesel engine

InactiveCN106523103AGuaranteed uptimeStable outputInternal combustion piston enginesExhaust apparatusHeat conductingEngineering

The invention discloses a medium circulation system for an exhaust heat indirect type temperature-difference thermoelectric device for a marine diesel engine. The medium circulation system comprises a hot-end circulation unit, a cold-end circulation unit and a controller. The hot-end circulation unit comprises a gas-liquid heat exchanger, a gas inlet pipeline, a gas outlet pipeline and a heat-conducting oil circulation pipeline capable of conveying heat-conducting oil to the hot end of the temperature-difference thermoelectric device. The cold-end circulation unit comprises a cooling medium circulation pipeline capable of conveying a cooling medium to the cold end of the temperature-difference thermoelectric device. The controller is used for controlling the flow of the heat-conducting oil and the flow of the cooling medium according to the temperature measurement values of temperature sensors. By the adoption of the medium circulation system for the exhaust heat indirect type temperature-difference thermoelectric device, under the condition of the working condition change of the diesel engine, self-adaptive control over medium circulation of the hot end and the cold end of the thermoelectric element is achieved, it is guaranteed that the temperature of the hot end and the cold end of the temperature-difference thermoelectric device is stable and controllable, and thus the design application and the good power generation output quality of the large-power temperature-difference thermoelectric device can be guaranteed.

Owner:NO 711 RES INST CHINA SHIPPING HEAVY IND GRP

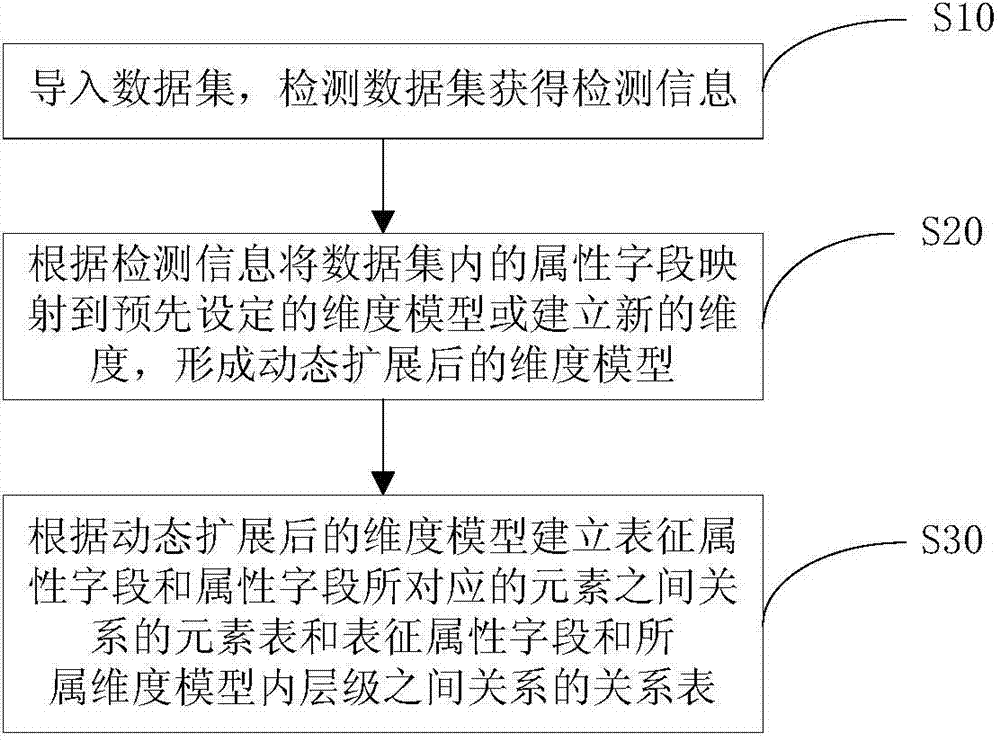

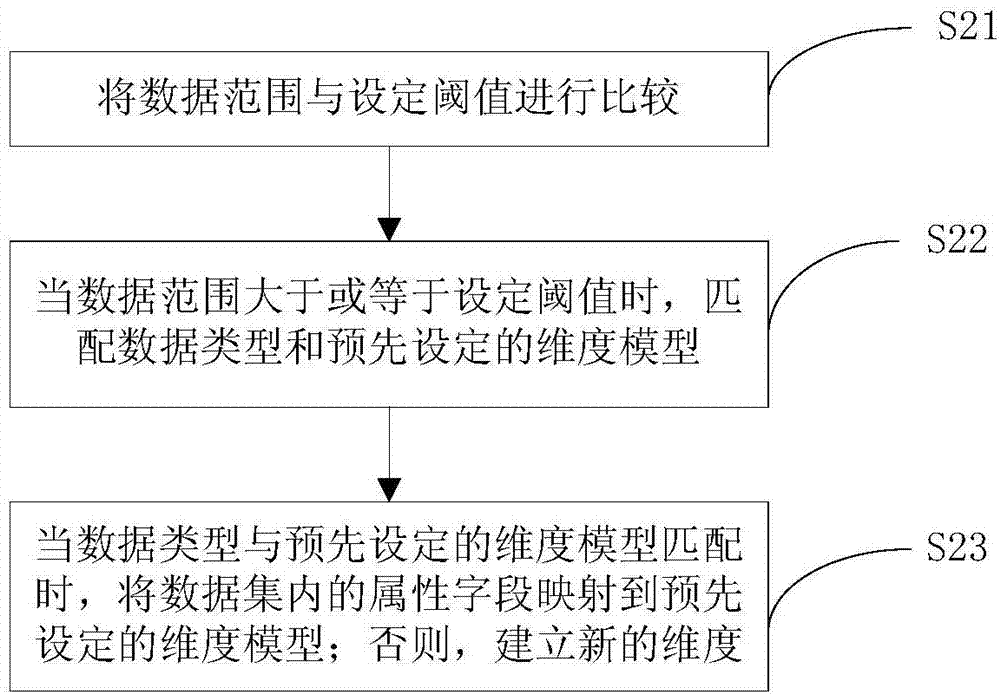

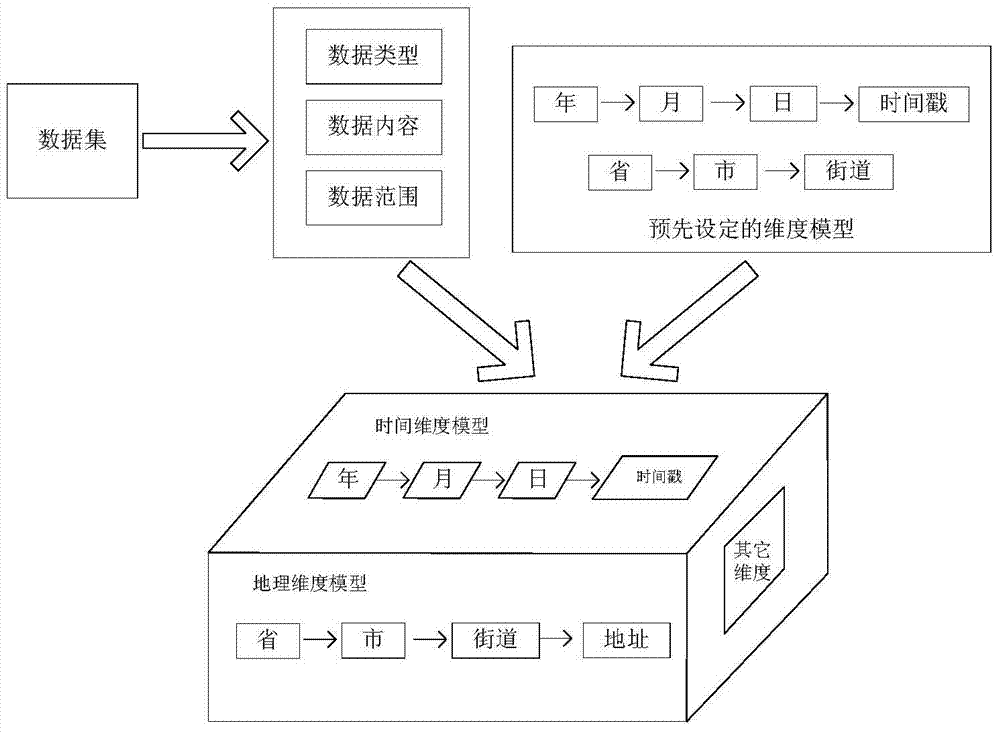

Dynamic extension method and system for multidimensional data analysis model

ActiveCN104850623AFlexible expansionMeet the needs of the big data eraSpecial data processing applicationsDynamic ExtensionExtension method

The present invention provides a dynamic extension method and system for a multidimensional data analysis model. The extension method comprises: importing a data set, and detecting the data set to obtain detection information; mapping attribute fields in the data set to a preset dimensional model according to the detection information or establishing new dimensions to form a dimensional model obtained after dynamic extension; and establishing an element table representing a relationship between the attribute fields and elements corresponding to the attribute fields, and a relation table representing the relationship between the attribute fields and the internal levels of the attribute fields in the dimensional model according to the dimensional model obtained after dynamic extension. According to the dynamic extension method and system for a multidimensional data analysis model provided by the present invention, the dynamic extension of dimensions is supported, the extension is very flexible, the extensions among different users cannot cause mutual interference, the extension cost is very low, and dynamic and various data can be processed, so that the dynamic extension method and system conform to the demands of the big data era.

Owner:HANGZHOU XUNHAN TECH CO LTD

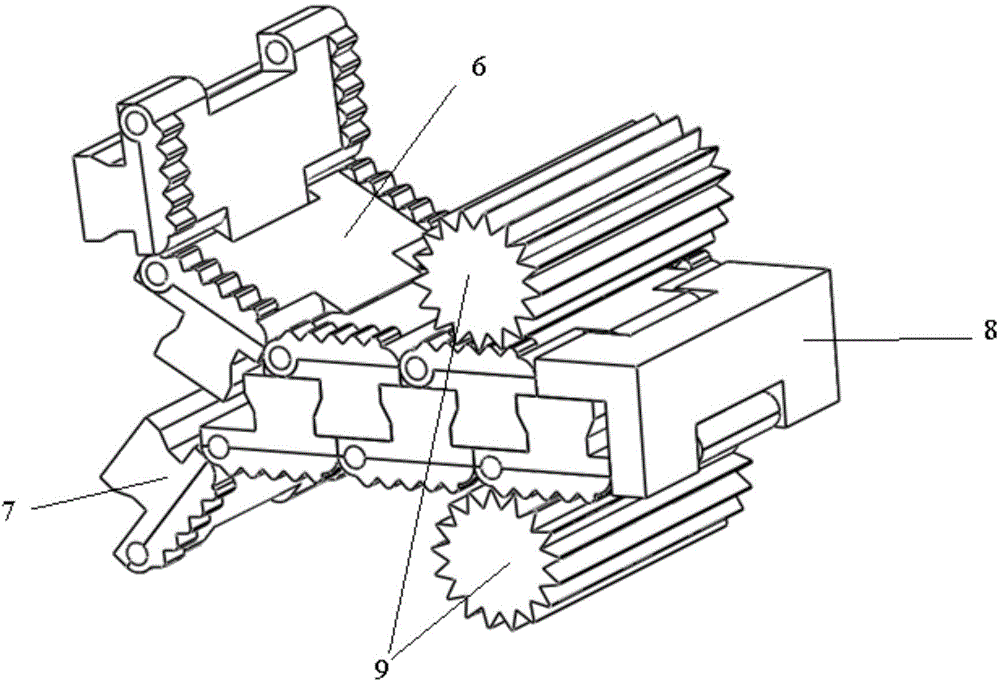

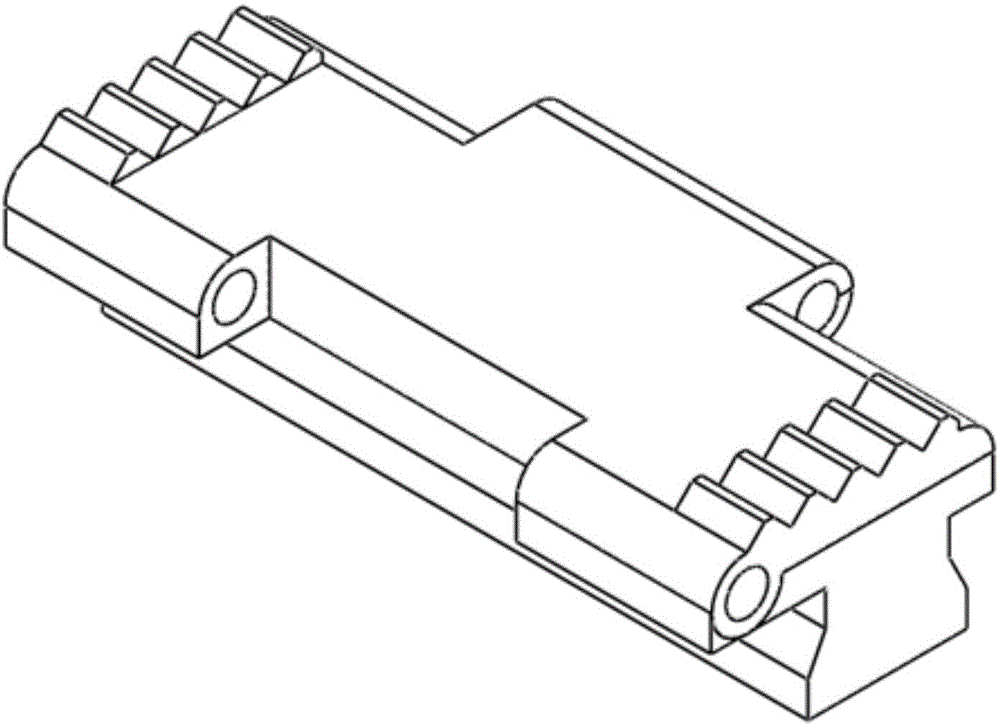

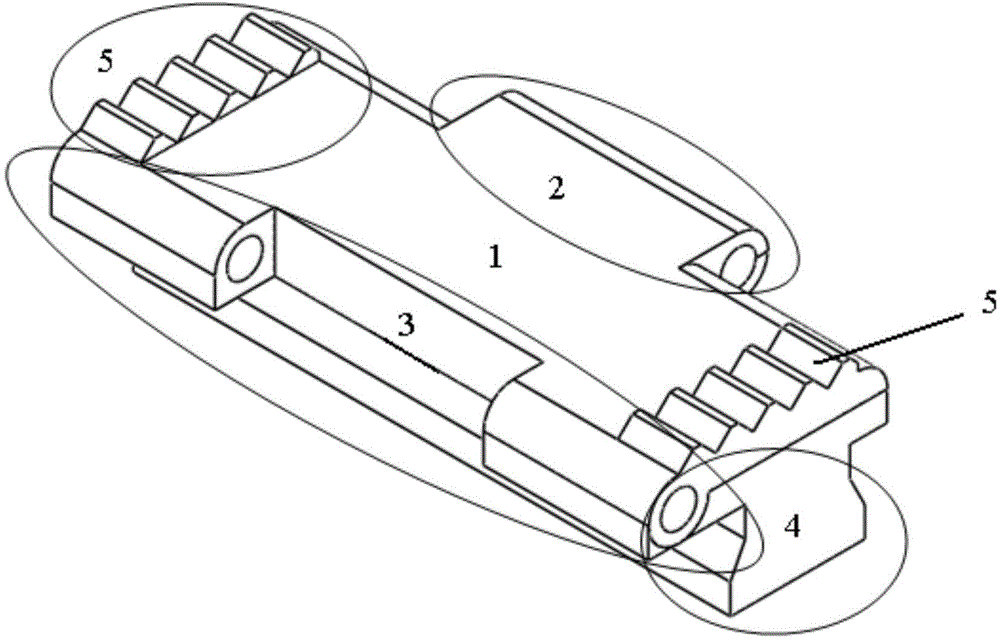

Parallel interlocking chain stretchable device and stretching method

ActiveCN105465278AFlexible expansionEasy to adjust the lengthHauling chainsHoisting chainsWinding machinePull force

The invention provides a parallel interlocking chain type stretchable device and a stretching method. The stretchable device is of a double-chain structure and formed by alternately engaging two single stretchable parallel chains. Each single stretchable parallel chain is composed of a plurality of mutually hinged chain type units. The number of the chain type units can be increased flexibly according to needs, and therefore the parallel interlocking chain type stretchable device has the advantage that the length is convenient to adjust. In the contracting process of the parallel interlocking chain type stretchable device, the chain type units of each contracting single stretchable parallel chain are wound on a chain winding machine, the function of contracting to the zero position is achieved, and the advantage that the occupied space is small after contracting is achieved. Furthermore, compared with an existing device, under the condition that the occupied space is fixed after the stretchable device contracts, a large extension length is provided. After the two single stretchable parallel chains are engaged and interlocked, the stretchable device has higher rigidity, can bear high-strength pushing force and pulling force needed by stretching, and can also bear the high bending force in the direction perpendicular to the stretching direction. The parallel interlocking chain type stretchable device has the advantage of being easy to produce and install.

Owner:GUANGDONG TITAN INTELLIGENT POWER CO LTD

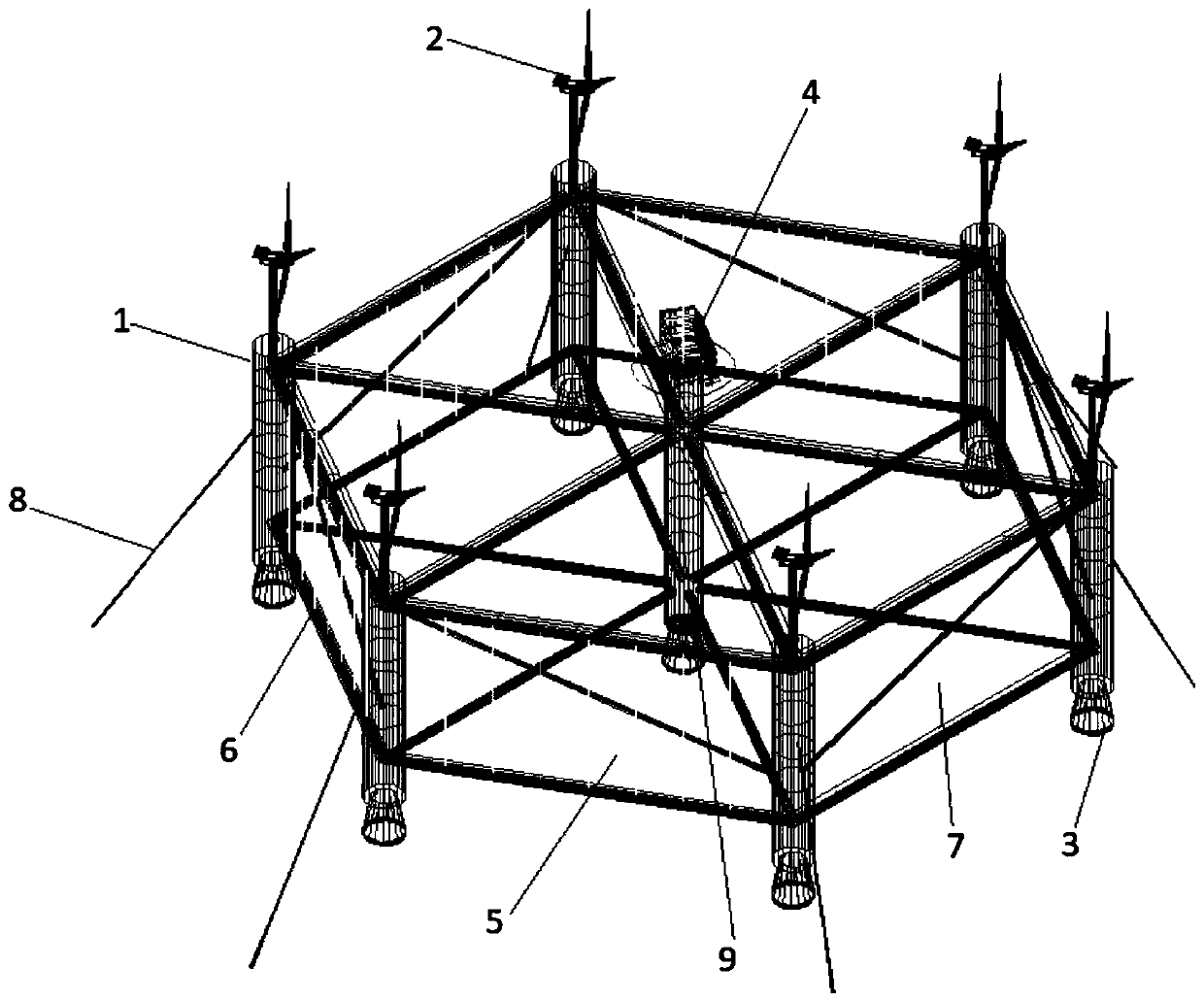

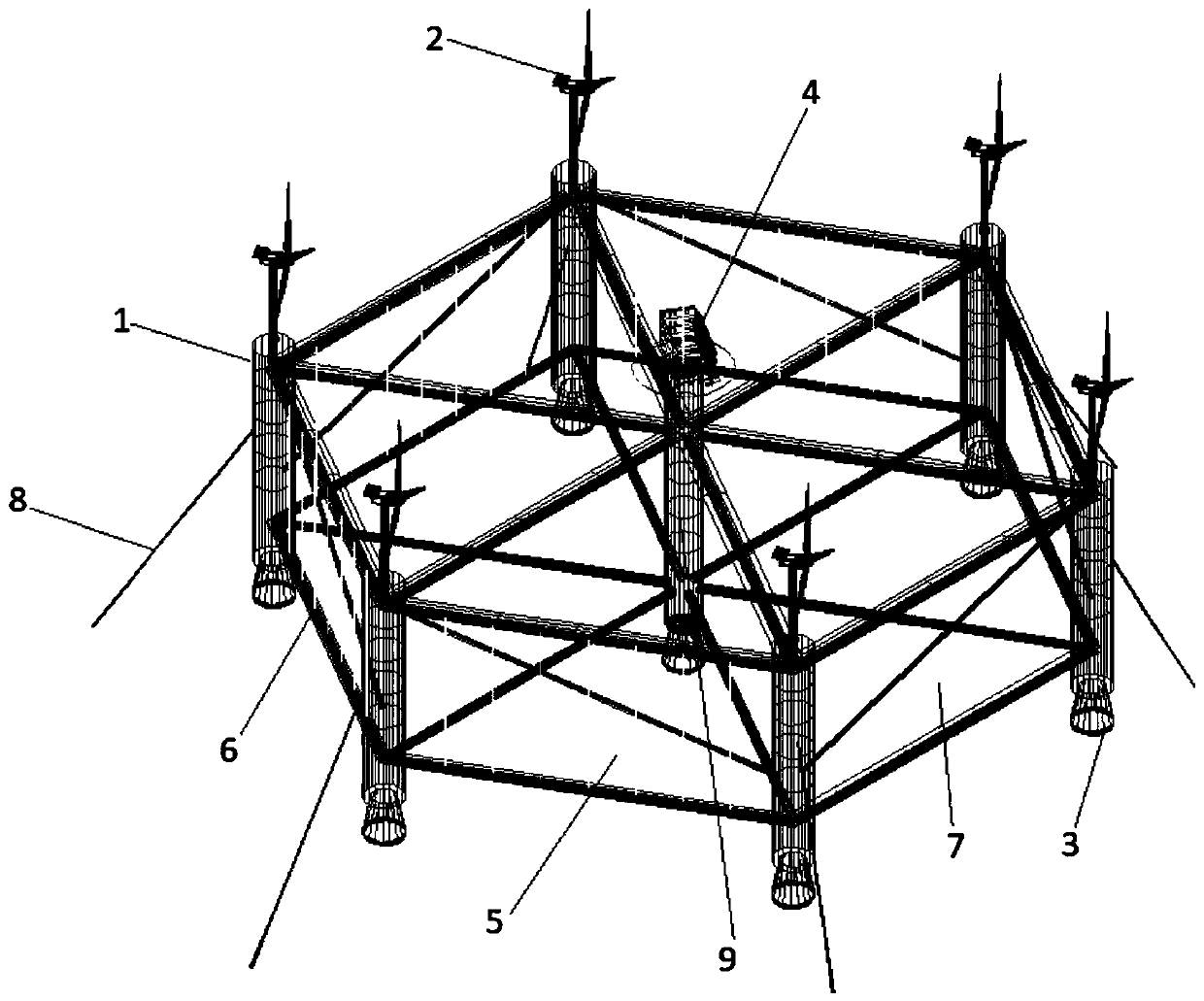

Offshore wind power and breeding integrated platform

InactiveCN111165412ASimple structural designFunction increaseArtificial islandsWaterborne vesselsOffshore wind powerElectric generator

The invention discloses an offshore wind power and breeding integrated platform. The platform is that a rigid frame structure is set up by adoption of multiple sets of buoyant wind towers; the whole is fixed or floats on the seabed; blocking nets are set on the periphery and at the bottom, so that a breeding area is formed; and a wind driven generator is arranged on the top, and used for wind power generation. The platform is suitable for a 50-300 m wind farm sea area, and is a working platform integrating offshore wind power generation and an offshore breeding farm into a whole; ring structure design is adopted; the overall size can be adjusted according to requirements; and thus, the platform has good economy and usability.

Owner:WISON NANTONG HEAVY IND