Ethernet realization system of FPGA chip internally provided with PHY transceiver function

A technology for implementing systems and transceivers, applied in the field of Ethernet, can solve problems such as increasing the complexity of PCB board design, increasing device types and costs, hidden code errors, etc., achieving high-reliability signal interconnection, reducing device types, and facilitating management Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] In order to make the technical means, creative features, goals and effects achieved by the present invention easy to understand, the present invention will be further described below in conjunction with specific embodiments.

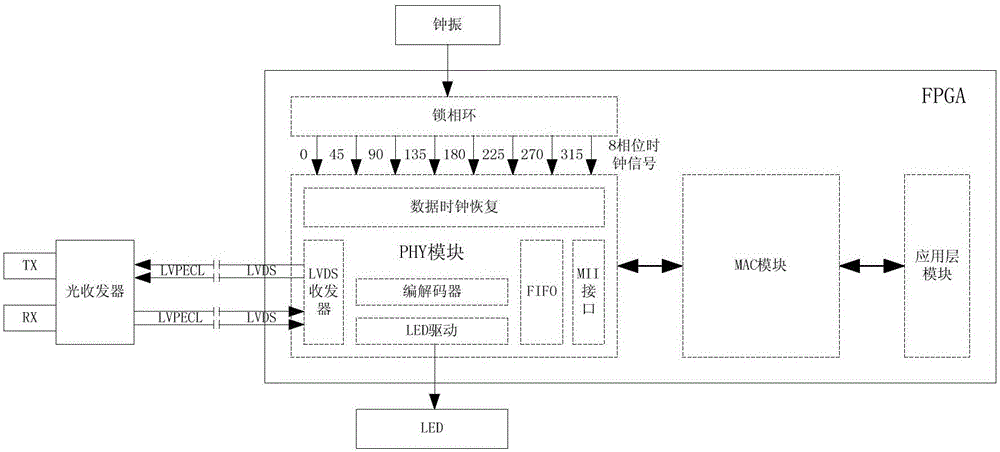

[0016] see figure 1 , the 100M optical Ethernet implementation scheme proposed by the present invention is to replace the independent PHY transceiver chip by realizing the PHY transceiver chip function inside the FPGA chip, and then the FPGA and the external optical transceiver are connected by LVDS differential signals to realize (carry out as required) differential signal conversion).

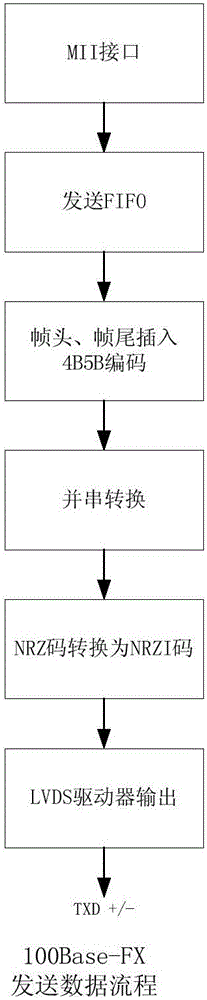

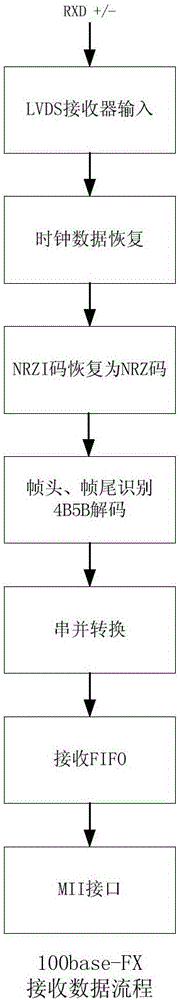

[0017] According to the functional requirements of the 100Base-FX 100M optical Ethernet physical layer PHY transceiver chip, the data flow of sending and receiving is as follows: figure 2 and image 3 shown.

[0018] Sending process: First, buffer the data to be sent from the MAC controller module to the sending FIFO through the MII interface, then perform Et...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More