Patents

Literature

587results about "Dielectric materials" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

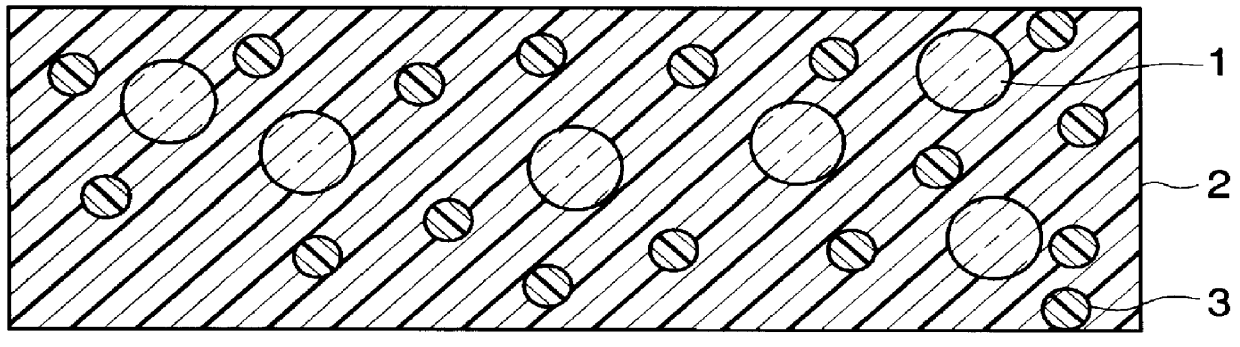

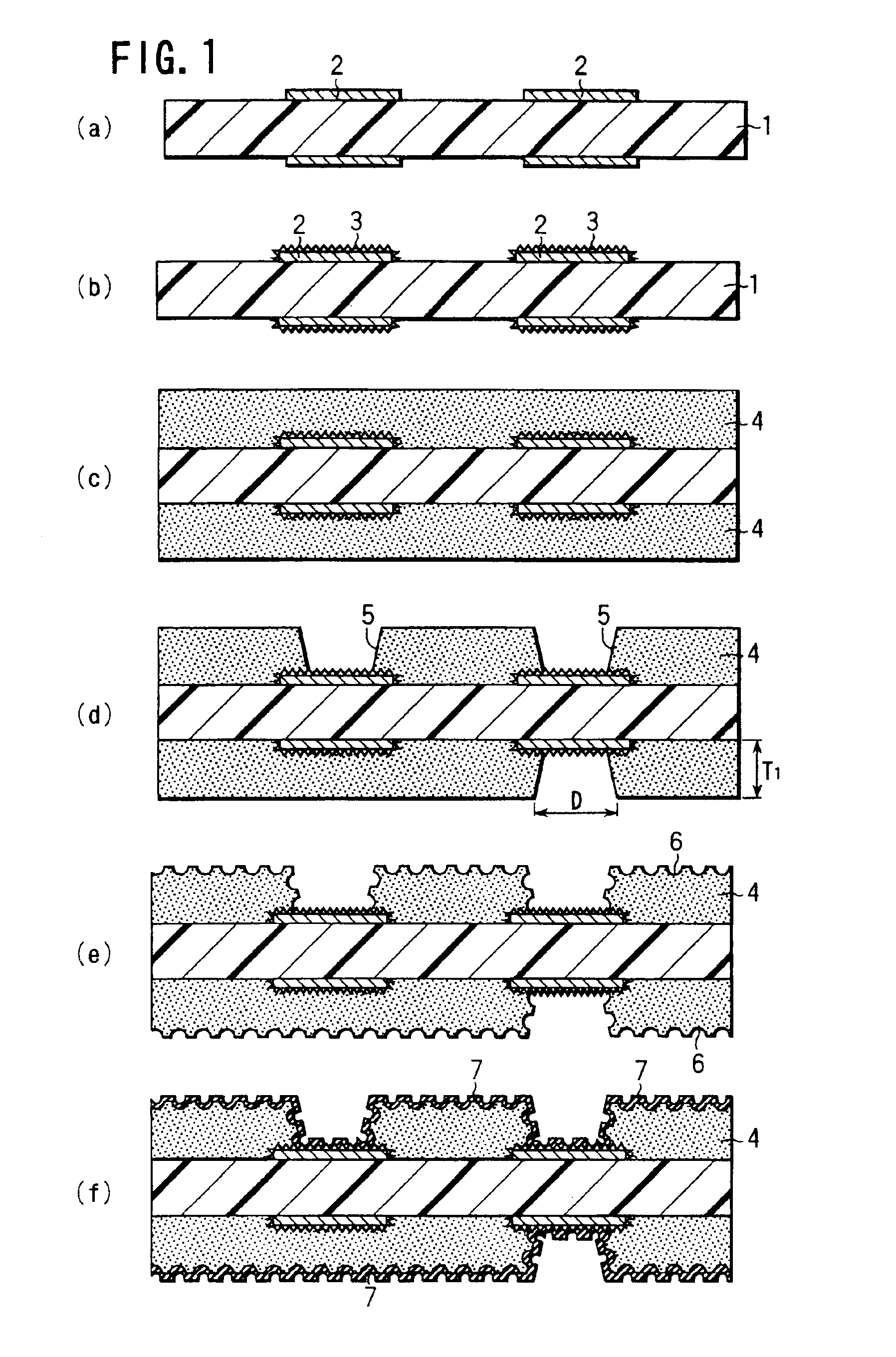

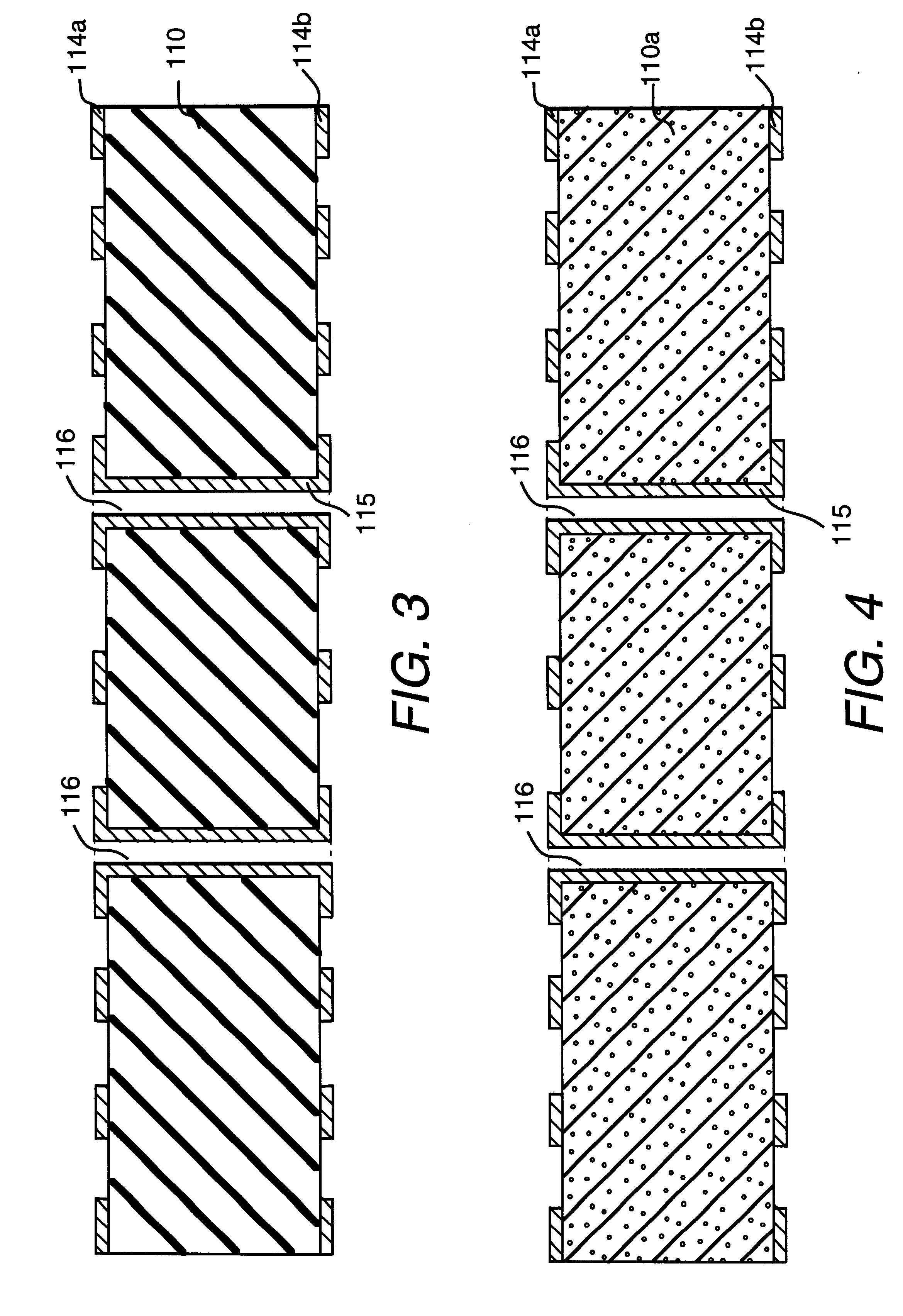

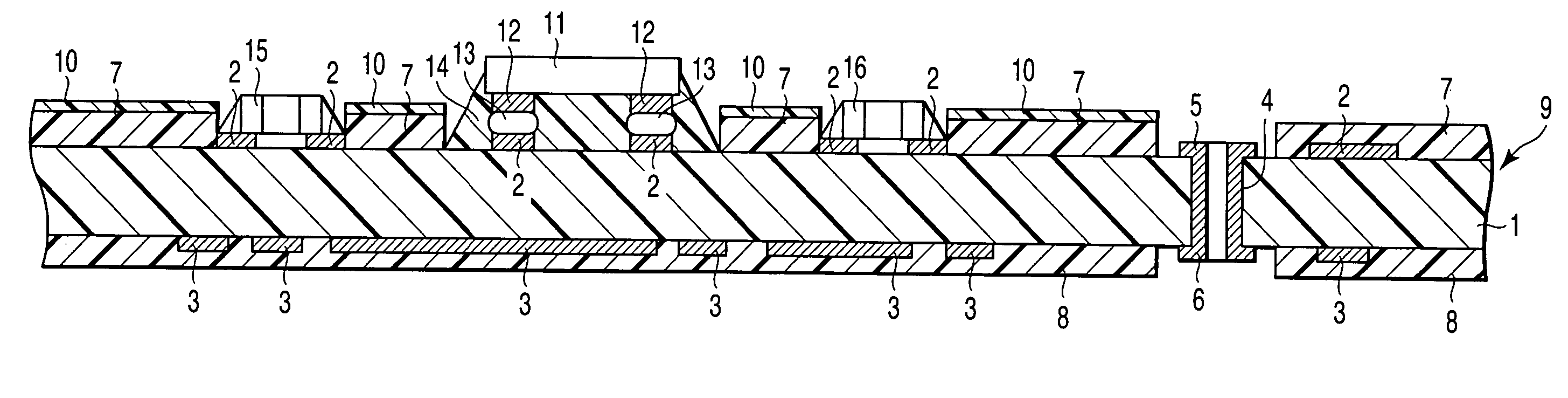

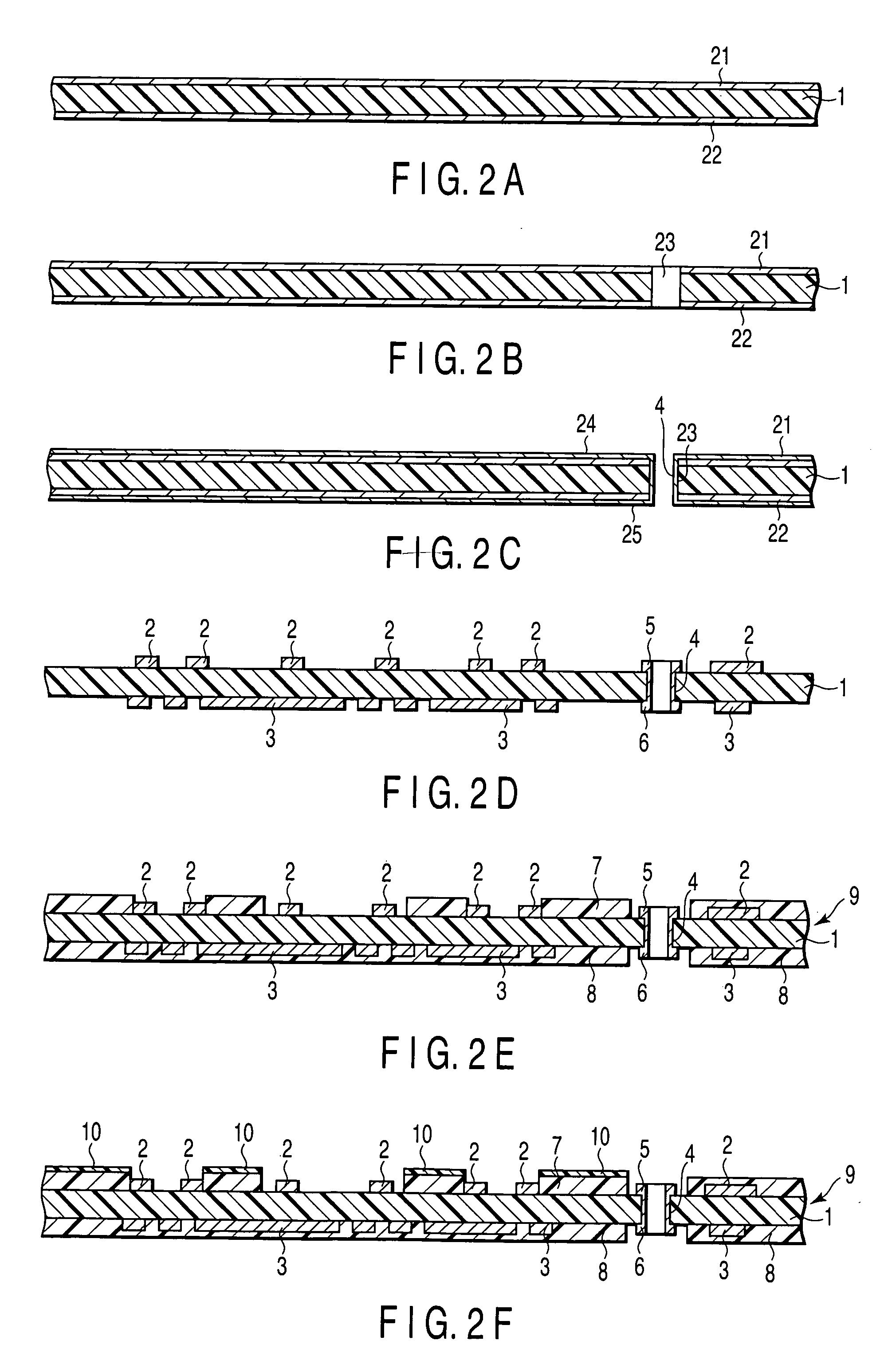

Laminate and multilayer printed circuit board

InactiveUS6114005AImprove connection reliabilityImprove featuresDielectric materialsSemiconductor/solid-state device detailsThermal expansionEngineering

A laminate capable of mounting semiconductor elements thereon; comprising an insulating layer which is constituted by a resin portion of sea-island structure and a woven reinforcement. The resin portion of sea-island structure is, for example, such that a resin as islands are dispersed in a resin as a matrix. Thus, the insulating layer exhibits a coefficient of thermal expansion of 3.0 DIFFERENCE 10 (ppm / K) in a planar direction thereof and a glass transition temperature of 150 DIFFERENCE 300 ( DEG C.). Owing to these physical properties, thermal stresses which the laminate undergoes in packaging the semiconductor elements thereon can be reduced, so that the connections of the laminate with the semiconductor elements can be made highly reliable.

Owner:HITACHI LTD

Touch panel and touch-sensitive display device

InactiveUS20120249465A1Designing can be facilitatedReduce materialDielectric materialsInput/output processes for data processingInsulation layerDisplay device

A touch panel structure and the manufacturing method thereof are disclosed, in which the manufacturing method includes the steps of: providing a bonding layer; and forming a conductive pattern layer on the bonding layer; wherein the conductive pattern layer is composed of at least one first and at least one second major conductors with an insulation layer interposed between the first and the second major conductors. Comparing with the prior art for manufacturing touch panels, the disclosure is advantageous in material cost, production cost, and production yield; moreover, the panel lamination process can be simplified and the touch panel structure can be joined to a planar or curvy panel and facilitate the design of a thinner product.

Owner:WINTEK CORP

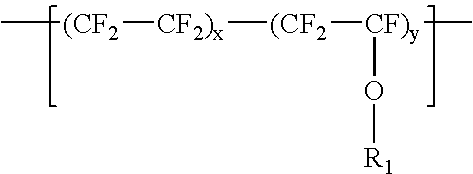

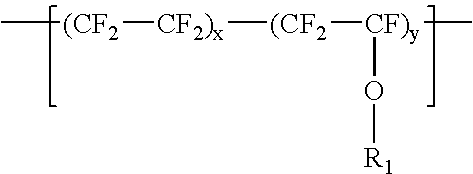

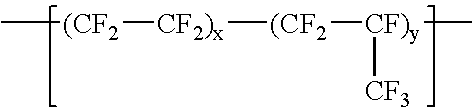

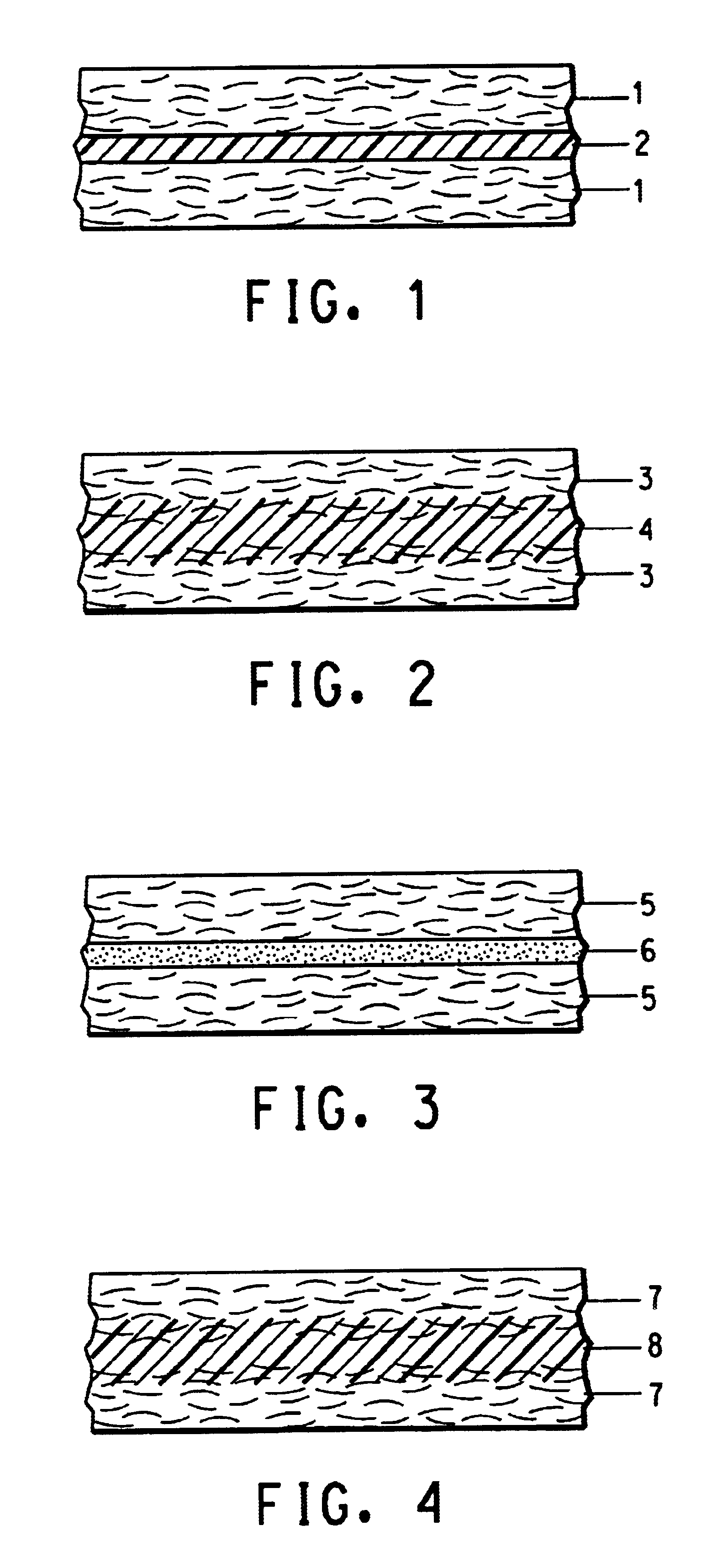

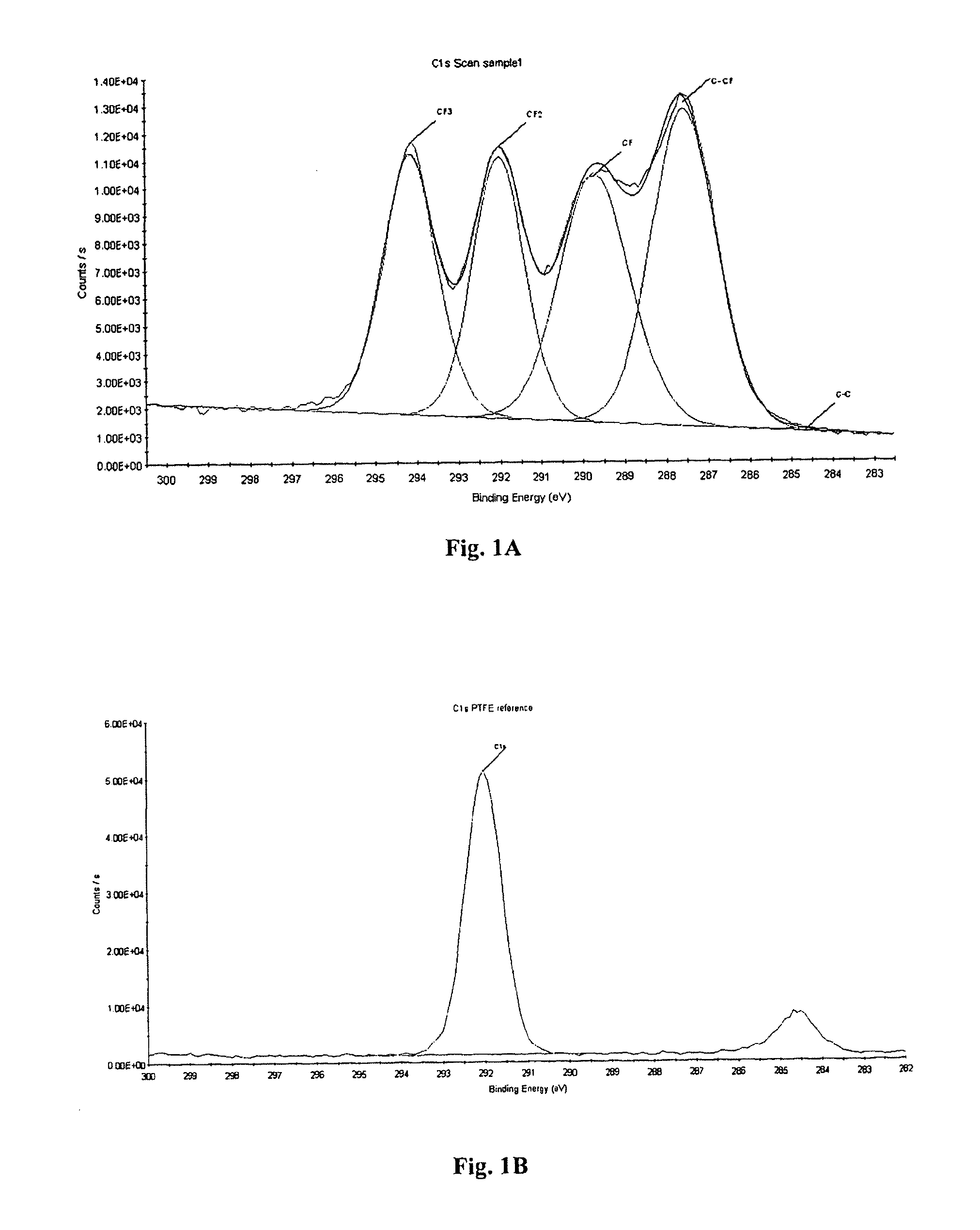

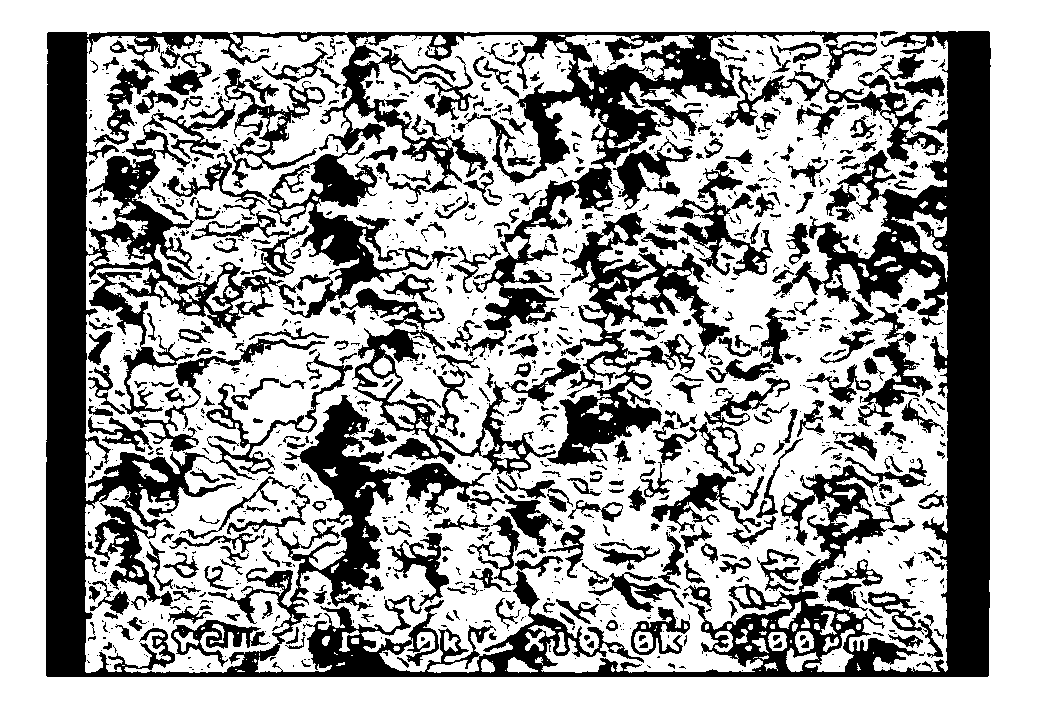

Polyimide based compositions useful as electronic substrates, derived in part from (micro-powder) fluoropolymer, and methods and compositions relating thereto

InactiveUS7026032B2Well as to enableLiquid crystal compositionsSubstation/switching arrangement detailsPolymer scienceFluoropolymer

The present invention is a polymeric composite comprising a polyimide component and a fluoropolymer component derived from a micro powder. The fluoropolymer micro powder has a melt point between 250 and 375° C. The fluoropolymer micro powder has an average particle size between 20 and 5000 nanometers (5.0 microns).The polyimide component and the fluoropolymer component are inter-mixed at a high dispersion level where the fluoropolymer component is present in a weight ratio from 10 to 60 percent. The polymeric composite of these two components is particularly useful in the form of a thin film used in high-speed digital circuitry or high signal integrity for low loss of a digital signal. The film can also be used as a wire wrap, or as a coverlay or base film substrate for flexible circuitry laminates.

Owner:EI DU PONT DE NEMOURS & CO

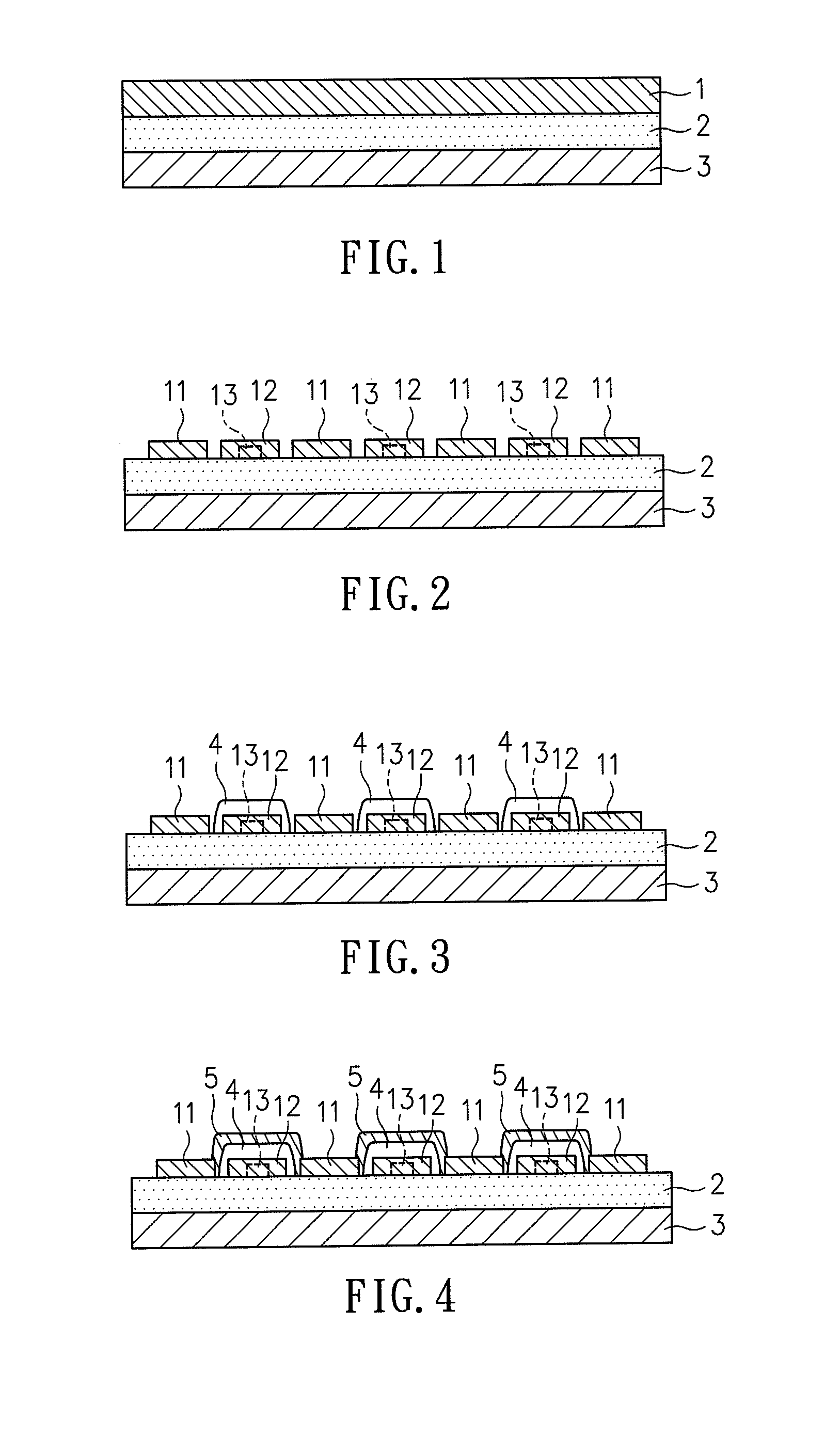

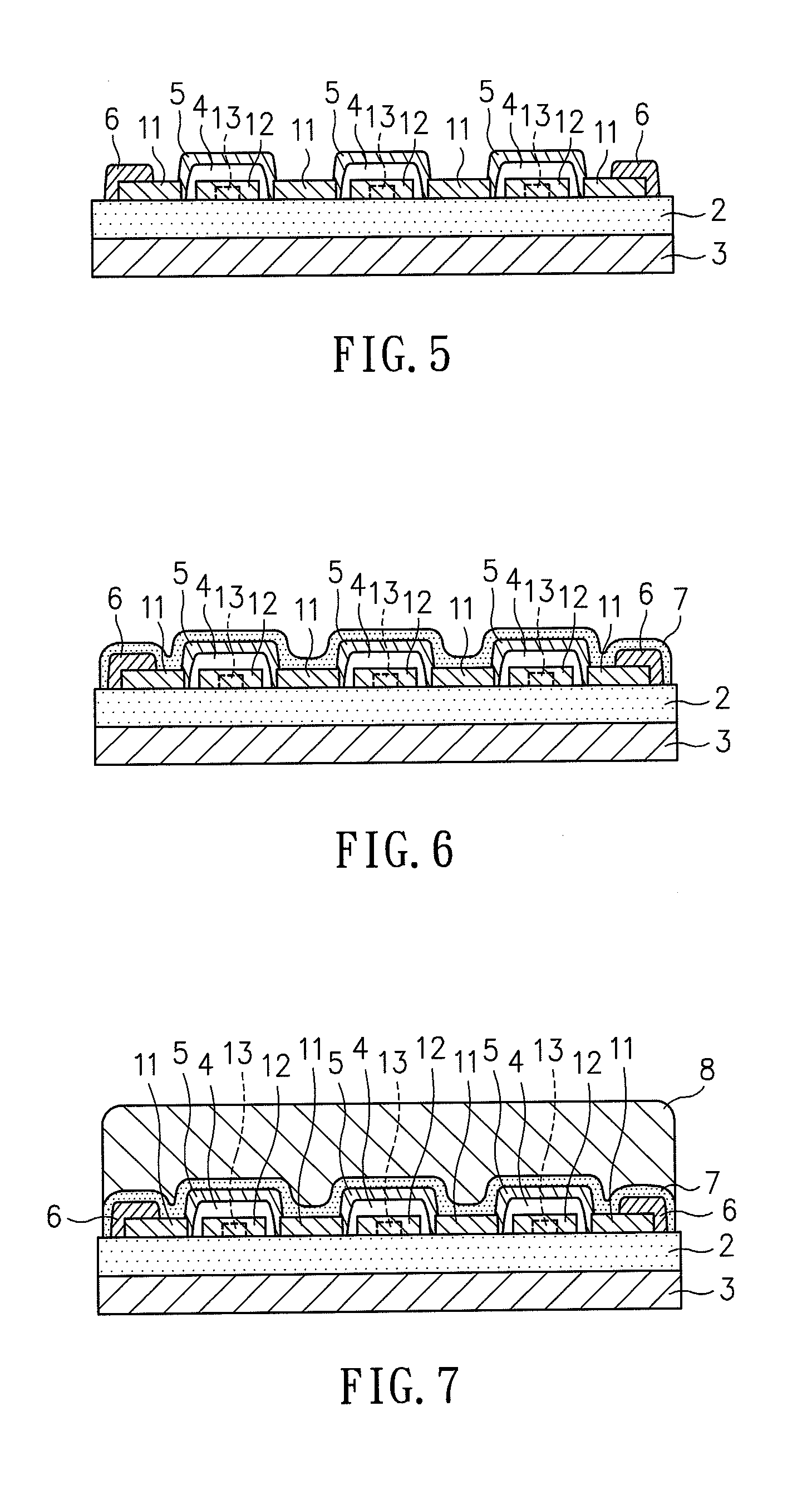

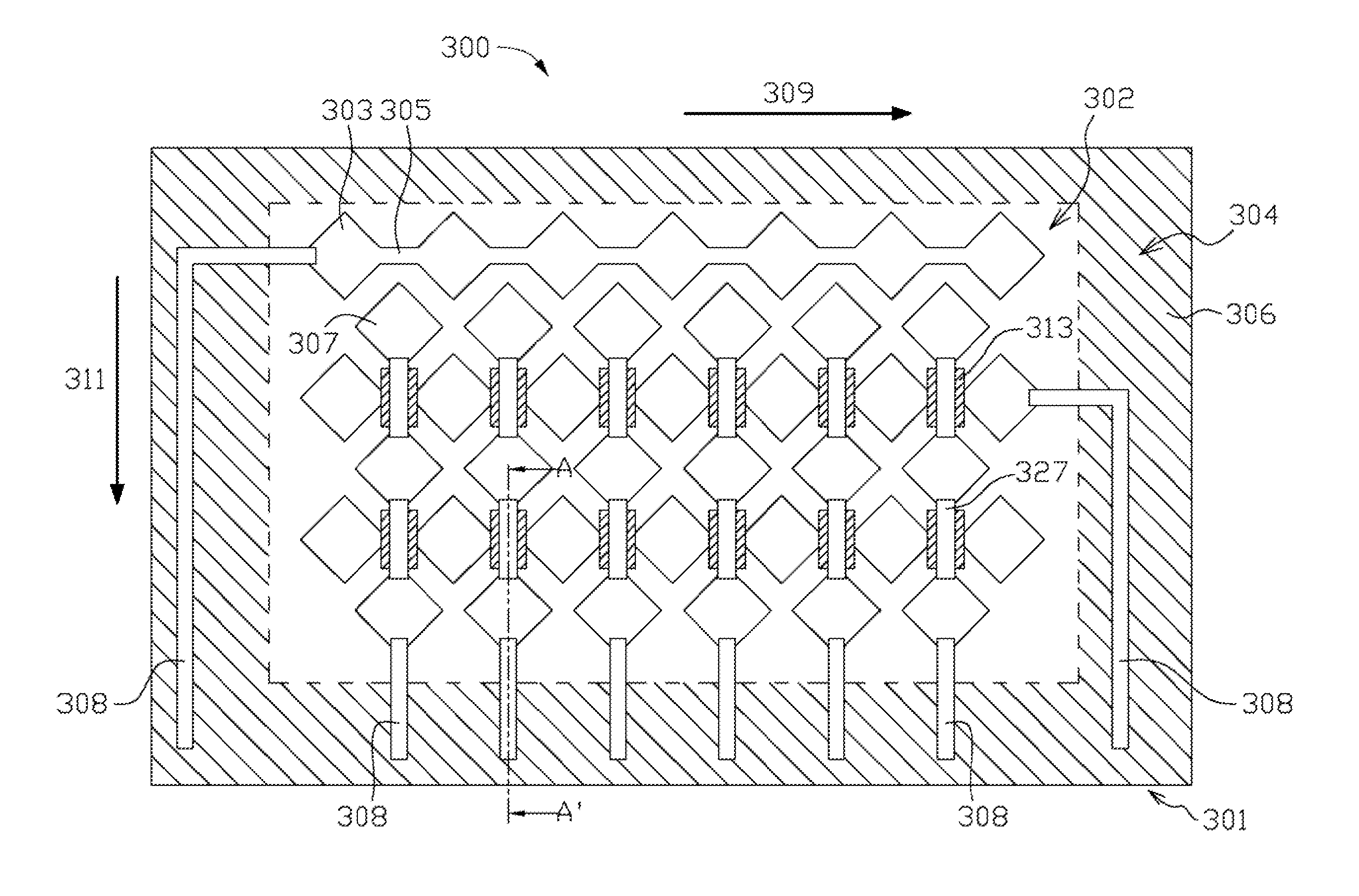

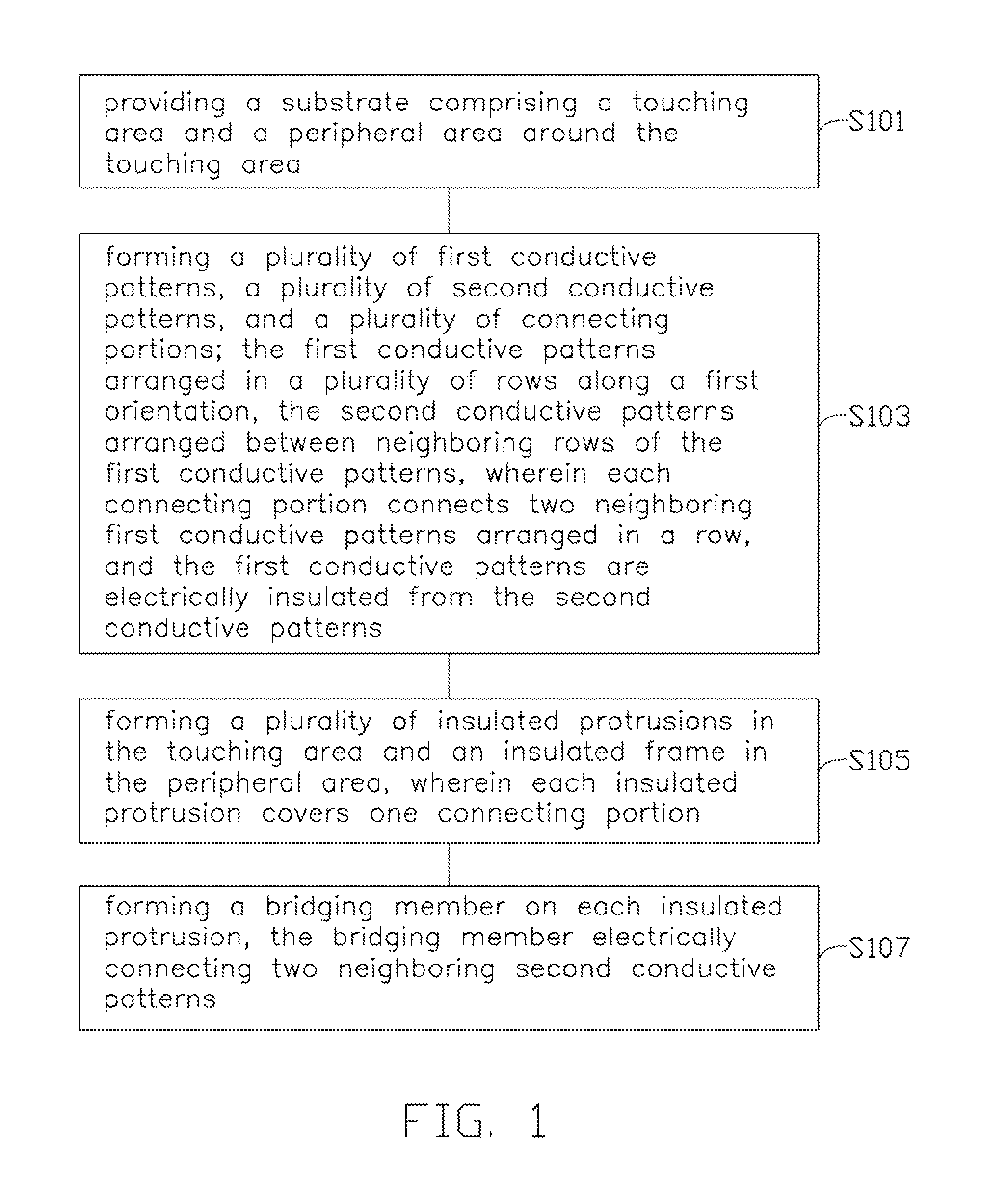

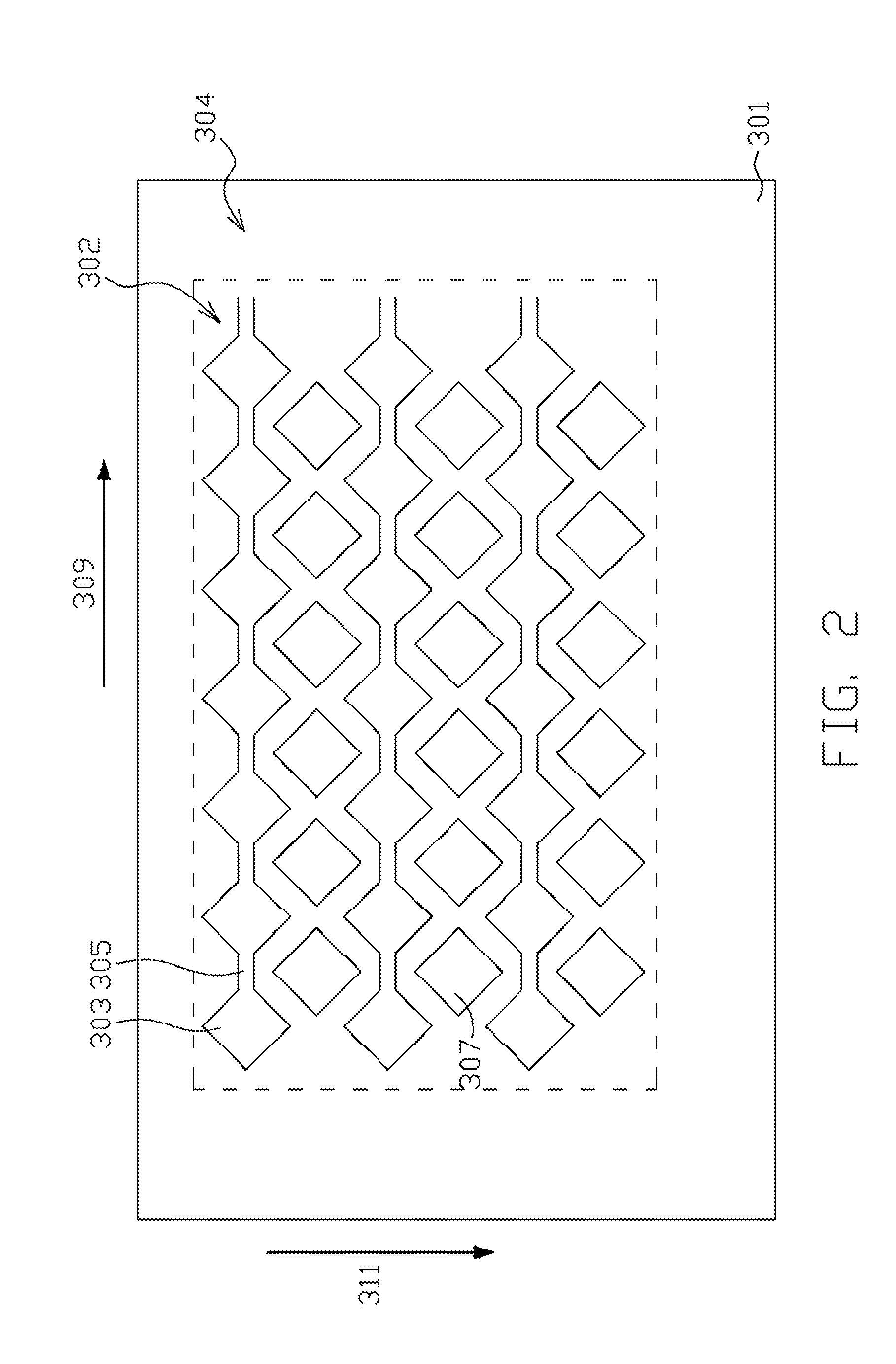

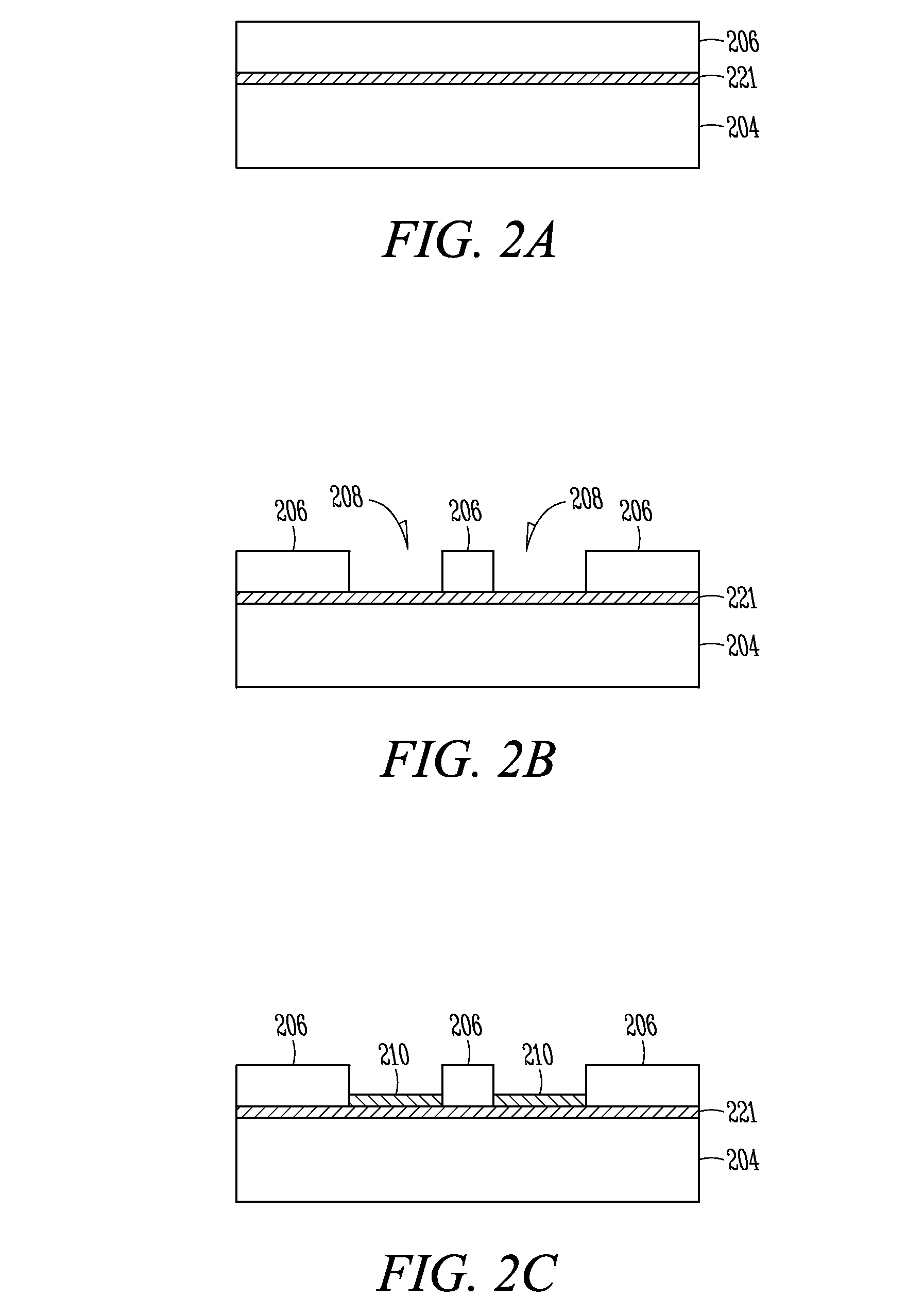

Capacitance touch panel module and fabrication method thereof

A method of fabricating a capacitance touch panel module includes forming a plurality of first conductive patterns on a substrate comprising a touching area and a peripheral area along a first orientation, a plurality of second conductive patterns along a second orientation, and a plurality of connecting portions in the touching area; forming a plurality of insulated protrusions, in which each insulated protrusion covering one connecting portion, and forming an insulated frame on the peripheral area; and forming a bridging member on each insulated protrusion.

Owner:INNOCOM TECH SHENZHEN +1

Polyimide based compositions useful as electronic substrates, derived in part from (micro-powder) fluoropolymer, and methods and compositions relating thereto

InactiveUS20050096429A1Well as to enableLiquid crystal compositionsSubstation/switching arrangement detailsPolymer scienceFluoropolymer

The present invention is a polymeric composite comprising a polyimide component and a fluoropolymer component derived from a micro powder. The fluoropolymer micro powder has a melt point between 250 and 375° C. The fluoropolymer micro powder has an average particle size between 20 and 5000 nanometers (5.0 microns). The polyimide component and the fluoropolymer component are inter-mixed at a high dispersion level where the fluoropolymer component is present in a weight ratio from 10 to 60 percent. The polymeric composite of these two components is particularly useful in the form of a thin film used in high-speed digital circuitry or high signal integrity for low loss of a digital signal. The film can also be used as a wire wrap, or as a coverlay or base film substrate for flexible circuitry laminates.

Owner:EI DU PONT DE NEMOURS & CO

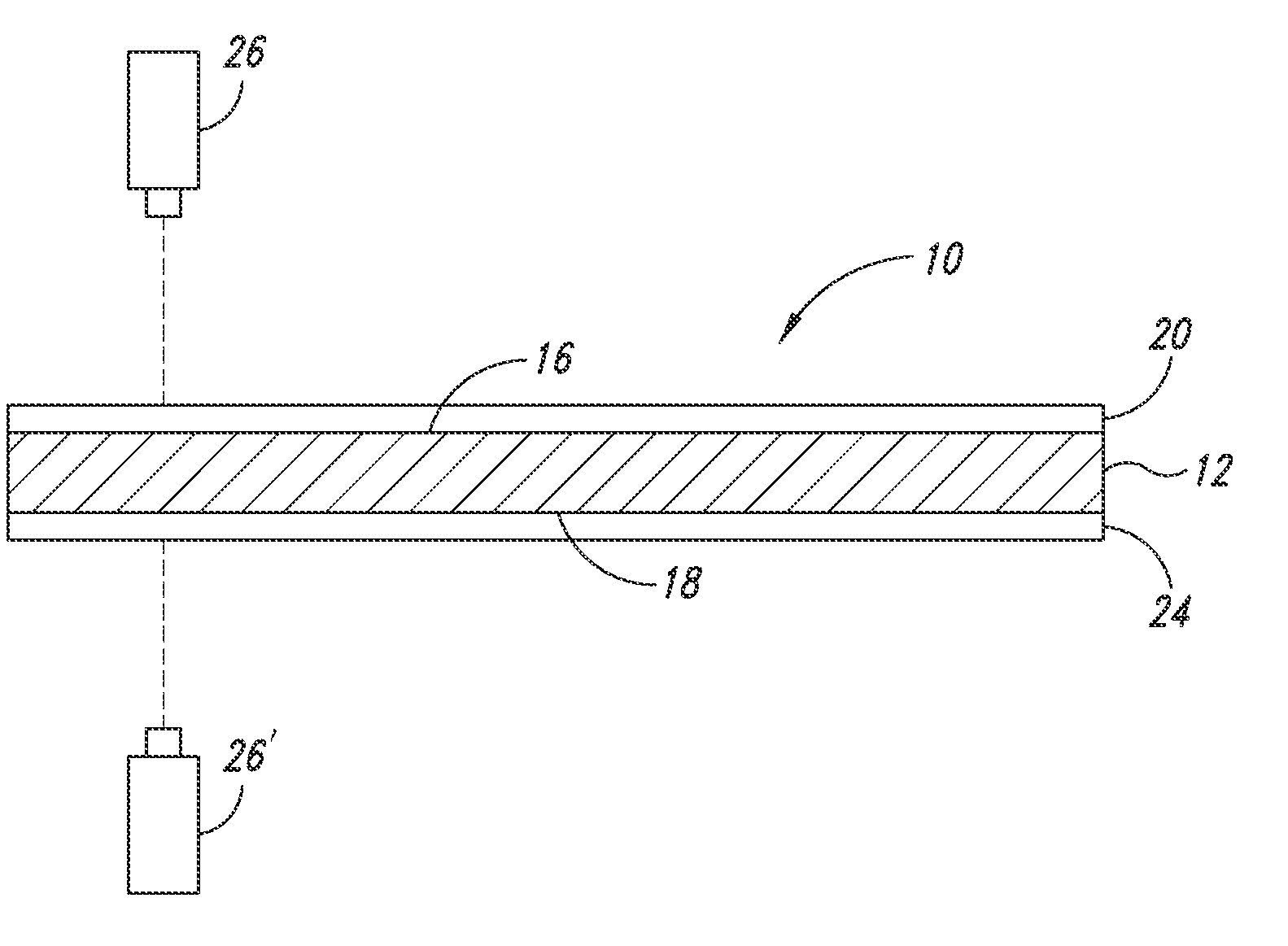

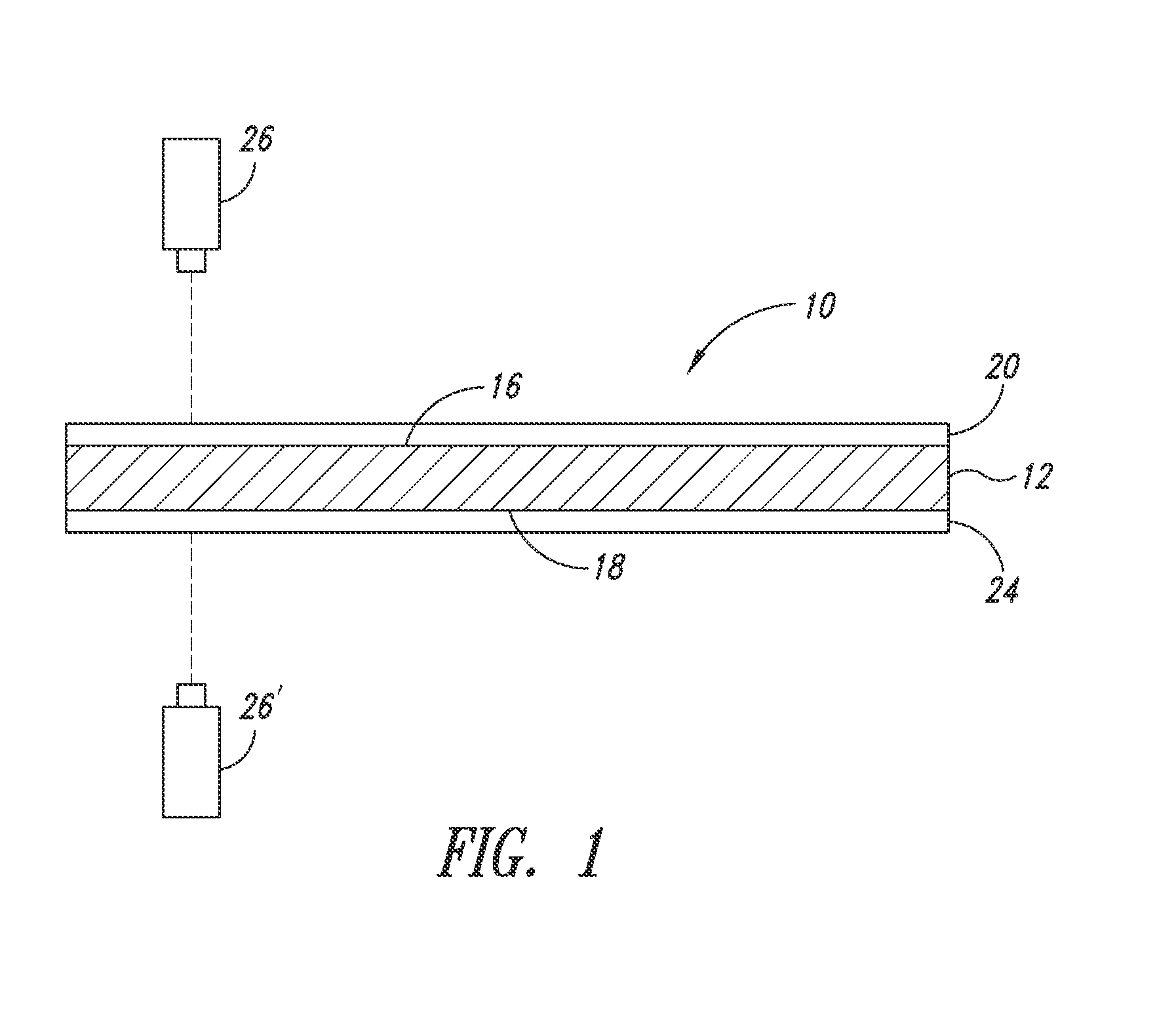

Two-sided laser patterning on thin film substrates

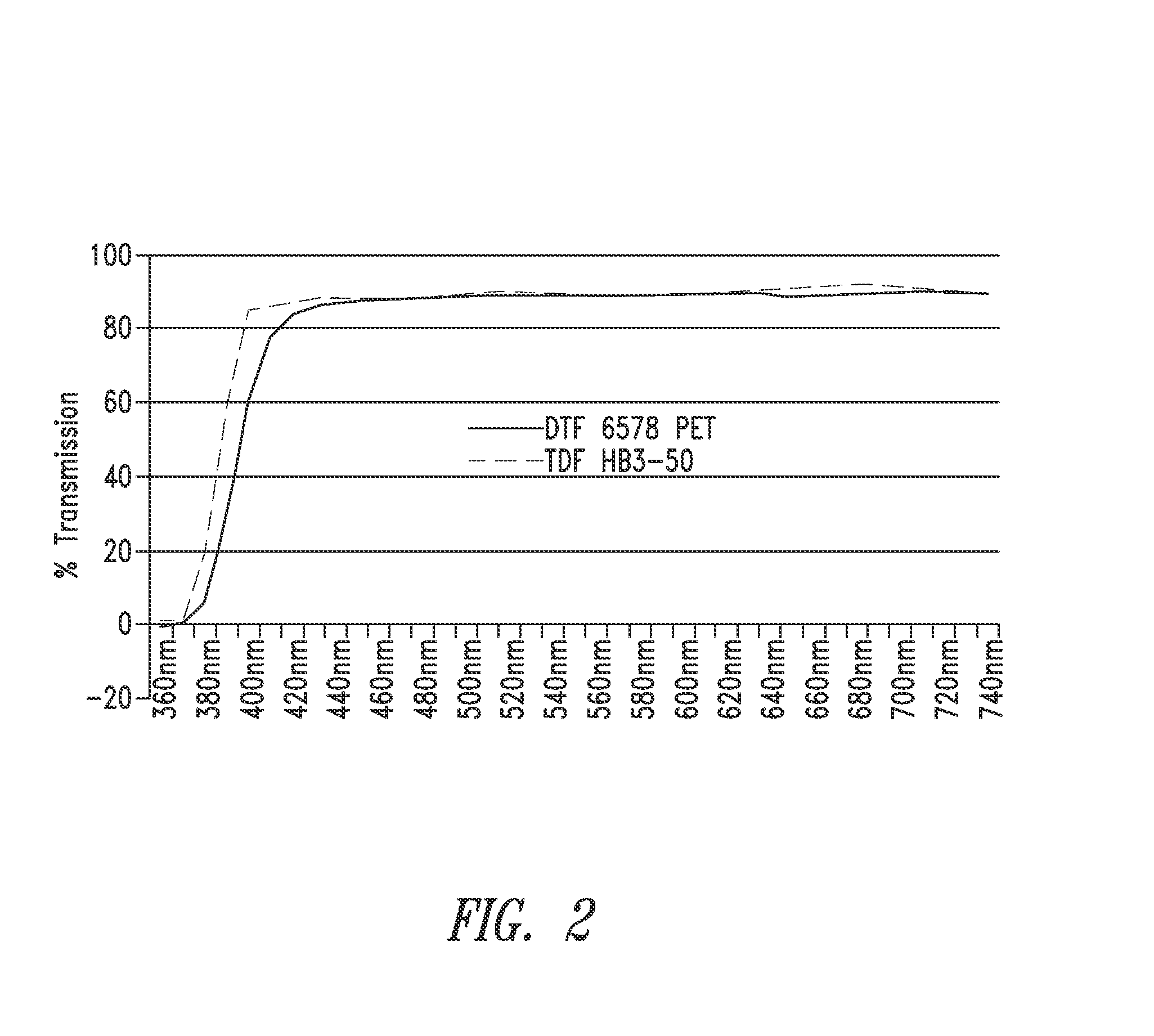

InactiveUS20140202742A1Improve throughputLight absorption dielectricsCircuit optical detailsLaser patterningTransparent conducting film

Owner:CHAMP GREAT INTL

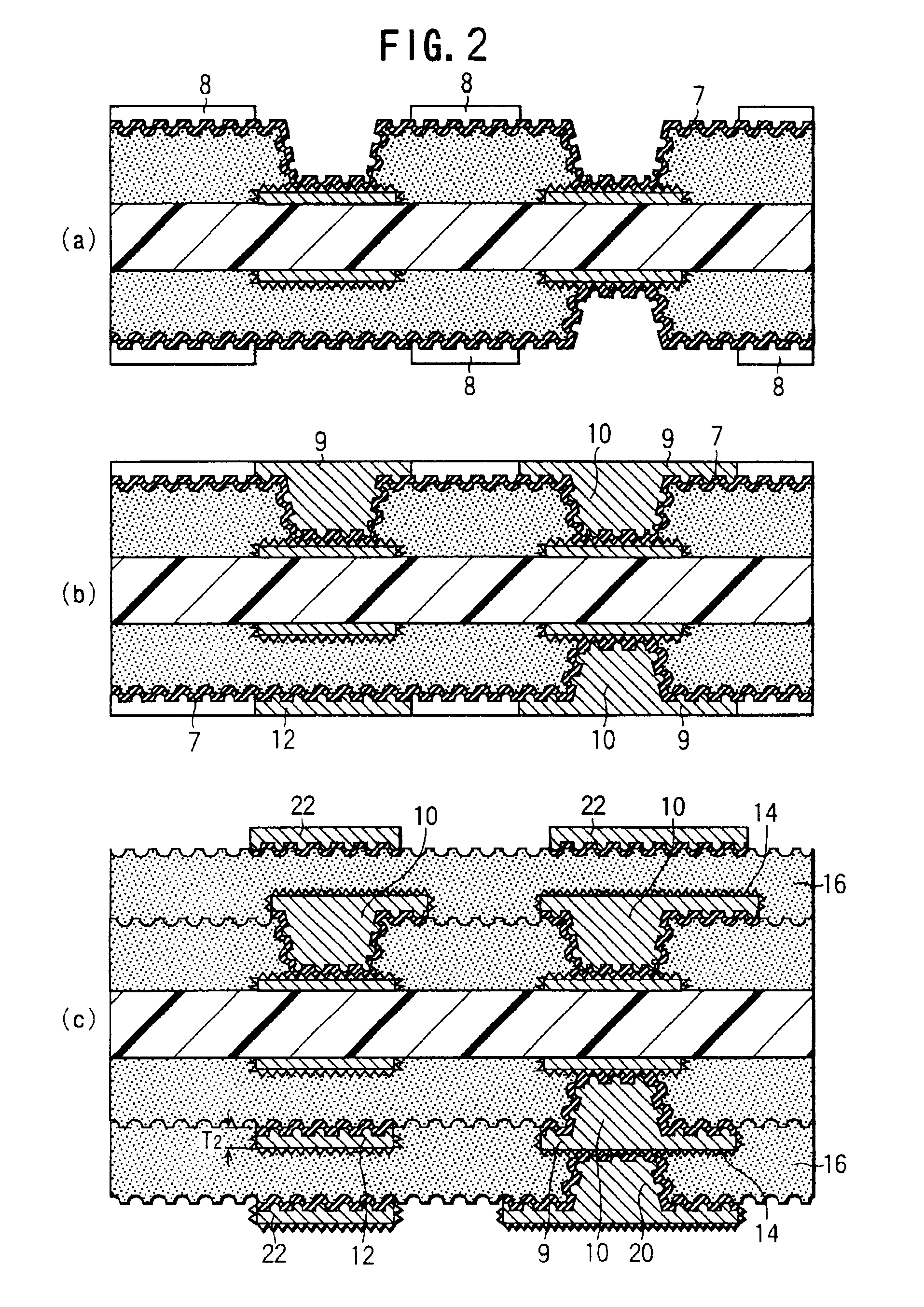

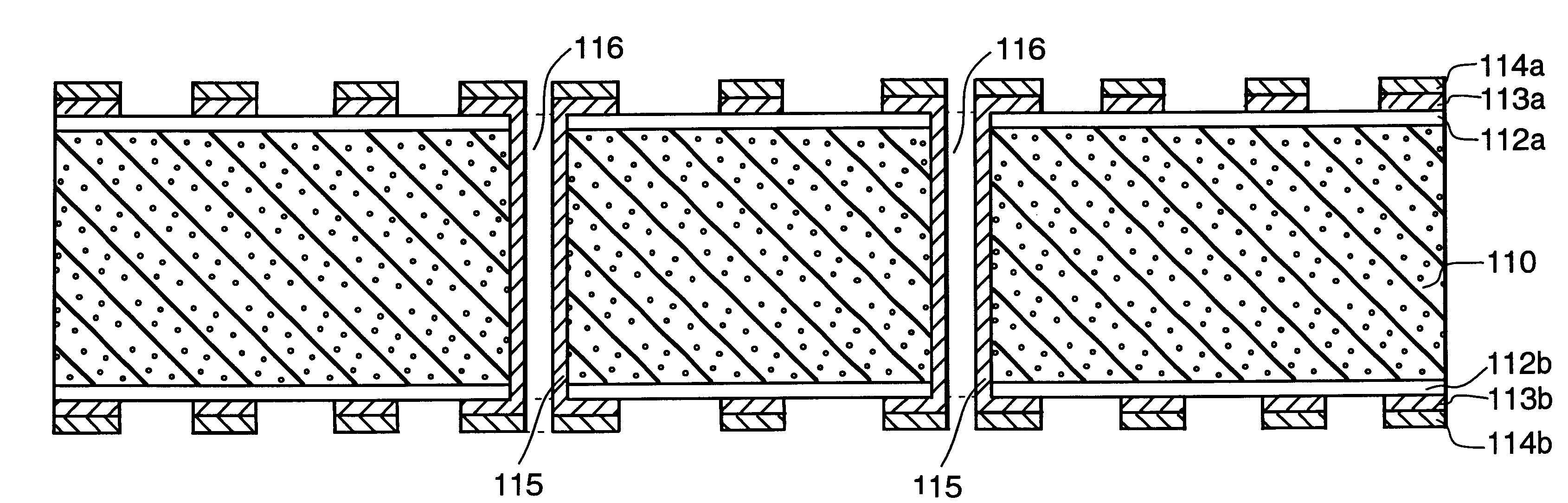

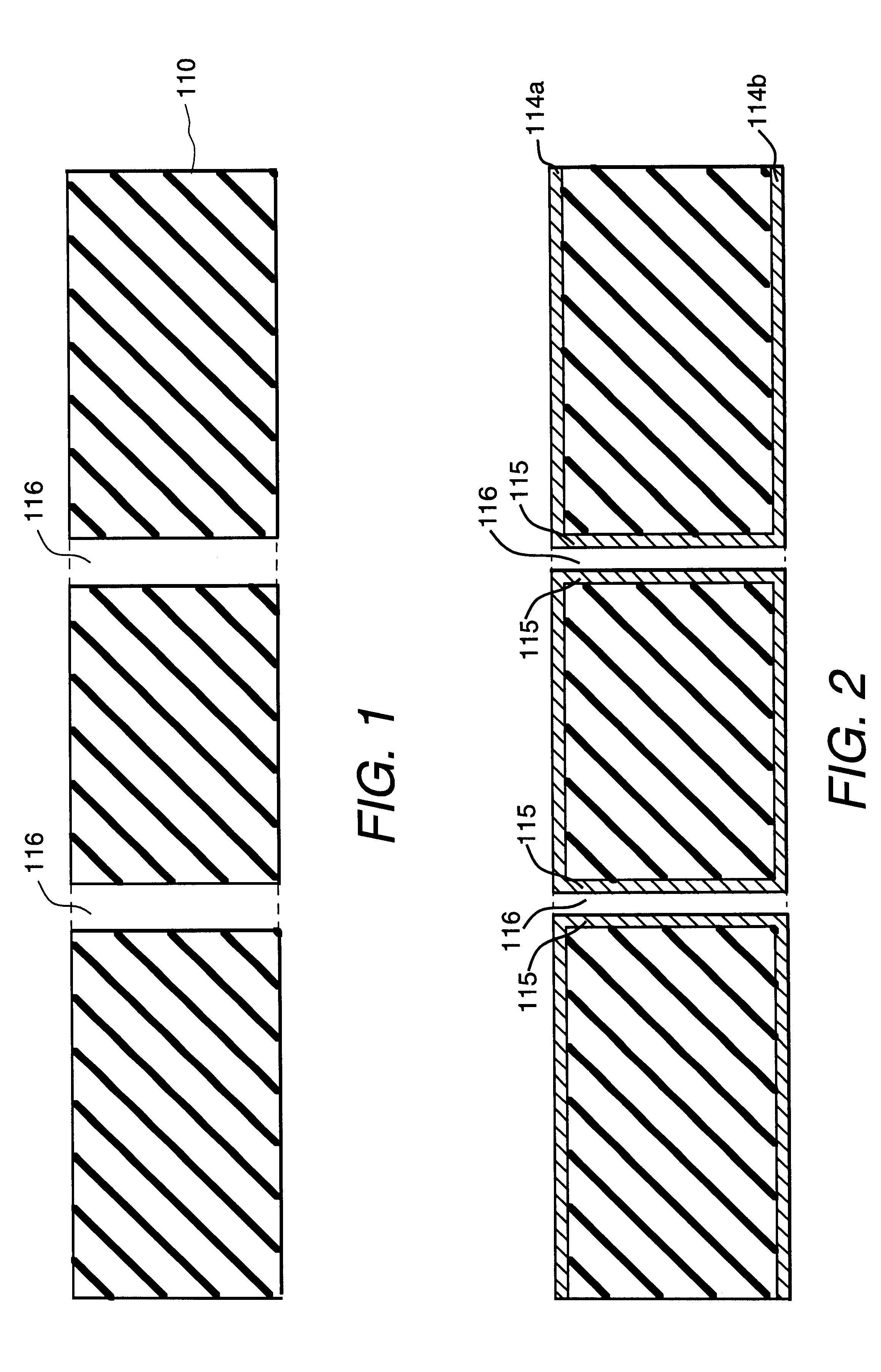

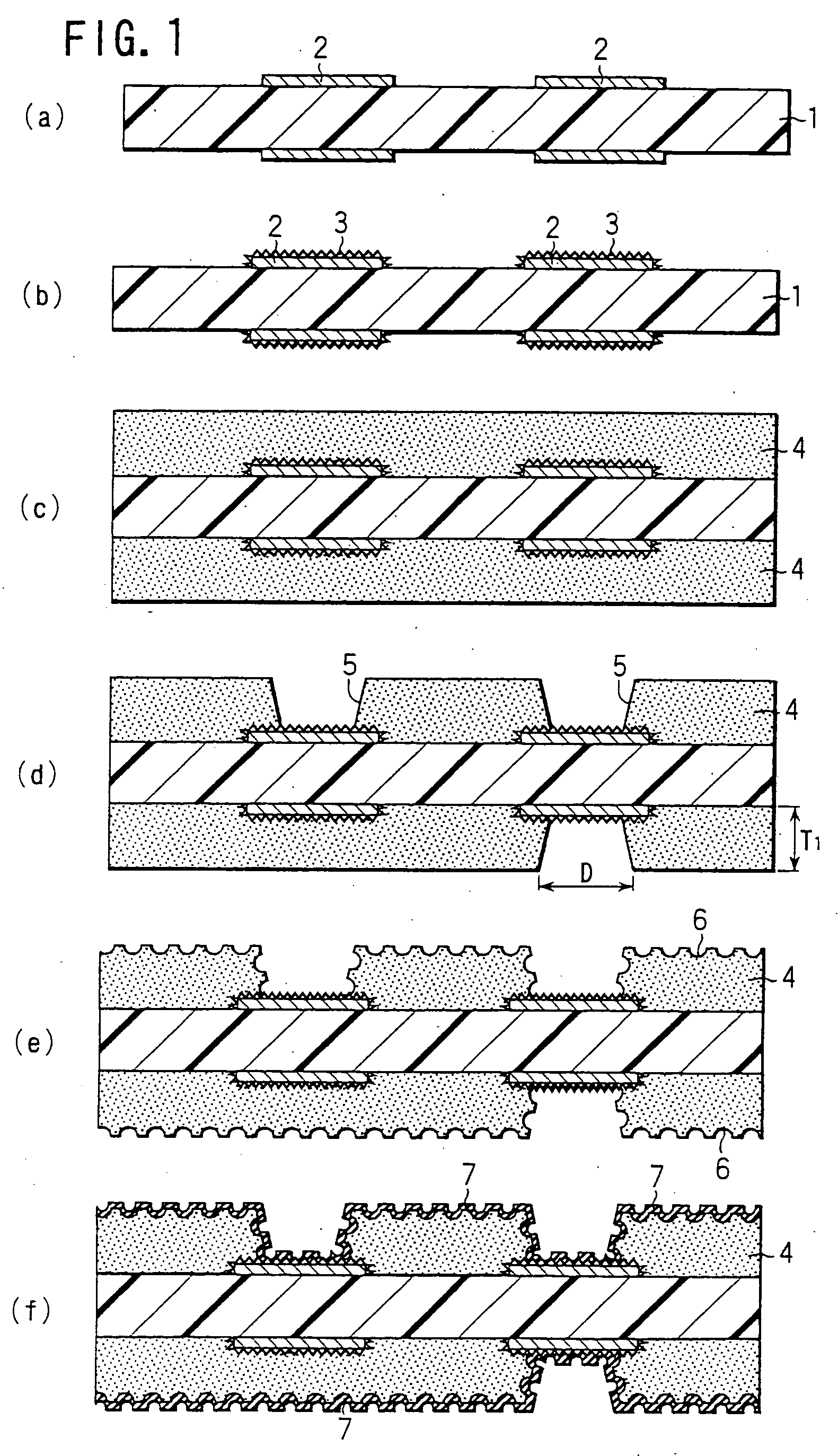

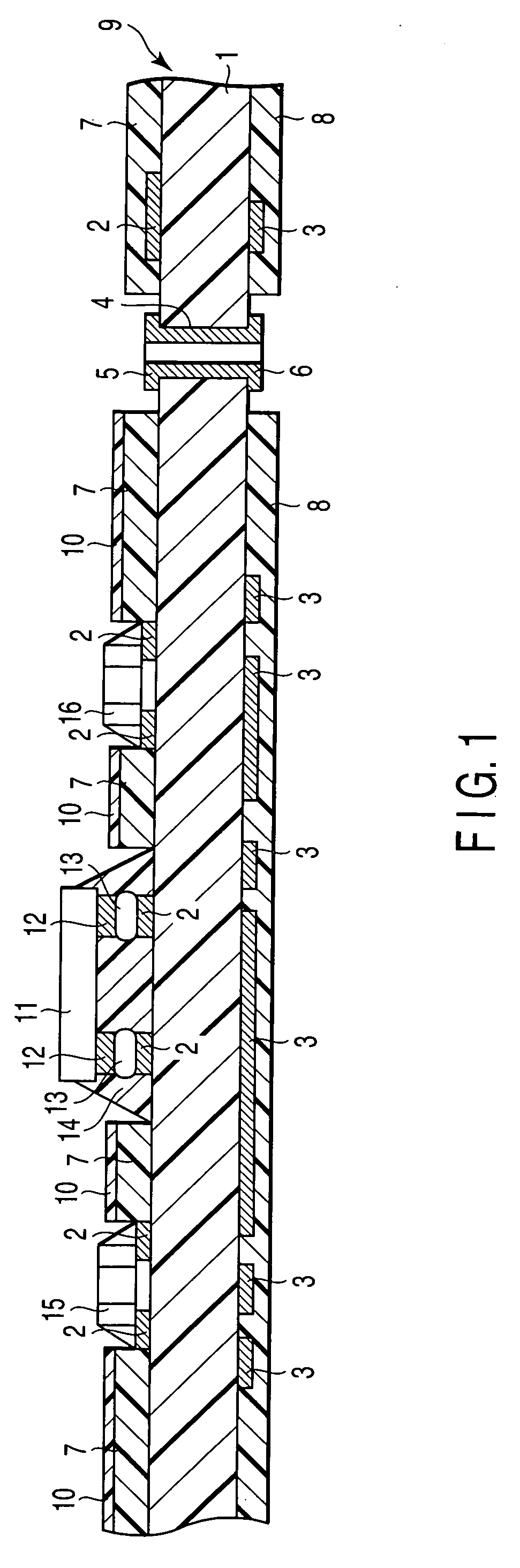

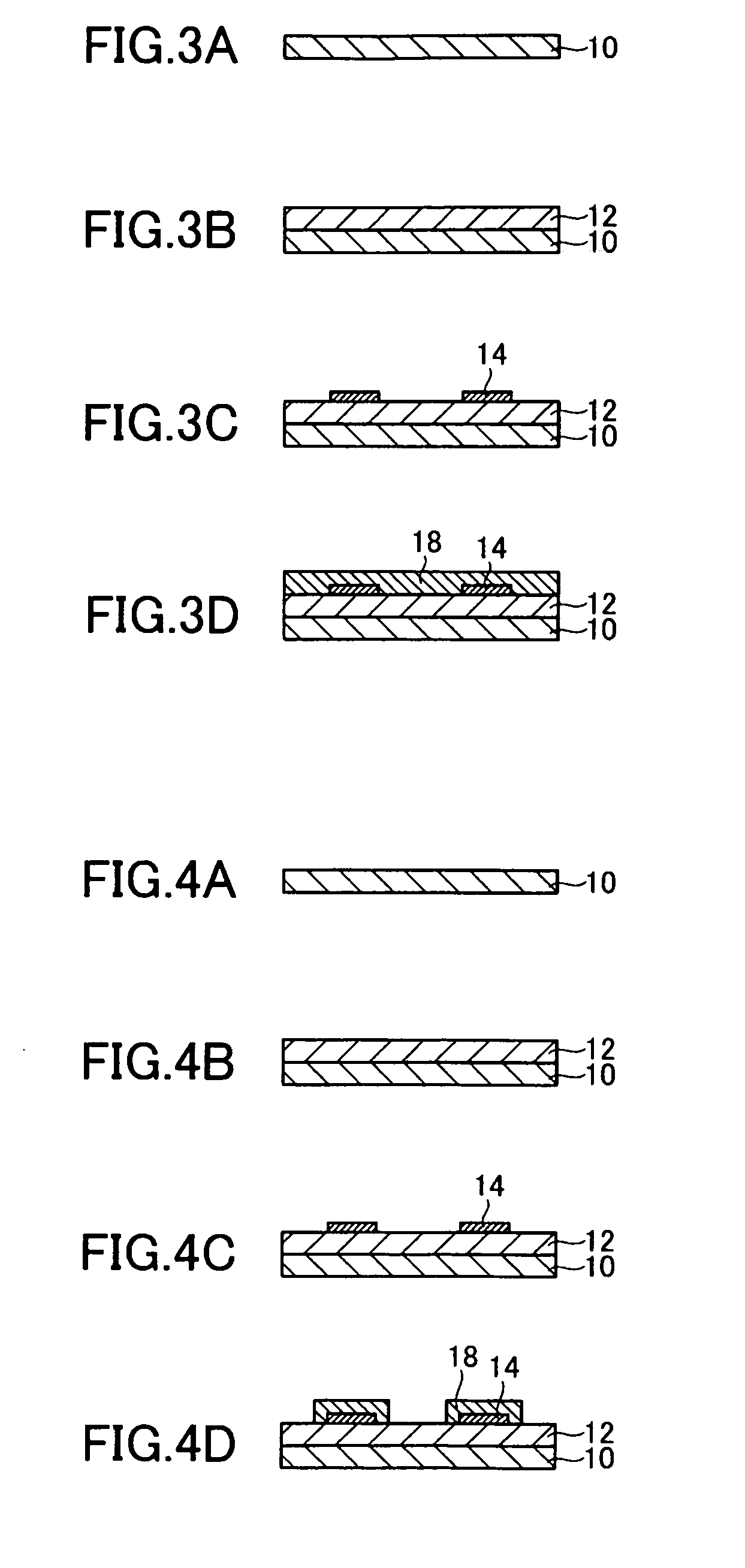

Multilayer printed wiring board having filled-via structure

InactiveUS7071424B1More highly reliableUniform thicknessInsulating substrate metal adhesion improvementDielectric materialsHigh fractureElectrical conductor

The present invention provides a multilayer printed wiring board having a filled viahole structure advantageously usable for forming a fine circuit pattern thereon, and having an excellent resistance against cracking under a thermal shock or due to heat cycle. The multilayer printed wiring board is comprised of conductor circuitry layers and interlaminar insulative resin layers deposited alternately one on another, the interlaminar insulative resin layers each having formed through them holes each filled with a plating layer to form a viahole. The surface of the plating layer exposed out of the hole for the viahole is formed substantially flat and lies at a substantially same level as the surface of the conductor circuit disposed in the interlaminar insulative resin layer. The thickness of the conductor circuitry layer is less than a half of the viahole diameter and less than 25 μm. The inner wall of the hole formed in the interlaminar insulative resin layer is roughened and an electroless plating layer is deposited on the roughened surface. An electroplating layer is filled in the hole including the electroless plating layer to form the viahole. The interlaminar insulative resin layer is formed from a composite of a fluororesin showing a high fracture toughness and a heat-resistant thermoplastic resin, a composite of fluororesin and thermosetting resin or a composite of thermosetting and thermoplastic resins.

Owner:IBIDEN CO LTD

Fluoropolymer dielectric composition for use in circuitized substrates and circuitized substrate including same

InactiveUS20060180936A1Produced successfullyDielectric materialsSemiconductor/solid-state device detailsFluoropolymerDielectric layer

A dielectric composition for forming a dielectric layer usable in circuitized substrates such as PCBs, chip carriers and the like, the composition including at least two fluoropolymers and two inorganic fillers. A circuitized substrate including at least one such dielectric layer and at least one conductive layer thereon is also provided.

Owner:TTM TECH NORTH AMERICA LLC

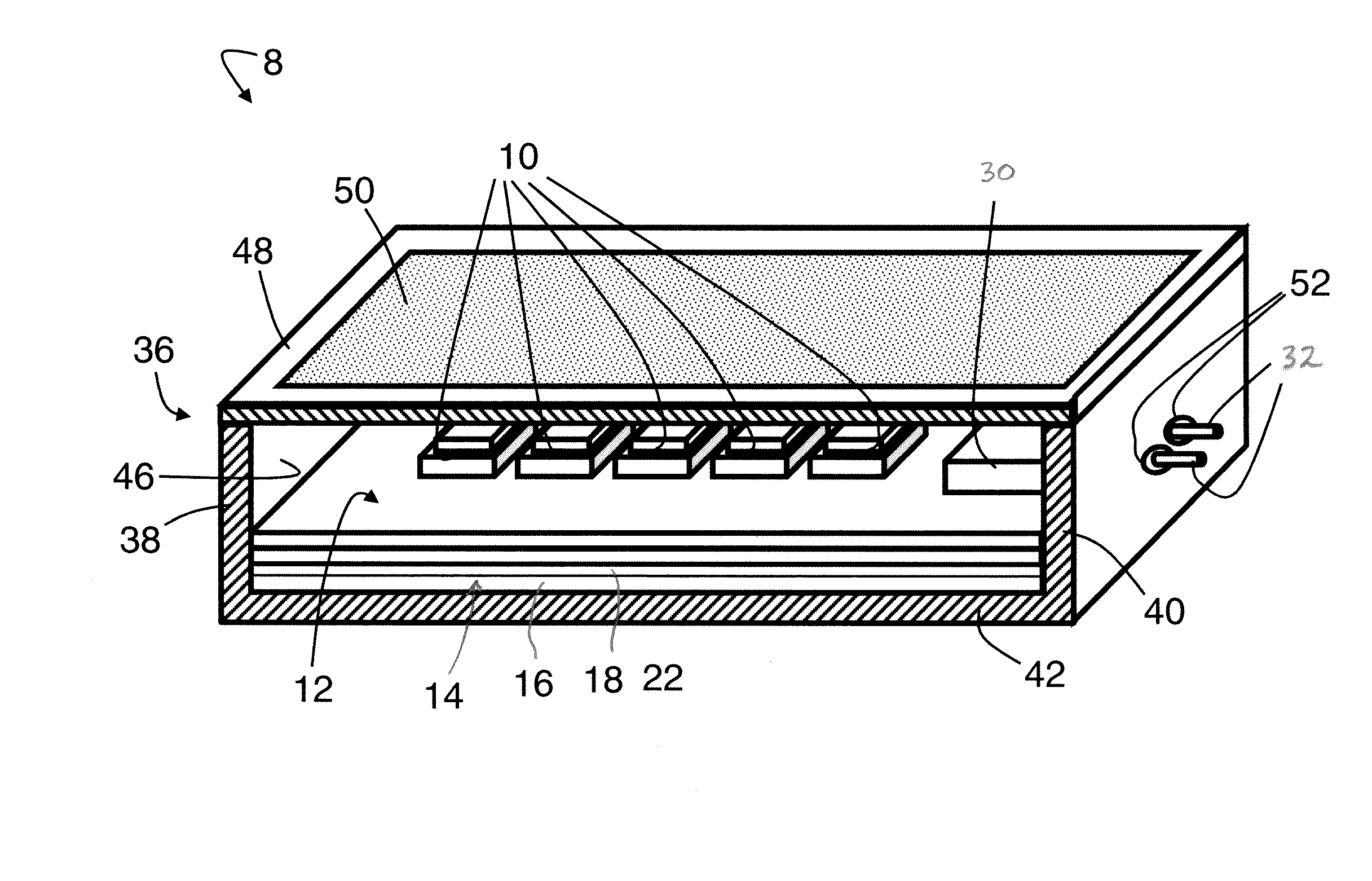

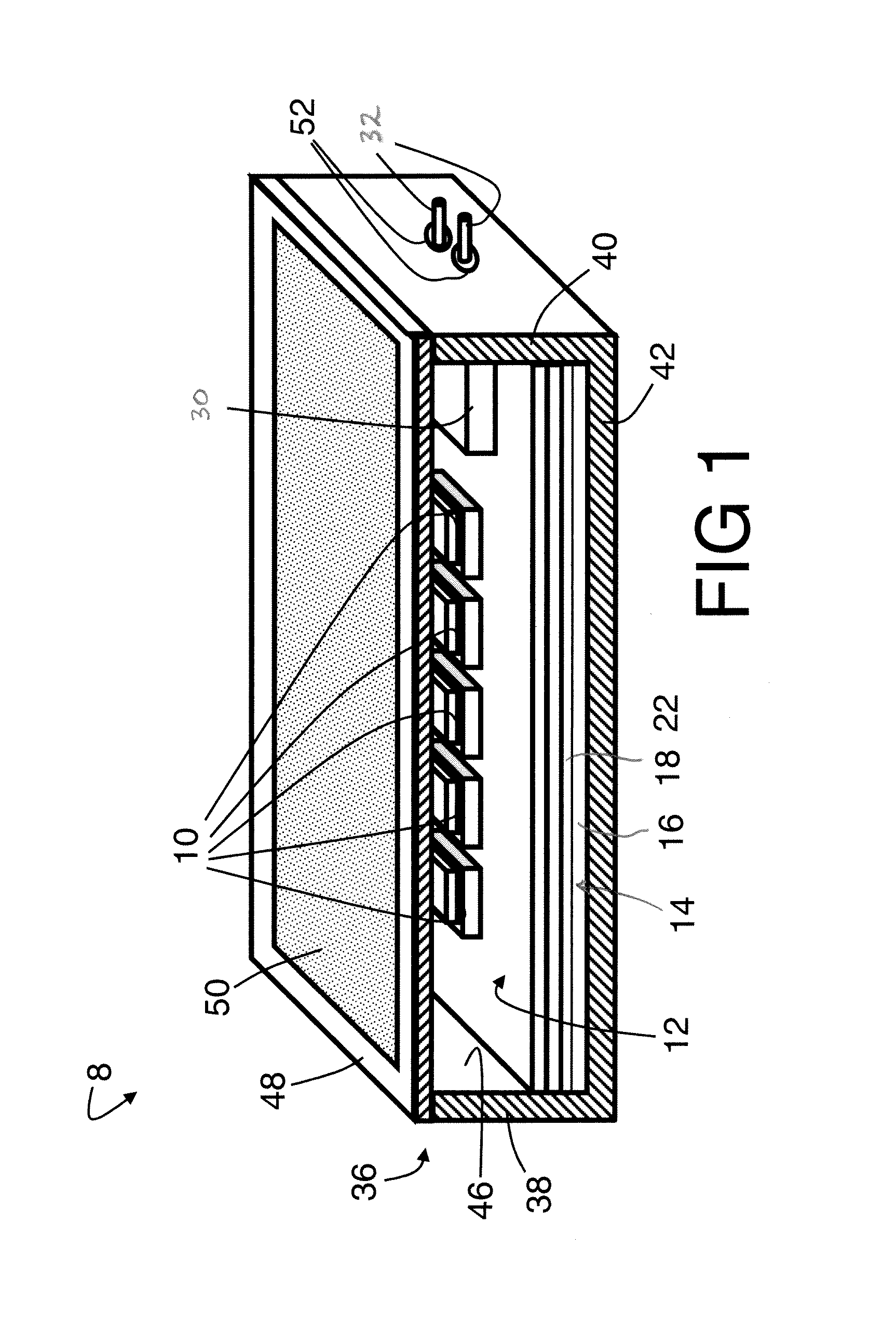

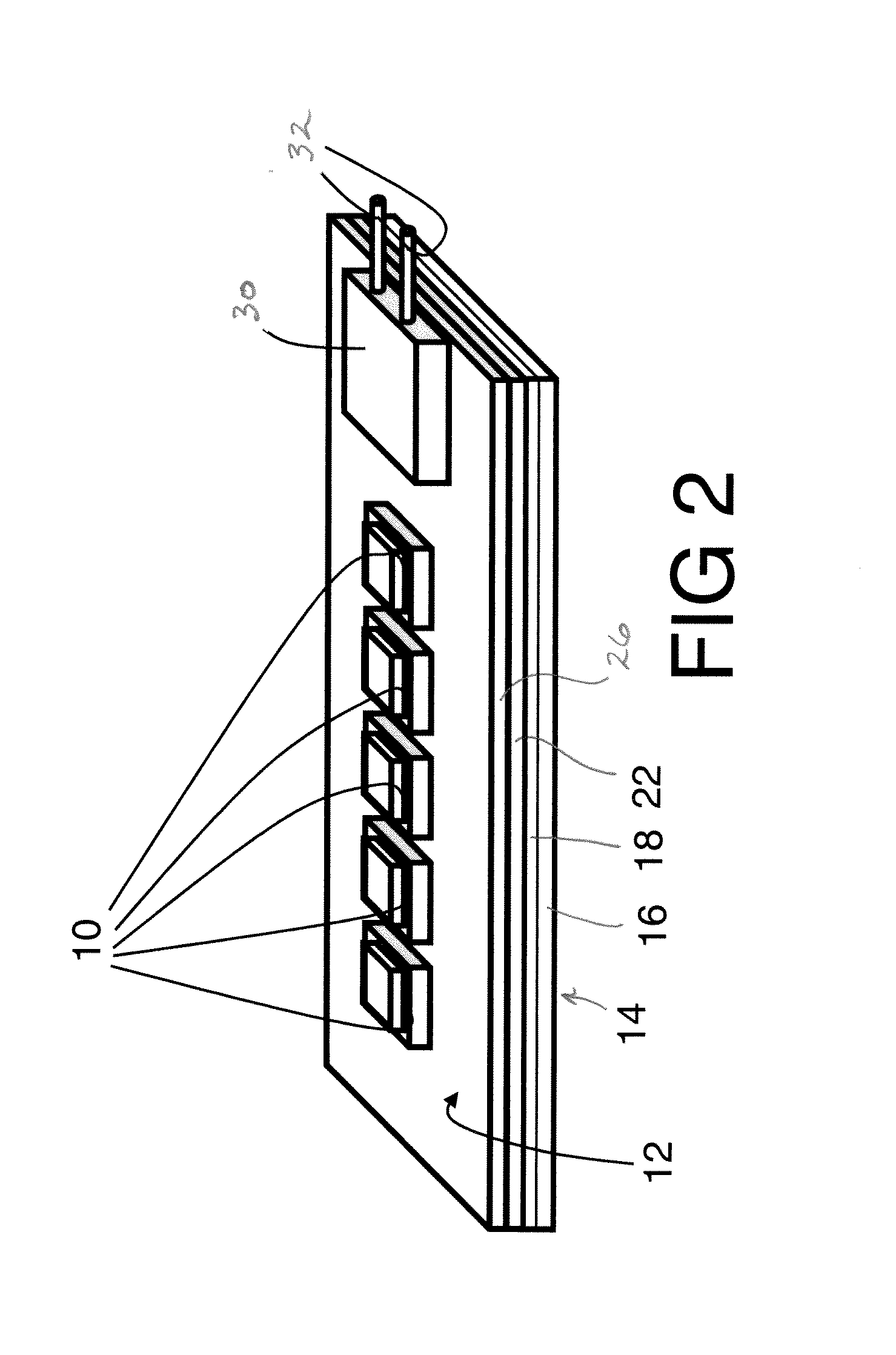

Incorporating reflective layers into LED systems and/or components

A light emitting apparatus includes a support having circuitry disposed thereon, at least one light emitting diode (LED) chip mounted on the support and in electrical communication with the circuitry and a reflective layer on the support adjacent the at least one chip.

Owner:GE LIGHTING SOLUTIONS LLC

Particulate filled fluoropolymer coating composition and method of making article therefrom

Processes for preparing an electrical substrate material include combining a ceramic modifier, a fluoropolymer coating composition and a silicone oil comprising a methyl-terminated polydimethyl siloxane, to yield a particle filled fluoropolymer coating composition. The fluoropolymer coating composition is applied to a fabric substrate to yield an electrical substrate material.

Owner:TONOGA

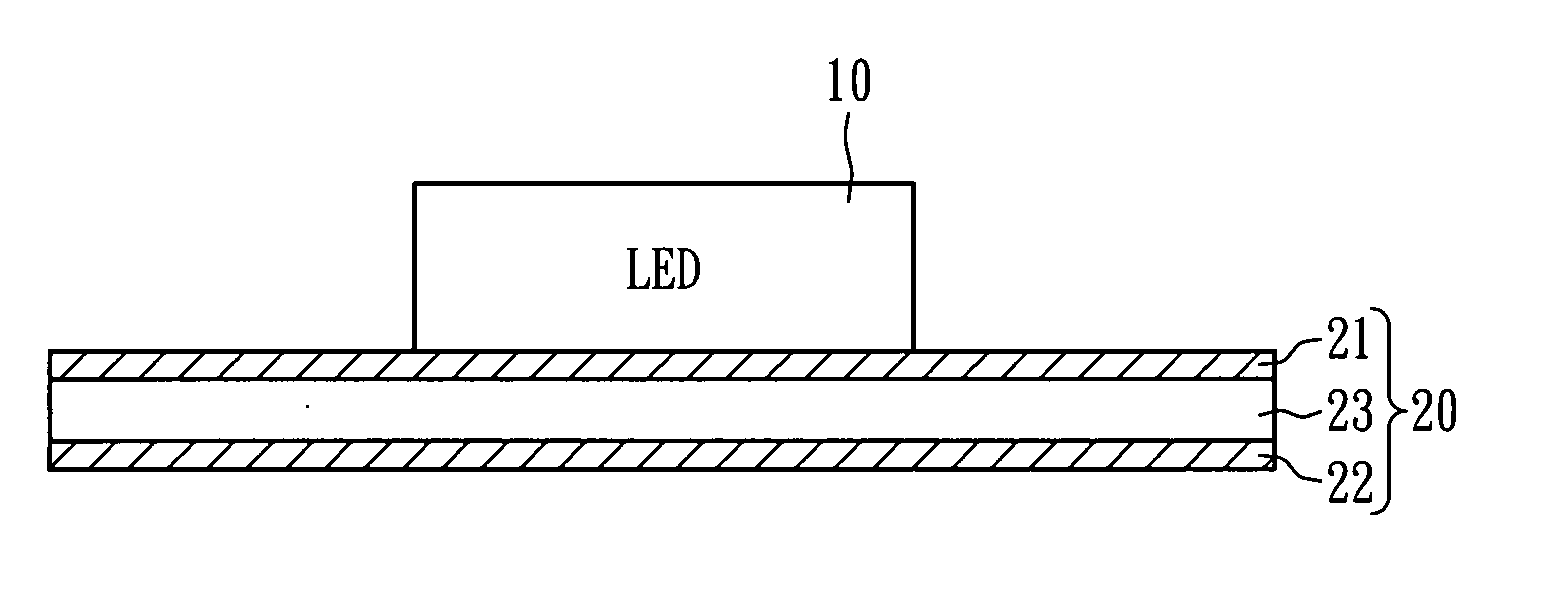

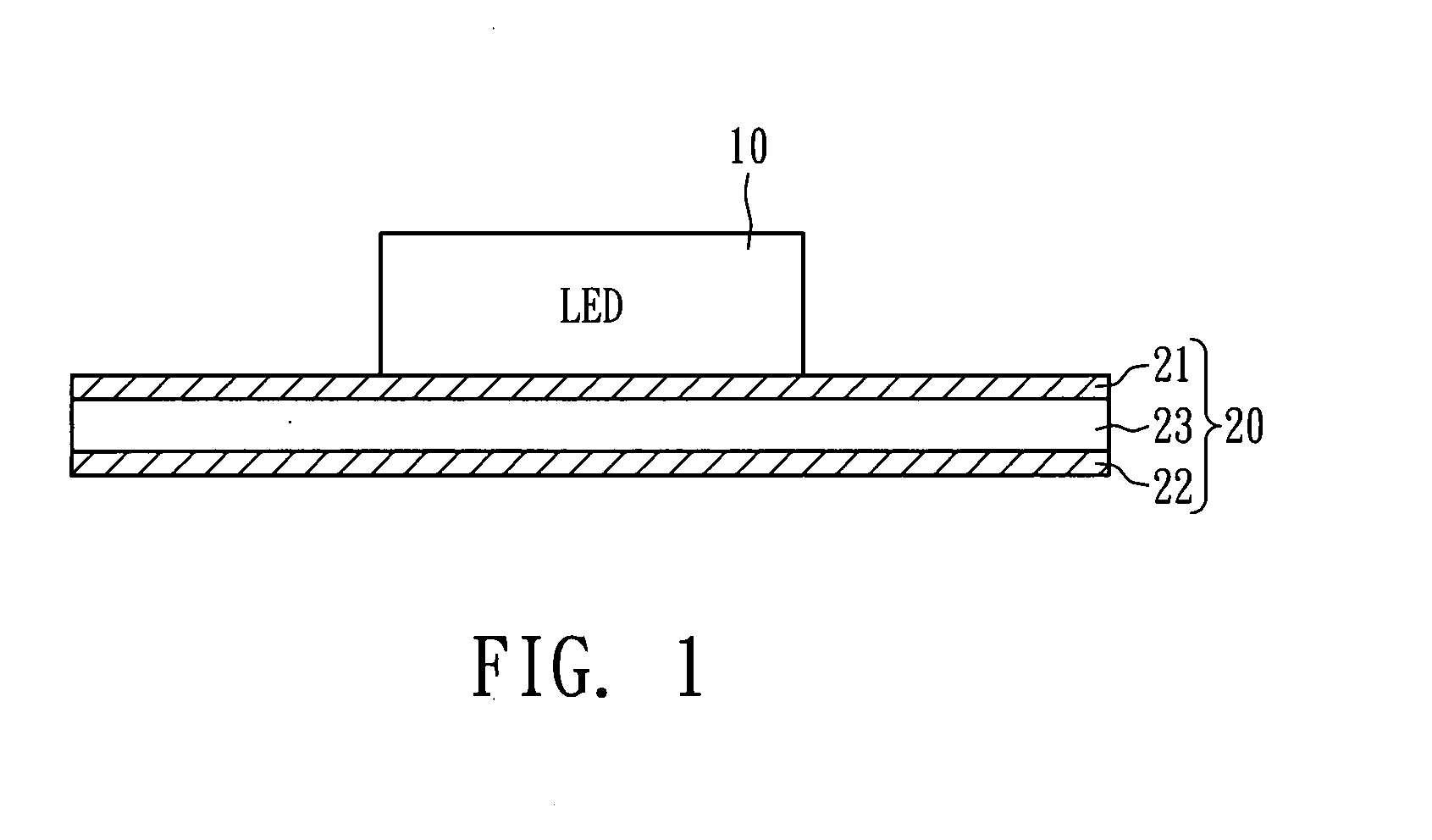

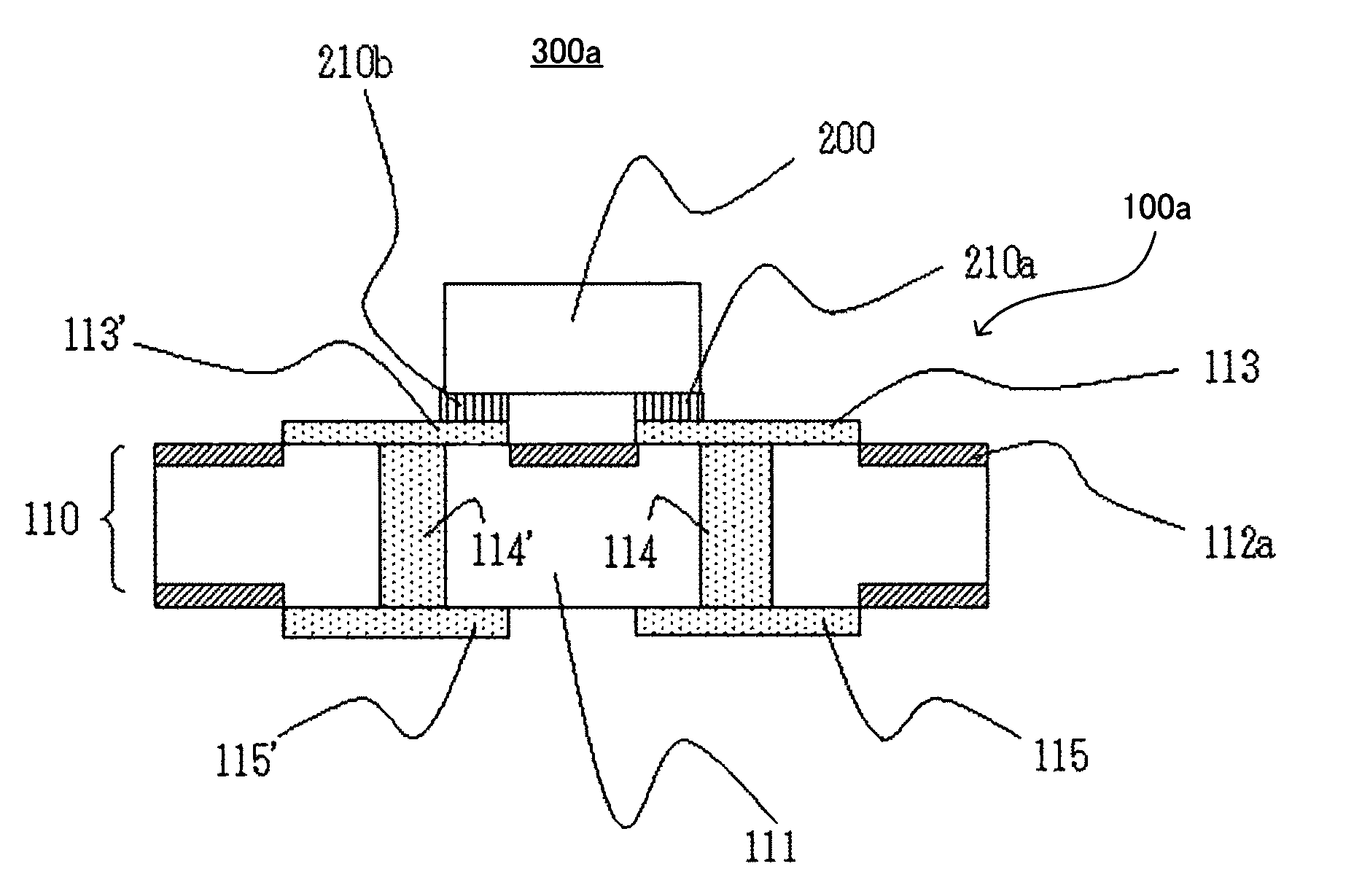

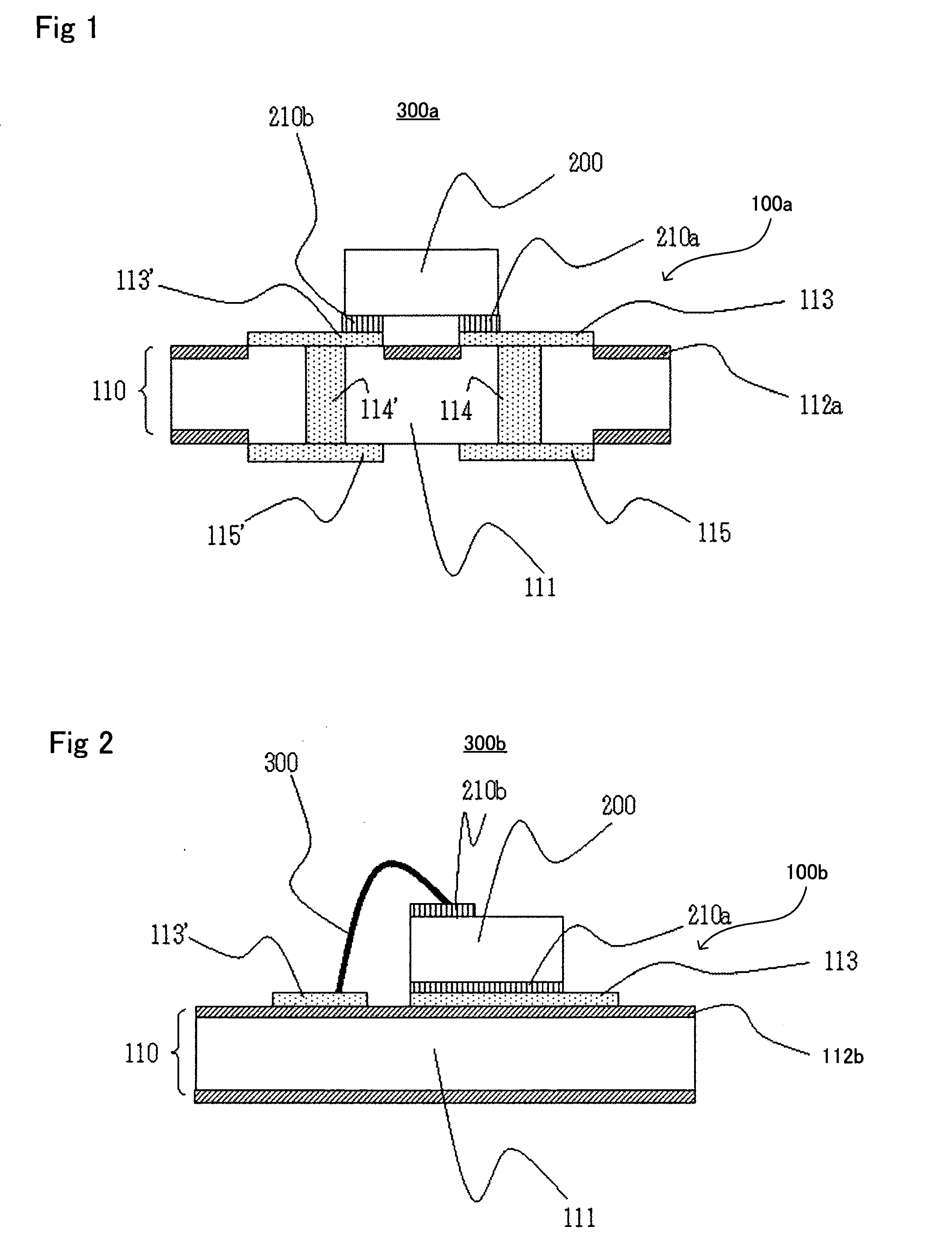

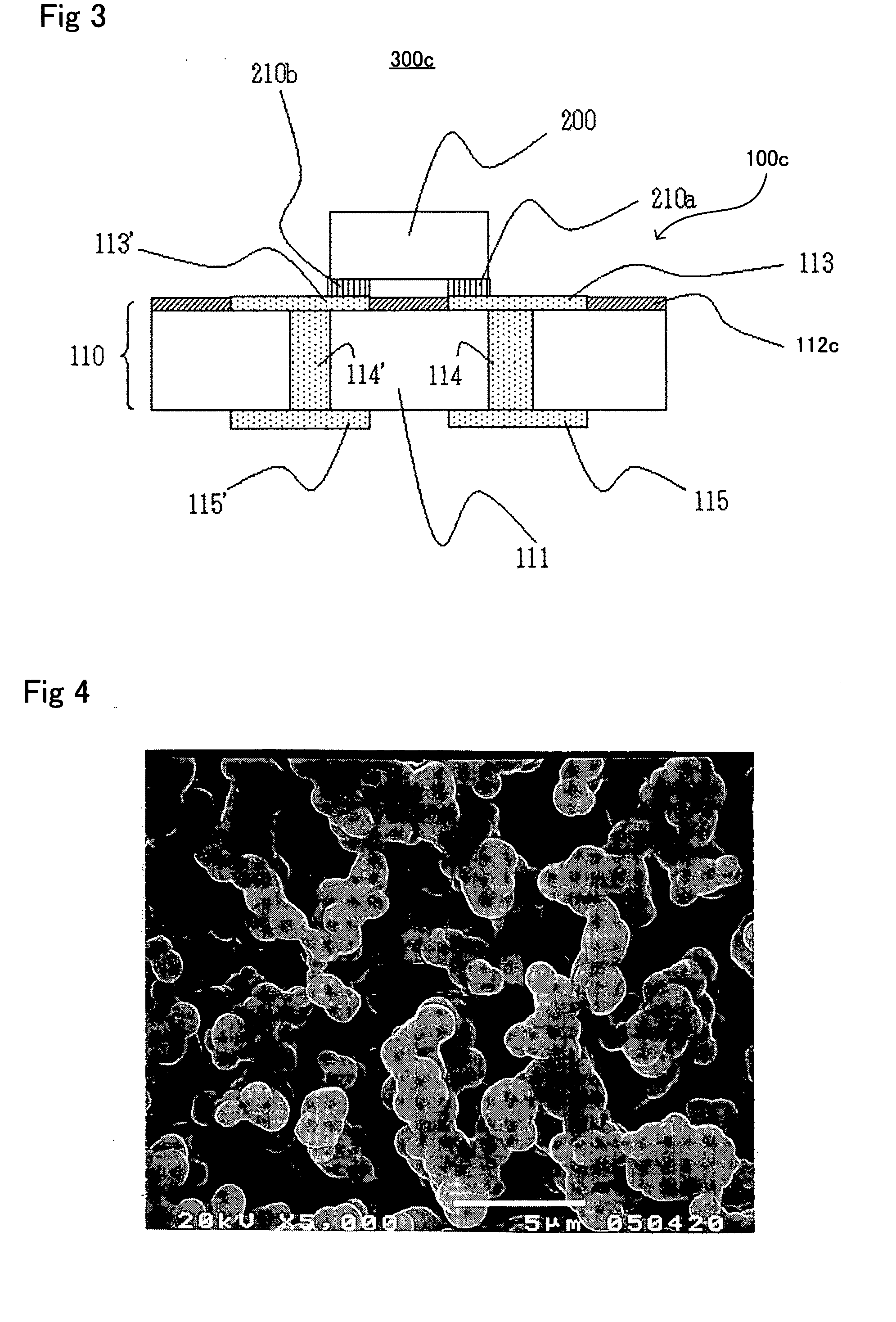

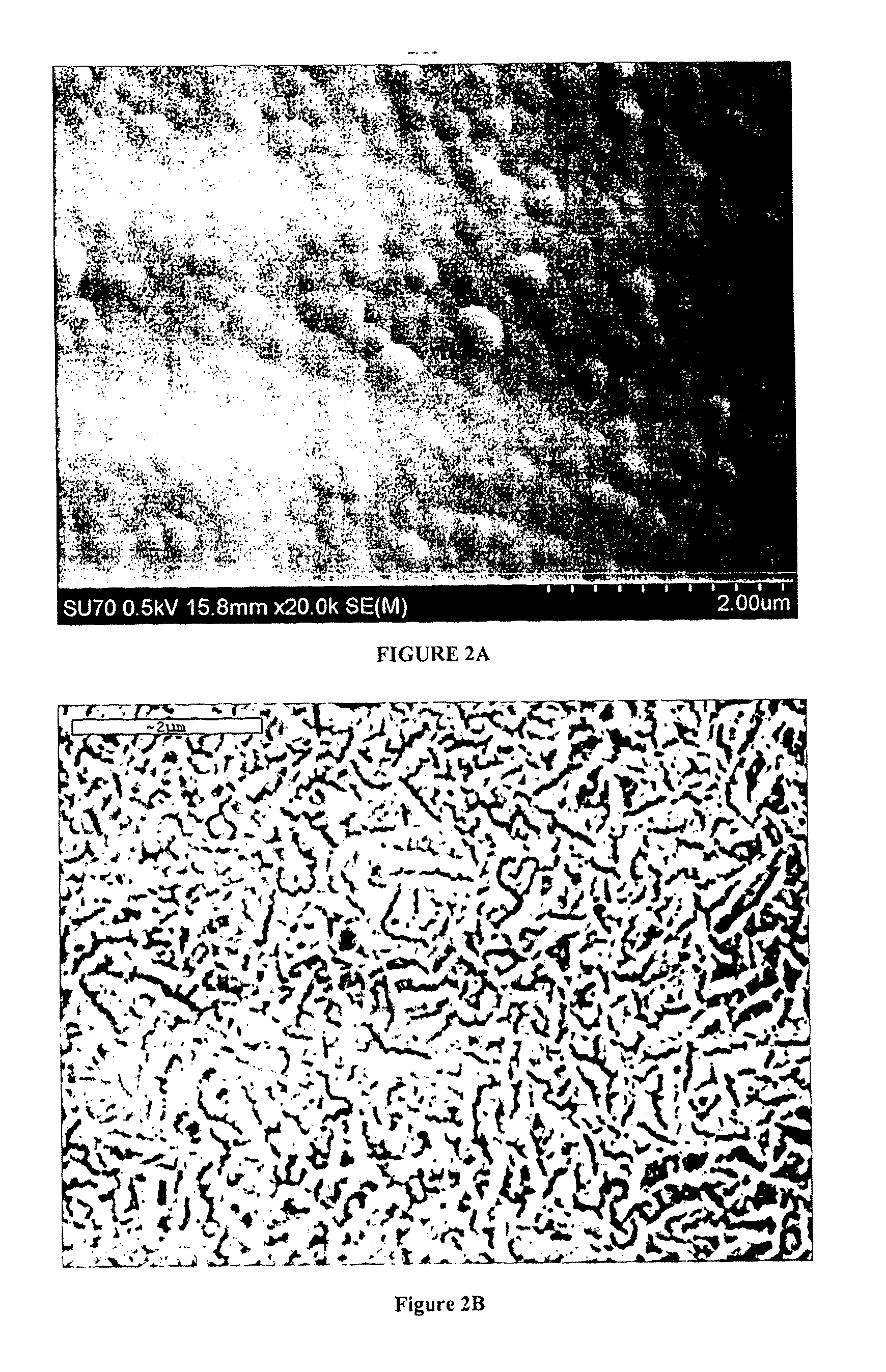

Heat dissipation substrate for electronic device

InactiveUS20080057333A1Improve bindingLow thermal conductivityInsulating substrate metal adhesion improvementDielectric materialsRough surfaceConductive polymer

A heat dissipation substrate for an electronic device comprises a first metal layer, a second metal layer, and a thermally conductive polymer dielectric insulating layer. A surface of the first metal layer carries the electronic device, e.g., a light-emitting diode (LED) device. The thermally conductive polymer dielectric insulating layer is stacked between the first metal layer and the second metal layer in a physical contact manner, and interfaces therebetween include at least one micro-rough surface with a roughness Rz larger than 7.0. The micro-rough surface includes a plurality of nodular projections, and the grain sizes of the nodular projections mainly are in a range of 0.1-100 μm. The heat dissipation substrate has a thermal conductivity larger than 1.0 W / m·K, and a thickness smaller than 0.5 mm, and comprises (1) a fluorine-containing polymer with a melting point higher than 150° C. and a volume percentage in a range of 30-60%, and (2) thermally conductive filler dispersed in the fluorine-containing polymer and having a volume percentage in a range of 40-70%.

Owner:POLYTRONICS TECH

Ceramic Substrate for Mounting a Light Emitting Element and Method for Manufacturing the Same

InactiveUS20070252523A1Damage suppressionIncrease brightnessDischarge tube luminescnet screensCircuit optical detailsLength waveNitride

A ceramic substrate for mounting a light emitting element. The ceramic substrate has a placement surface for placing a light emitting element having an electrode; and an electrode electrically-connected with the electrode of the light emitting element, wherein the ceramic substrate comprises a substrate body consisting of a nitride ceramics; and a coat layer coating at least a part of a surface of the substrate body and consisting of a ceramics different from the nitride ceramics forming the substrate body; and the coat layer has an optical reflectance of 50% or more for any light having a wavelength of from 300 to 800 nm, which can increase a luminance of the light emitting element by reflecting the light emitted from the element efficiently with certainty, and which has a high heat radiation property; and a manufacturing method therefor.

Owner:TOKUYAMA CORP

Apparatus with a Multi-Layer Coating and Method of Forming the Same

ActiveUS20110253429A1Prevent oxidationPrevent and hinder solderingDielectric materialsSolid-state devicesEngineeringPrinted circuit board

In some embodiments, a printed circuit board (PCB) comprises a substrate comprising an insulating material. The PCB further comprises a plurality of conductive tracks attached to at least one surface of the substrate. The PCB further comprises a multi-layer coating deposited on the at least one surface of the substrate. The multi-layer coating (i) covers at least a portion of the plurality of conductive tracks and (ii) comprises at least one layer formed of a halo-hydrocarbon polymer. The PCB further comprises at least one electrical component connected by a solder joint to at least one conductive track, wherein the solder joint is soldered through the multi-layer coating such that the solder joint abuts the multi-layer coating.

Owner:HZO INC

Method for the application of a conformal nanocoating by means of a low pressure plasma process

InactiveCN102821873ALow costCoating thicknessDielectric materialsElectric discharge tubesNanostructureNanometre

The invention relates to a conformal nanocoating applied by a low pressure plasma process. The invention also relates to a method for making such a conformal nanocoating on a three-dimensional nanostructure, in particular a three-dimensional structure containing electrically conductive and non-conductive elements.

Owner:EUROPLASMA

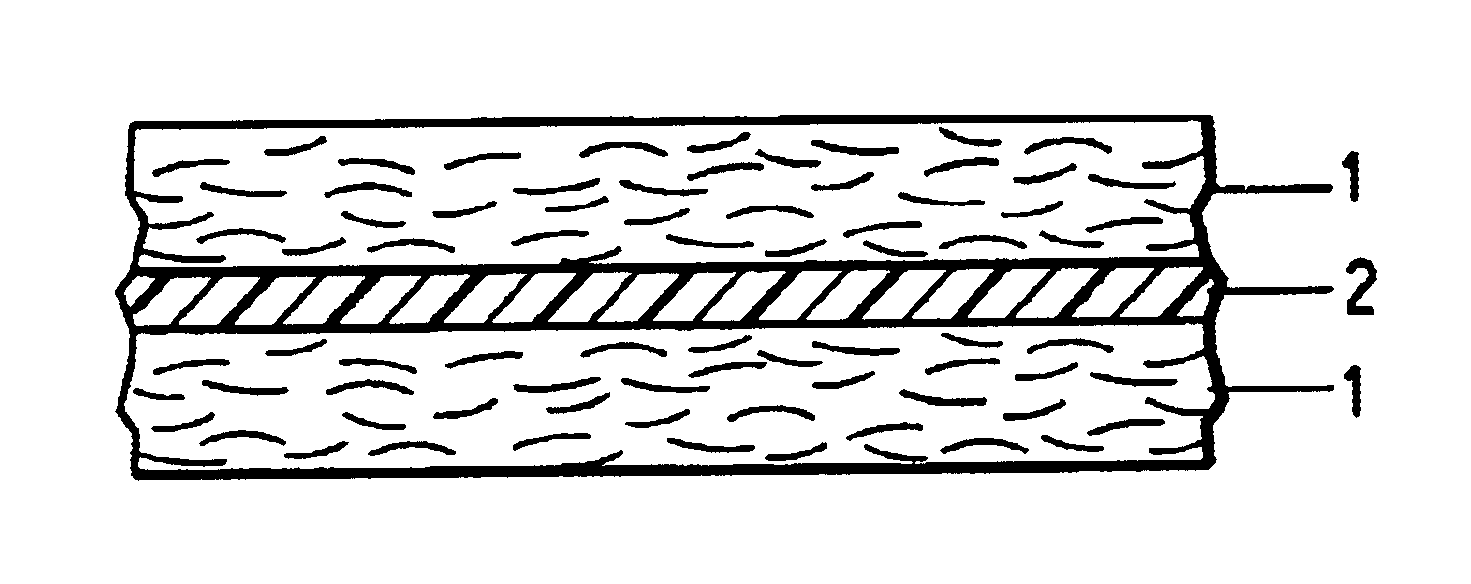

Sheet material especially useful for circuit boards

InactiveUS6929848B2Semiconductor/solid-state device detailsSolid-state devicesFiberPolymer chemistry

A sheet comprising thermoplastic polymer (TP) and short high tensile modulus fibers, in which the concentration of TP in the middle of the sheet is higher than at the surface of the sheet, useful for making prepregs with a thermoset resin.

Owner:EI DU PONT DE NEMOURS & CO

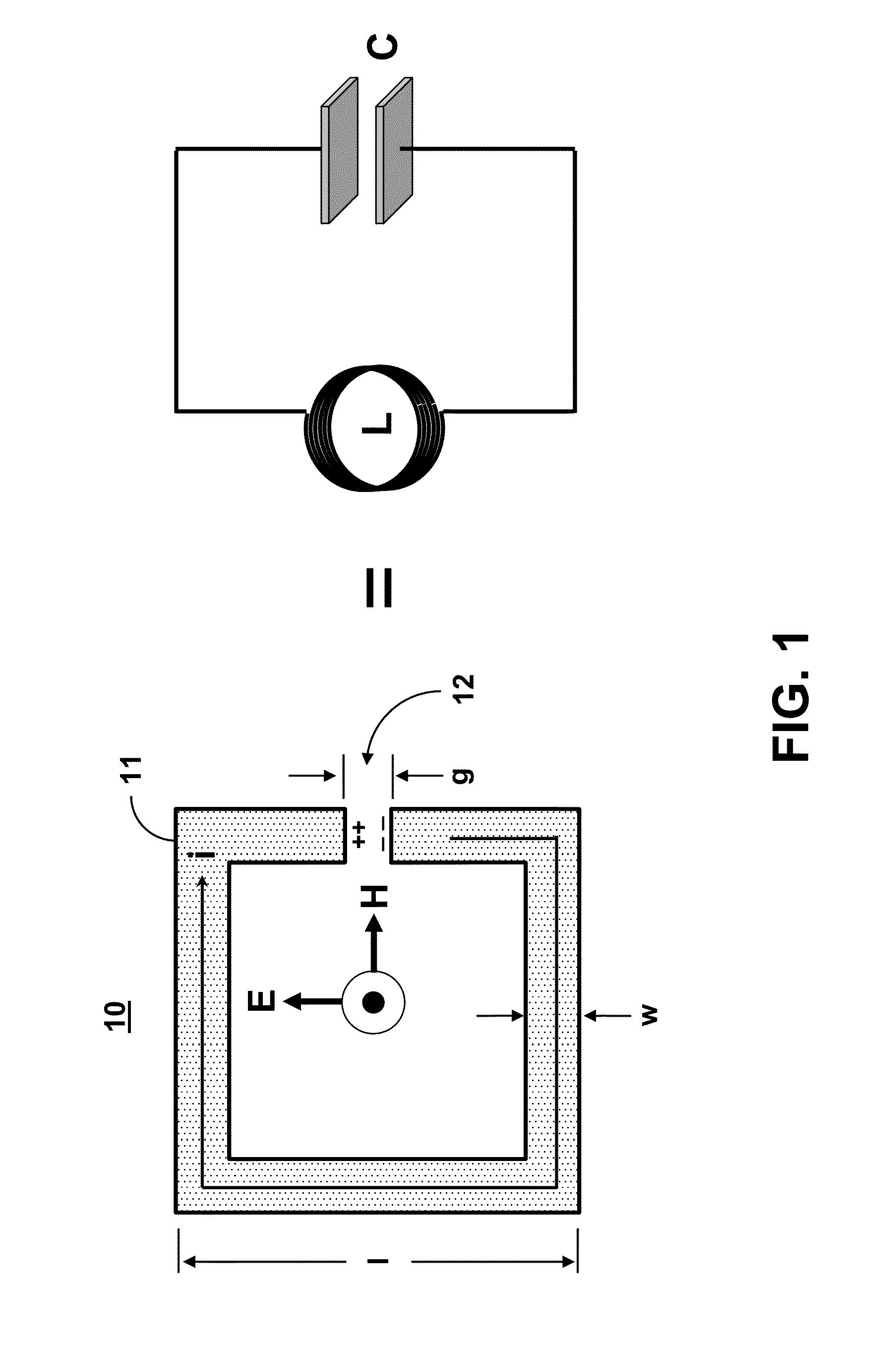

Terahertz metamaterials

ActiveUS8803637B1Reduce dielectric lossesFlexible and designDielectric materialsCross-talk/noise/interference reductionTerahertz radiationDielectric substrate

Terahertz metamaterials comprise a periodic array of resonator elements disposed on a dielectric substrate or thin membrane, wherein the resonator elements have a structure that provides a tunable magnetic permeability or a tunable electric permittivity for incident electromagnetic radiation at a frequency greater than about 100 GHz and the periodic array has a lattice constant that is smaller than the wavelength of the incident electromagnetic radiation. Microfabricated metamaterials exhibit lower losses and can be assembled into three-dimensional structures that enable full coupling of incident electromagnetic terahertz radiation in two or three orthogonal directions. Furthermore, polarization sensitive and insensitive metamaterials at terahertz frequencies can enable new devices and applications.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

Plasma-Polymerized Polymer Coating

ActiveUS20130033825A1Improve performanceEasy to assembleDielectric materialsPrinted circuit secondary treatmentEngineeringPolymer coatings

An electrical or electro-optical assembly comprising a substrate comprising an insulating material, at least one conductive track present on at least one surface of the substrate, at least one electrical or electro-optical component connected to at least one of the at least one conductive track, and a continuous coating comprising one or more plasma-polymerized polymers completely covering the at least one surface of the substrate, the at least one conductive track and the at least one electrical or electro-optical component.

Owner:HZO INC

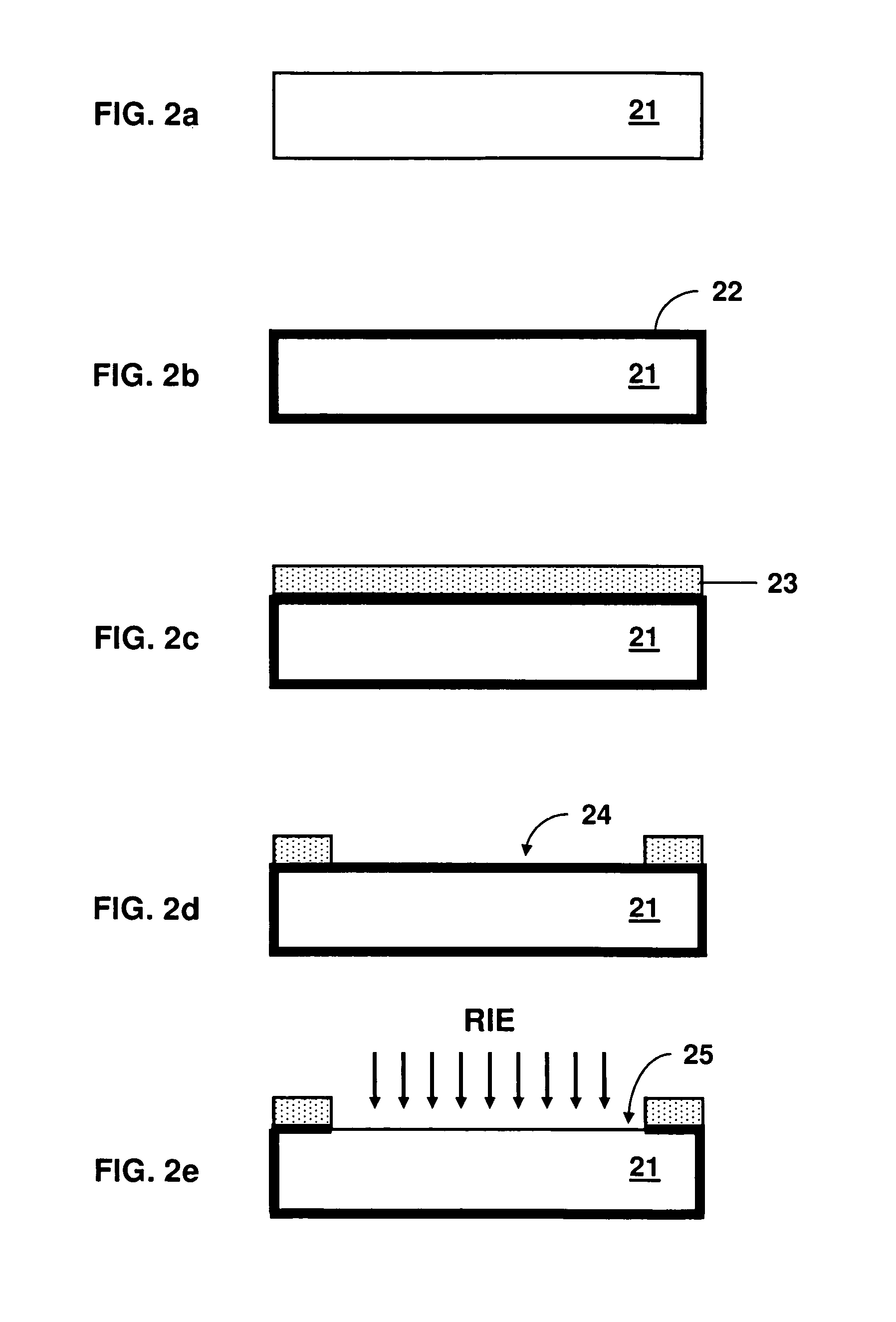

Processing low dielectric constant materials for high speed electronics

InactiveUS6297459B1Easy to fillEqually distributedPorous dielectricsInsulating substrate metal adhesion improvementPorous layerPrinted circuit board

A low dielectric constant printed circuit board includes: a low dielectric constant porous polymer layer having holes therethrough, the porous layer having pores; and a patterned metallization layer over surfaces of the low dielectric constant porous polymer layer and surfaces of the holes, the patterned metallization layer not significantly protruding into the pores of the porous layer.

Owner:SABIC INNOVATIVE PLASTICS IP BV

Solid sheet material especially useful for circuit boards

InactiveUS20030082974A1Reduce moisture absorption performanceHigh melting pointDielectric materialsSynthetic resin layered productsPolymer scienceMoisture absorption

A solid sheet which contains an nonwoven fabric made from short high tensile modulus fibers and a thermoplastic polymer having a low moisture absorption matrix resin that is useful as a substrate for circuit boards.

Owner:EI DU PONT DE NEMOURS & CO

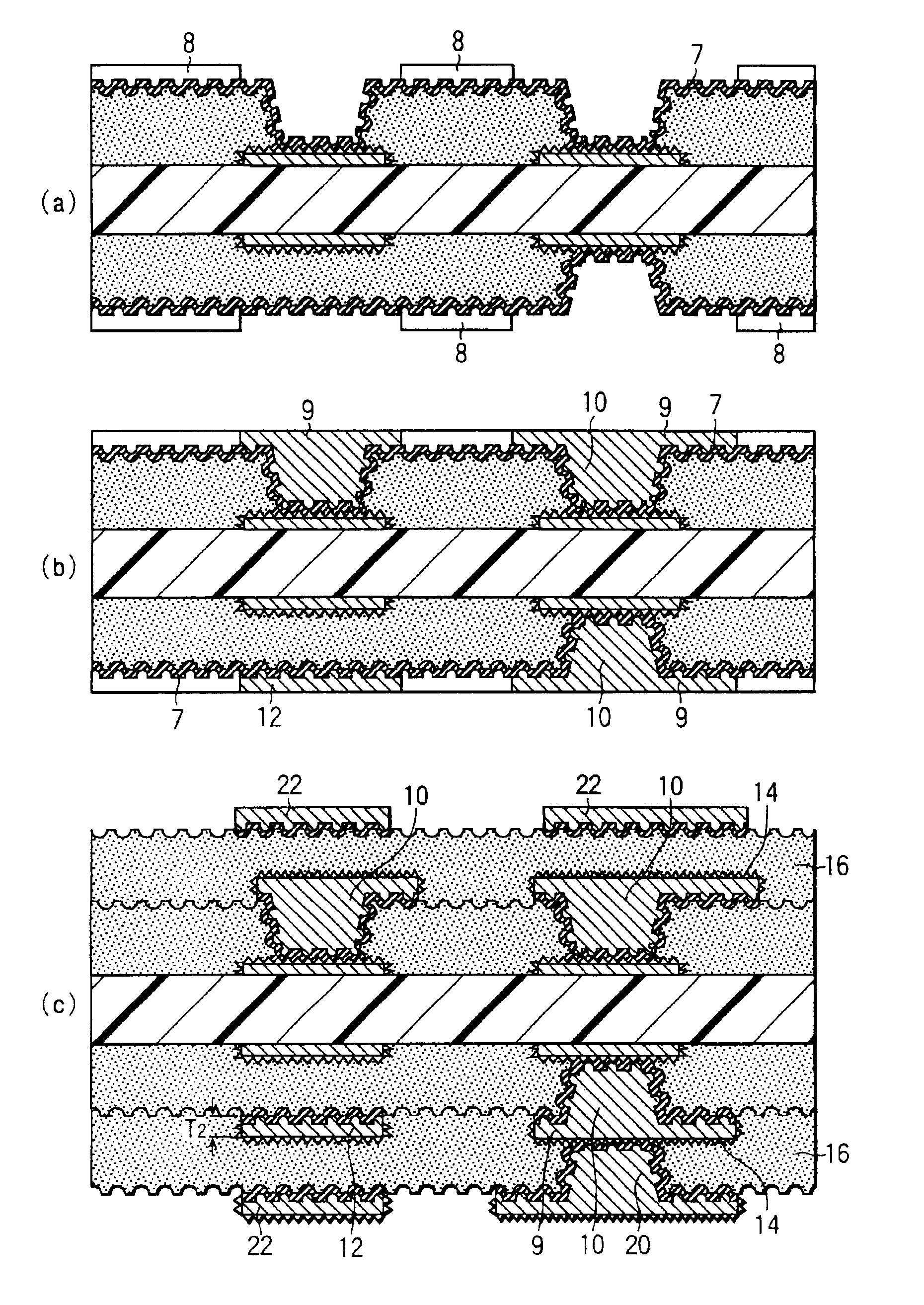

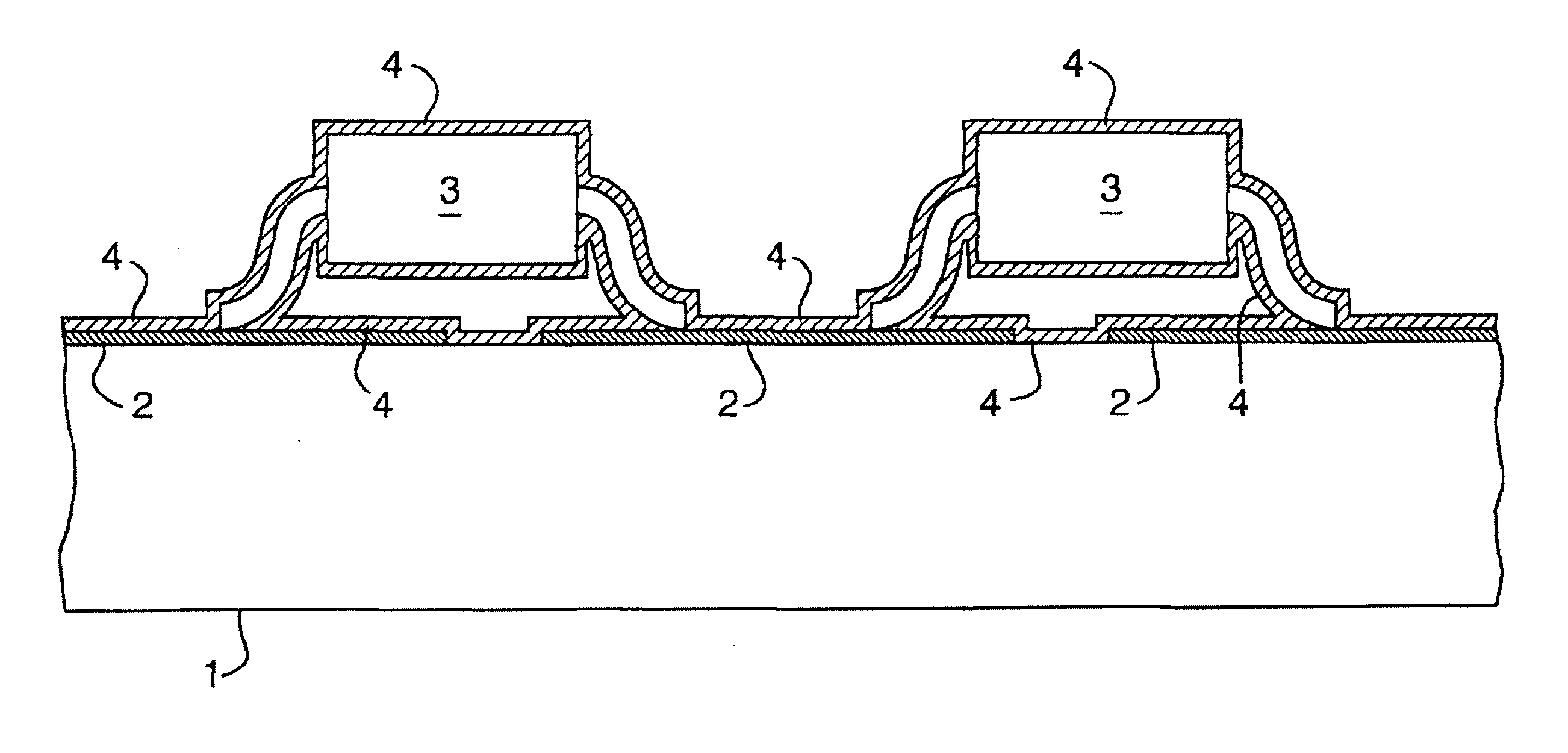

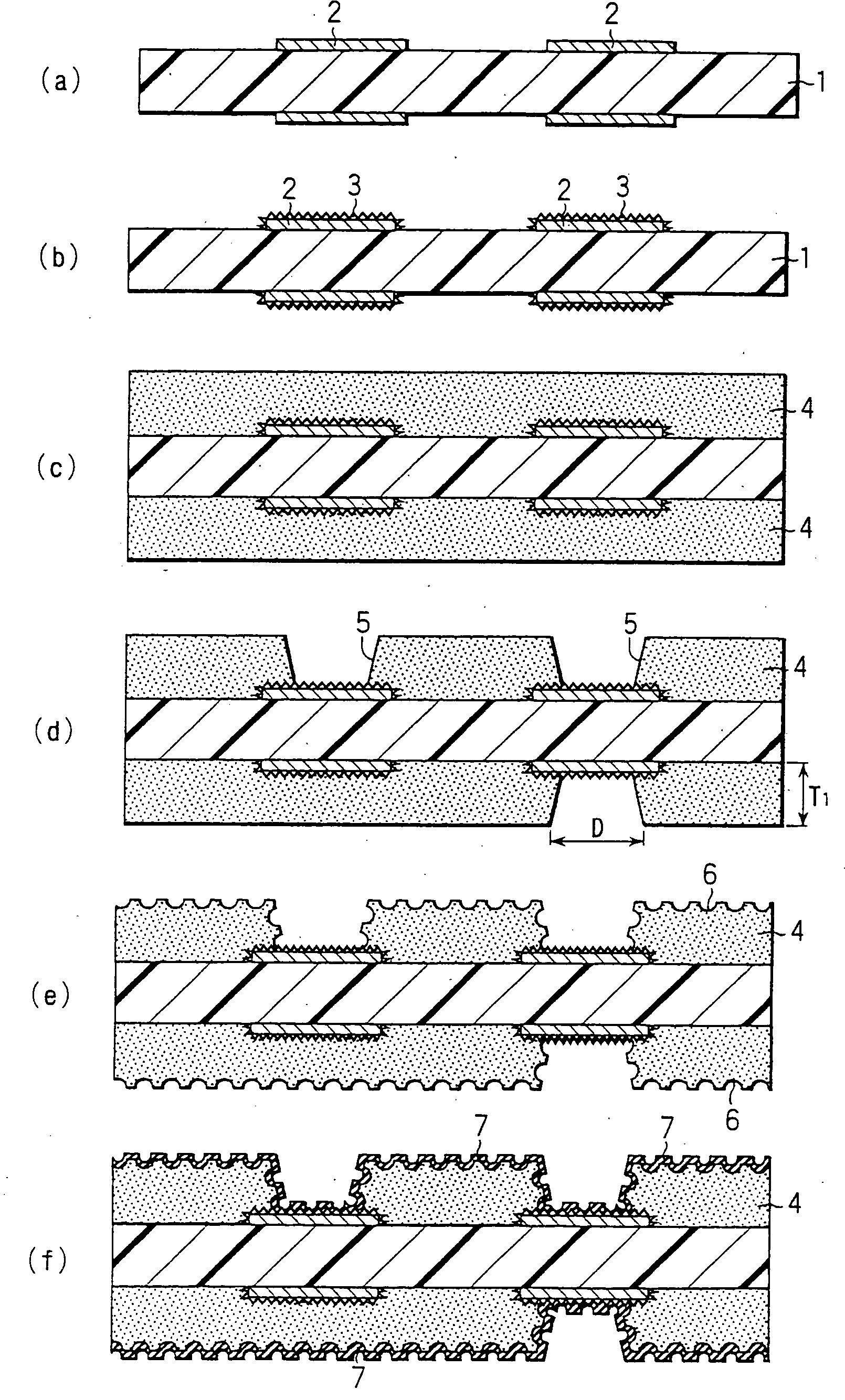

Multilayer printed wiring board with filled viahole structure

InactiveUS20050100720A1Large malleabilityAdhesionInsulating substrate metal adhesion improvementDielectric materialsElectrical conductorHigh fracture

The present invention provides a multilayer printed wiring board having a filled viahole structure advantageously usable for forming a fine circuit pattern thereon, and having an excellent resistance against cracking under a thermal shock or due to heat cycle. The multilayer printed wiring board is comprised of conductor circuitry layers and interlaminar insulative resin layers deposited alternately one on another, the interlaminar insulative resin layers each having formed through them holes each filled with a plating layer to form a viahole. The surface of the plating layer exposed out of the hole for the viahole is formed substantially flat and lies at a substantially same level as the surface of the conductor circuit disposed in the interlaminar insulative resin layer. The thickness of the conductor circuitry layer is less than a half of the viahole diameter and less than 25 μm. The inner wall of the hole formed in the interlaminar insulative resin layer is roughened and an electroless plating layer is deposited on the roughened surface. An electroplating layer is filled in the hole including the electroless plating layer to form the viahole. The interlaminar insulative resin layer is formed from a composite of a fluororesin showing a high fracture toughness and a heat-resistant thermoplastic resin, a composite of fluororesin and thermosetting resin or a composite of thermosetting and thermoplastic resins.

Owner:IBIDEN CO LTD

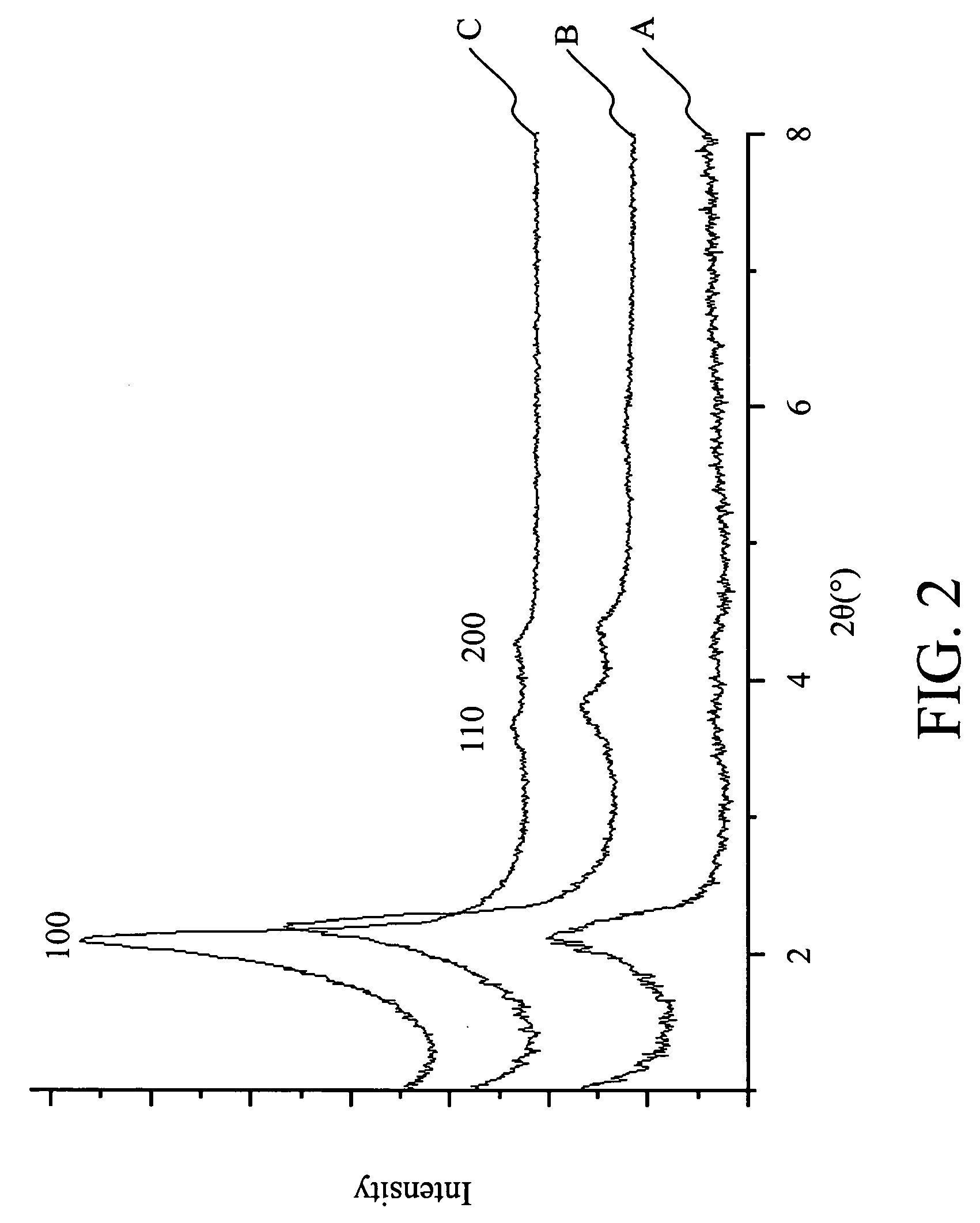

Mesoporous silica/fluorinated polymer composite material

A mesoporous silica / fluorinated polymer composite material. Made up of hydrophobic modified mesoporous silica with a pore size of 0.1 to 50 nm and a fluorinated polymer, to provide Dk<4, Df<0.04, and CTE<60 ppm, the material is suitable for use in printed circuit boards or substrates in high frequency applications.

Owner:CHUNG YUAN CHRISTIAN UNIVERSITY

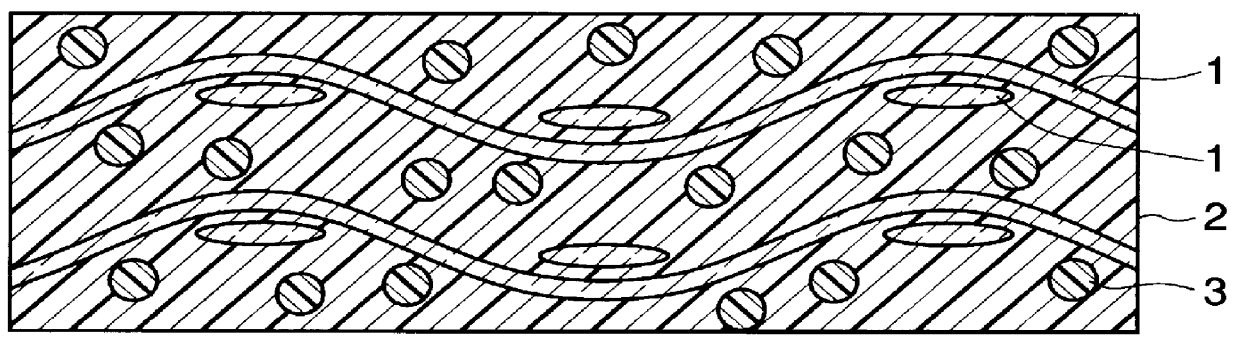

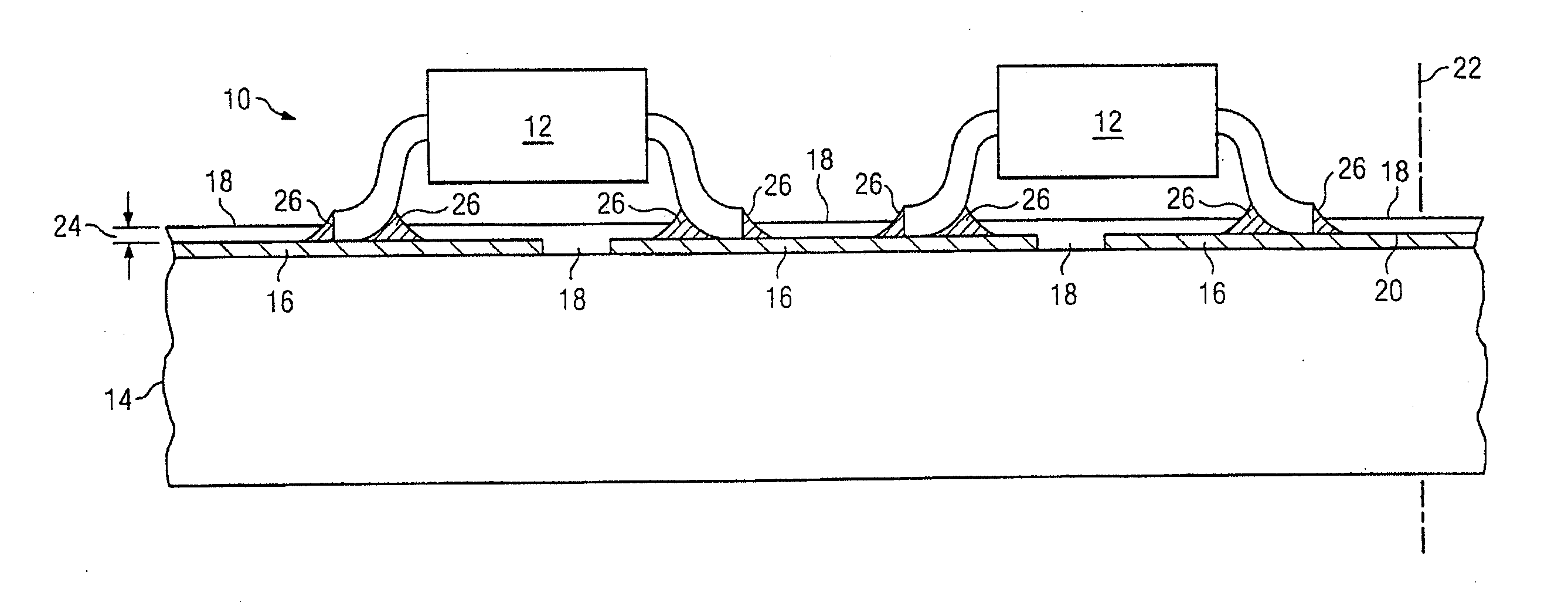

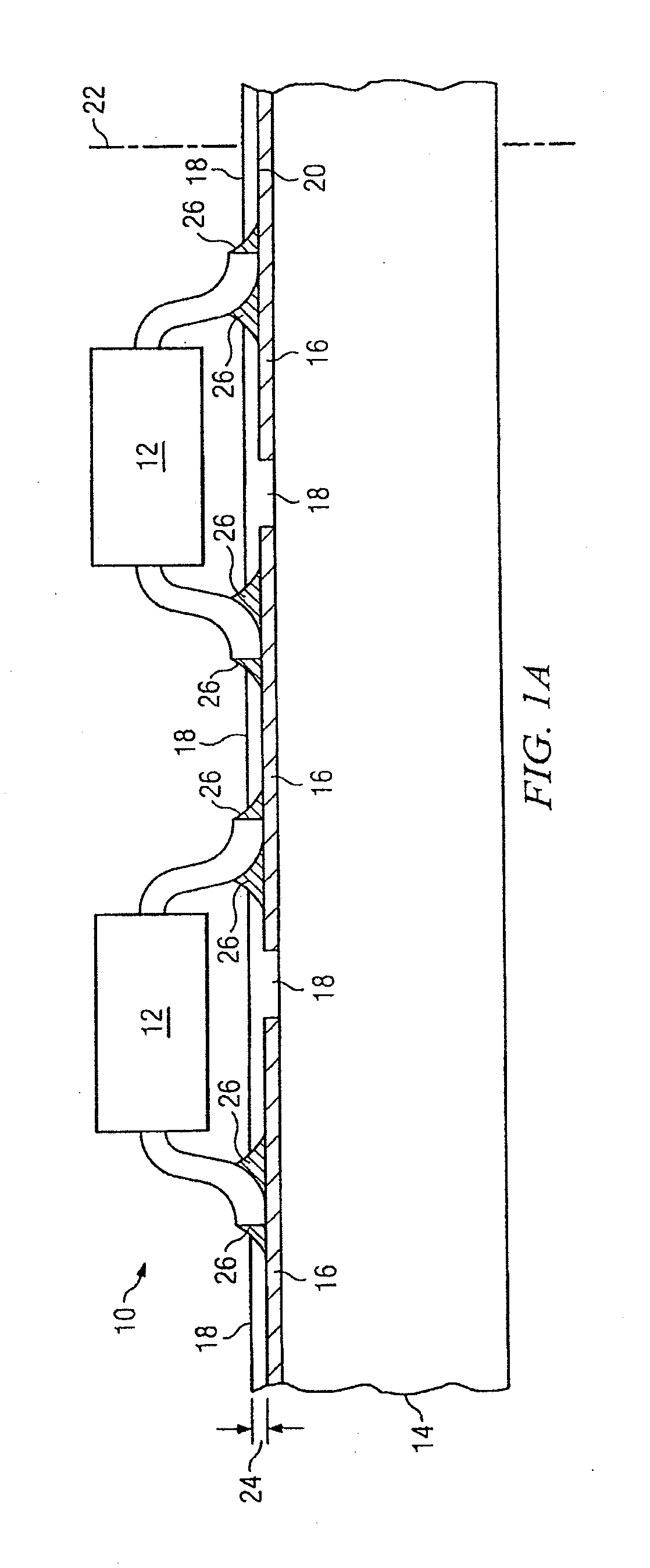

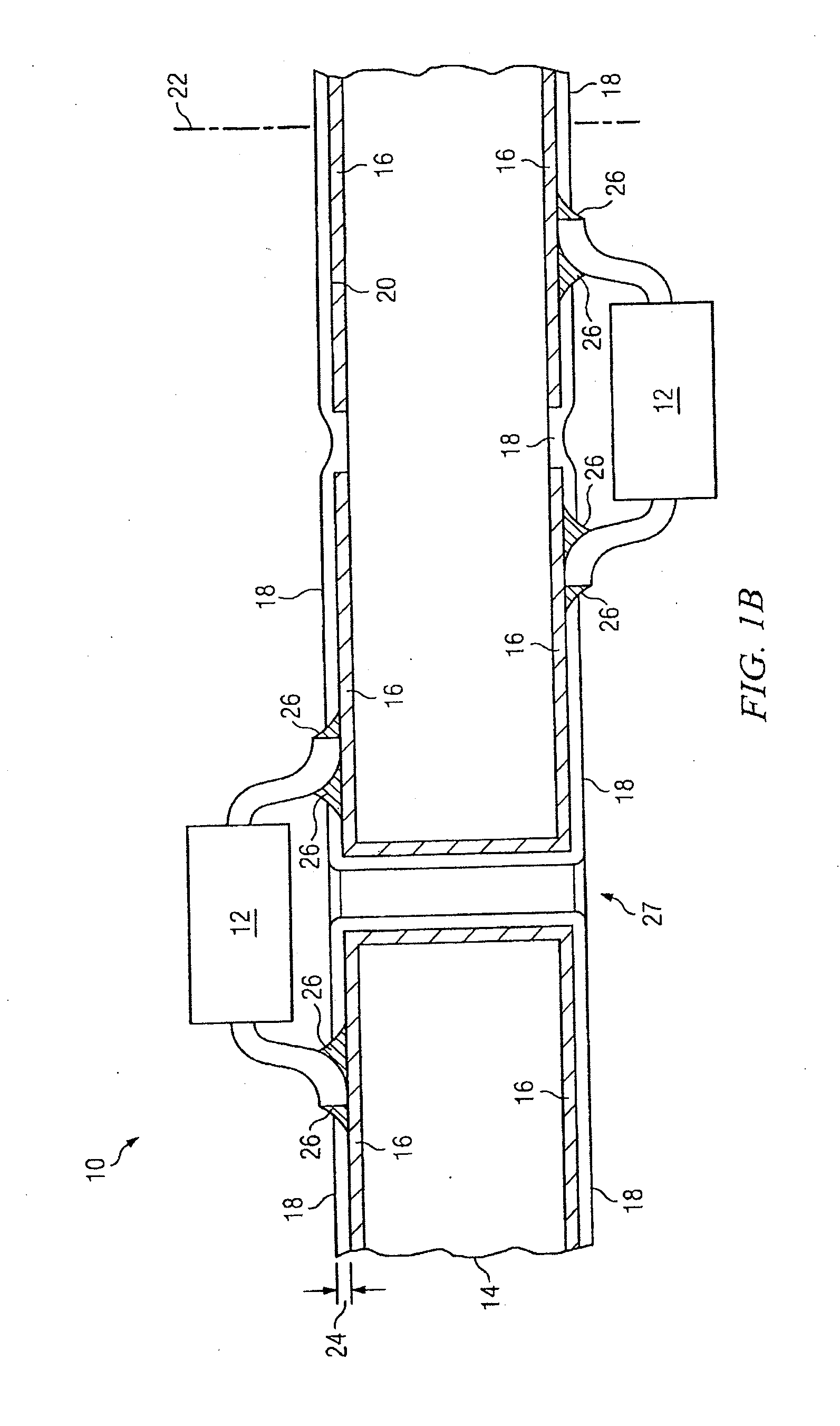

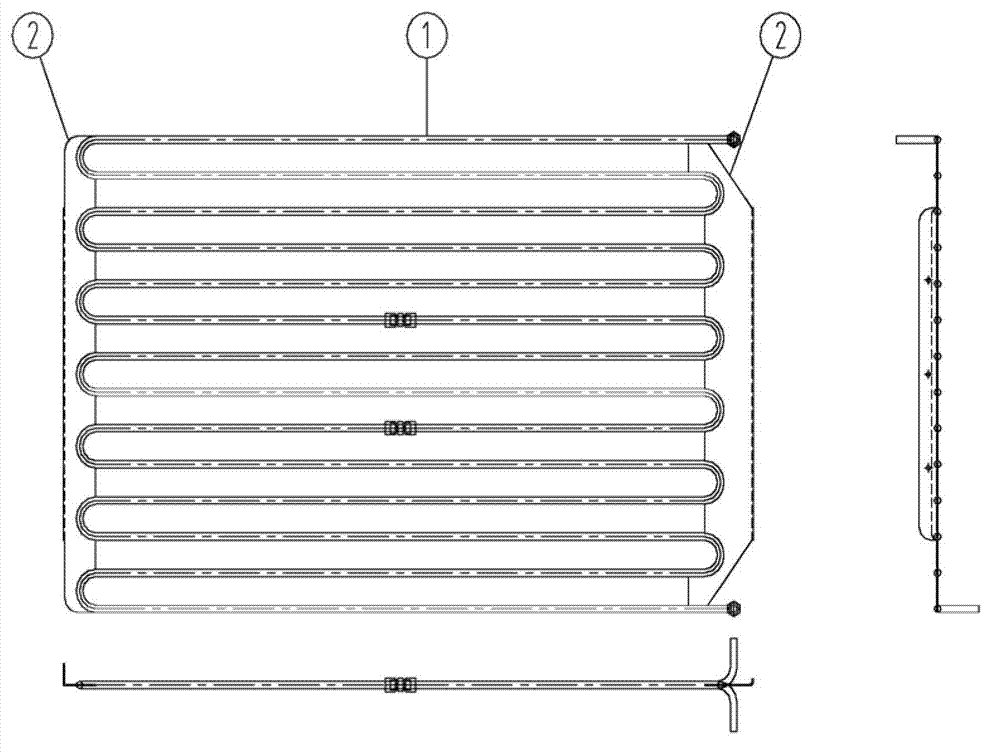

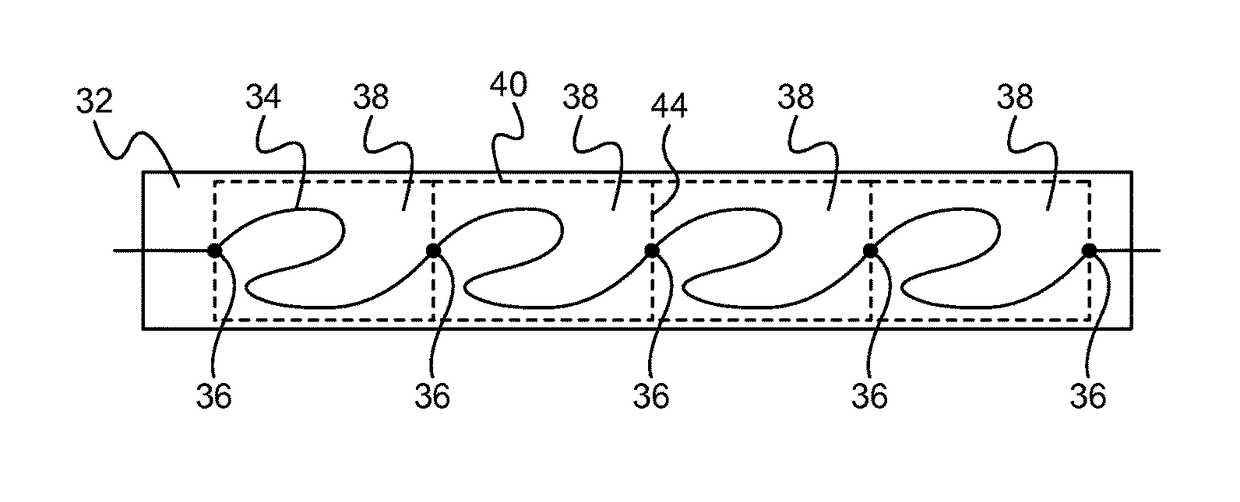

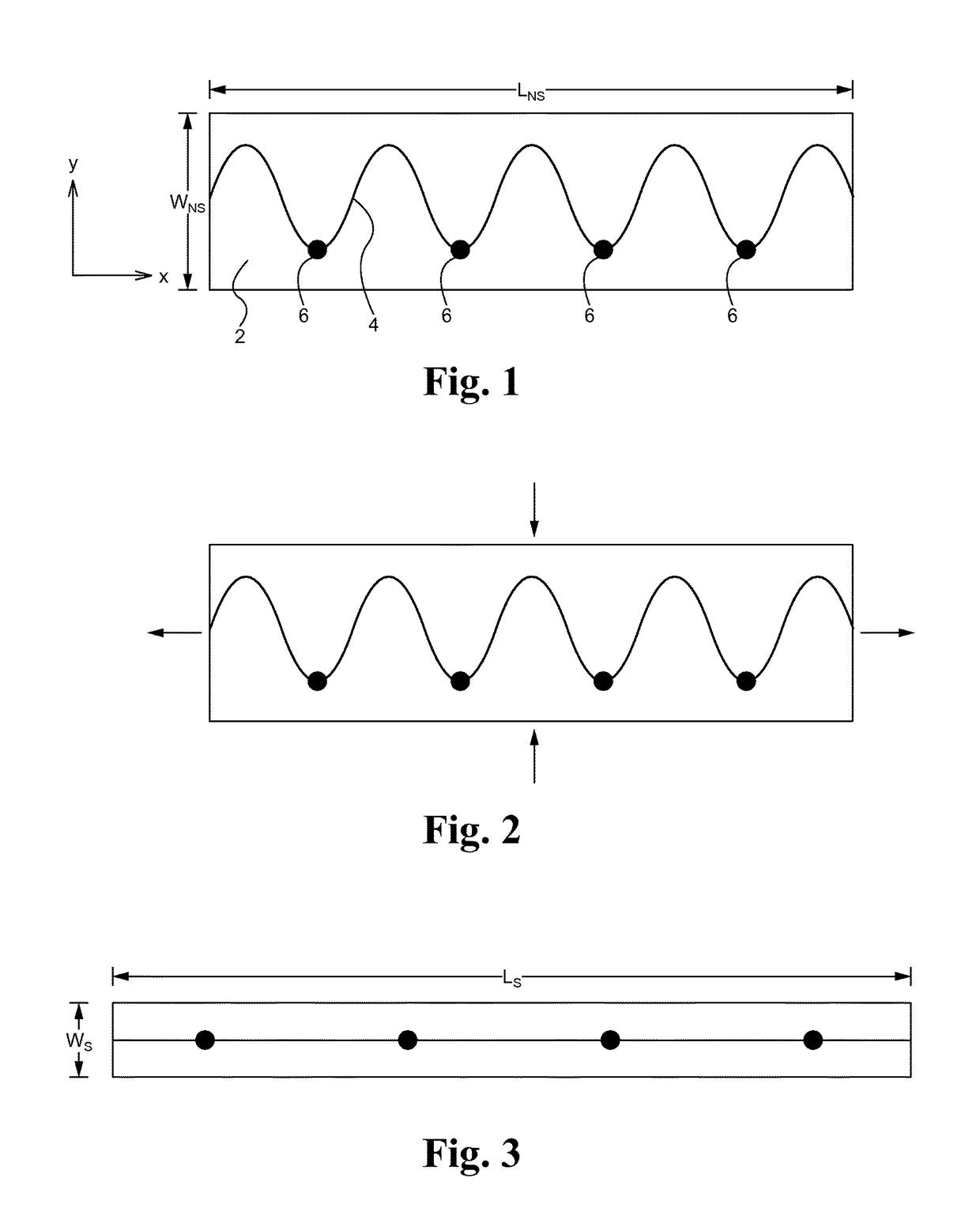

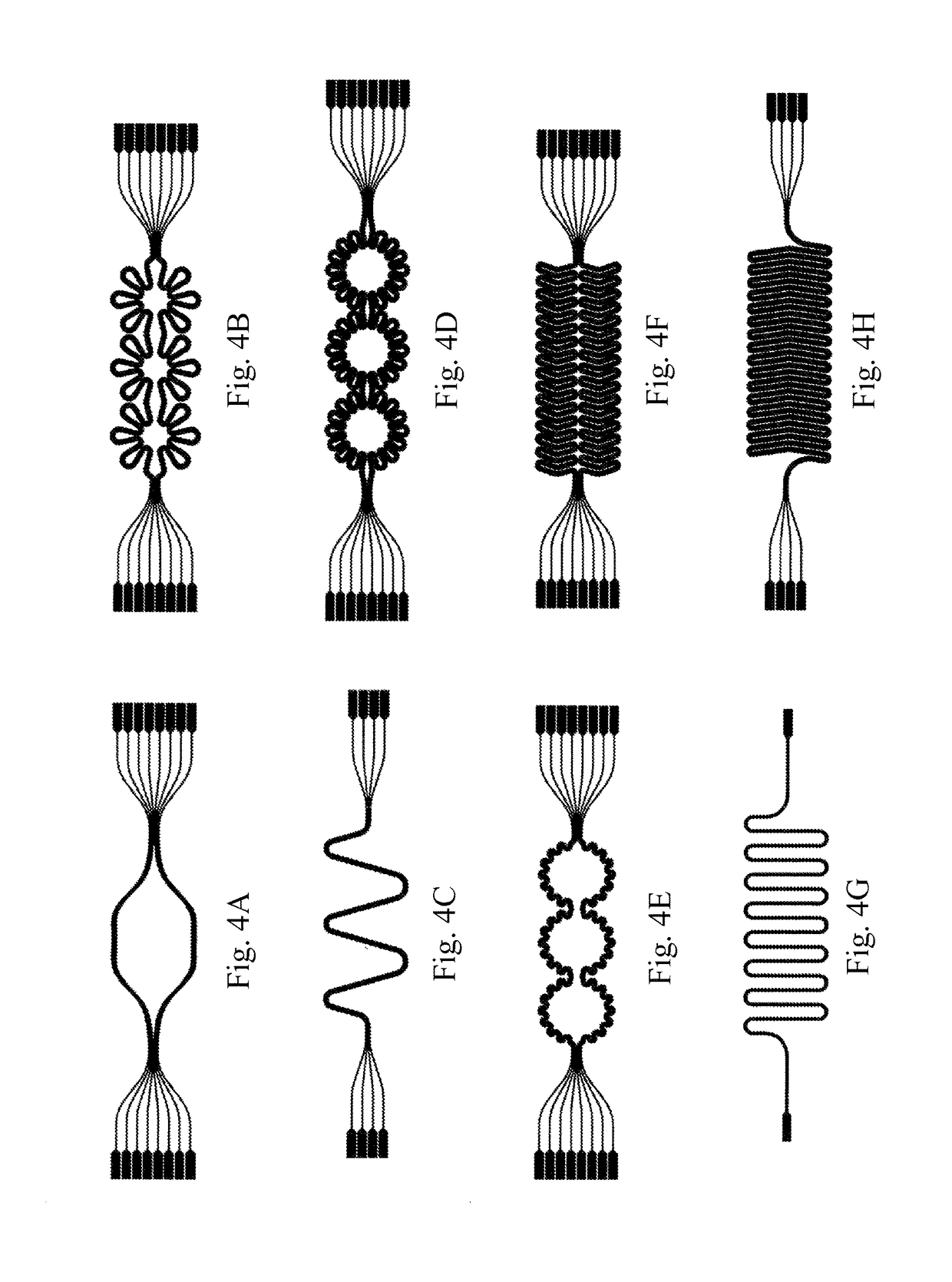

Method of making stretchable interconnect using magnet wires

InactiveUS9674949B1Freedom of movementCircuit bendability/stretchabilityDielectric materialsElastic substrateEngineering

A stretchable wire assembly includes a metal wire coupled between two elastic substrates. The two elastic substrates are selectively coupled together, and the metal wire is attached to one or both elastic substrates at select locations. The form of the metal wire is such that when the elastic substrates are in a relaxed, or non-stretched, state the metal wire forms a tortuous path, such as a waveform, along the coupled elastic substrates. The tortuous path of the metal wire provides slack such that as the elastic substrates are stretched the slack is taken up. Once released, the elastic substrates move from the stretched position to the relaxed, non-stretched position, and slack is reintroduced into the metal wire in the form of the original tortuous path.

Owner:FLEXTRONICS AP LLC

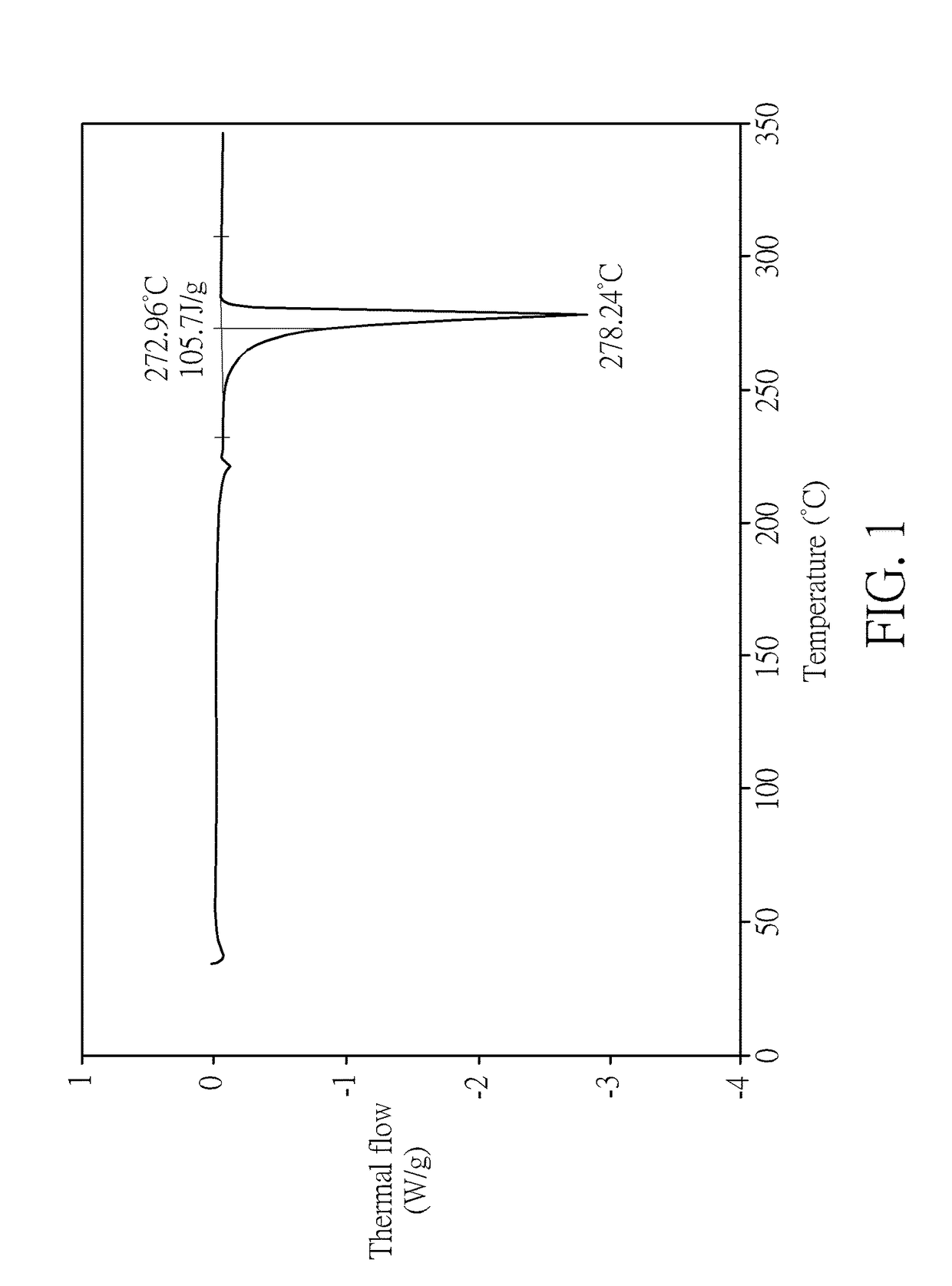

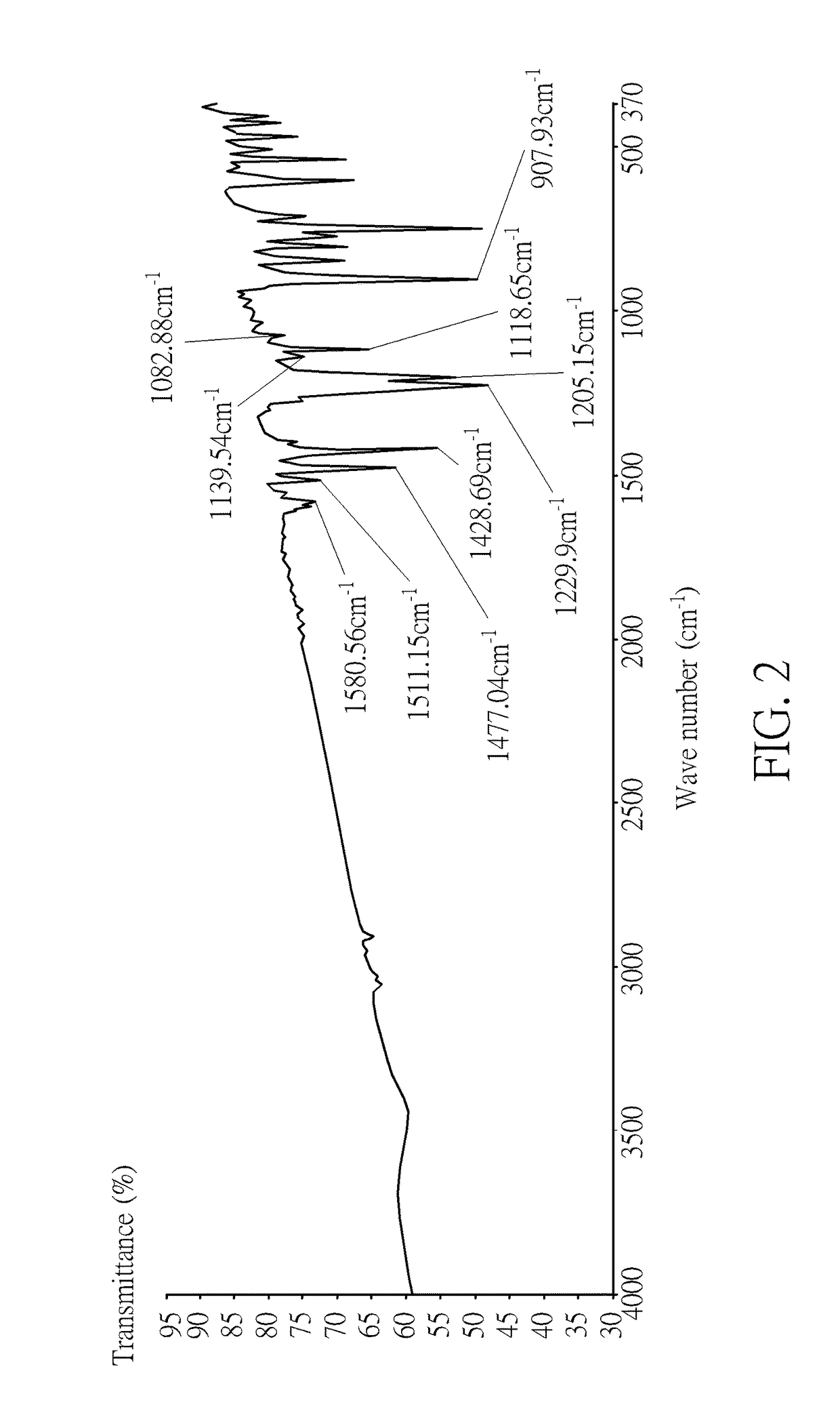

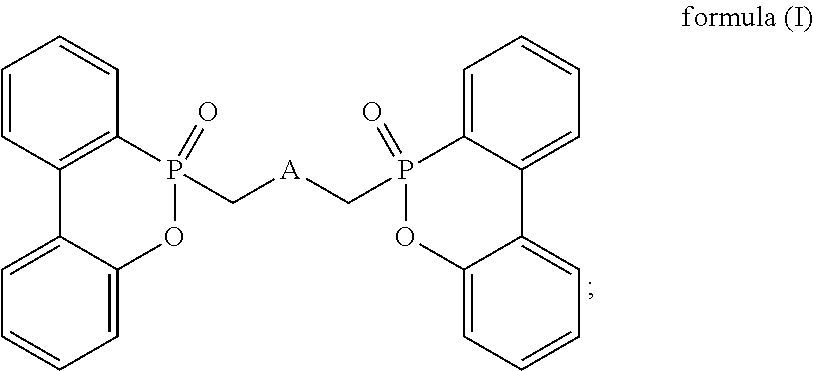

Resin composition

ActiveUS20170166729A1Low thermal expansionImprove heat resistanceFireproof paintsDielectric materialsThermal expansionCopper

The present invention relates to resin composite materials, and more particularly, to low-dielectric resin composition and prepreg, resin film, resin coated copper, laminate and printed circuit board formed therefrom. The low-dielectric resin composition includes a phosphorus-containing flame retardant as shown in formula (I) and a resin with an active unsaturated bond. The low-dielectric resin composition may further be manufactured as a prepreg, a resin film, a resin coated copper, a laminate, or a printed circuit board, having a high glass transition temperature, low dielectric property, halogen-free flame retardancy and low percent of thermal expansion of laminate.

Owner:ELITE ELECTRONICS MATERIAL ZHONGSHAN

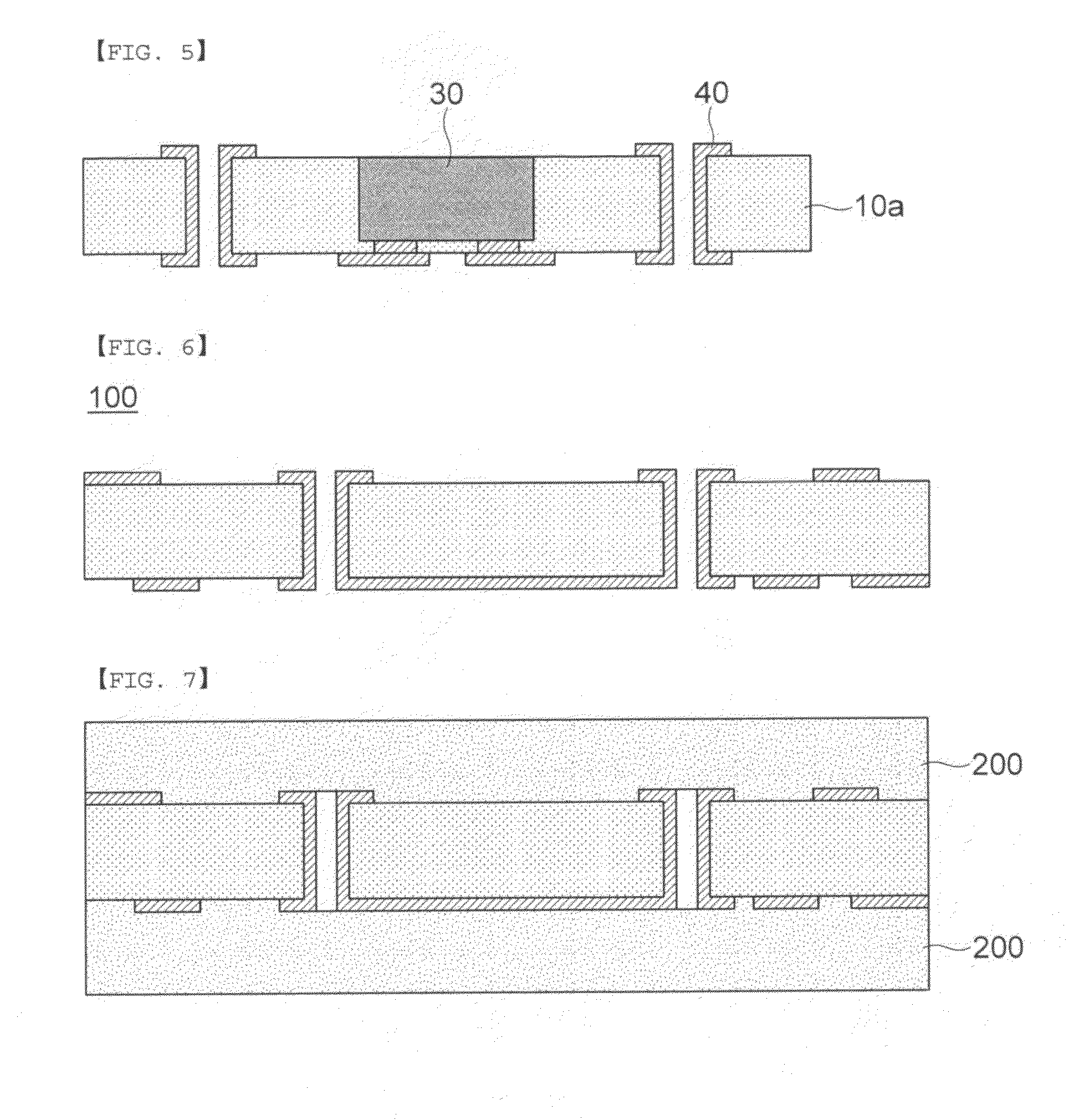

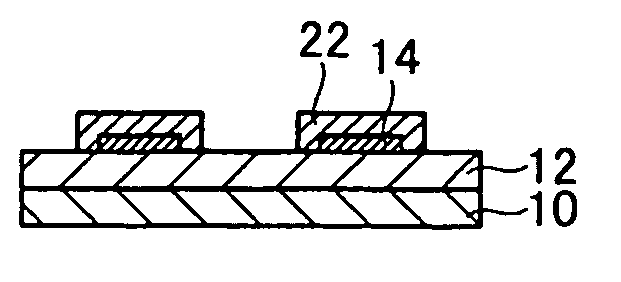

Module substrate and disk apparatus

InactiveUS20060103030A1Dielectric materialsSemiconductor/solid-state device detailsElectrical and Electronics engineeringMagnetic disks

A module substrate includes an insulating substrate, a circuit pattern formed on at least a main surface of the insulating substrate, a protection film formed on the main surface of the insulating substrate including the circuit patter such as to expose a mount region of the circuit pattern, an active element part mounted on the mount region of the circuit pattern, a fluororesin film formed on the protection film at least in a vicinity of the mount region of the active element part, and an underfill filled between the active element part and the mount region of the circuit pattern.

Owner:KK TOSHIBA

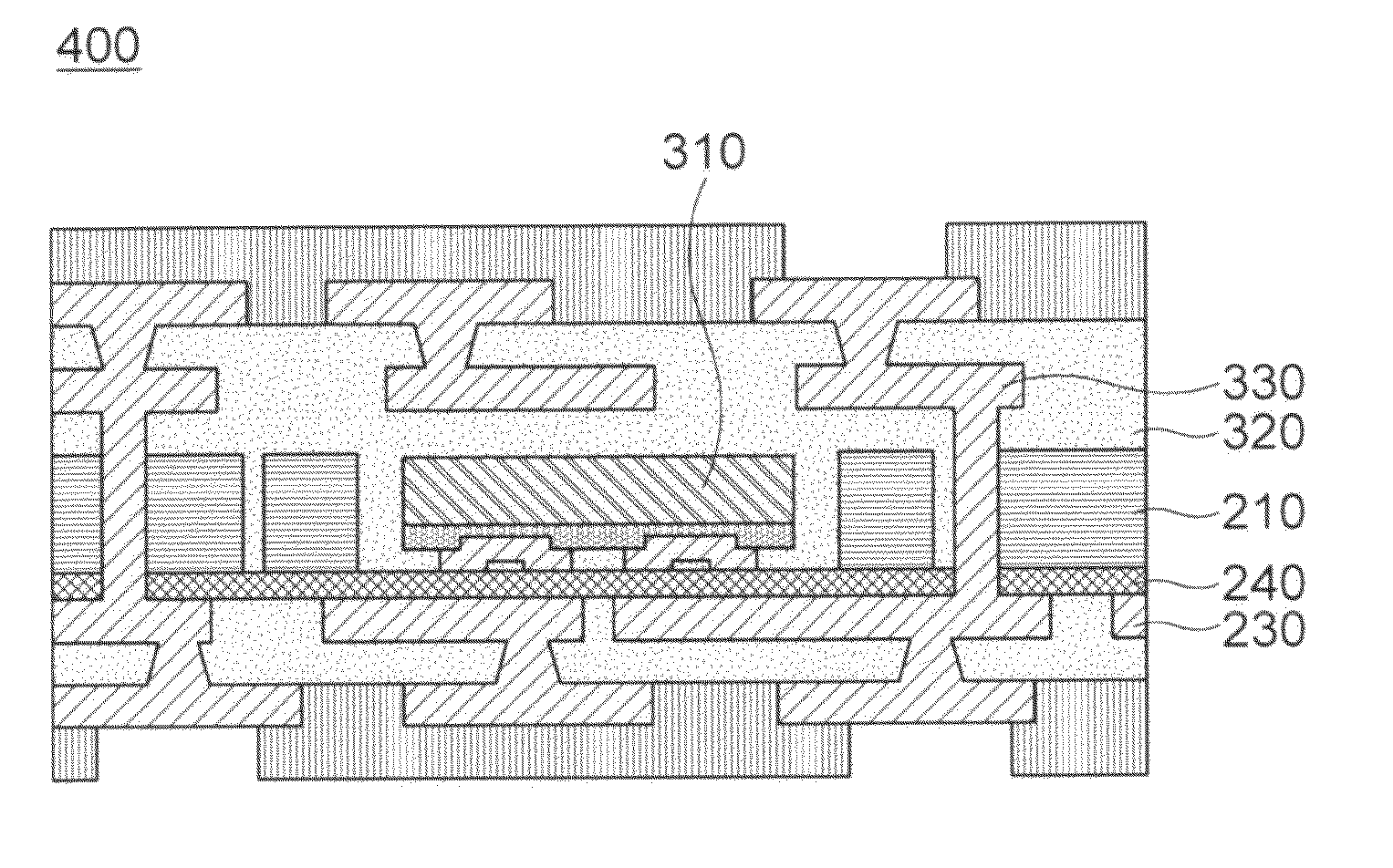

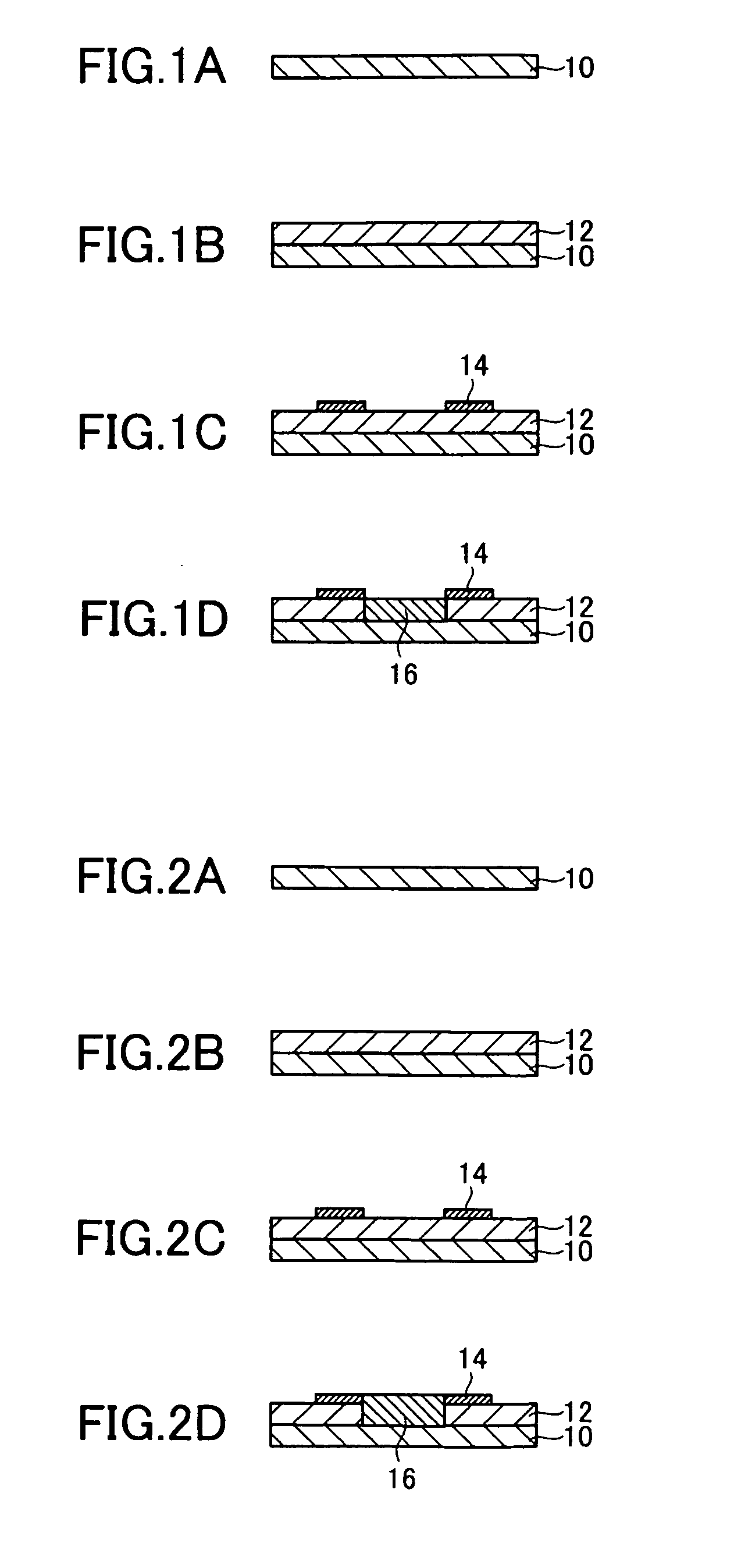

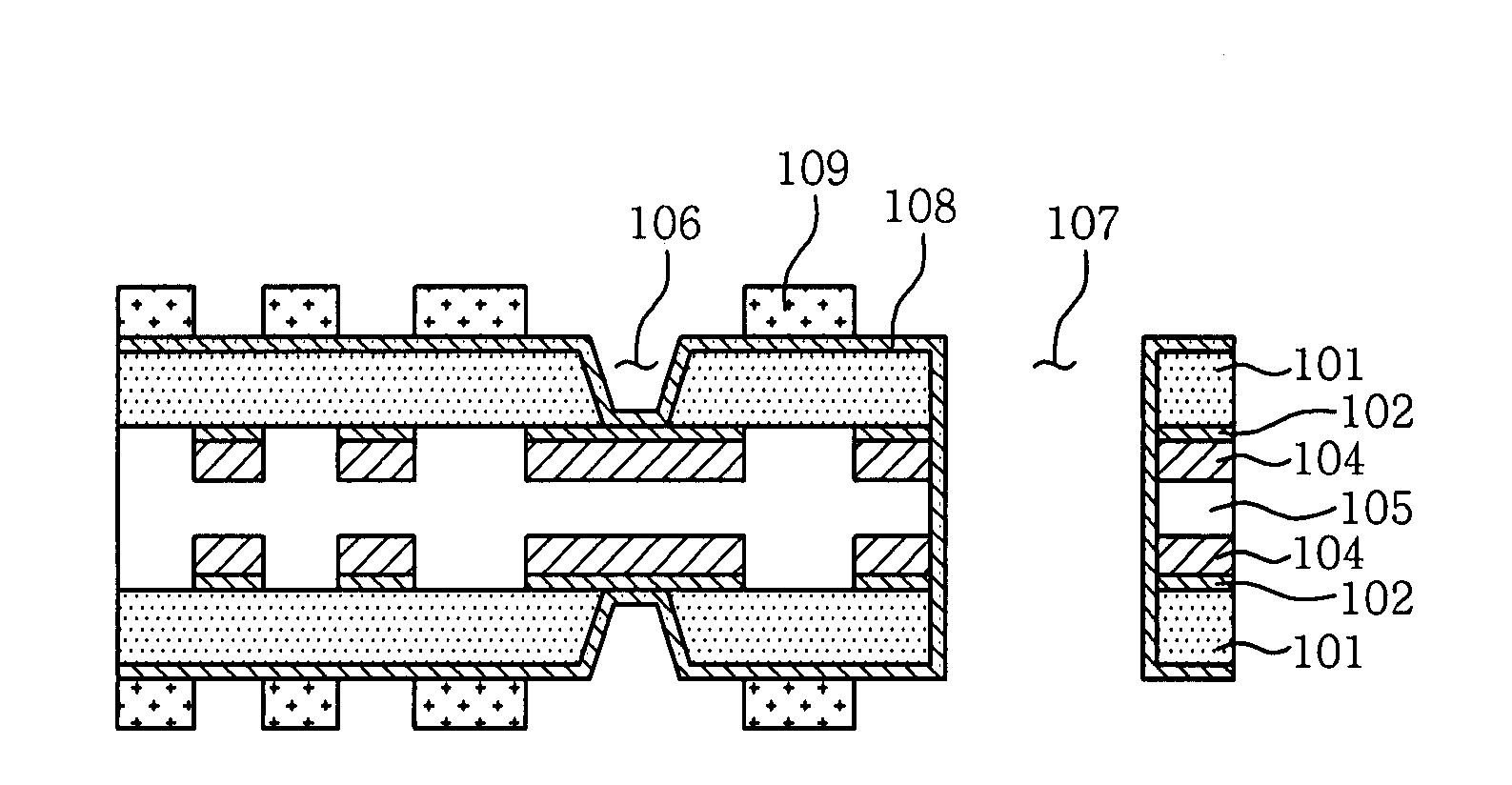

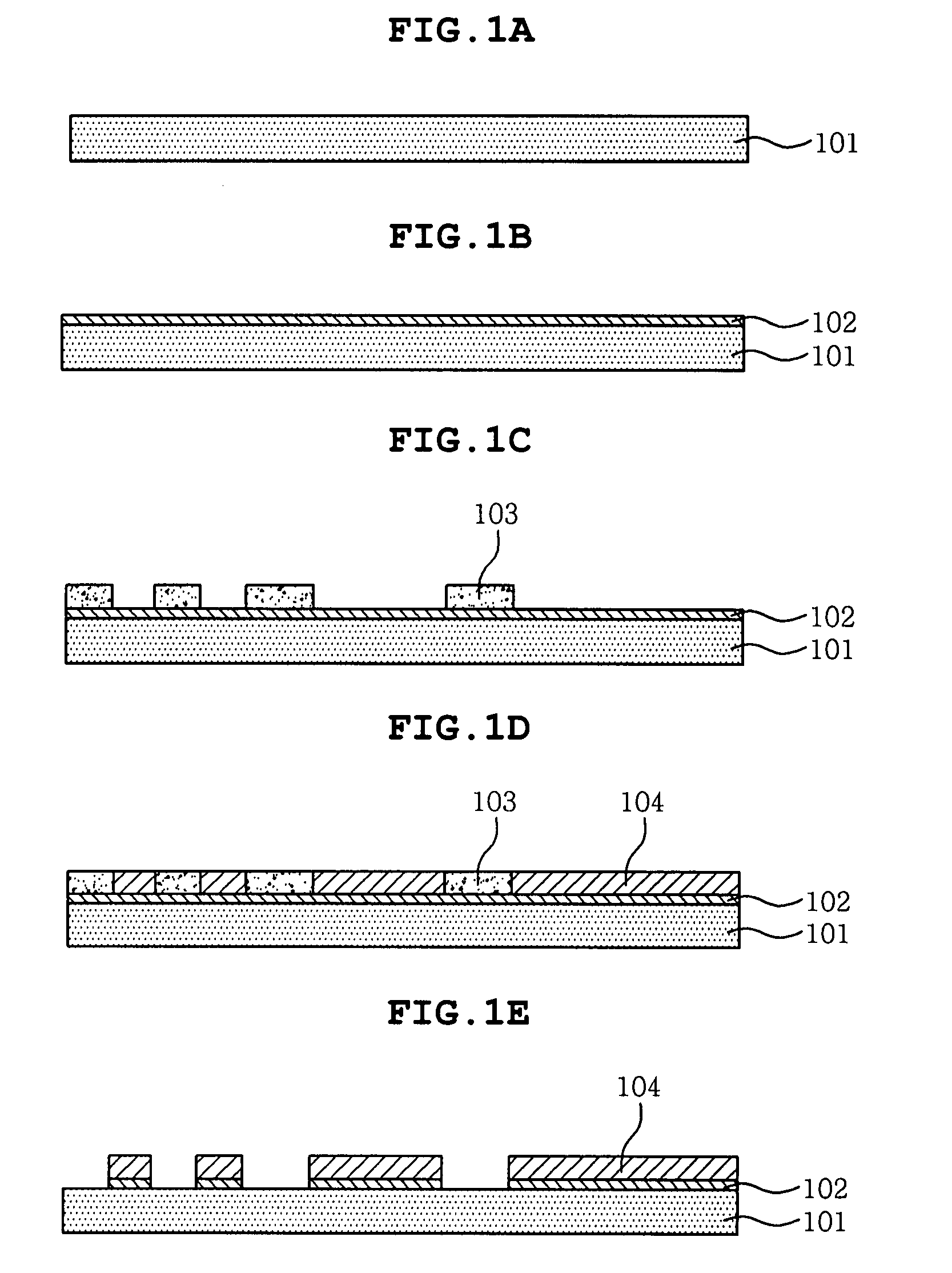

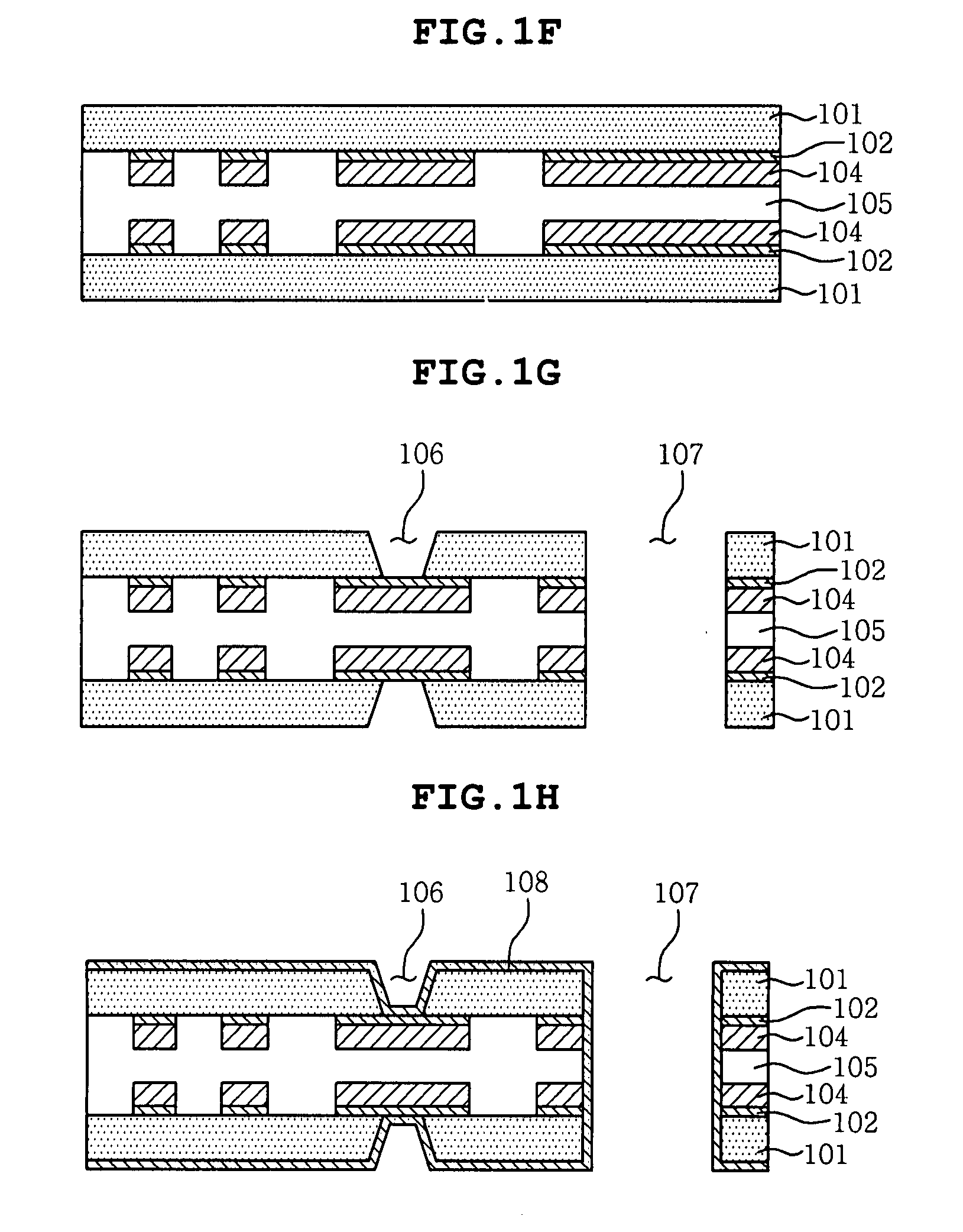

Embedded printed circuit board and method of manufacturing the same

InactiveUS20110290540A1Printed circuit assemblingLamination ancillary operationsDegrees of freedomEngineering

Disclosed herein are an embedded printed circuit board and a method of manufacturing the same. The embedded printed circuit board includes: an insulating layer on which a cavity is formed; a chip mounted on the cavity; and a circuit layer formed on the insulating layer, wherein the insulating layer is made of photosensitive compositions including photosensitive monomer and photoinitiator. As a result, the cavity can be formed by selectively using only the insulating layer, thereby making it possible to secure a degree of freedom in the design of the embedded printed circuit board.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

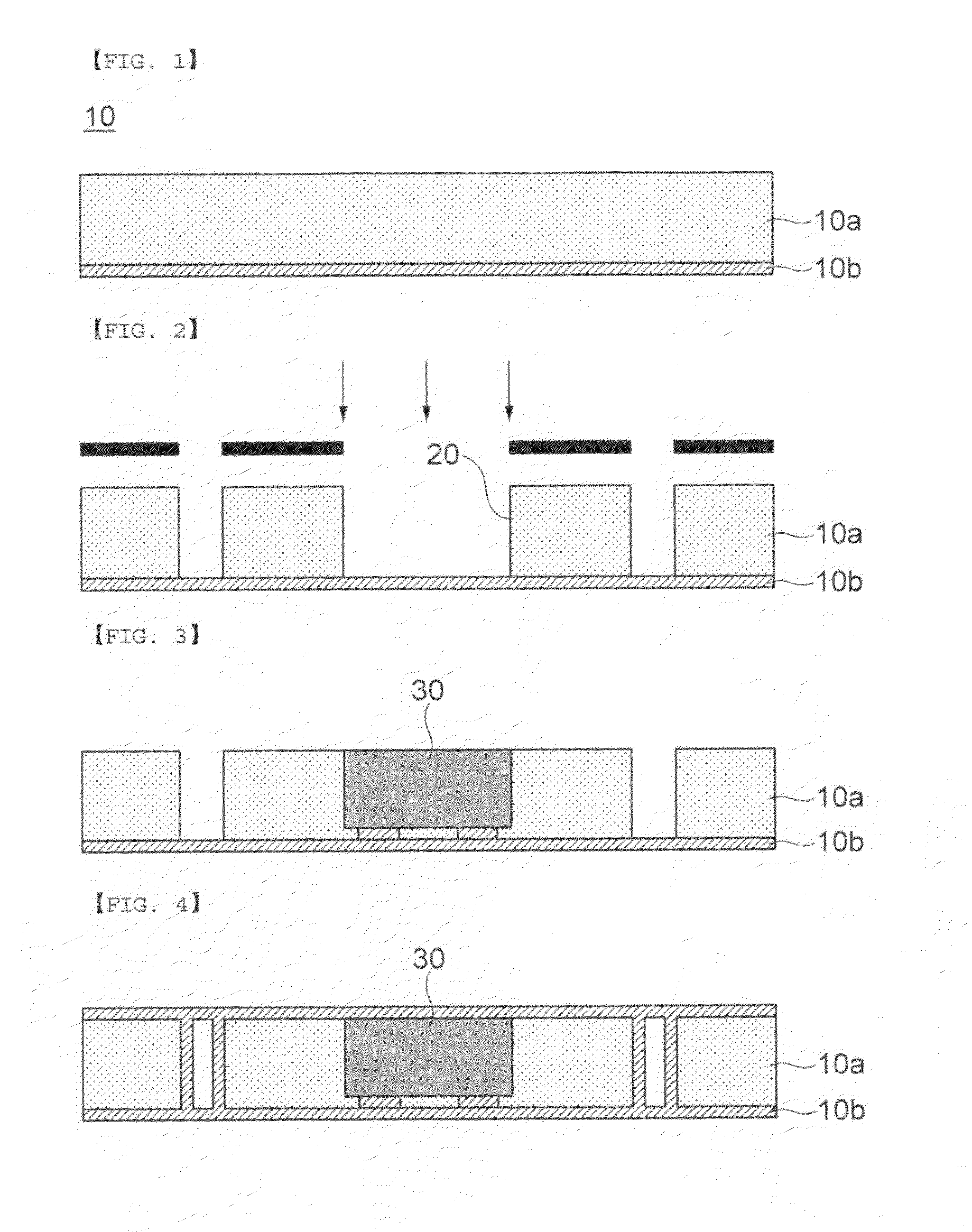

Method of forming wiring board and wiring board obtained

ActiveUS20100078208A1Improve reliabilityInhibit migrationPorous dielectricsDielectric materialsEngineeringMetal

A method of forming a wiring board comprises: a step of forming a receptive layer having a porous structure on a substrate; a step of forming wiring portions in a desired conductive pattern on a surface of the receptive layer by ejecting a colloidal metal solution for drawing by an ink-jet system based on image date of the conductive pattern; and a step of performing a migration-proof treatment on at least part of the receptive layer exposed between mutually adjacent wiring portions.

Owner:FUJIFILM CORP

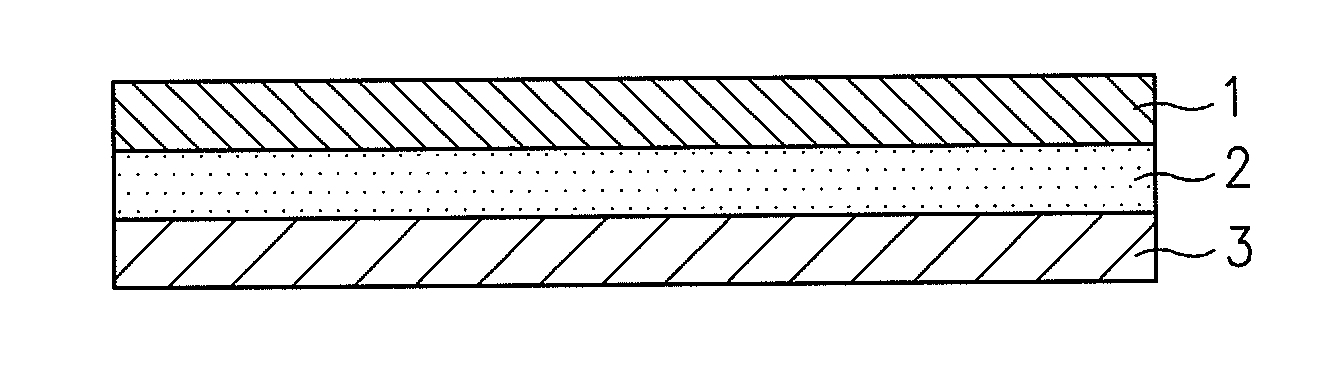

Printed circuit board and method of manufacturing the same

InactiveUS20080053688A1Function increaseHighly reliable fine circuitsDielectric materialsHigh frequency circuit adaptationsGas phaseIon beam

Disclosed herein are a thin printed circuit board, in which a pair of high-functional resin substrates having a permittivity ranging from 1.5 to 4.0, on one surface of each of which a circuit pattern is formed through ion-beam surface treatment, vapor deposition and electroplating, are layered with an insulating layer interposed therebetween, and a method of manufacturing the printed circuit board. The circuit patterns are positioned inside the substrates. Thereafter, external layers are formed through ion-beam surface treatment, vapor deposition and electroplating. According to the present invention, the adhesiveness between each of the substrates and a metal layer may be improved through the ion-beam surface treatment / vapor deposition. Furthermore, since the pair of resin substrates are layered with the insulating layer interposed therebetween, the circuit patterns may be disposed inside the pair of resin substrates, so that the total thickness of the substrate may be reduced, thereby realizing highly reliable fine circuits.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

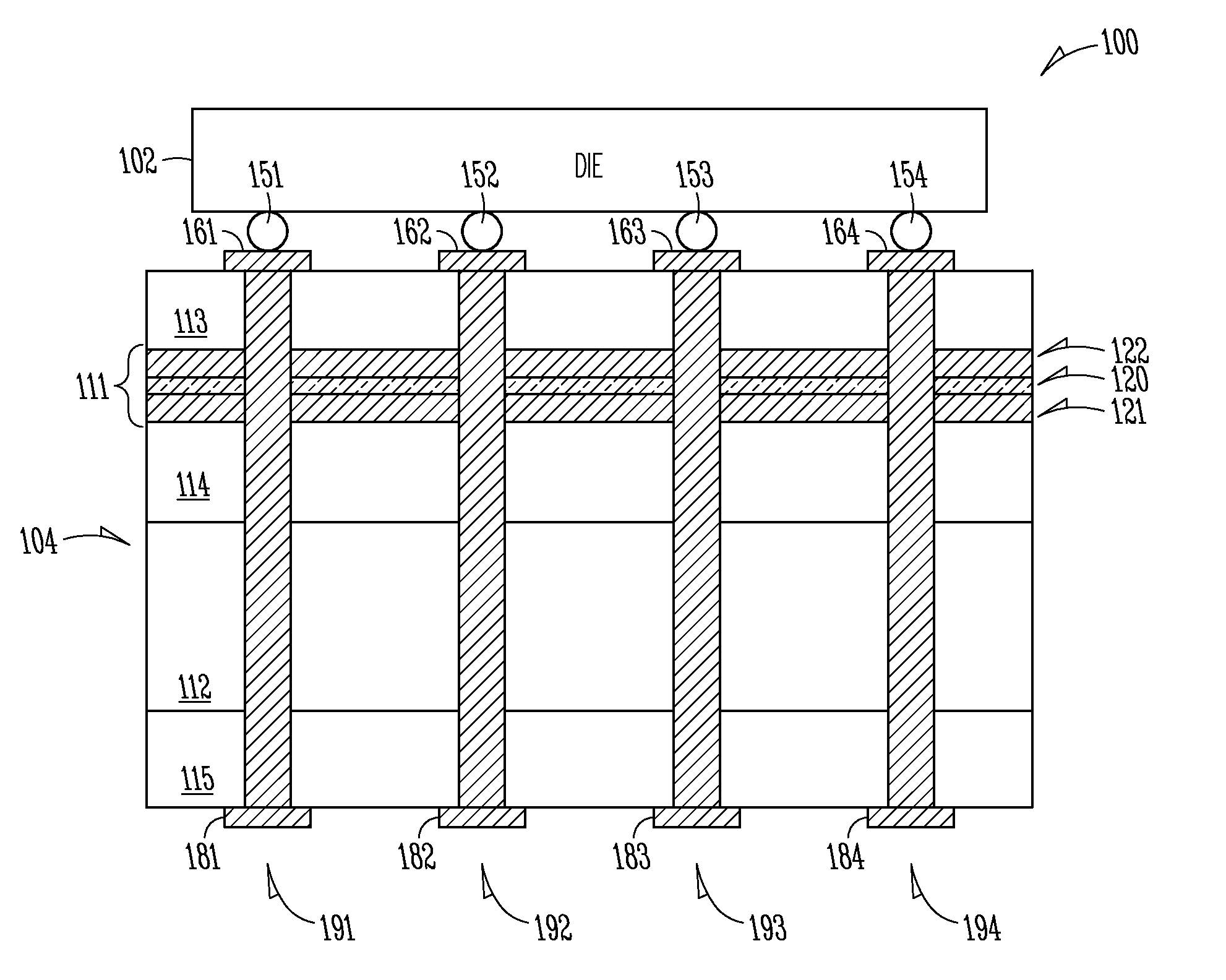

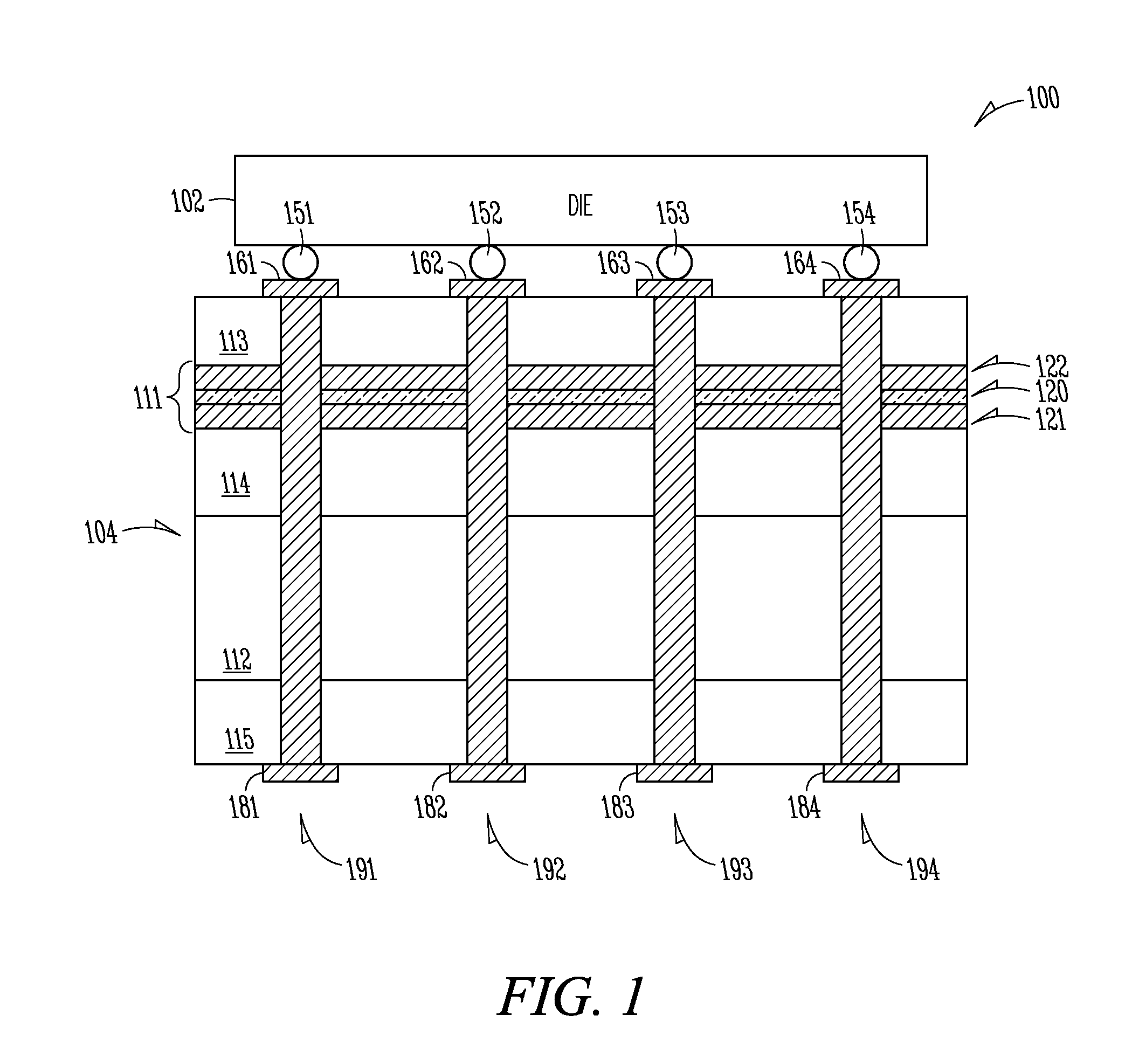

Polymer-based integrated thin film capacitors, packages containing same and methods related thereto

Some embodiments include thin film capacitors (TFC) formed on a package substrate of an integrated circuit package. The TFC include a polymer-based dielectric layer deposited directly on the package substrate. At least one of the TFC includes a first electrode layer, a second electrode layer, with the polymer-based dielectric layer located between the first and second electrode layers. Each of the first and second electrode layers is also formed individually and directly on the package substrate. Other embodiments are described and claimed.

Owner:INTEL CORP

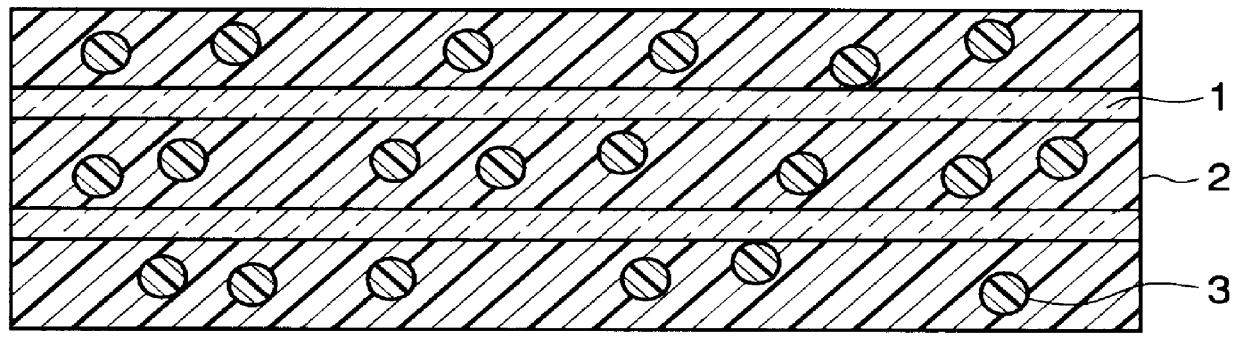

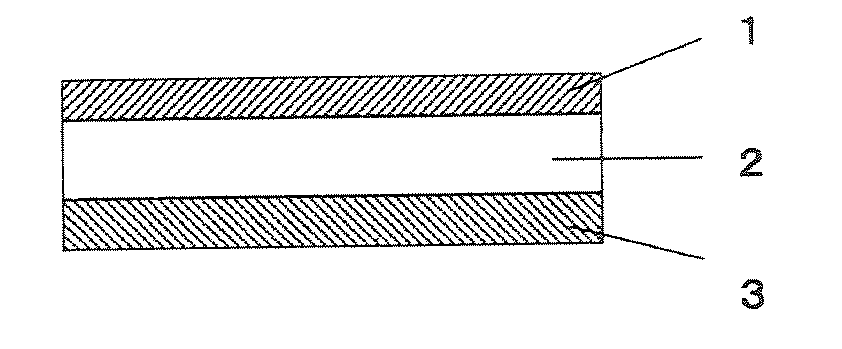

Laminate for flexible printed wiring board

ActiveUS20080107866A1Improve adhesionImprove bending resistanceDielectric materialsSynthetic resin layered productsSignal responsePolymer science

To provide a laminate for a flexible printed wiring board excellent in signal response in the high frequency region. A laminate for a flexible printed wiring board having a three-layer laminated structure where a reinforcing layer (A), an electrical insulator layer (B) and an electrical conductor layer (C) are laminated in this order, wherein the electrical insulator layer (B) is made of a fluorocopolymer comprising repeating units (a) based on tetrafluoroethylene and / or chlorotrifluoroethylene, repeating units (b) based on a fluoromonomer excluding tetrafluoroethylene and chlorotrifluoroethylene, and repeating units (c) based on a monomer having an acid anhydride residue and the electrical conductor layer (C) has a surface roughness of at most 10 μm on the side being in contact with the electrical insulator layer (B). The laminate for a flexible printed wiring board is excellent in signal response in the high frequency region and excellent in flex resistance.

Owner:ASAHI GLASS CO LTD

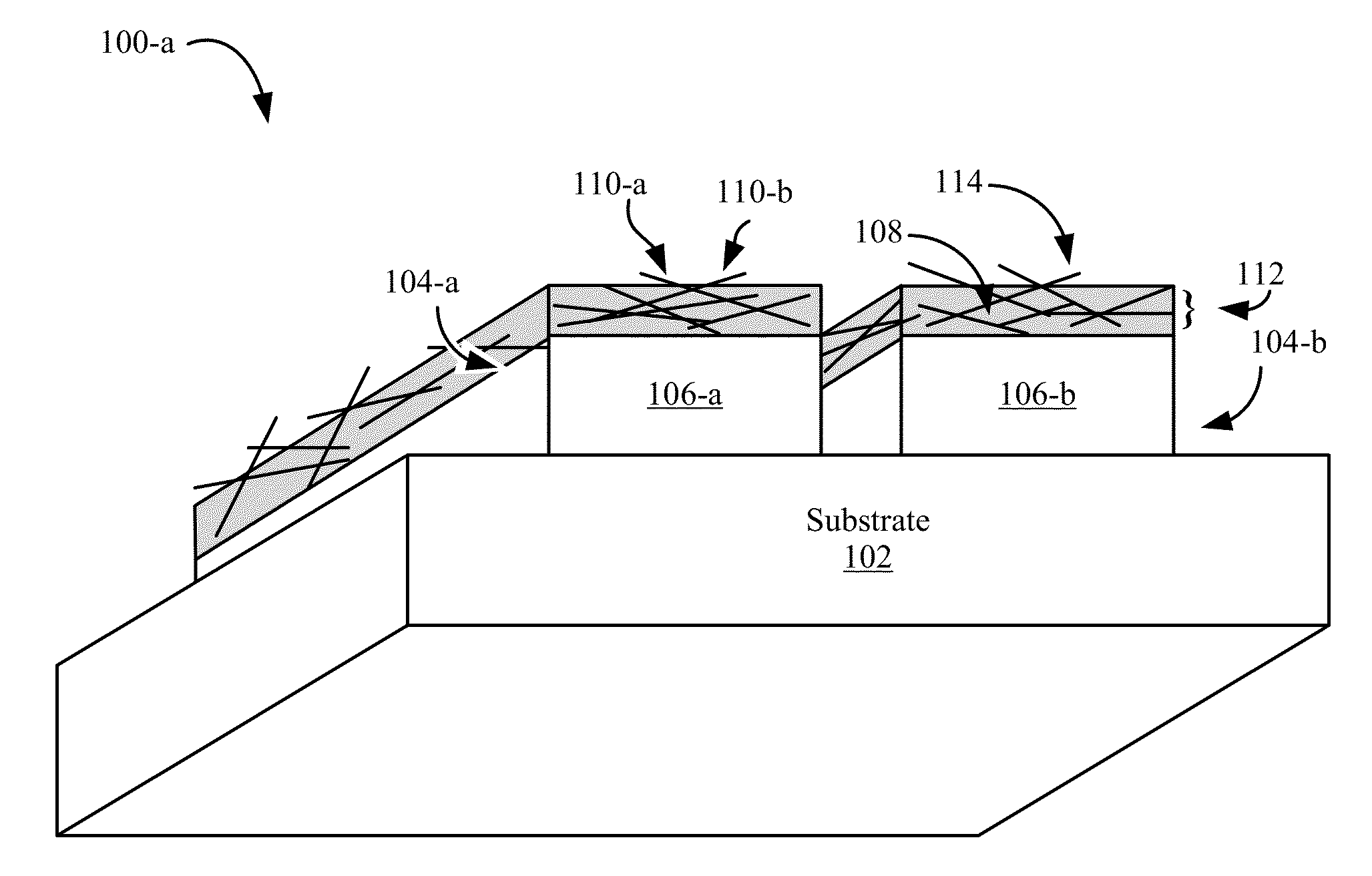

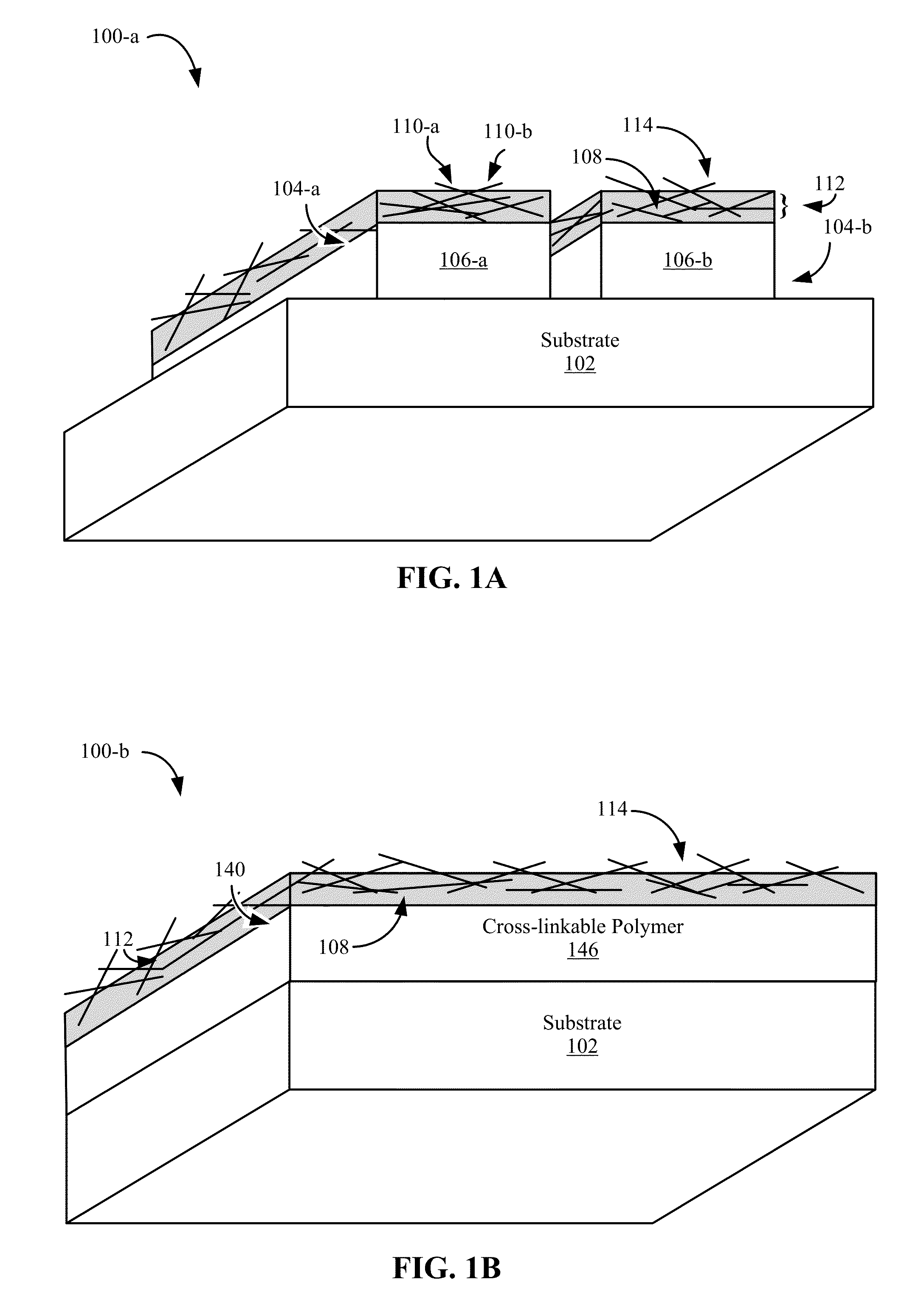

Composite Conductive Films with Enhanced Thermal Stability

ActiveUS20150038033A1Enhanced hardness propertyImprove temperature stabilityNanoinformaticsApparatus for heat treatmentCross-linkNanowire

A composite conductive film is provided that includes a layer of cross-linked polymer having a surface and an inorganic mesh comprising a plurality of nanowires of an inorganic material. The nanowires are, in isolated form, characterized by a first conductivity stability temperature. Further, the plurality of nanowires is embedded within at least a region of the layer of cross-linked polymer, where the region is continuous from the surface of the layer of cross-linked polymer. The layer of cross-linked polymer and the inorganic mesh are arranged to form the composite conductive film having a second conductivity stability temperature that is greater than the first conductivity stability temperature.

Owner:SINOVIA TECH