Patents

Literature

34results about How to "Reduce hardware resource consumption" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

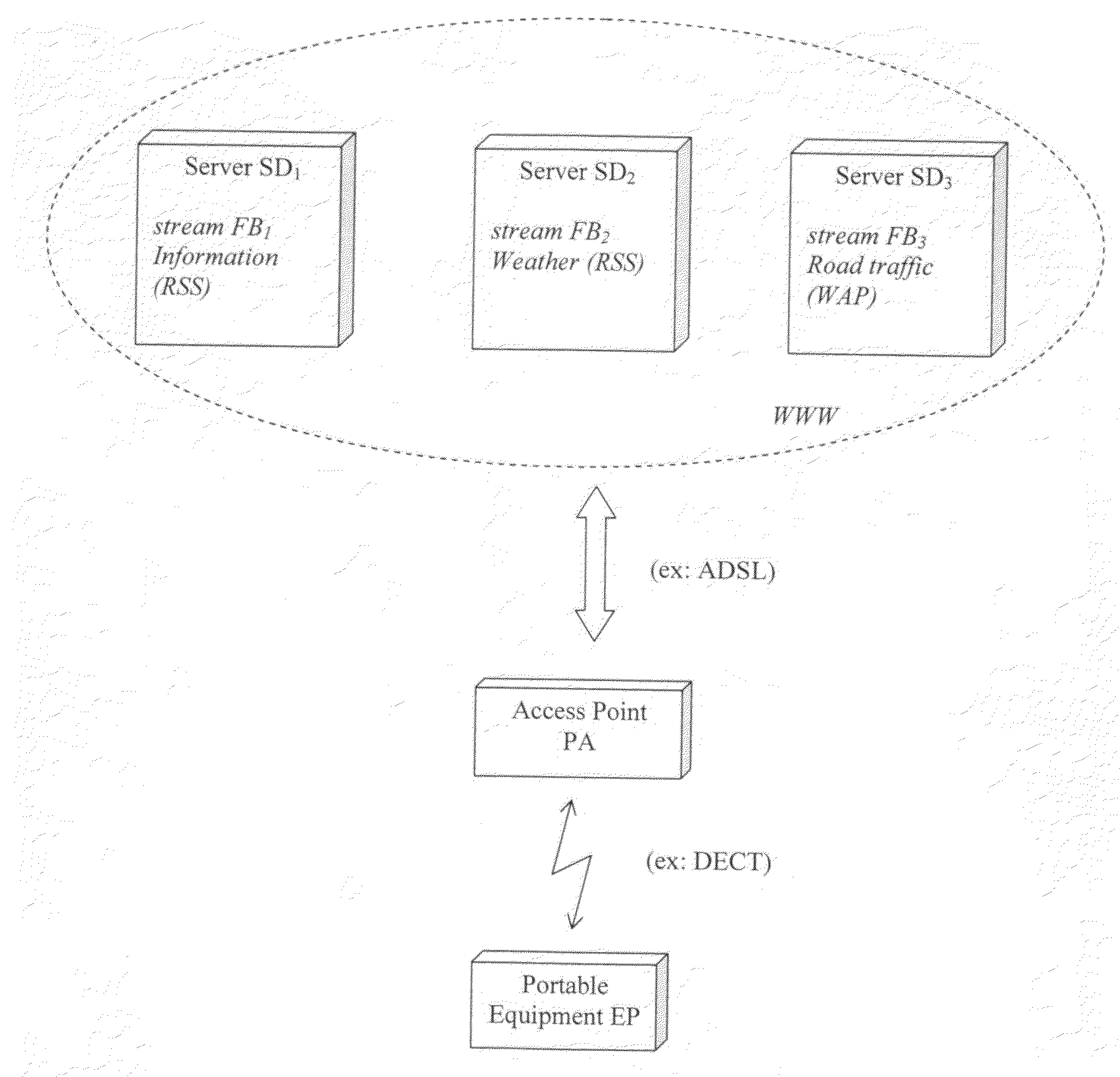

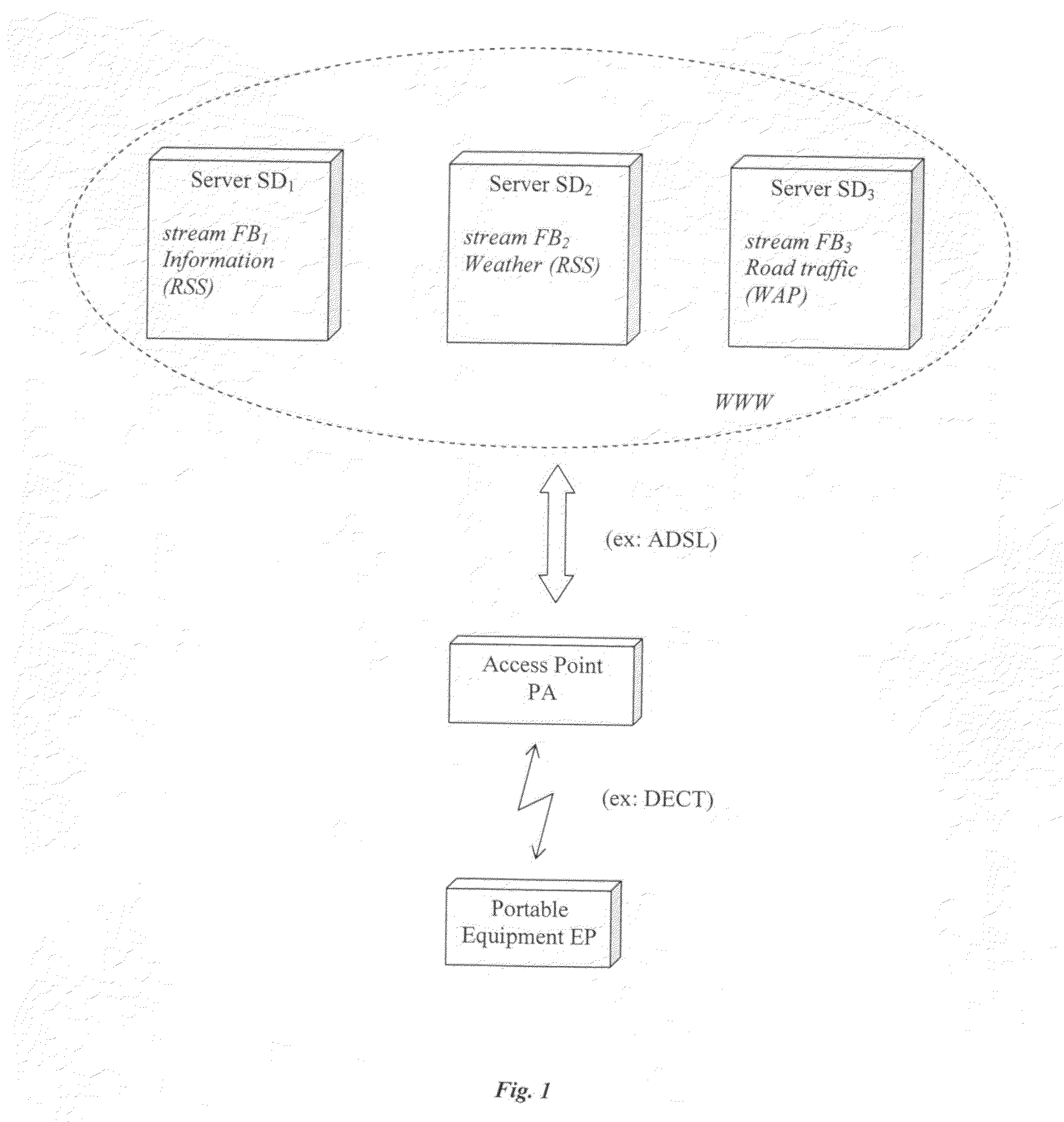

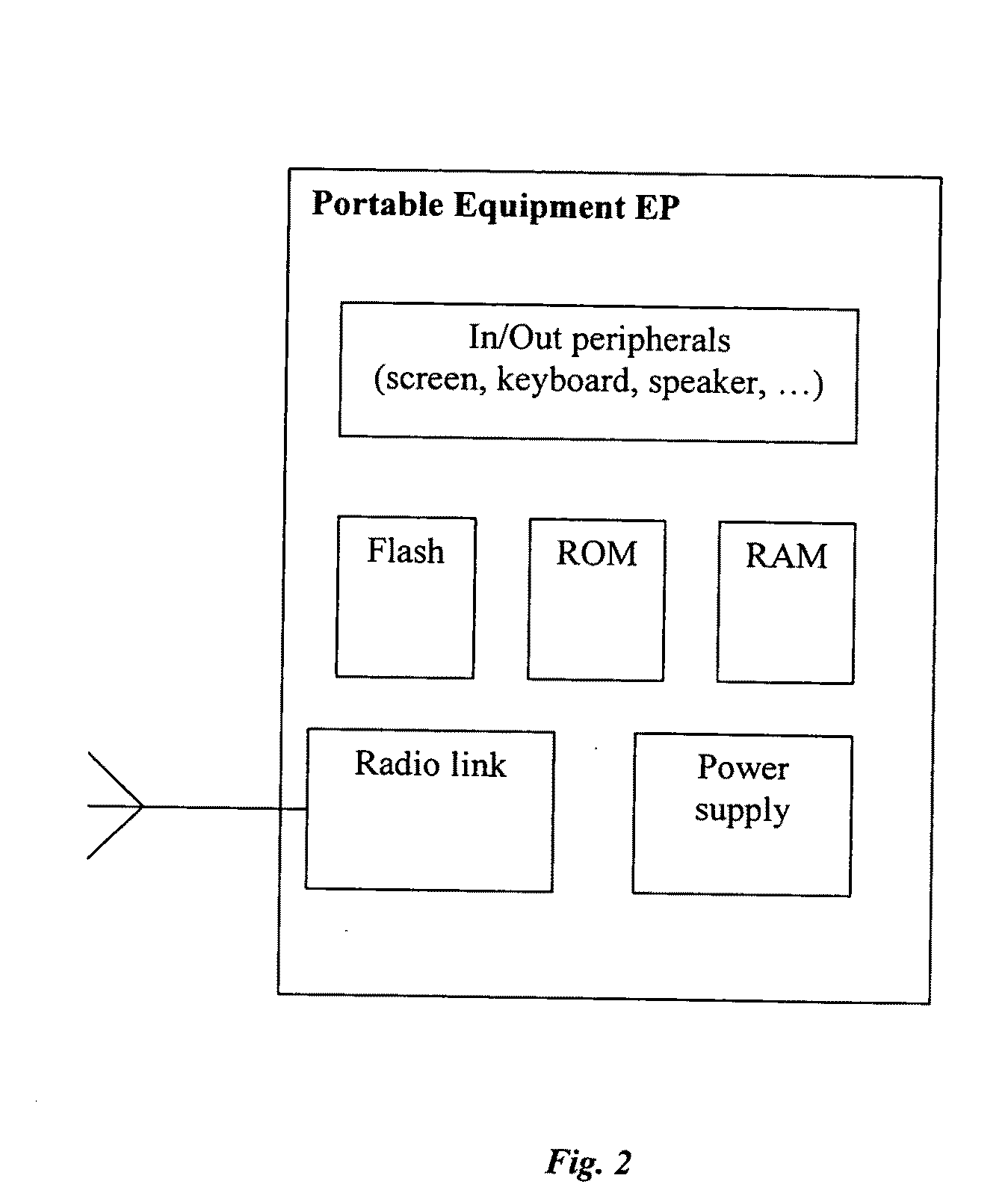

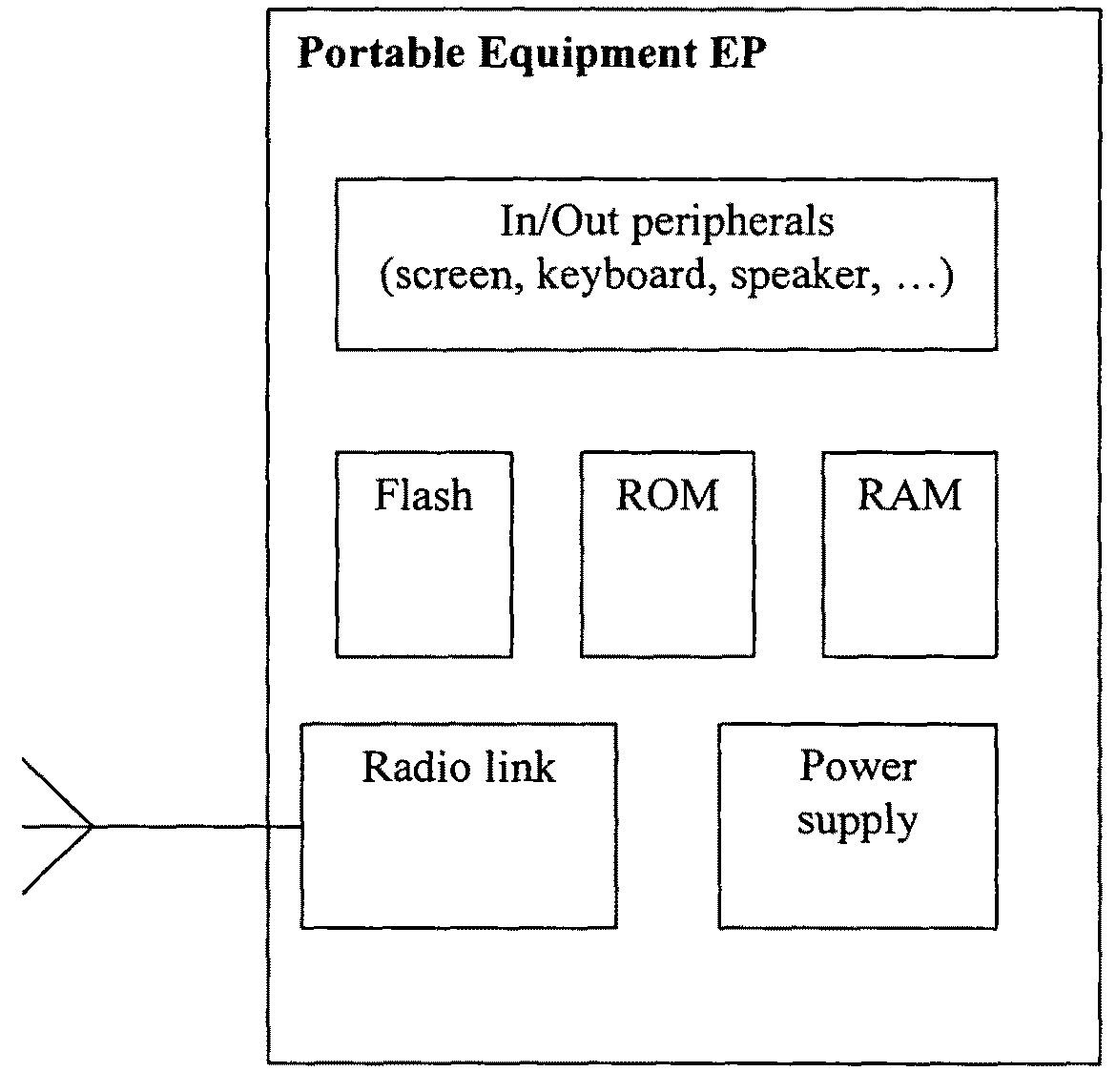

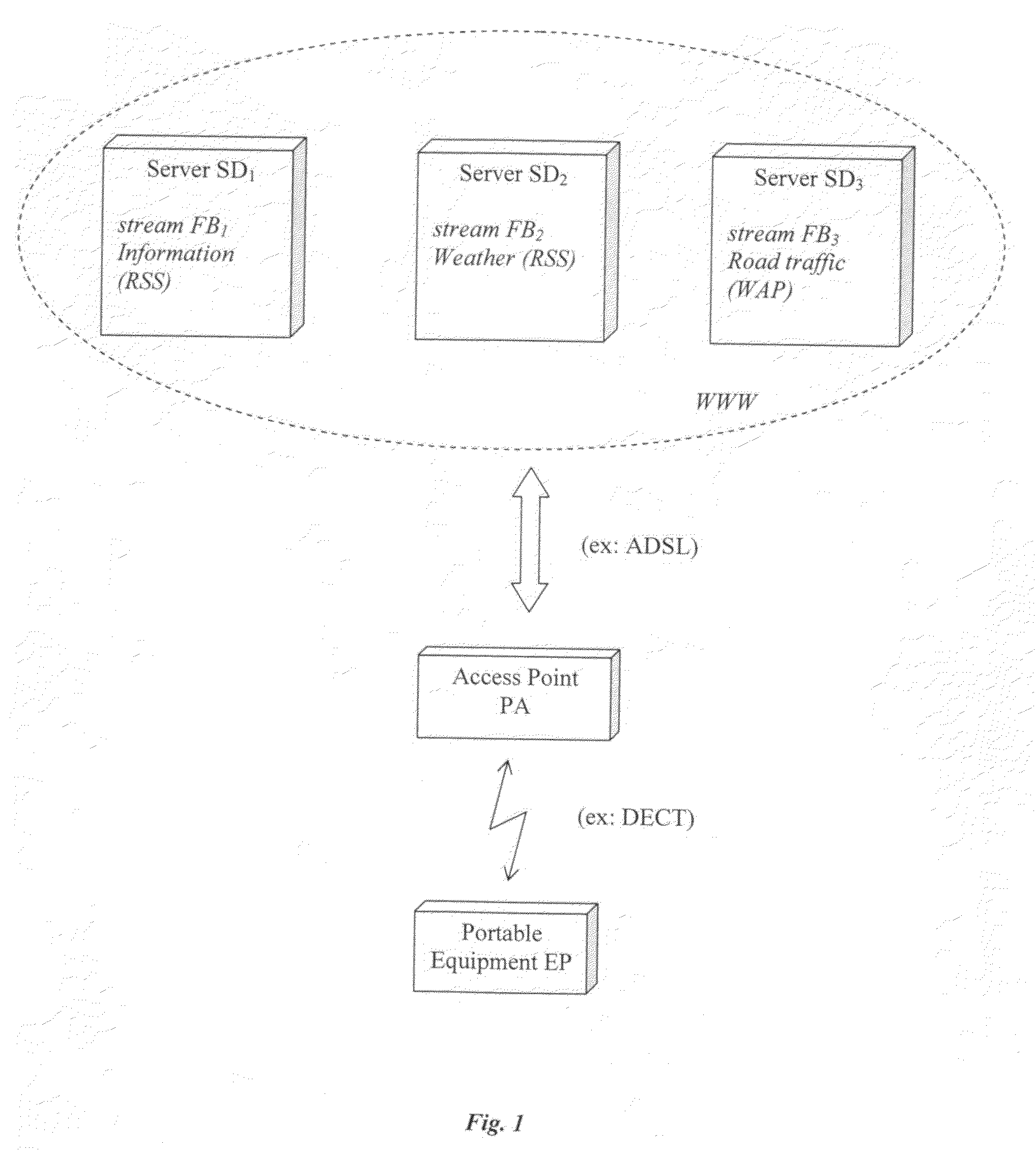

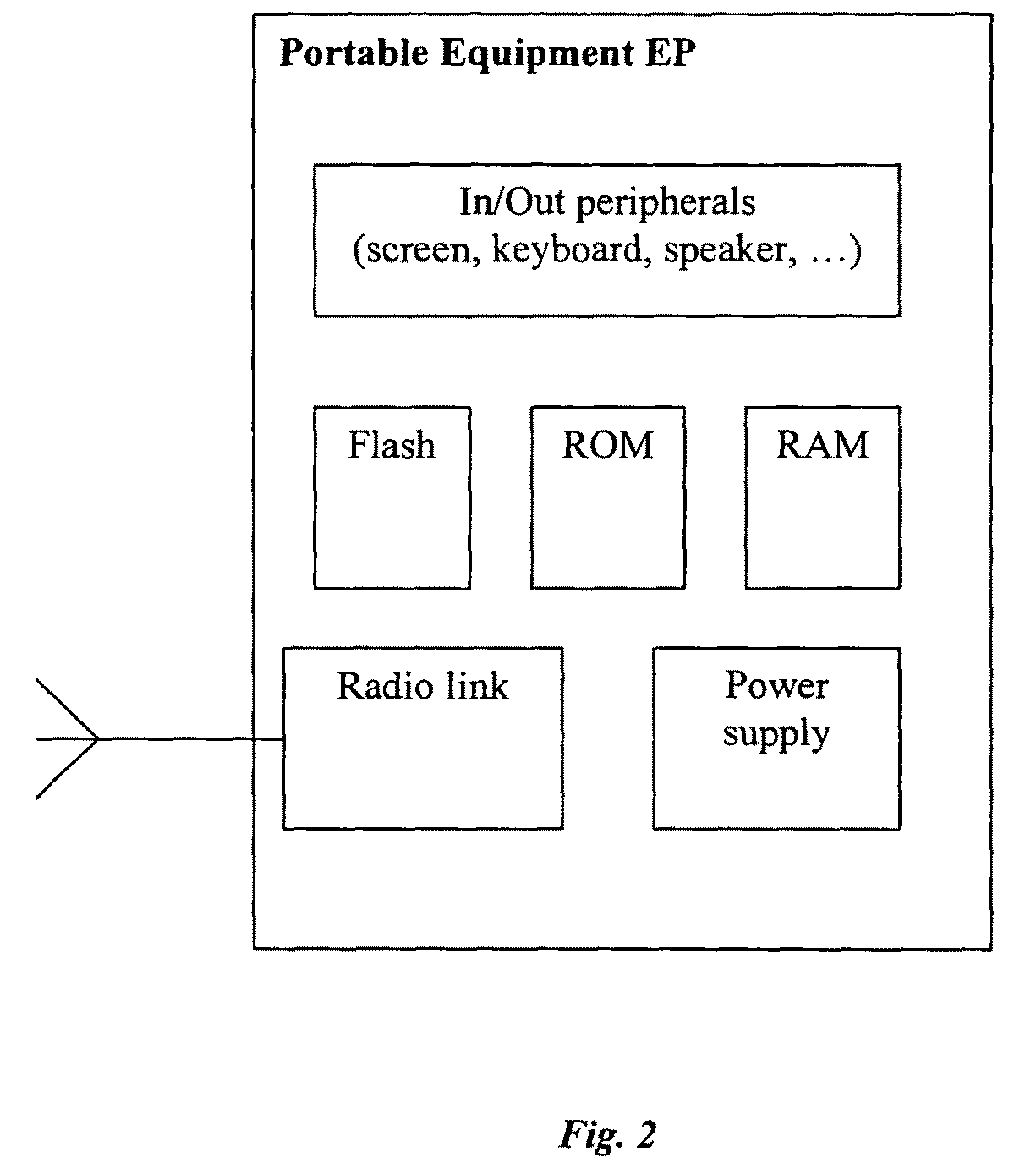

Communication Device and Base for an Advanced Display

ActiveUS20090221326A1Improve user friendlinessMinimize constraintDigital data information retrievalNetwork traffic/resource managementData streamTime segment

The present invention relates to a portable communication device equipped with a screen and a random access memory comprising:means for receiving a data stream through a radio link;means for automatically displaying information from the data stream on said display screen, without any user's request, a part of this information being stored in random access memory during a period of time that is longer than the duration of display;means for displaying information from the data stream on said display screen, upon user's request, this information being stored in random access memory during the duration of display only. The present invention also relates to a base able to communicate with a portable communication device.

Owner:INTERDIGITAL CE PATENT HLDG

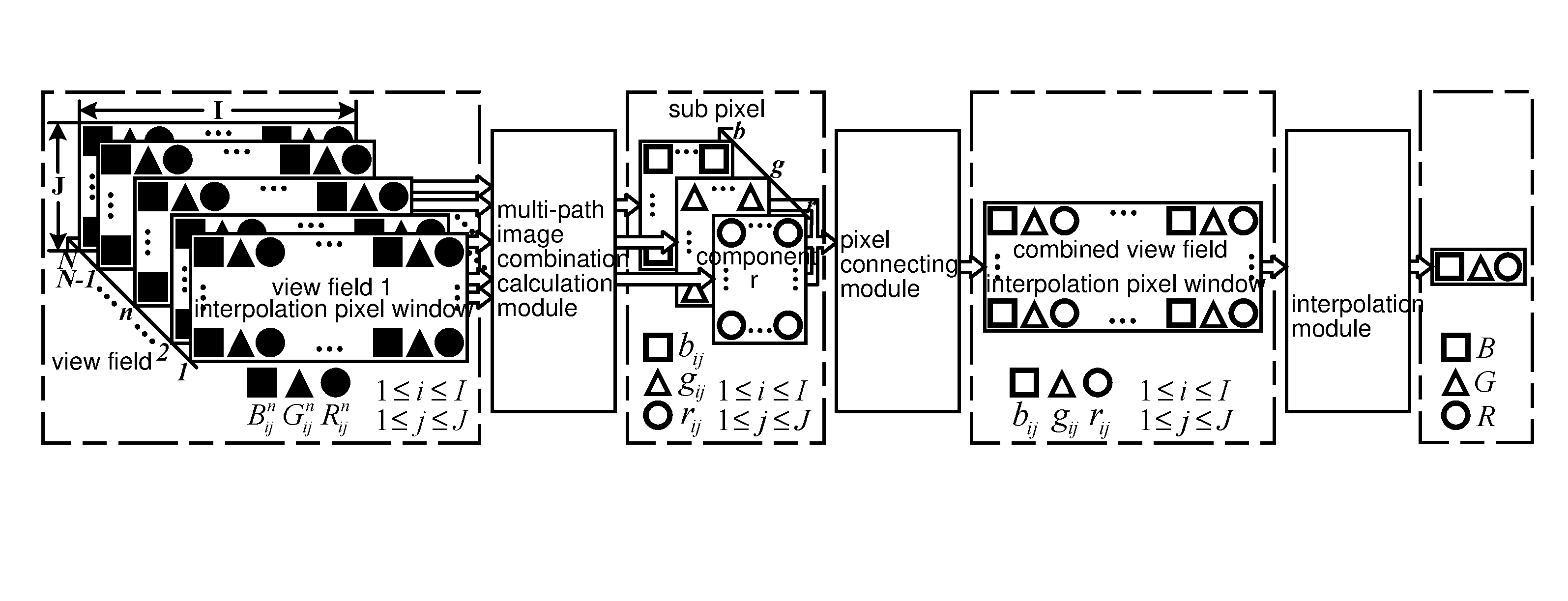

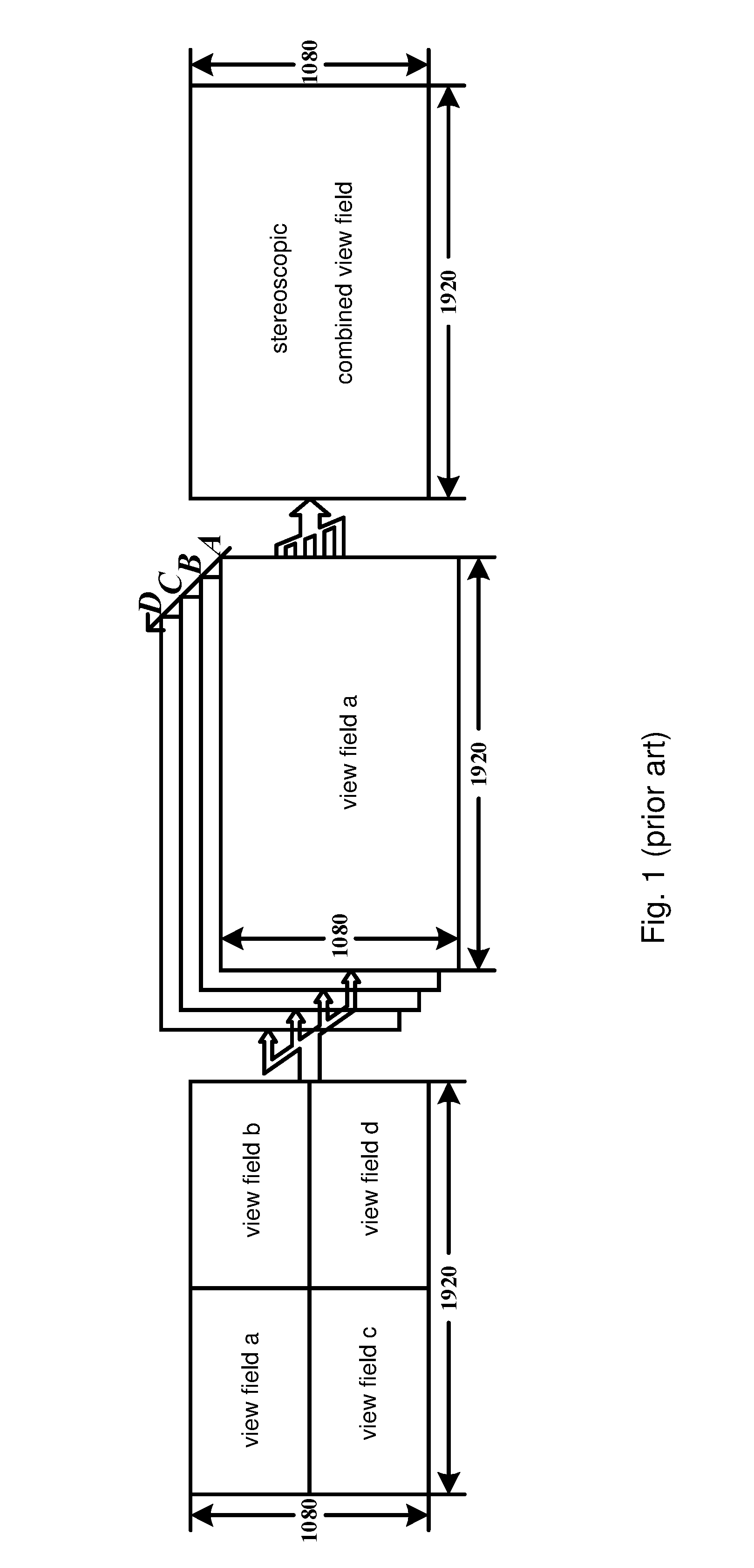

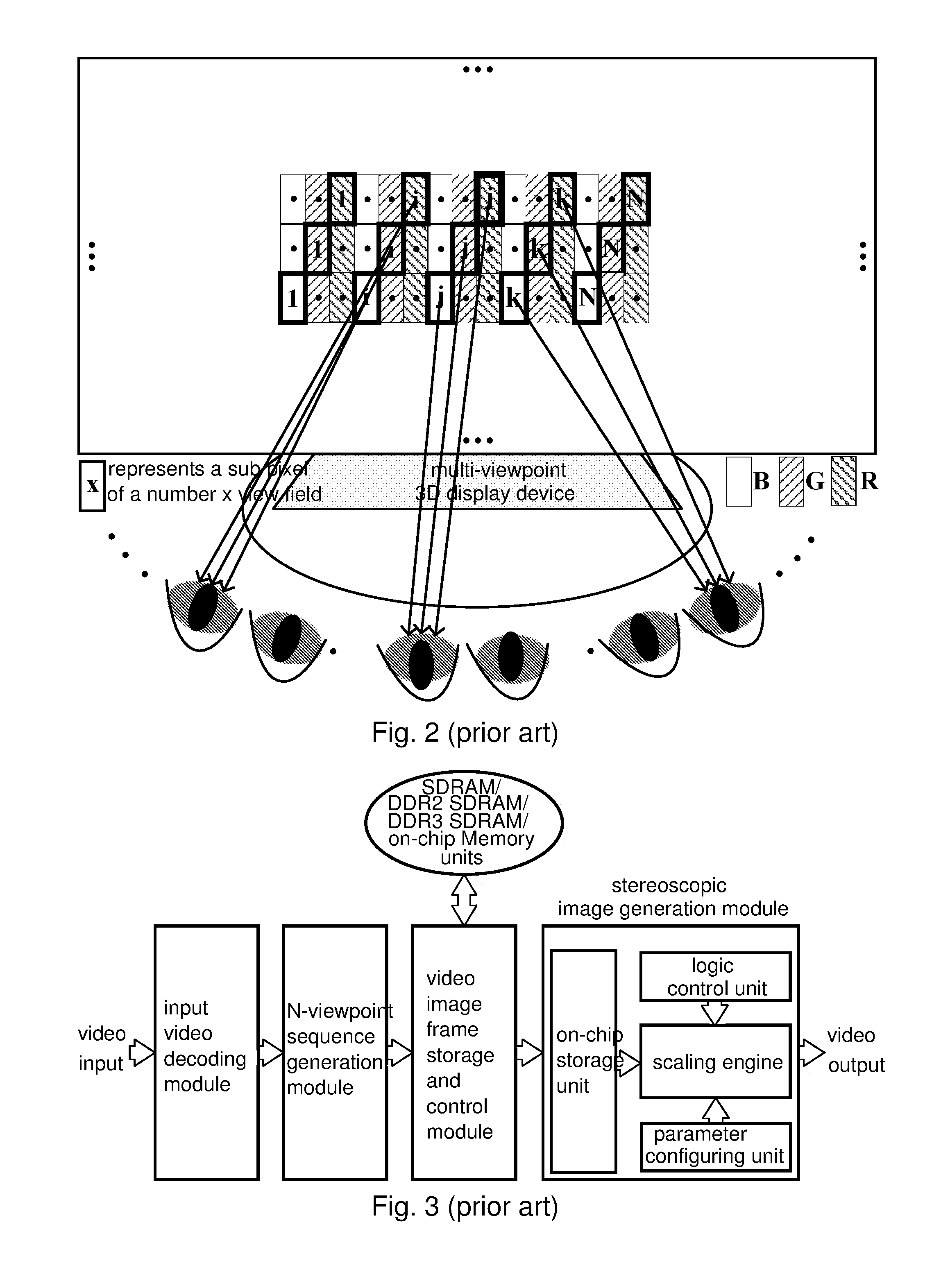

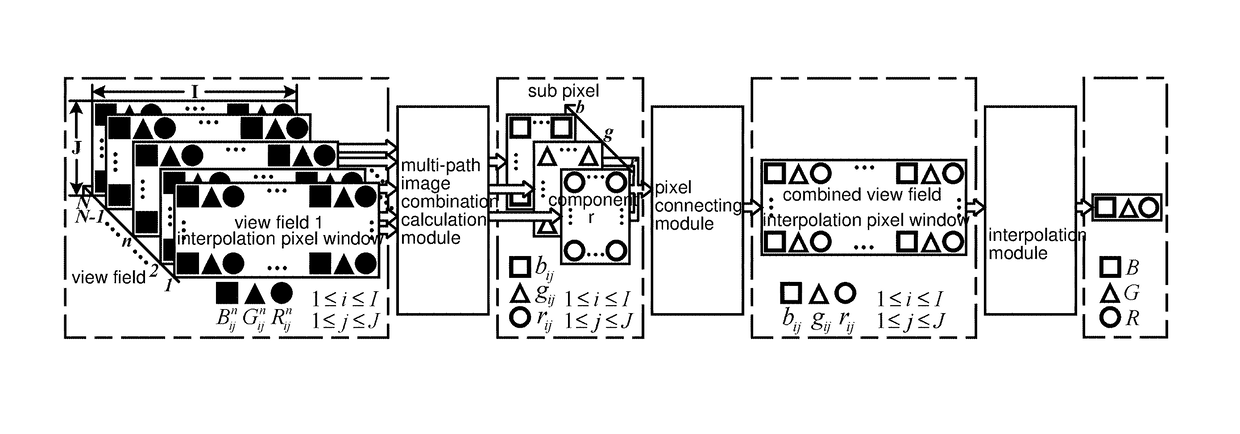

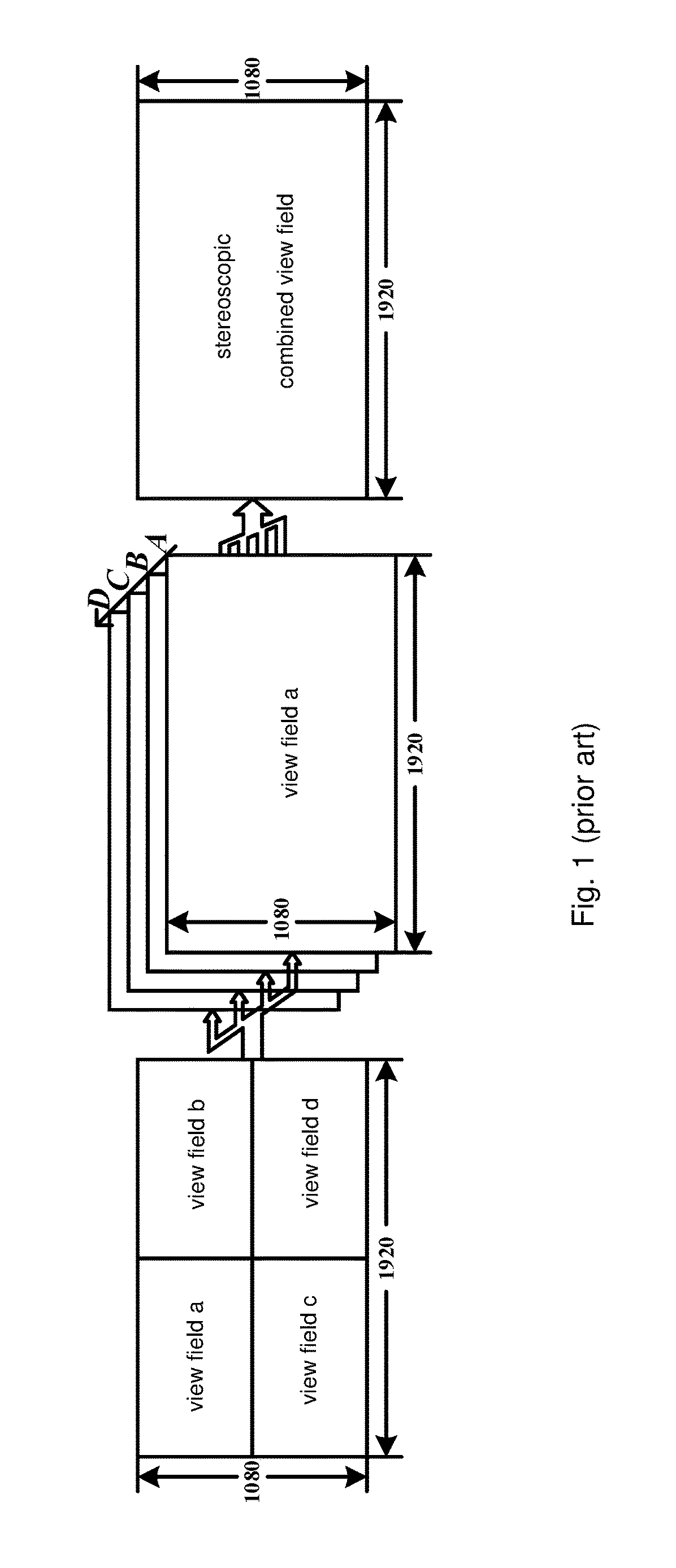

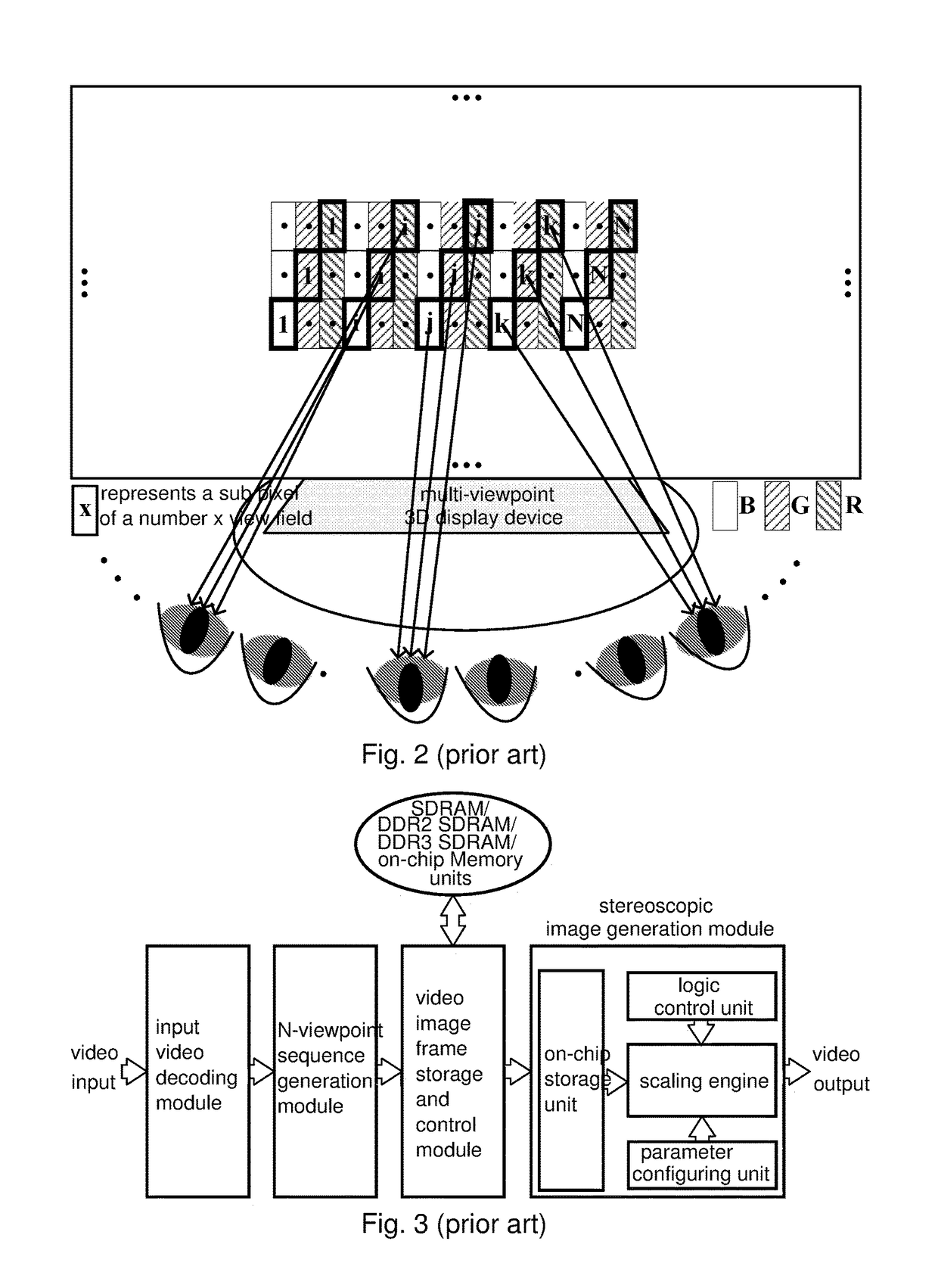

Parallel scaling engine for multi-view 3DTV display and method thereof

ActiveUS20160156898A1Remove redundant pixel calculationCalculation resource is savedGeometric image transformationSteroscopic systemsViewpointsFloating point

A parallel synchronous scaling engine for multi-view 3D display and a method thereof are provided, wherein, selection and combination calculation are provided to an interpolation pixel window, then interpolation calculation is provided to a combined interpolation pixel window of a combined view field, calculation results are directly displayed on a display terminal. That is to say, interpolation is originally provided before stereoscopic pixel rearrangement, which is now improved, in such a manner that screening and combination of pixel points is provided before interpolation calculation. According to the present invention, computation and memory resource is greatly saved. The method is suitable to be implemented by hardware, for satisfying various numbers of viewpoints and interpolation algorithm, and being compatible with multi-view 3D display with the integrated and floating-point pixel arrangement, wherein the computation resource does not need to be increased with increasing of the viewpoints.

Owner:XI AN JIAOTONG UNIV

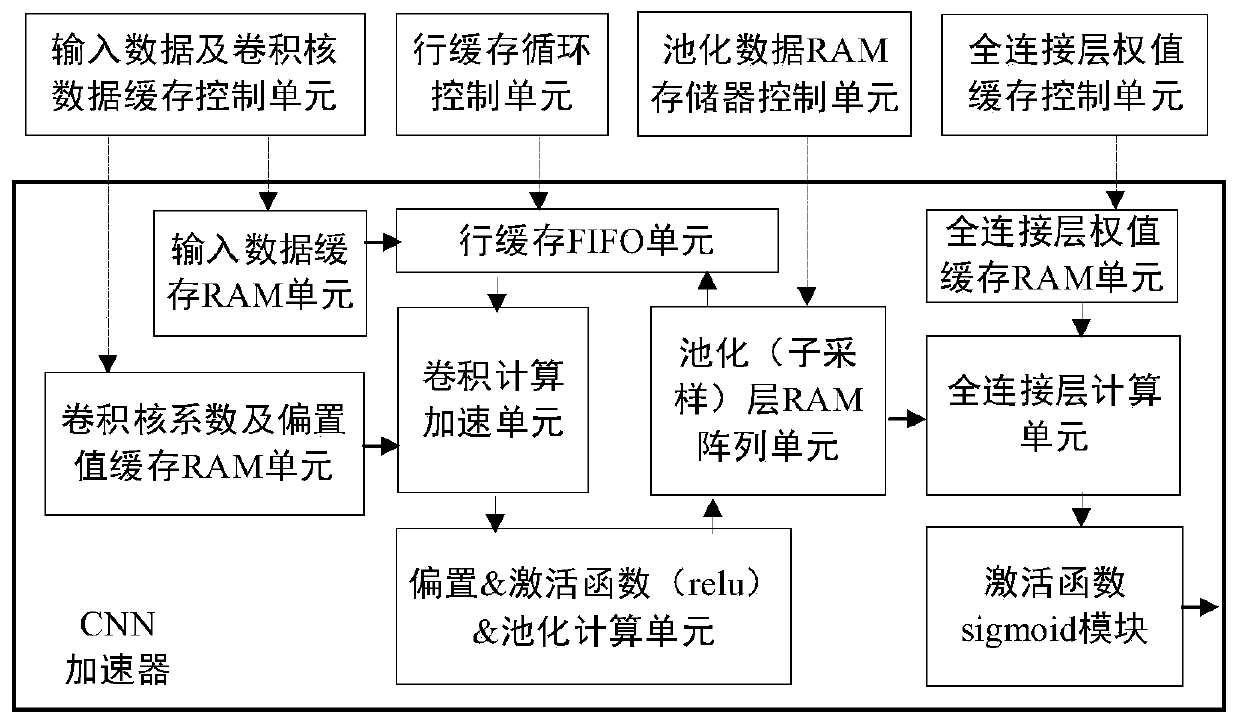

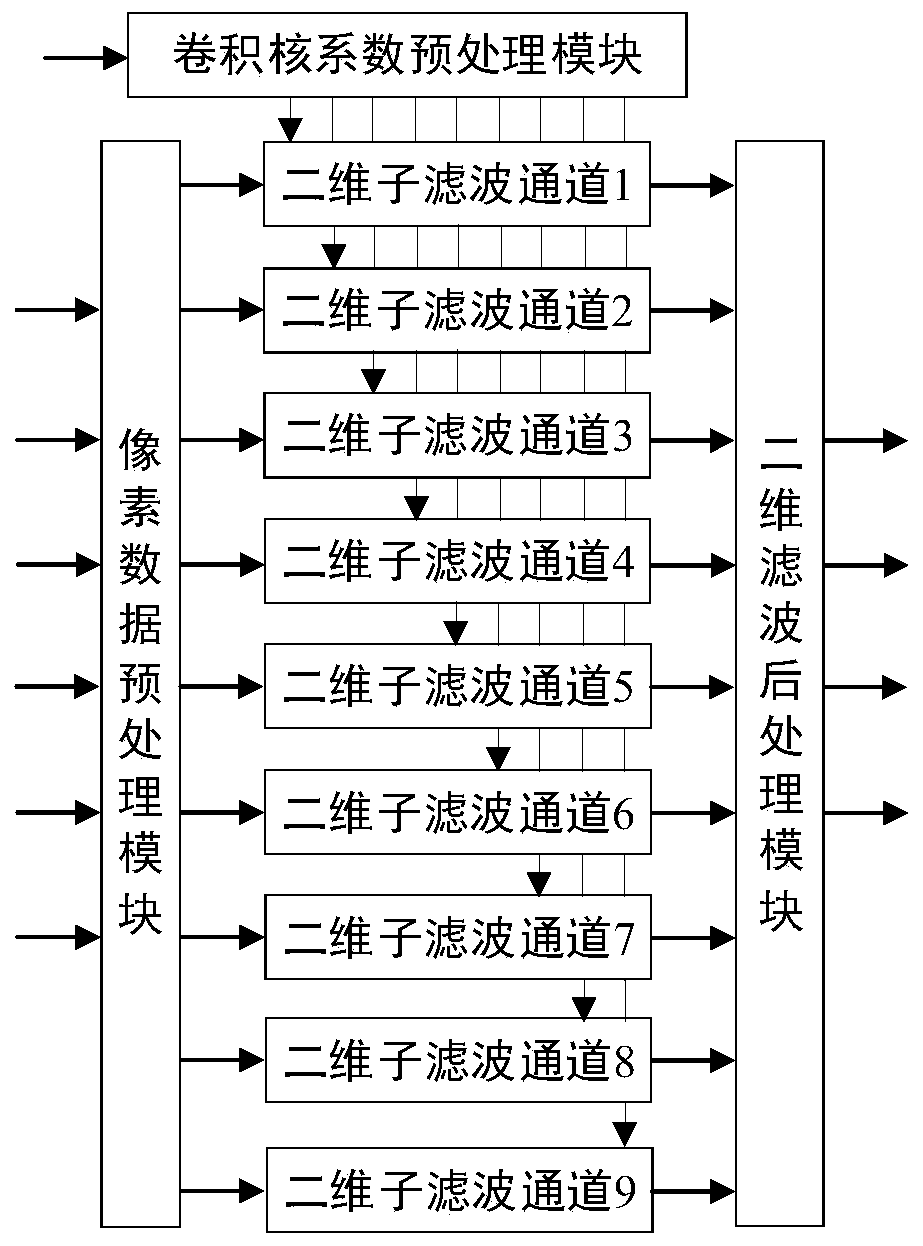

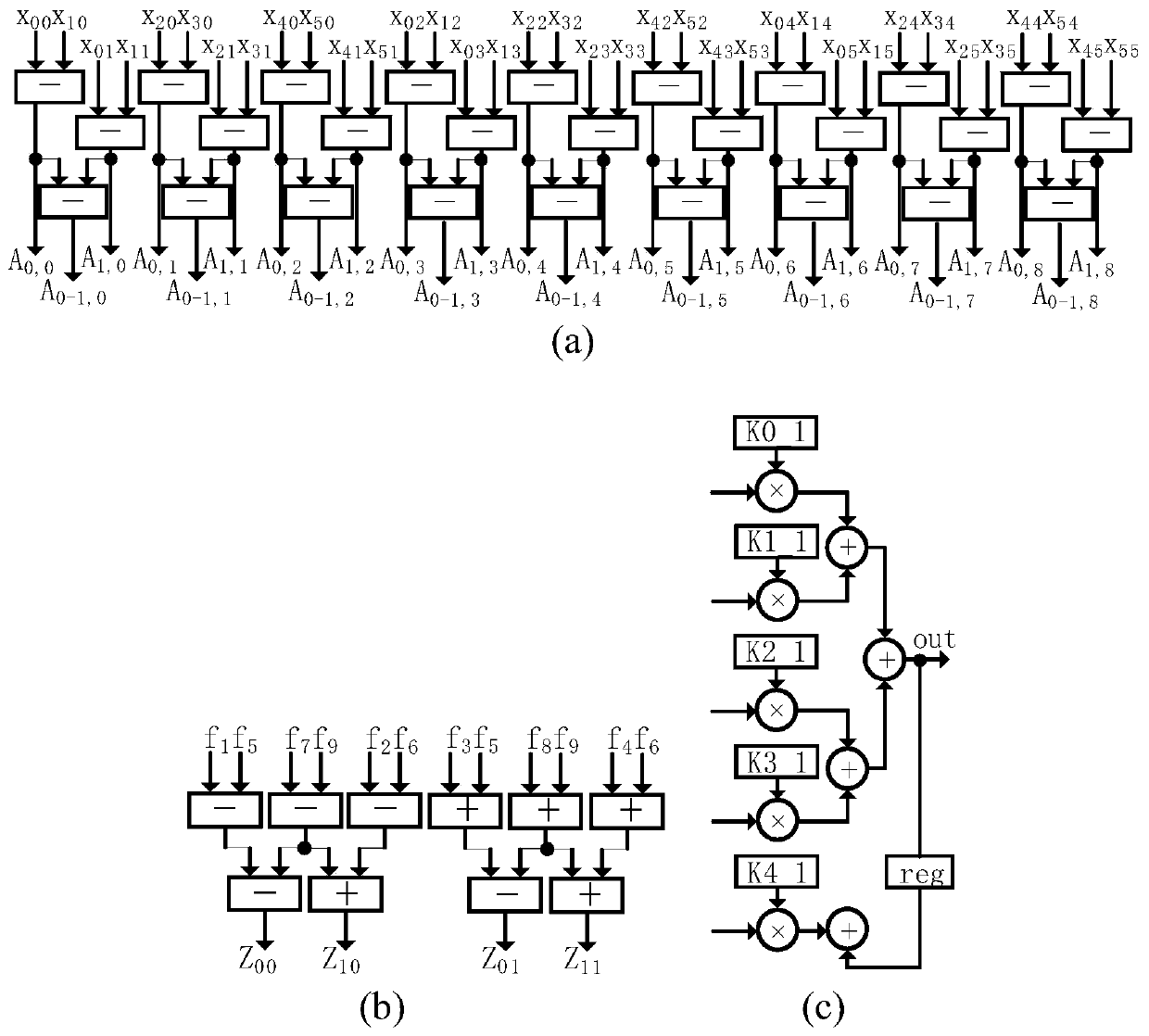

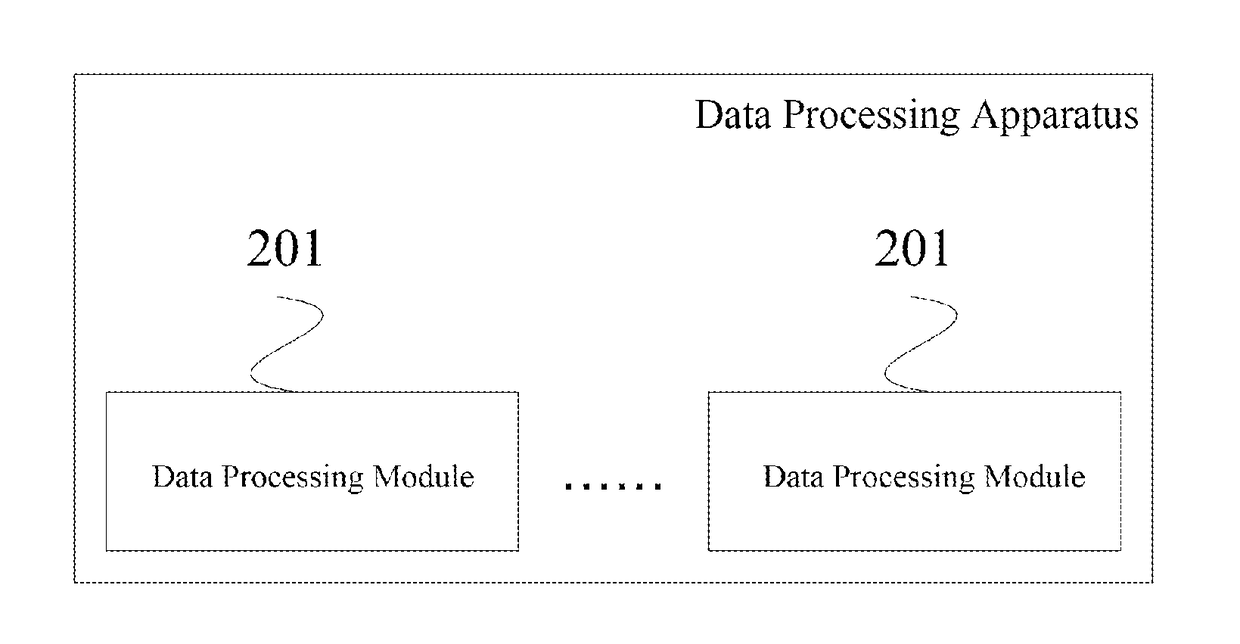

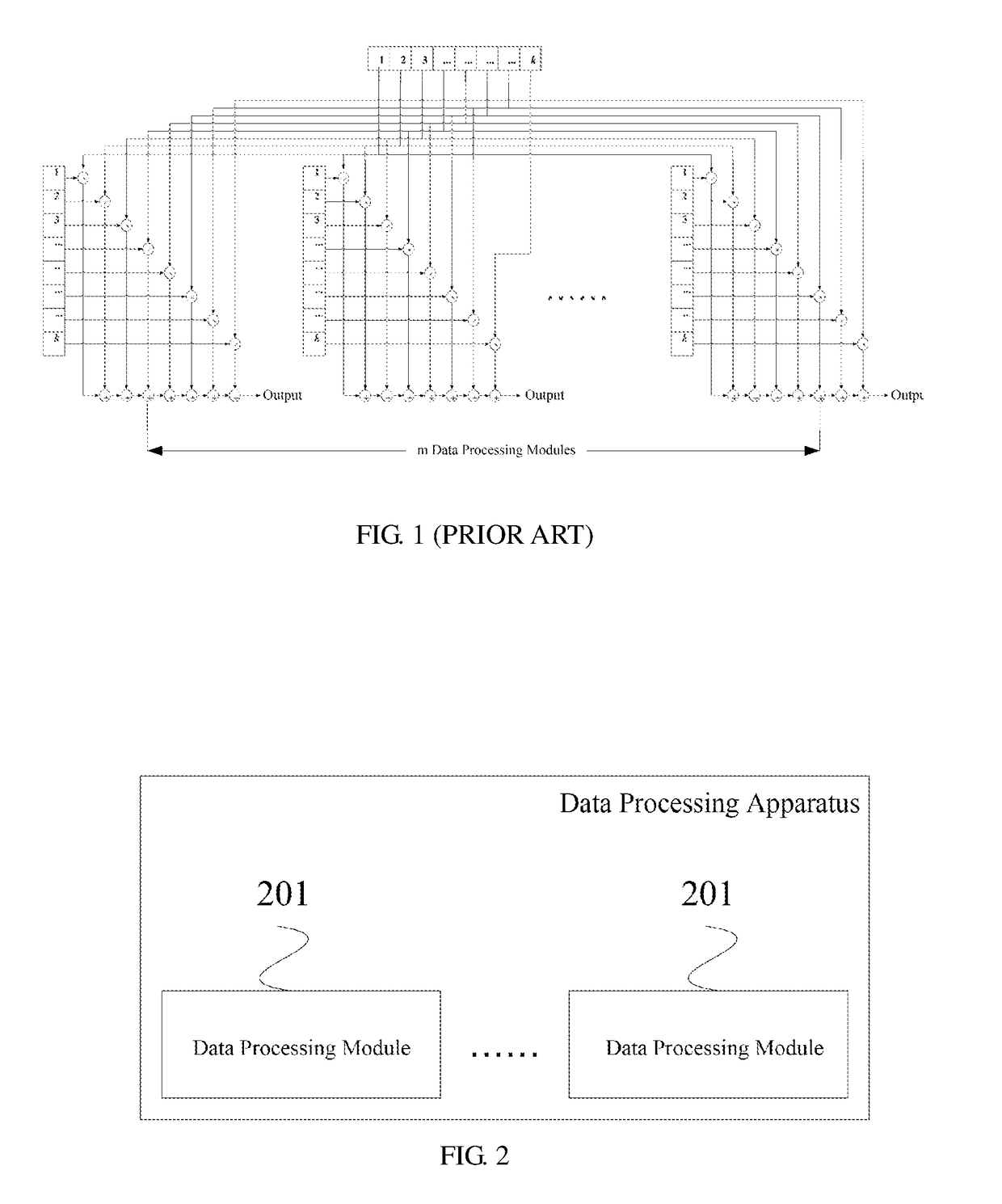

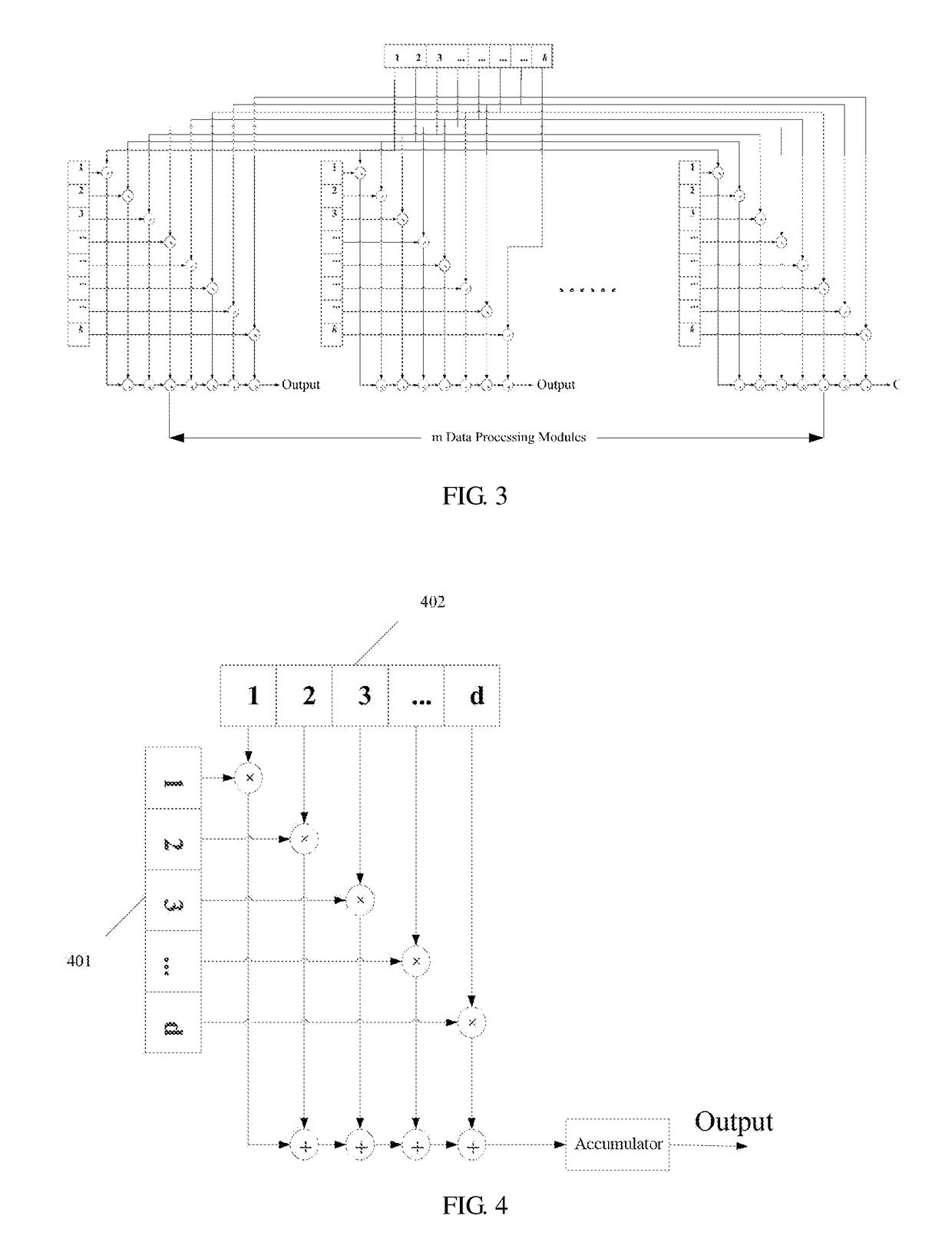

A convolutional neural network accelerator circuit based on a fast filtering algorithm

ActiveCN109948784AImprove performanceSave caching timeEnergy efficient computingPhysical realisationActivation functionFilter algorithm

The invention discloses a convolutional neural network accelerator circuit based on a fast filtering algorithm. In order to reduce the calculation amount of a convolutional neural network algorithm (CNN), the method provided by the invention utilizes a fast filtering algorithm to eliminate the redundancy of overlapped region calculation between convolutional windows in two-dimensional convolutionoperation, so that the algorithm strength is reduced, and the convolution calculation efficiency is improved. Next, a convolution calculation acceleration unit of a four-parallel fast filtering algorithm is designed, and the unit is realized by adopting a parallel filtering structure which is composed of a plurality of small filters and is low in complexity. For the programmable FPGA design, not only can the consumption of hardware resources be reduced, but also the running speed can be increased. Meanwhile, the activation function is subjected to optimization design, and a hardware circuit ofthe activation function (sigmoid) is designed by using a piecewise fitting method combining a lookup table and a polynomial, so that the hardware circuit of the approximate activation function is ensured not to reduce the precision.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

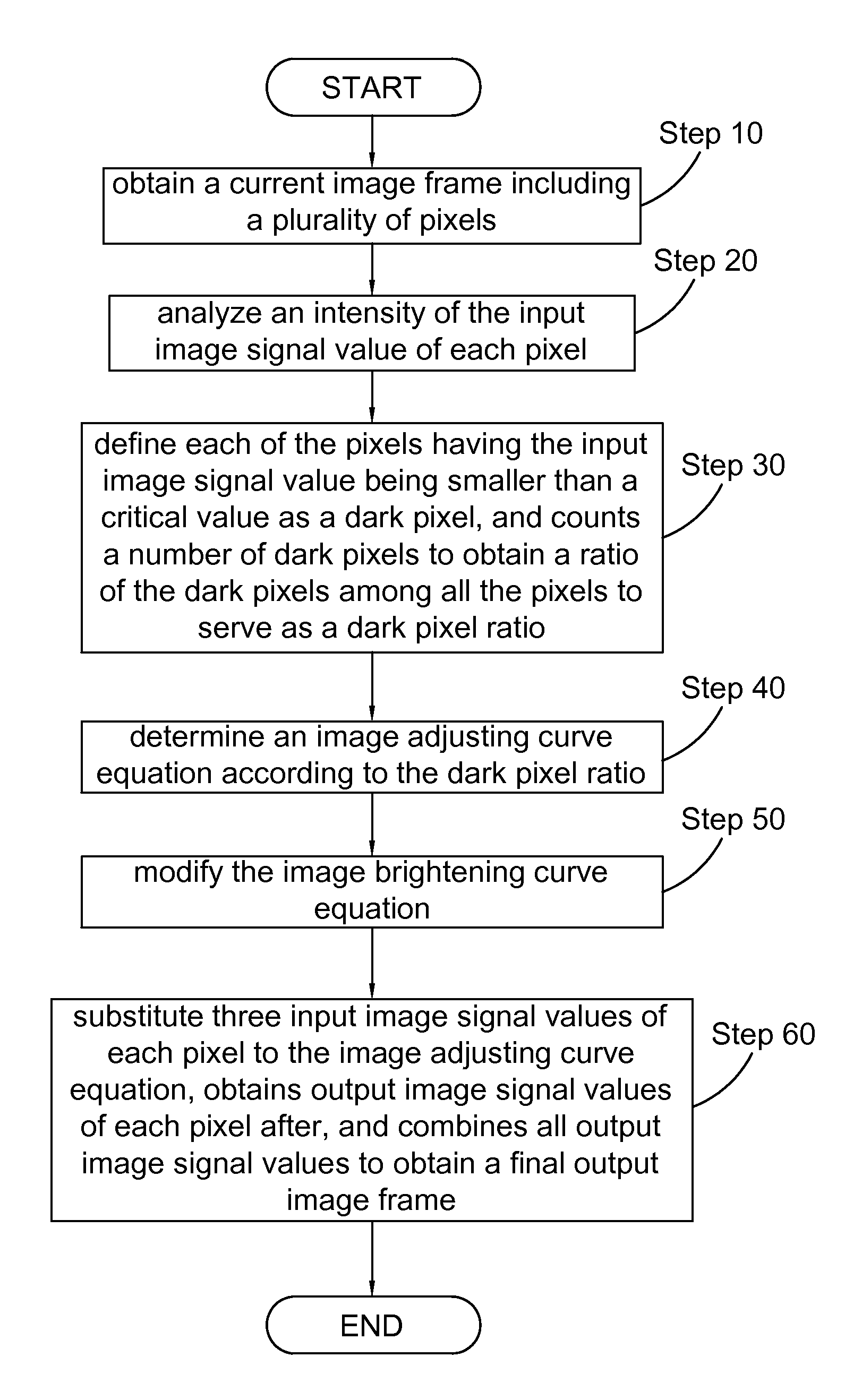

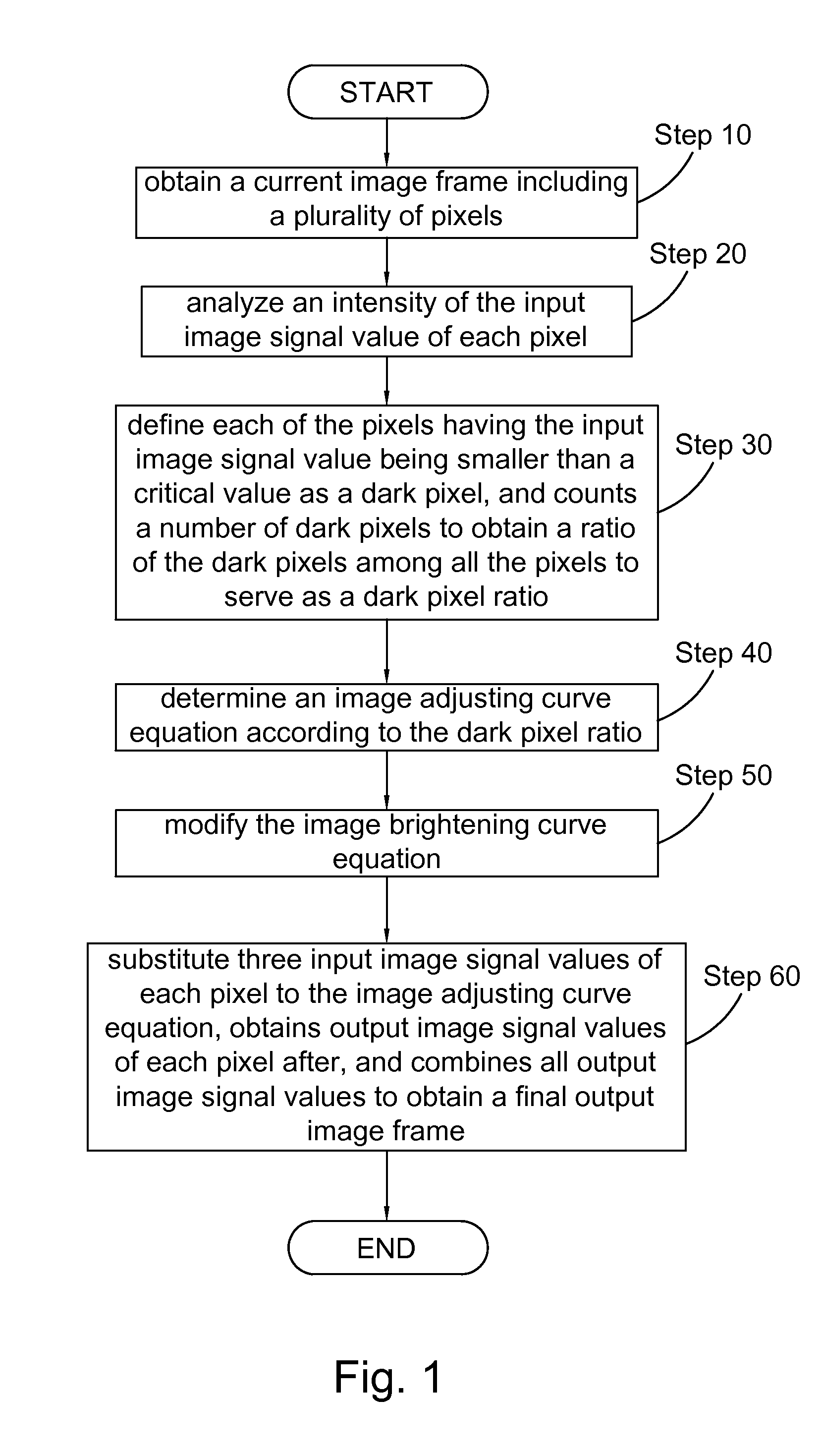

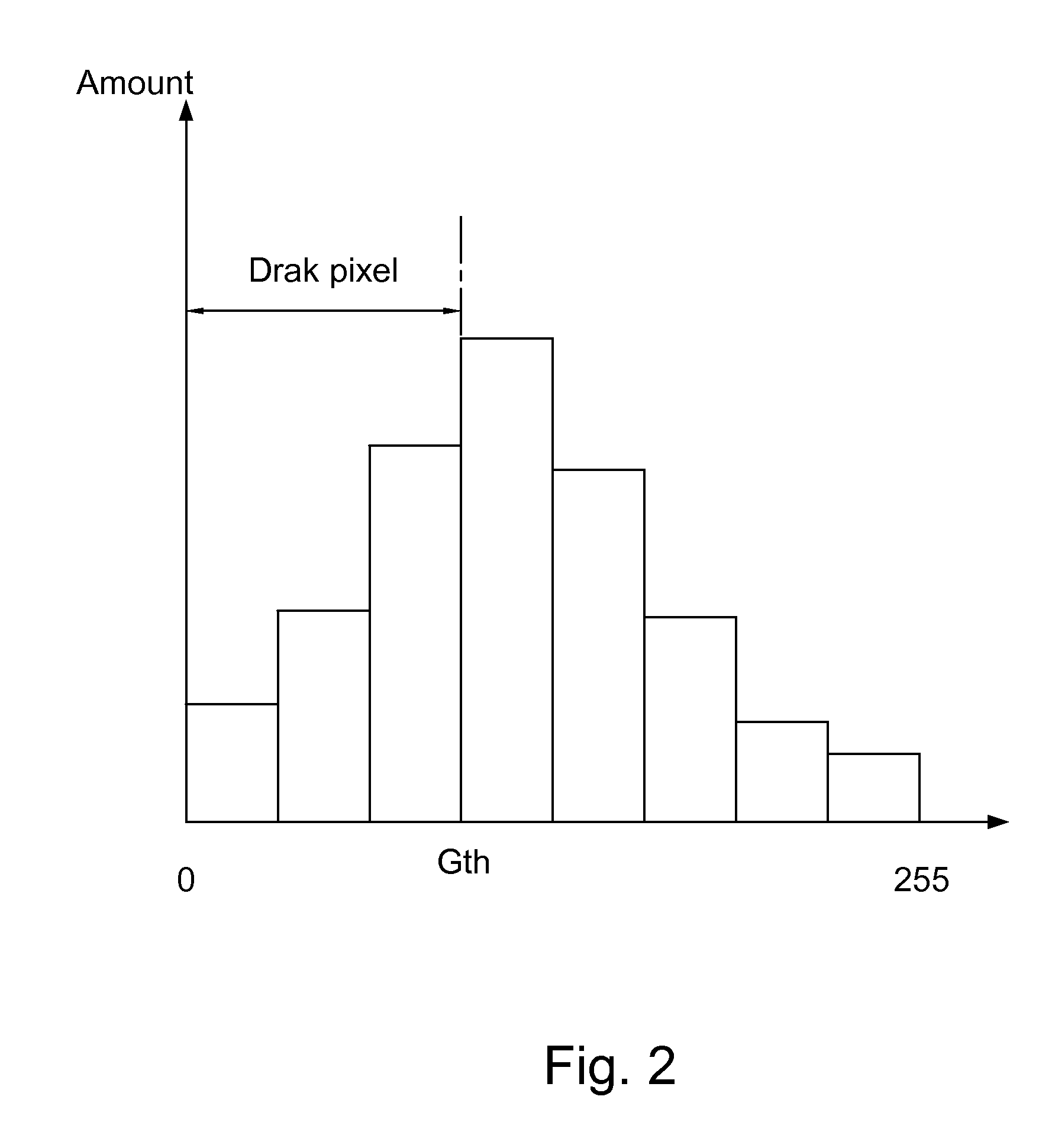

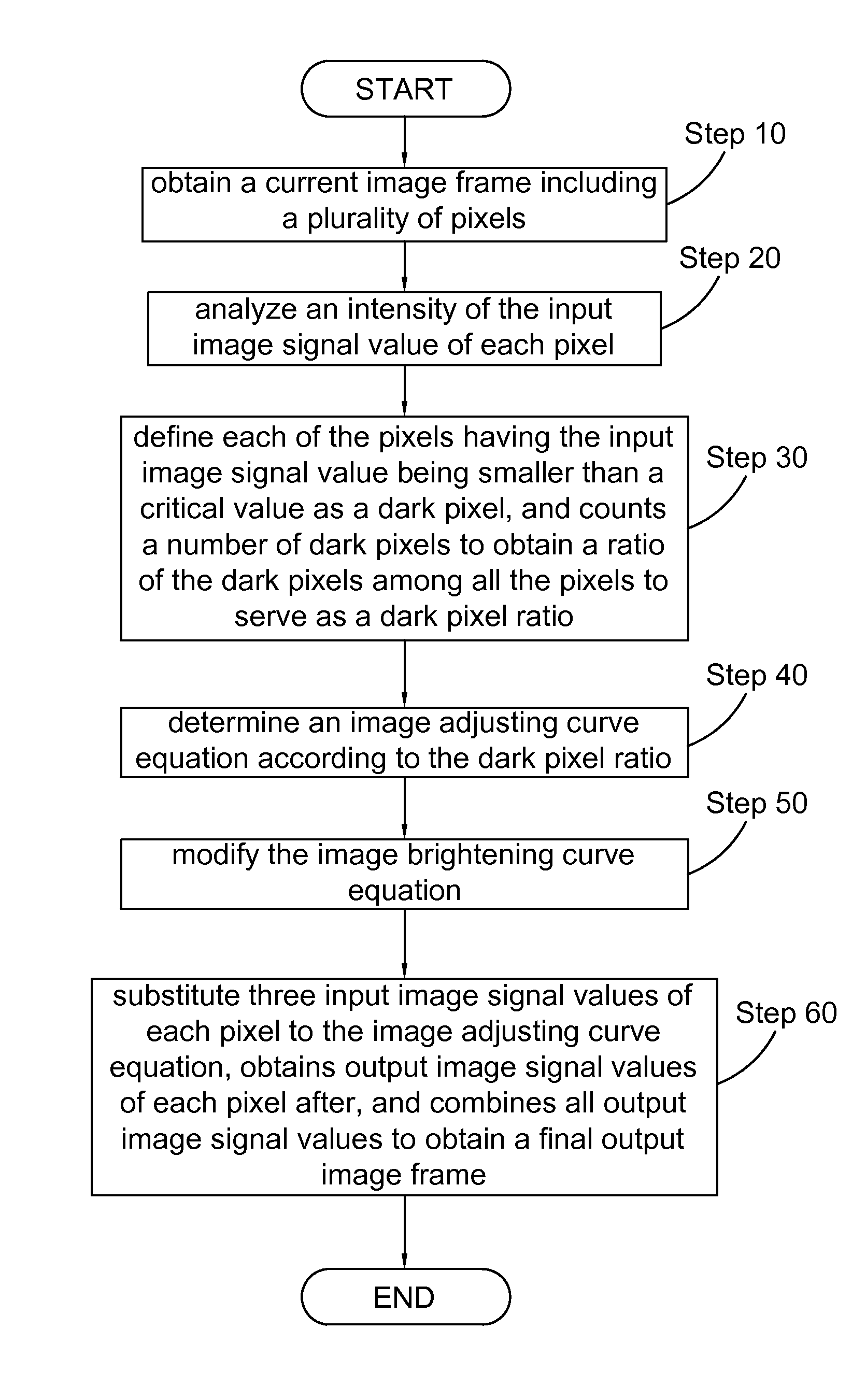

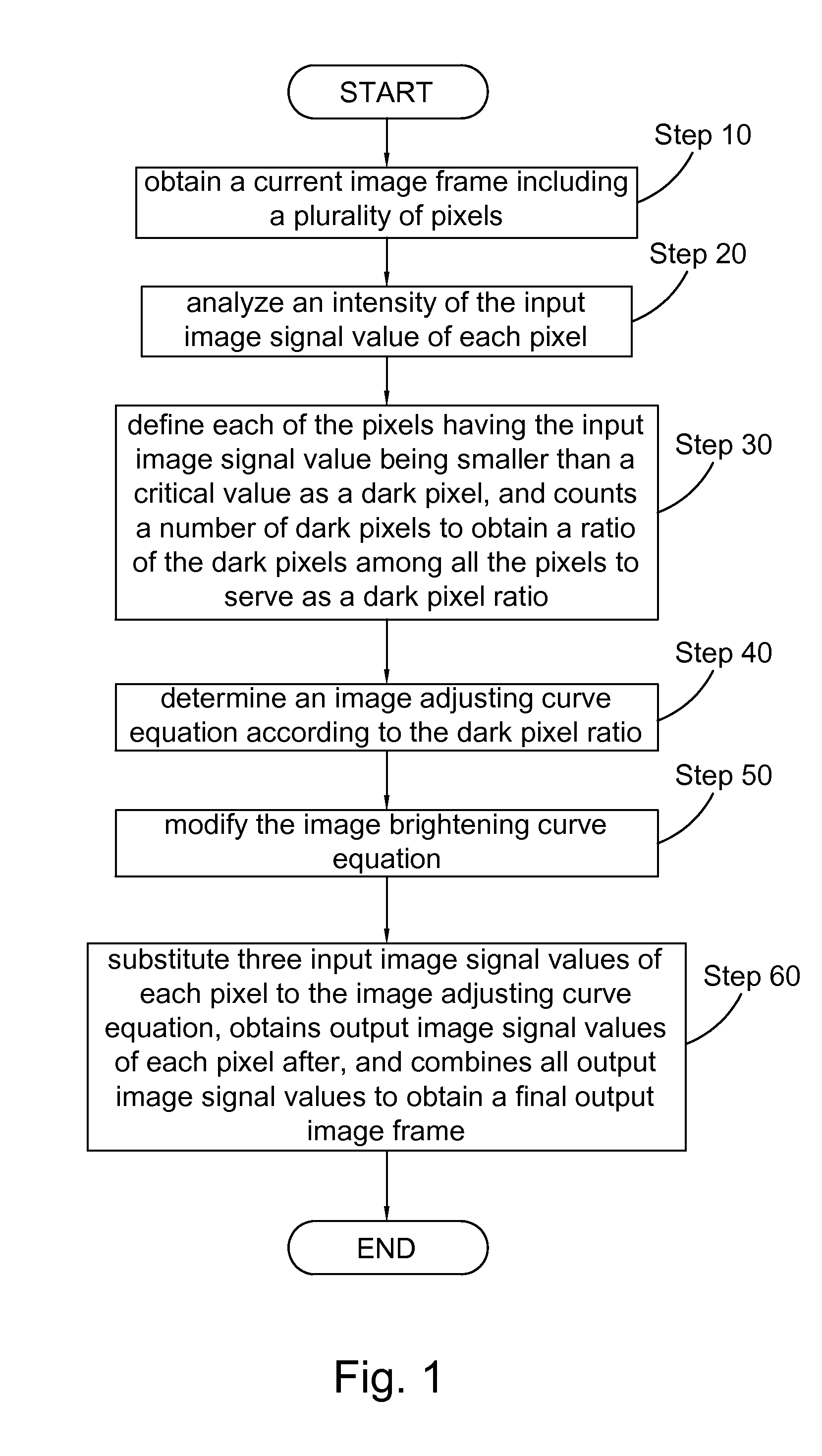

Method for adjusting image

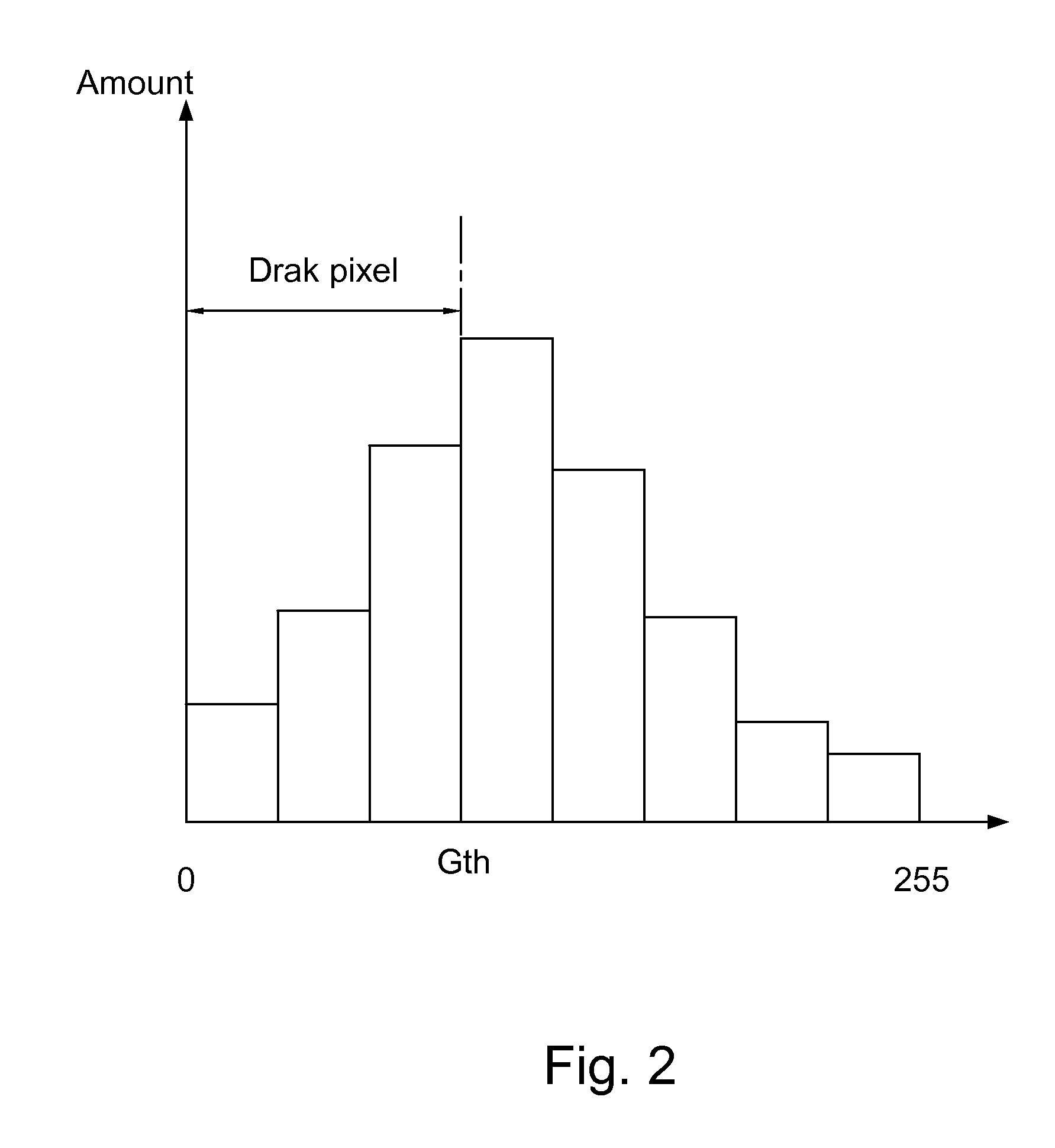

ActiveUS20110141371A1Reduce hardware resource consumptionImproving image adjustment effectTelevision system detailsColor signal processing circuitsOutput deviceImaging Signal

A method for adjusting image is applied to an image output device. According to the method, the image output device firstly obtains a current image frame including plural pixels, and analyzes an intensity of an input image signal value of each pixel. The image output device defines each pixel having the input image signal value being smaller than a critical value as a dark pixel, and counts a number of the dark pixels to obtain a ratio of the dark pixels among all the pixels to serve as a dark pixel ratio. The image output device determines an image adjusting curve equation according to the dark pixel ratio, substitutes the input image signal values to the image adjusting curve equation, and obtains output image signal values of the pixels. Finally, the image output device combines all the output image signal values to obtain a final output image frame.

Owner:MSI COMP SHENZHEN

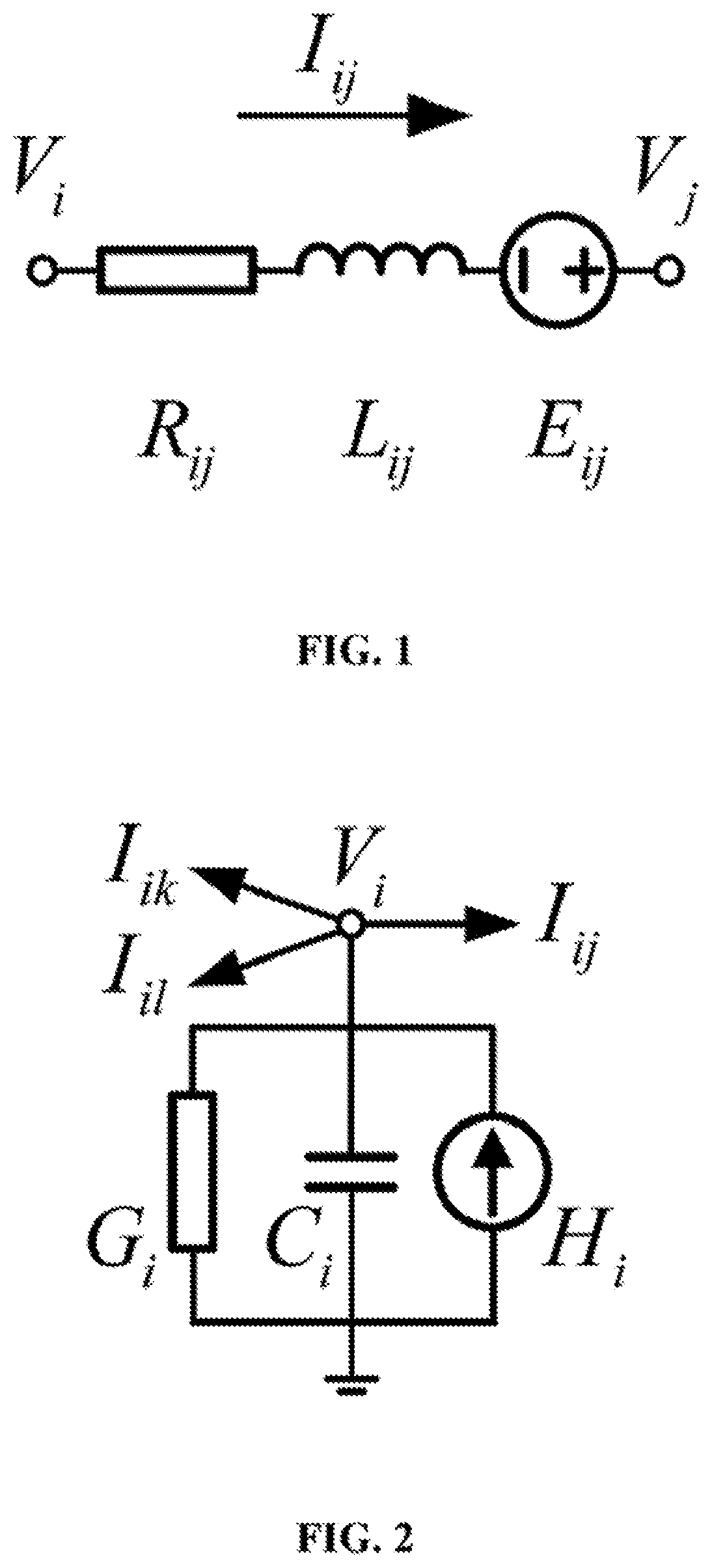

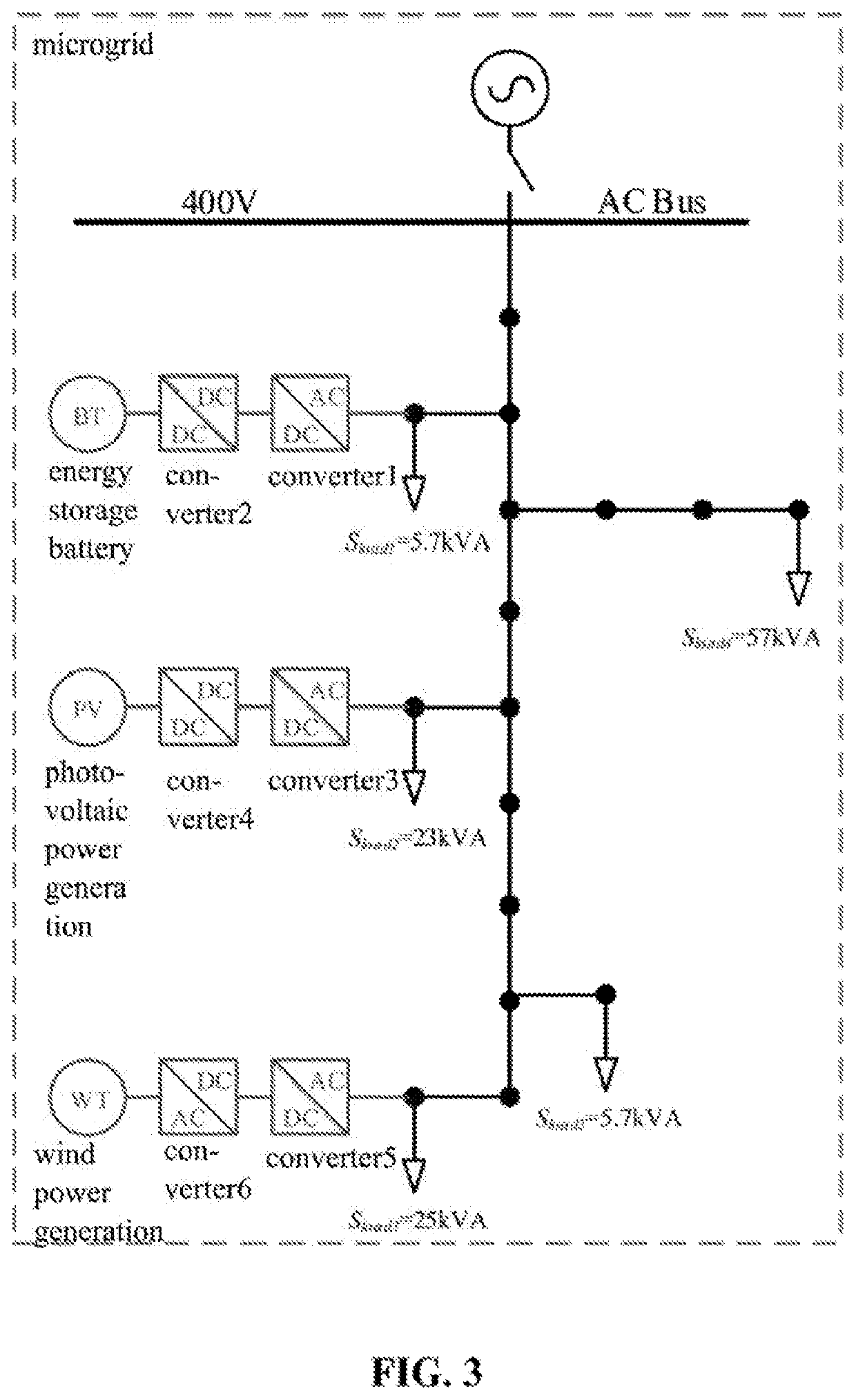

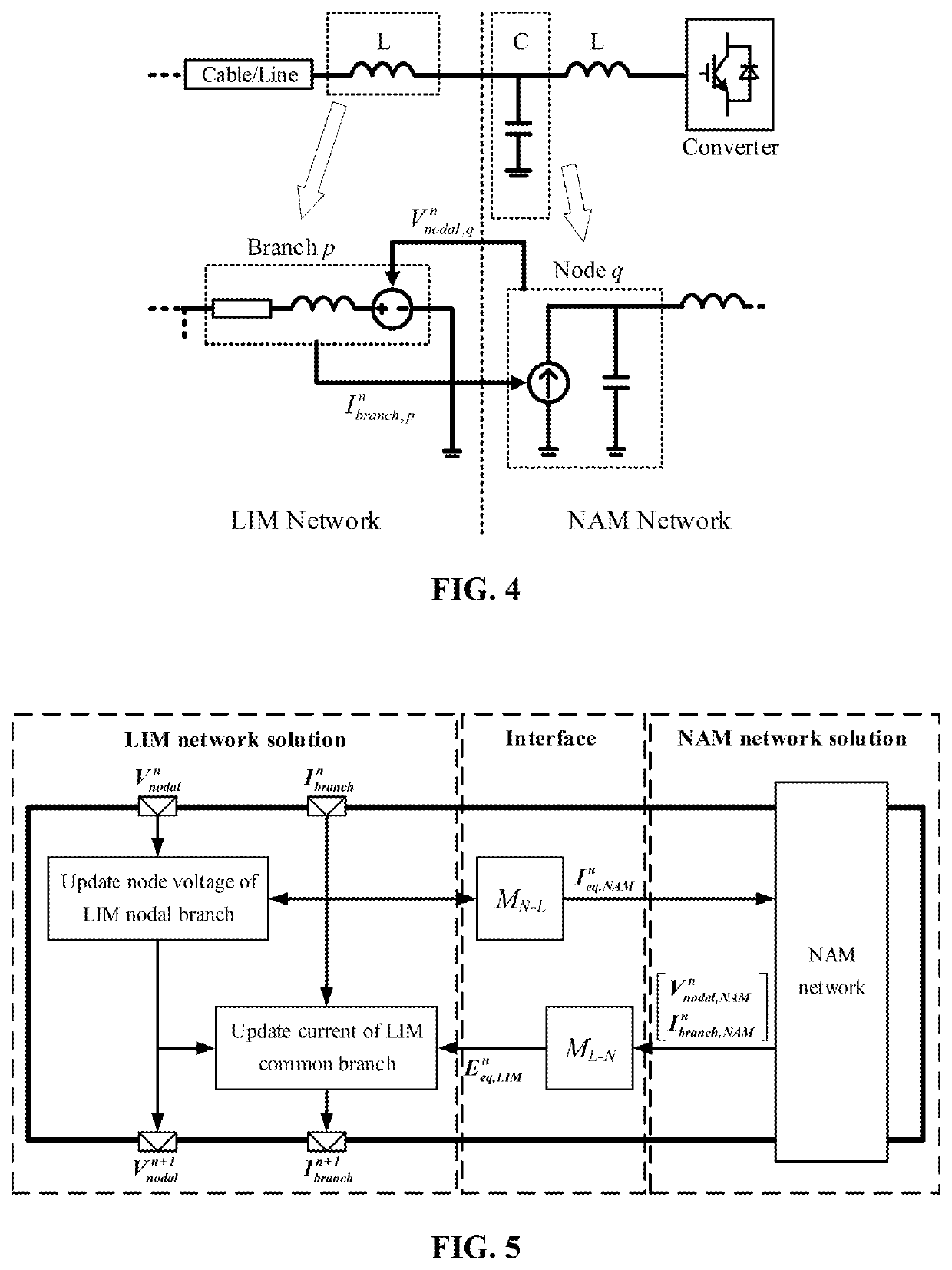

Hybrid electromagnetic transient simulation method for microgrid real-time simulation

ActiveUS20210050722A1High simulationImprove parallelismGeneration forecast in ac networkSingle network parallel feeding arrangementsDiagonal matrixEngineering

A hybrid electromagnetic transient simulation method for microgrid real-time simulation, wherein a traditional node analysis method (NAM) and a highly parallel latency insertion method (LIM) are combined, so that the microgrid is firstly divided from a filter of a distributed power generation system to form one latency insertion method (LIM) network containing a power distribution line and a plurality of node analysis method (NAM) networks containing the distributed power generation system respectively, the NAM network being simulated by traditional node analysis method, the LIM network being simulated by the latency insertion method, in an initialization stage, one correlation matrix and four diagonal matrixes containing line parameters used for LIM network simulation being formed according to line topology and parameters of the microgrid, in a main cycle of the simulation, the LIM network solved simultaneously with multiple NAM networks, a parallelism of a microgrid simulation being improved.

Owner:SHANGHAI JIAO TONG UNIV

Portable communication device for an advanced display

ActiveUS7925202B2OptimizationImprove the display effectTelevision system detailsColor television detailsStatic random-access memoryData stream

A portable communication device equipped with a screen and a random access memory. The device receives a data stream through a radio link for automatically displaying information from the data stream on a display screen, without any user's request, a part of this information being stored in random access memory during a period of time that is longer than the duration of display and displays information from the data stream on the display screen, upon user's request, this information being stored in random access memory during the duration of display only.

Owner:INTERDIGITAL CE PATENT HLDG

Method for adjusting image

ActiveUS8218087B2Reduce hardware resource consumptionConsume resourcesTelevision system detailsColor signal processing circuitsOutput deviceComputer science

A method for adjusting image is applied to an image output device. According to the method, the image output device firstly obtains a current image frame including plural pixels, and analyzes an intensity of an input image signal value of each pixel. The image output device defines each pixel having the input image signal value being smaller than a critical value as a dark pixel, and counts a number of the dark pixels to obtain a ratio of the dark pixels among all the pixels to serve as a dark pixel ratio. The image output device determines an image adjusting curve equation according to the dark pixel ratio, substitutes the input image signal values to the image adjusting curve equation, and obtains output image signal values of the pixels. Finally, the image output device combines all the output image signal values to obtain a final output image frame.

Owner:MSI COMP SHENZHEN

Encoder and decoder for LDPC code

ActiveUS20170264314A1Reduce the amount requiredReduce hardware resource consumptionError correction/detection using multiple parity bitsCode conversionParity-check matrixParallel computing

Disclosed relates to a decoder for LDPC code, including: a variable node processing unit; a check node processing unit; a memory for storing iterative messages of edges of a parity-check matrix for LDPC code; and a controller for controlling the node processing units to perform iterations of decoding until the decoding ends, wherein, in each iteration of decoding, the controller controls the variable node processing unit to compute variable node messages in a traversing manner for all variable nodes and updates the iterative messages in the memory according to the computed variable node messages, and controls the check node processing unit to compute check node messages in a traversing manner for all check nodes and updates the iterative messages in the memory according to the computed check node messages.

Owner:BEIJING HANG TIAN HUA TECH CO LTD +2

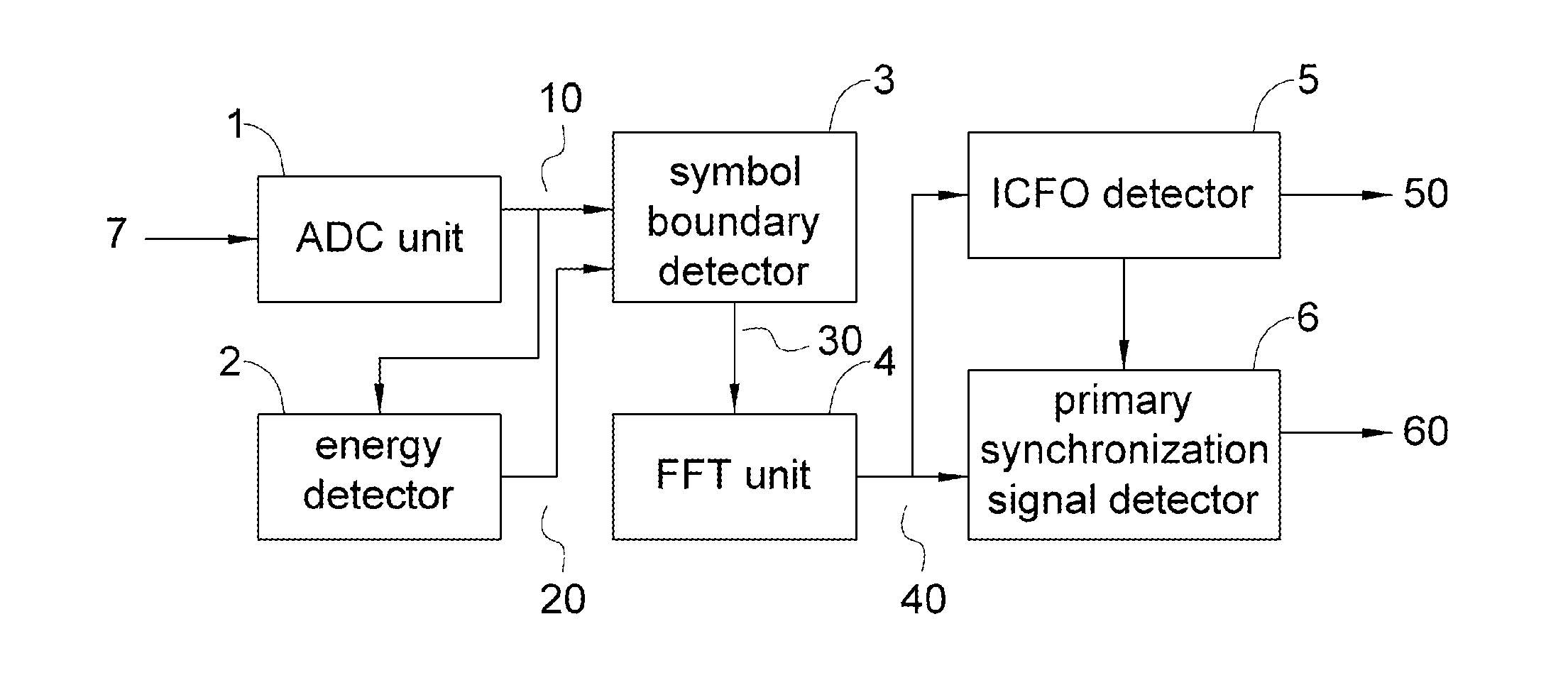

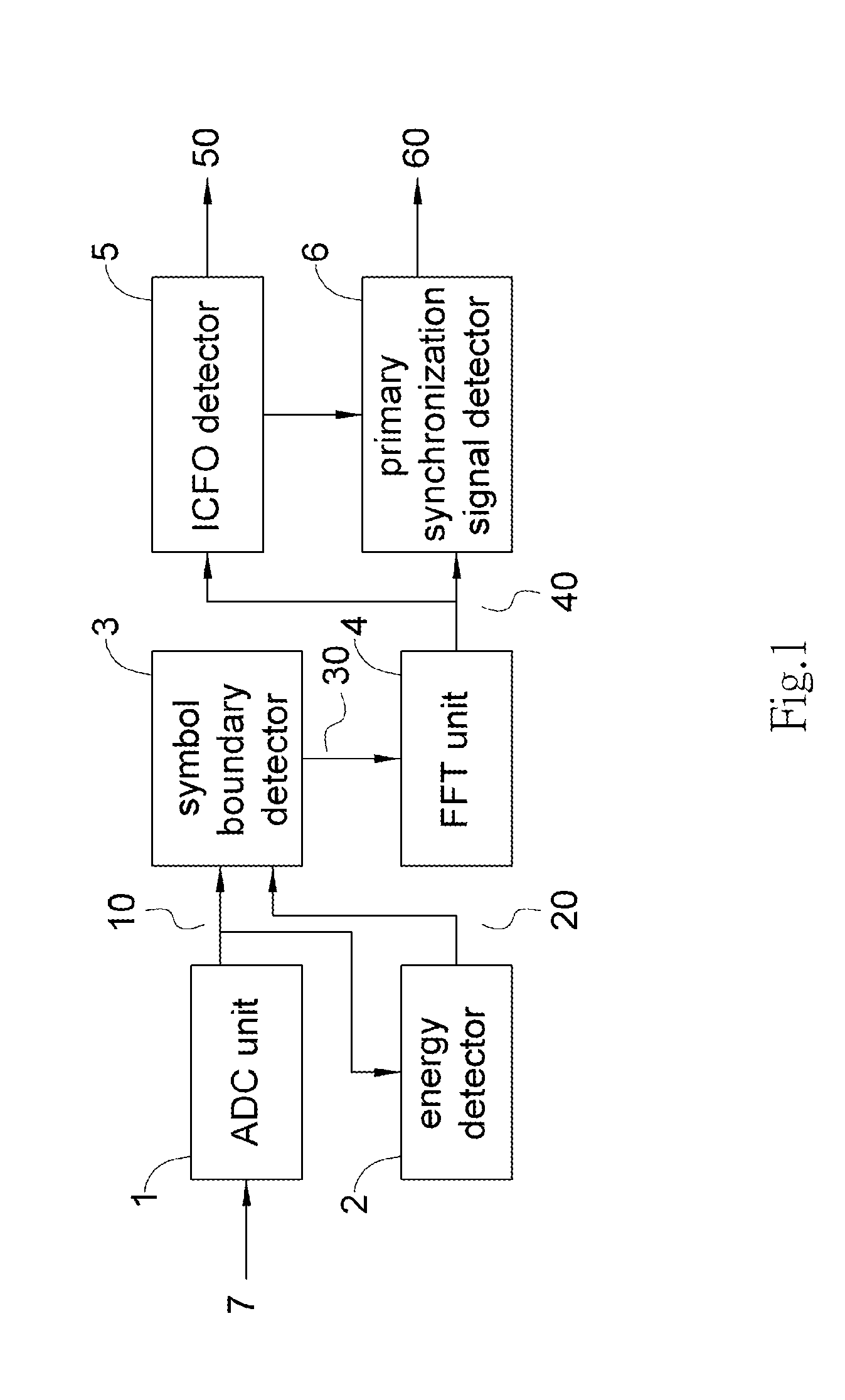

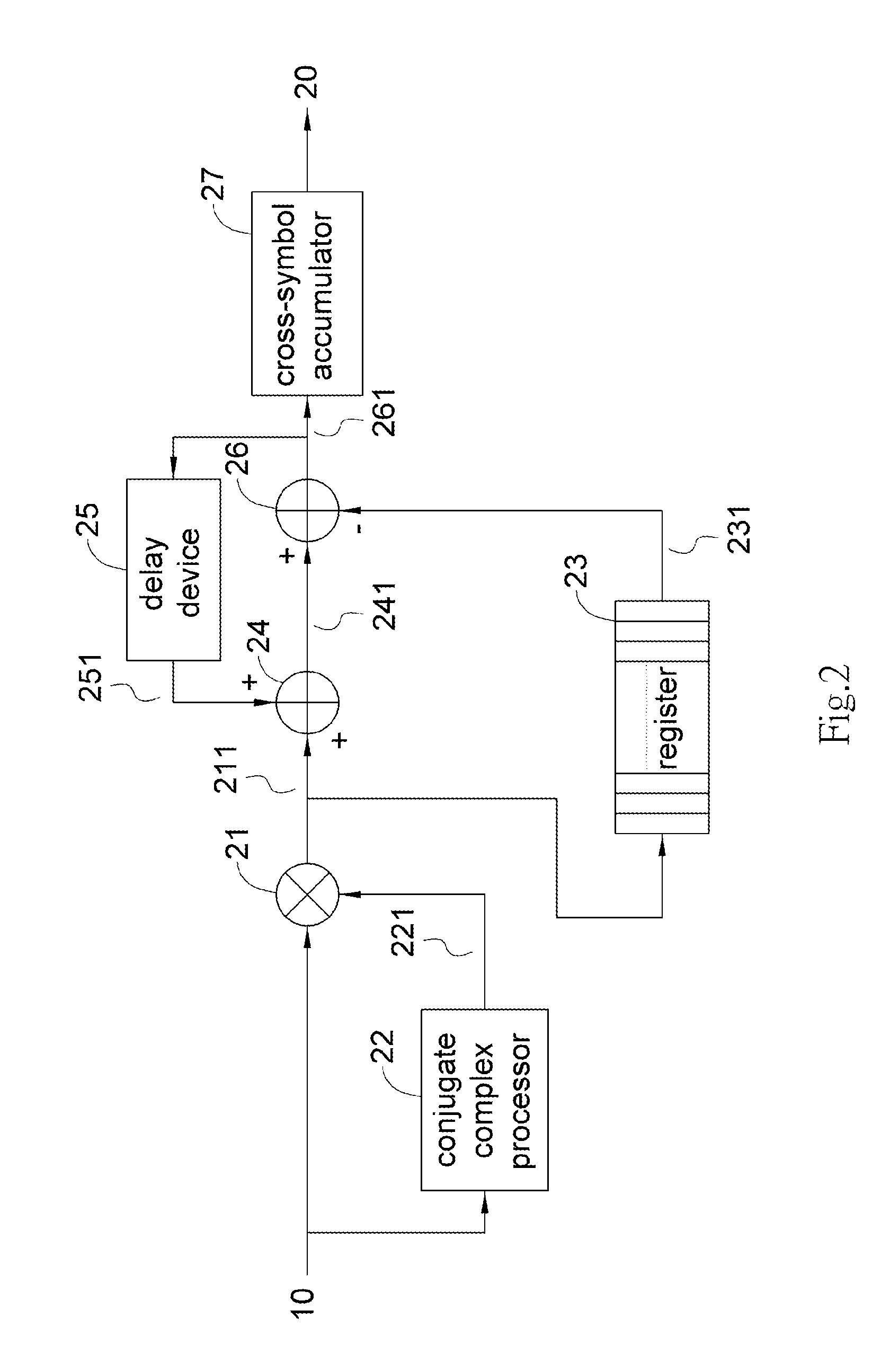

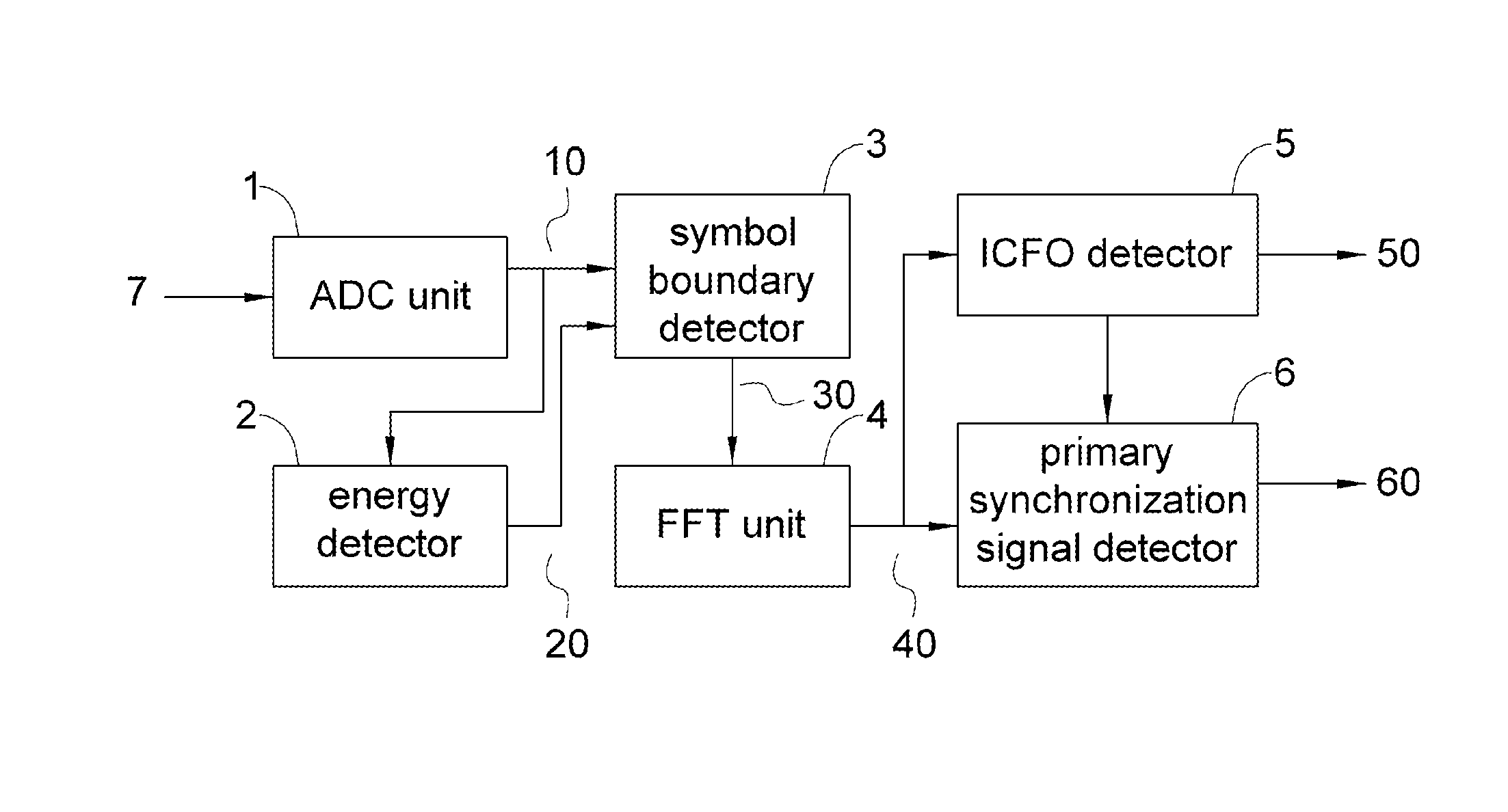

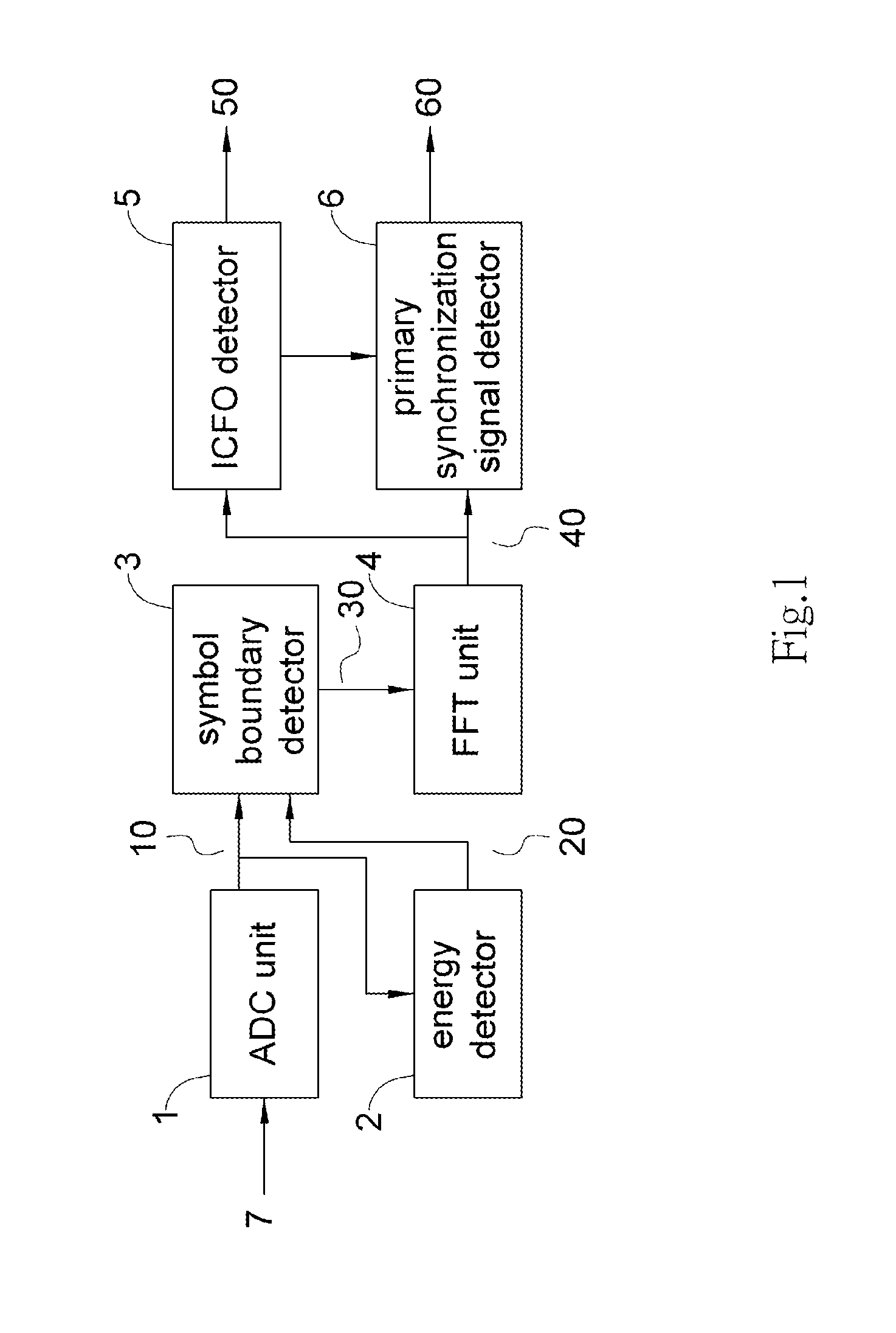

Method and apparatus for cell search and synchronization in mobile communication

ActiveUS20150208369A1Smoothly transmitSmooth transmissionSynchronisation arrangementModulated-carrier systemsCell searchSynchronization signal

The present invention provides a method and an apparatus for cell search and synchronization for subscriber stations of the Long Term Evolution (LTE) system. The invention uses primary synchronizing signal of primary synchronization code in each frame structure to establish synchronization with the base station when a subscriber station accesses the LTE network. With such synchronization between the subscriber station and the base station, control signals and transmission data may be correctly exchanged between them.

Owner:NAT TAIWAN UNIV

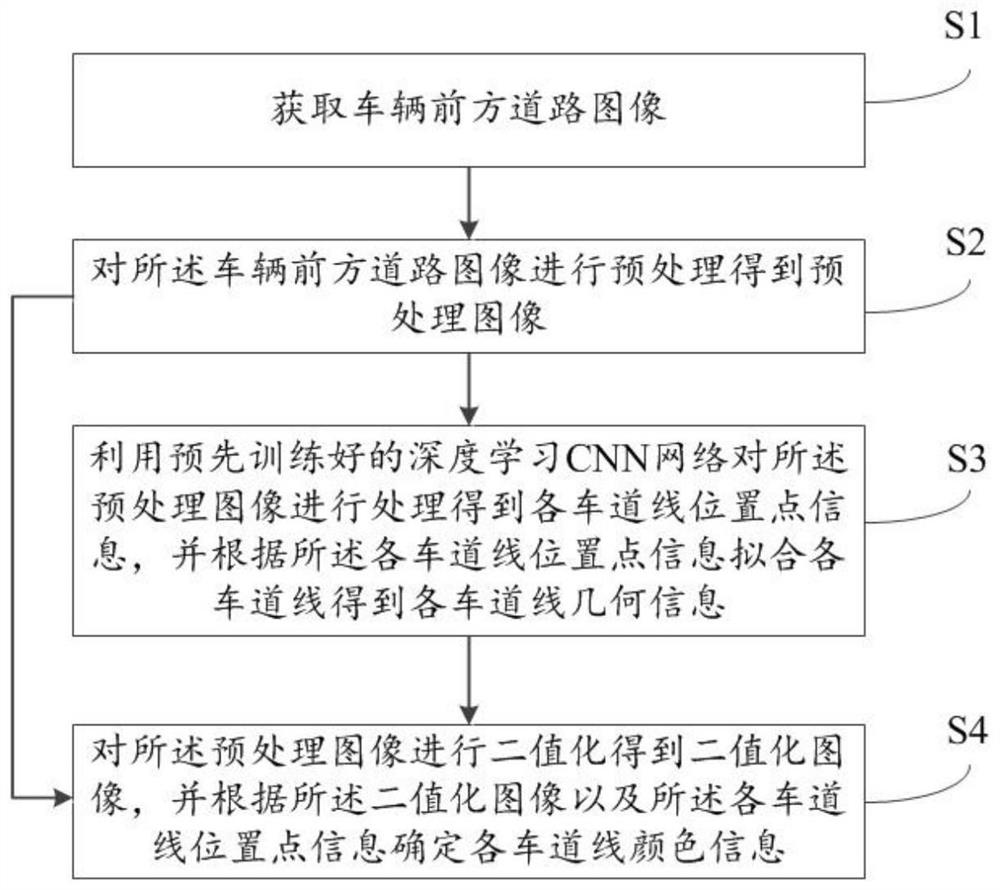

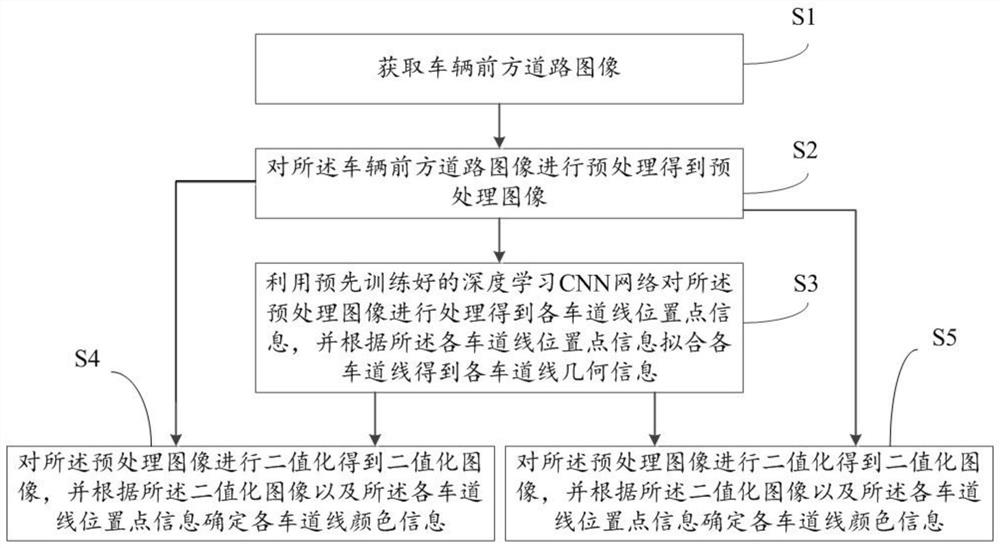

Lane line detection method and system

PendingCN112926365AImprove detection accuracyReduce hardware resource consumptionCharacter and pattern recognitionDetection performanceEngineering

The invention relates to a lane line detection method and system. The method comprises the following steps: acquiring an image of a road in front of a vehicle; preprocessing the image of the road in front of the vehicle to obtain a preprocessed image; processing the preprocessed image by using a pre-trained deep learning CNN network to obtain position point information of each lane line, and fitting each lane line according to the position point information of each lane line; binarizing the preprocessed image to obtain a binarized image, and determining lane line color information according to the binarized image and the position point information of each lane line; and graying the preprocessed image, performing image threshold segmentation to obtain a threshold segmentation image, and determining lane line virtual and real information according to the threshold segmentation image and the position point information of each lane line. The consumed computing resources can be reduced, the lane line detection performance in a special road scene is improved, and the real-time requirement is met.

Owner:GUANGZHOU AUTOMOBILE GROUP CO LTD

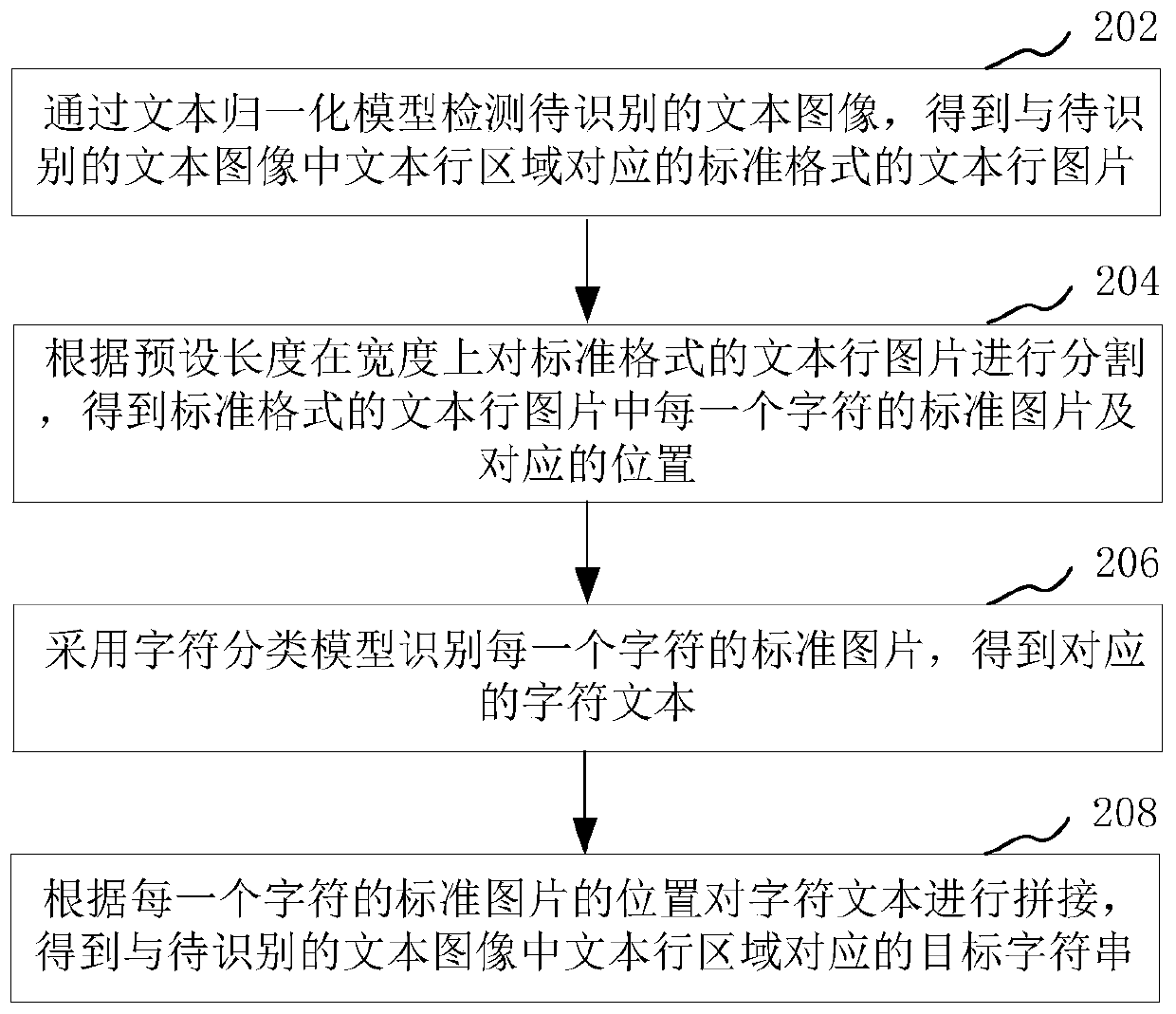

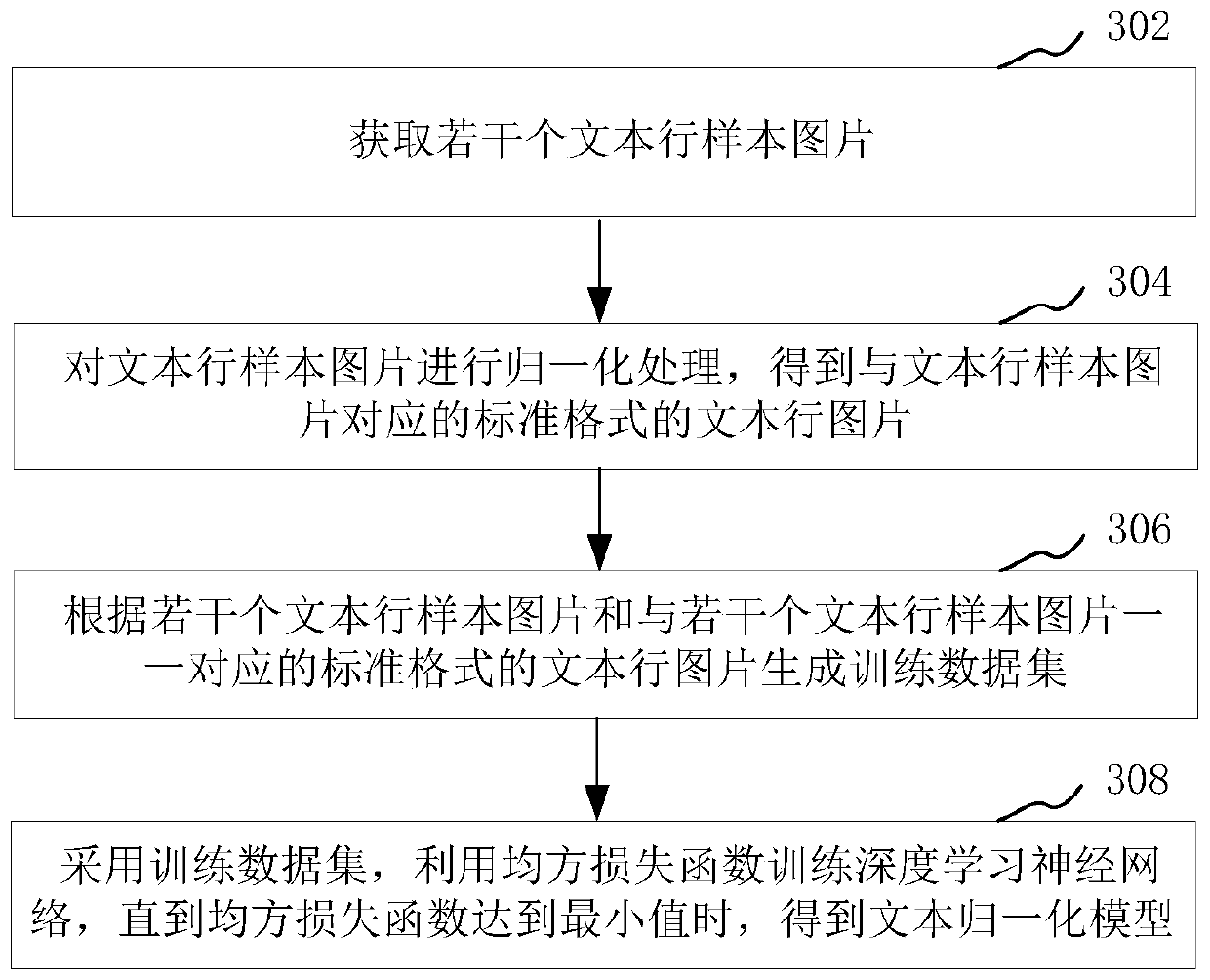

Text recognition method and device, computer equipment and storage medium

PendingCN110969154AReduce hardware resource consumptionExcellent performanceCharacter and pattern recognitionComputer equipmentText normalization

The invention relates to a text recognition method and device, computer equipment and a storage medium. The method comprises the following steps: obtaining a normalized text line picture in a standardformat corresponding to a text line region of a to-be-identified text image by adopting a trained text normalization model; cutting the text line picture in the standard format in the width directionaccording to the preset length; obtaining a standard picture and a corresponding position of each character in the text line picture in the standard format. Therefore, when the OCR task is executed,only simple character classification needs to be carried out without depending on a BLSTM + CTC framework, hardware resource consumption is lower, performance is better, the network structure is simpler, and higher recognition precision is achieved.

Owner:上海眼控科技股份有限公司

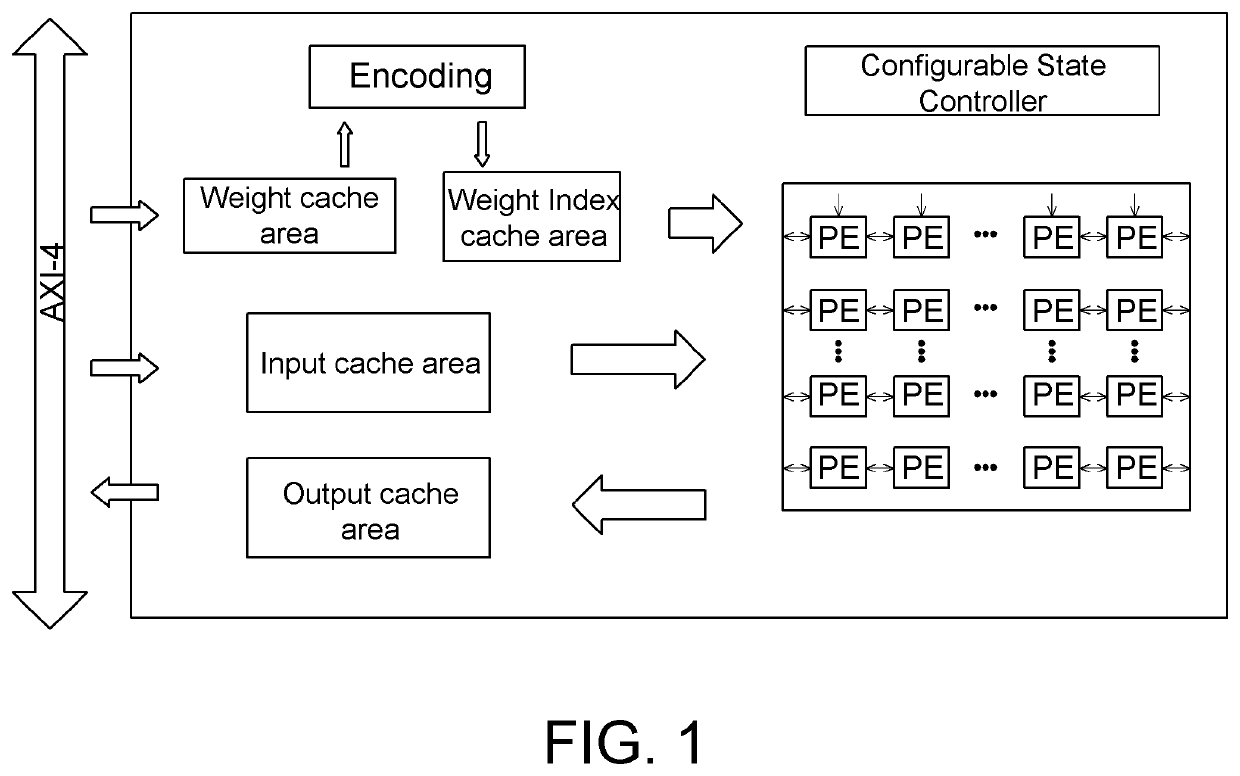

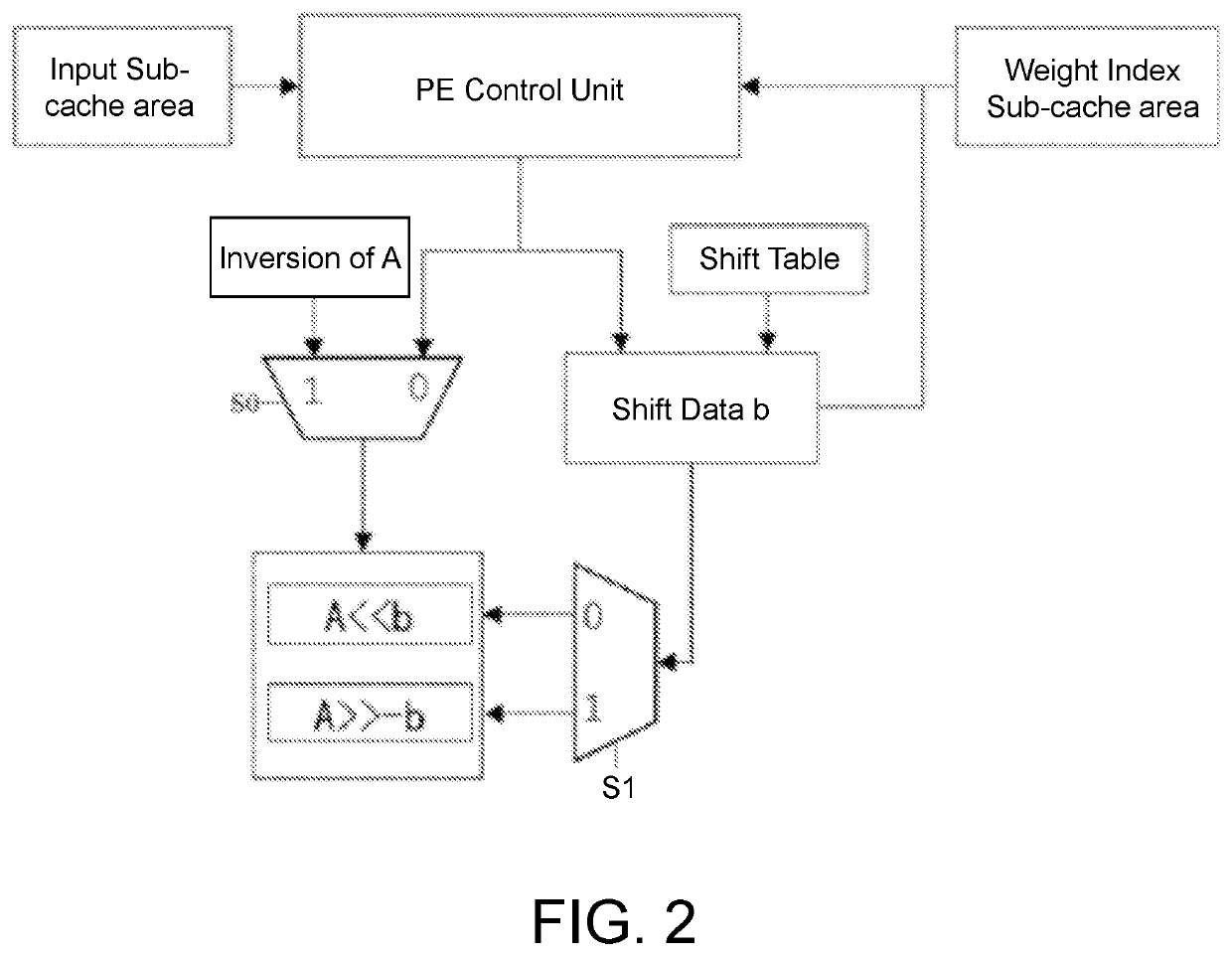

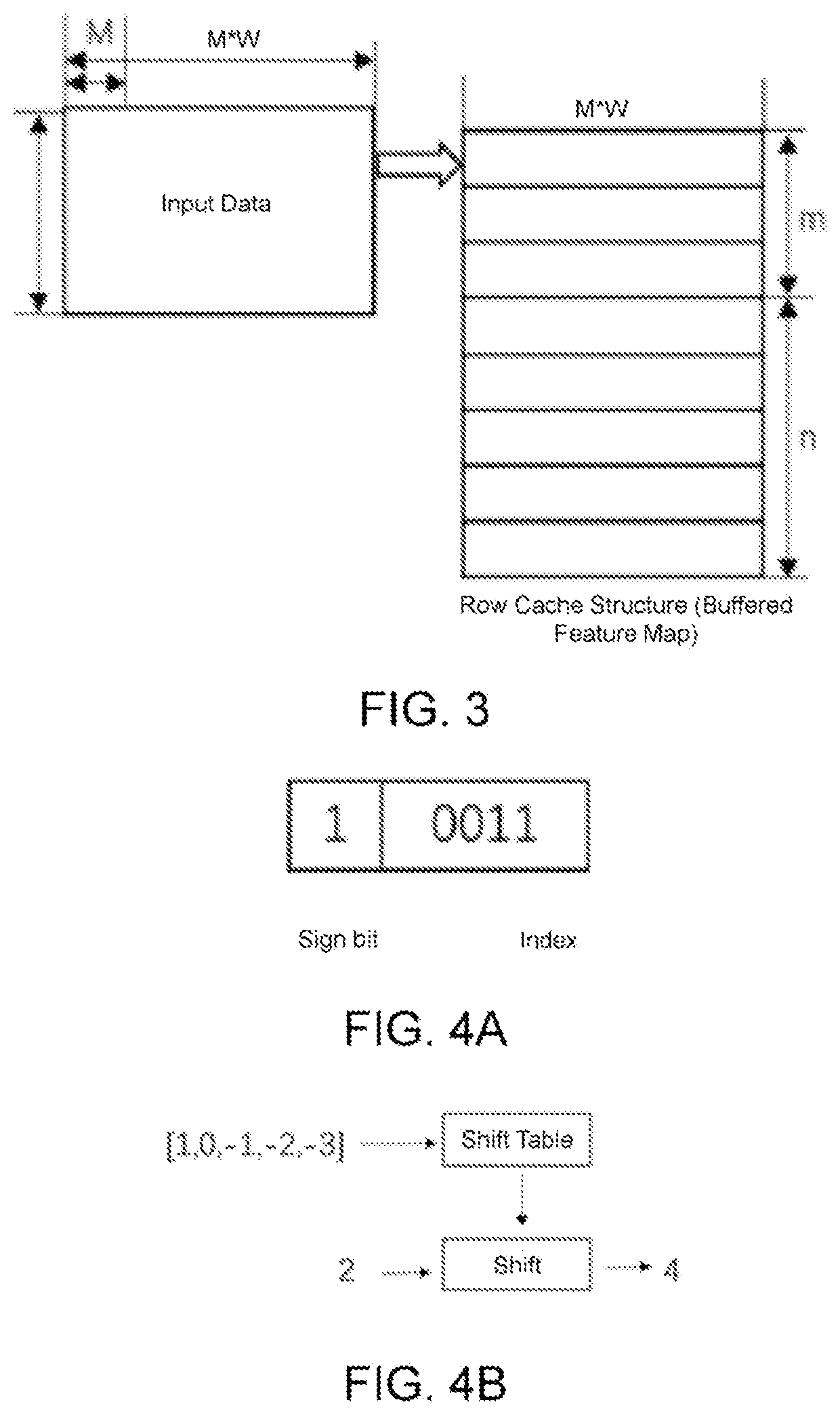

Deep neural network hardware accelerator based on power exponential quantization

PendingUS20210357736A1Lower requirementImprove computing efficiencyResource allocationDigital data processing detailsParallel computingNeural network hardware

A deep neural network hardware accelerator comprises: an AXI-4 bus interface, an input cache area, an output cache area, a weighting cache area, a weighting index cache area, an encoding module, a configurable state controller module, and a PE array. The input cache area and the output cache area are designed as a line cache structure; an encoder encodes weightings according to an ordered quantization set, the quantization set storing the possible value of the absolute value of all of the weightings after quantization. During the calculation of the accelerator, the PE unit reads data from the input cache area and the weighting index cache area to perform shift calculation, and sends the calculation result to the output cache area. The accelerator uses shift operations to replace floating point multiplication operations, reducing the requirements for computing resources, storage resources, and communication bandwidth, and increasing the calculation efficiency of the accelerator.

Owner:SOUTHEAST UNIV

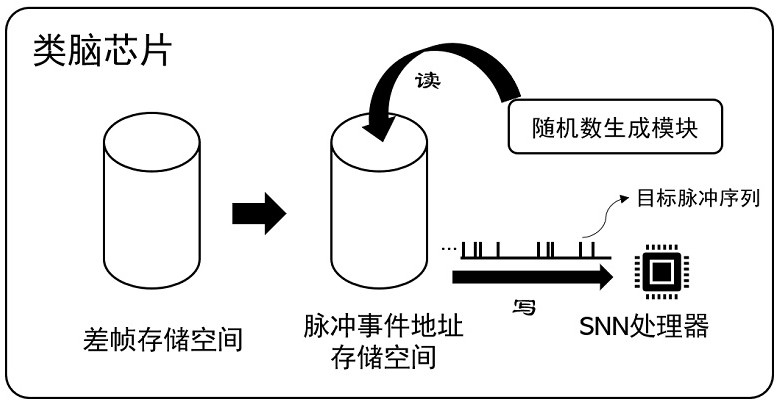

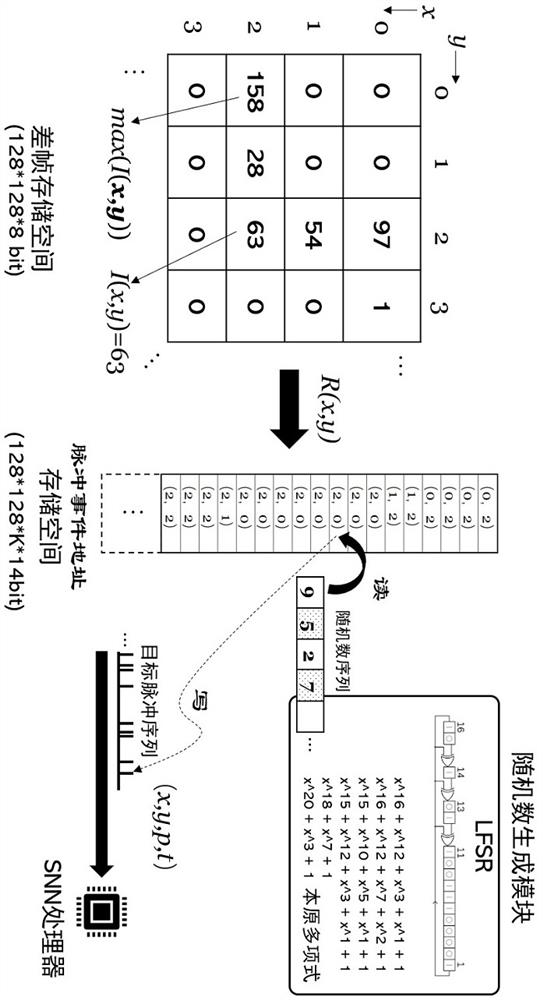

Pulse sequence randomization method and device, brain-like chip and electronic equipment

ActiveCN114495178AGood randomizationReduce hardware resource consumptionBiometric pattern recognitionNeural architecturesEmbedded systemImage sensor

The invention relates to a pulse sequence randomization method and device, a brain-like chip and electronic equipment. In order to convert an image output by a frame image sensor or an environment signal collected by the sensor into a randomized target pulse sequence suitable for being processed by a pulse neural network processor, a pulse event address and a pulse event number are stored; and reading the corresponding pulse event address or the number of pulse events according to a random number generation module, thereby generating a target pulse sequence formed by the corresponding pulse events. The method has the technical effects of low hardware resource consumption, good randomization effect, contour enhancement and background noise suppression, and provides a new technical path for generating a pulse sequence with biological characteristics. The method is suitable for the field of brain-like chips.

Owner:深圳时识科技有限公司 +1

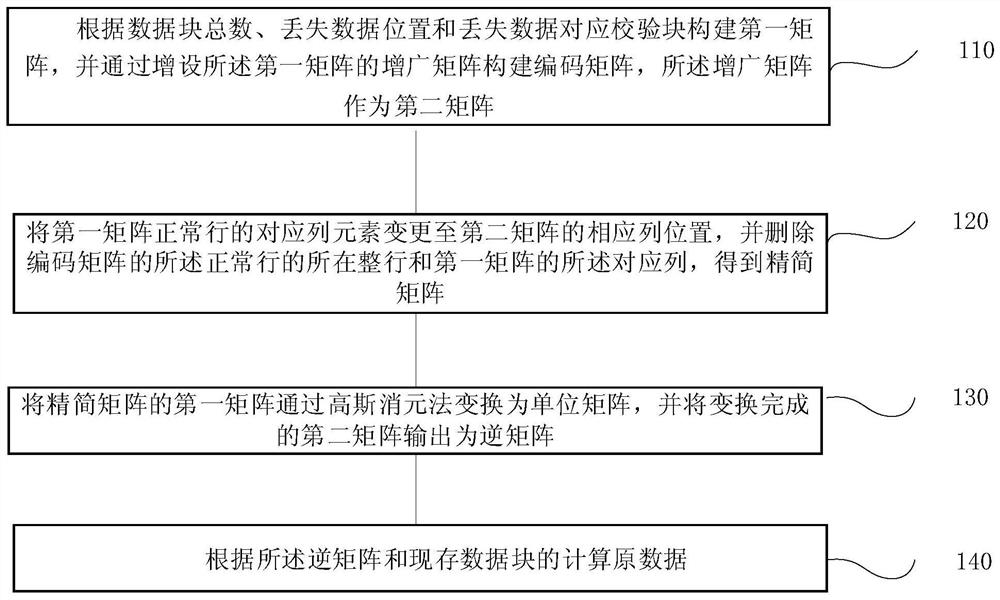

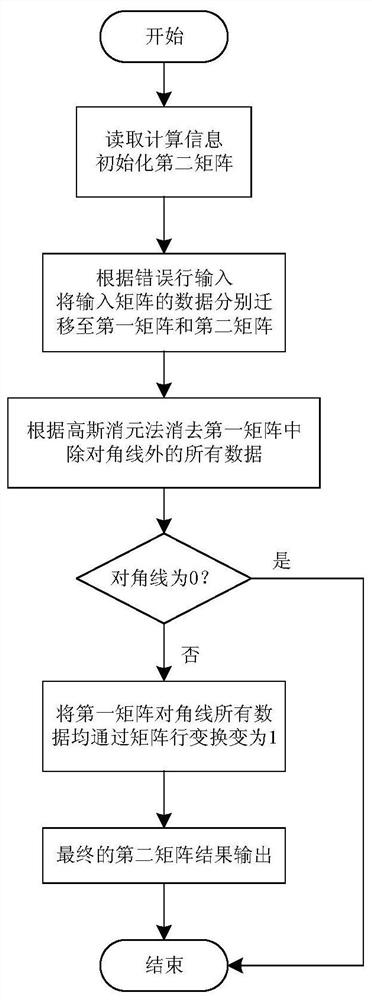

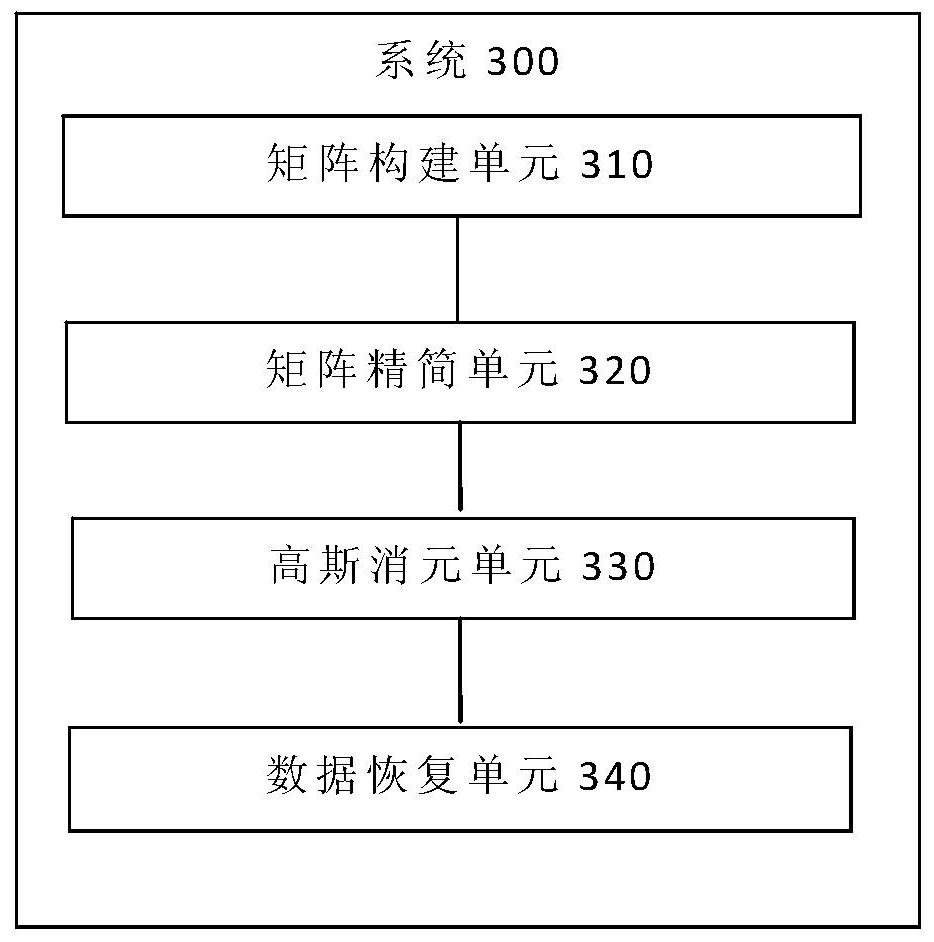

Lost data recovery method and system based on erasure code, terminal and storage medium

PendingCN111858157AReduce calculation stepsReduce hardware resource consumptionRedundant data error correctionRedundant operation error correctionData locationTheoretical computer science

The invention provides a lost data recovery method and system based on erasure codes, a terminal and a storage medium, and the method comprises the steps of constructing a first matrix according to the total number of data blocks, the position of lost data and a check block corresponding to the lost data, constructing a coding matrix through adding an augmented matrix of the first matrix, and enabling the augmented matrix to serve as a second matrix; changing the corresponding column elements of the normal row of the first matrix to the corresponding column positions of the second matrix, anddeleting the whole row where the normal row of the coding matrix is located and the corresponding column of the first matrix to obtain a simplified matrix; converting the first matrix of the simplified matrix into a unit matrix through a Gaussian elimination method, and outputting the converted second matrix as an inverse matrix; and calculating original data according to the inverse matrix and the existing data block. According to the invention, the calculation complexity of the Gaussian elimination method is reduced, the calculation performance is improved, the number of GF dividers used inthe RS erasure decoding inverse matrix calculation process is reduced, the consumption of hardware resources is reduced to a greater extent, and the development cost is saved.

Owner:SUZHOU LANGCHAO INTELLIGENT TECH CO LTD

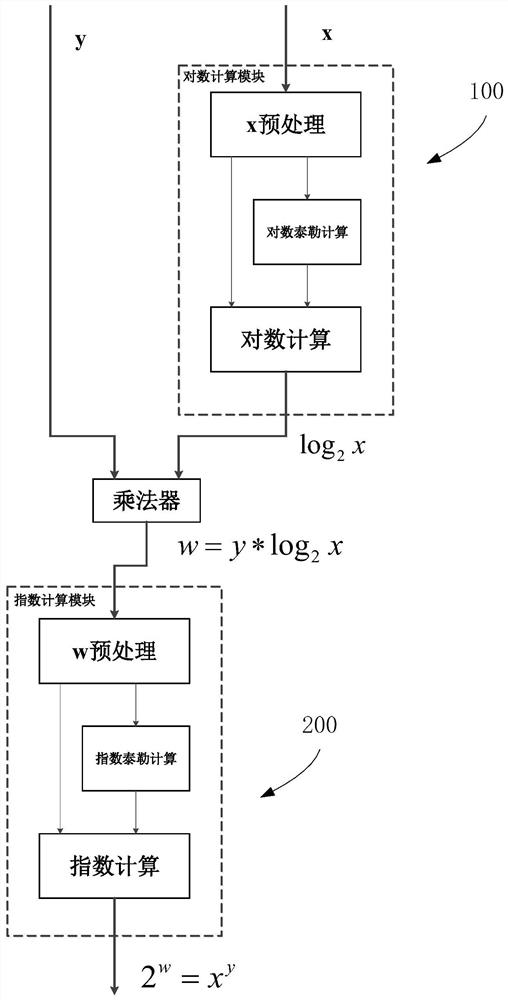

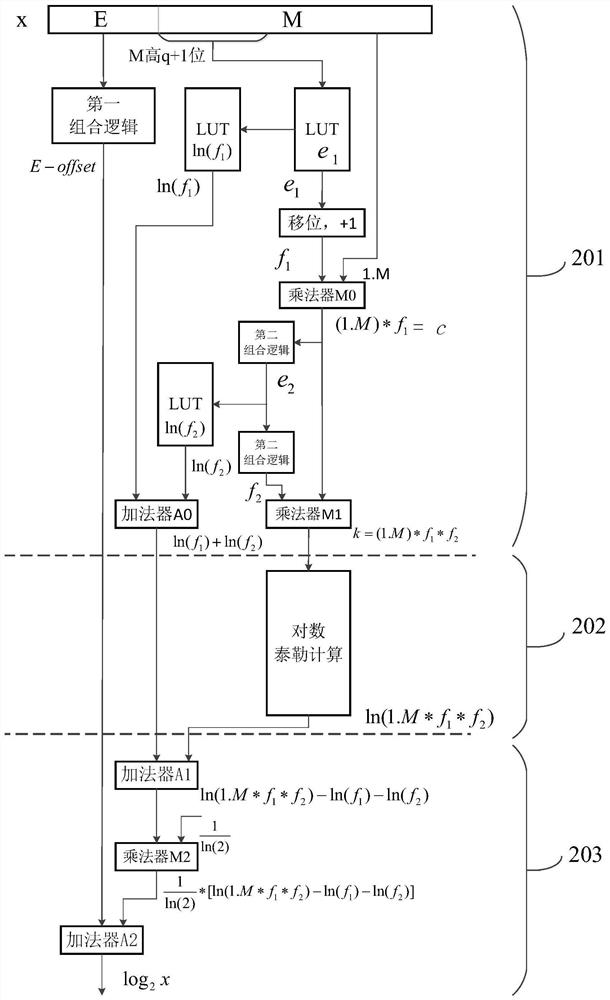

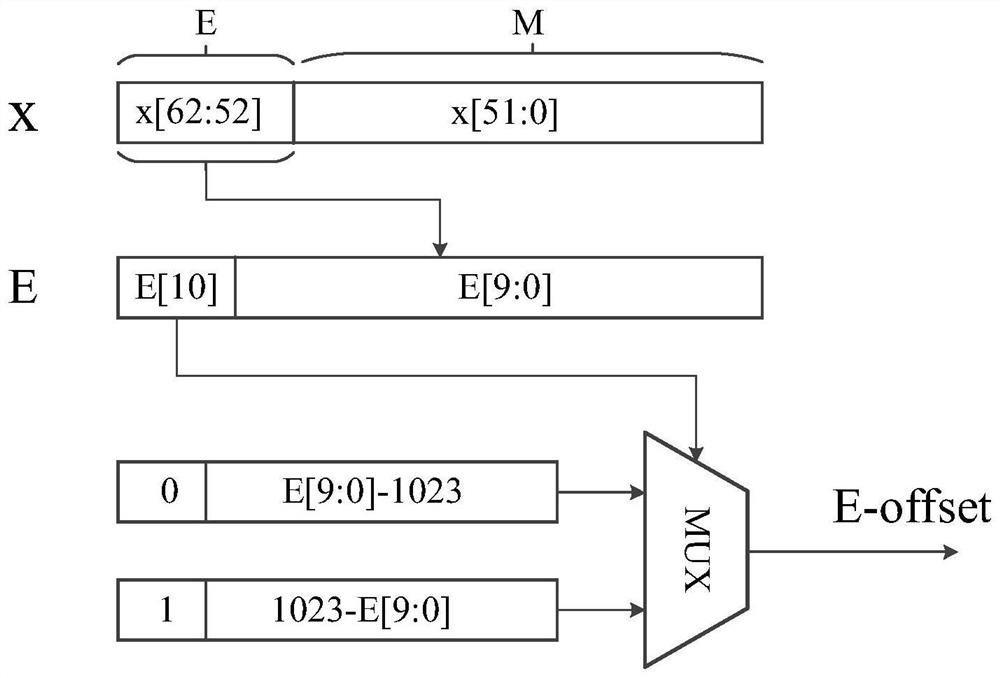

Hardware operation circuit for calculating Power function and data processing method

PendingCN114860193AExtend the calculation rangeReduce overheadDigital data processing detailsEnergy efficient computingAlgorithmComputer engineering

The invention discloses a hardware operation circuit for calculating a Power function and a data processing method, and the hardware operation circuit comprises a logarithm calculation module, a multiplication module and an index calculation module. The logarithm calculation module is configured to generate a first intermediate parameter according to the order code of the first parameter, calculate a second intermediate parameter by adopting a table look-up and logarithm Taylor series expansion mode according to the mantissa of the first parameter, and generate a logarithm calculation result according to the first intermediate parameter and the second intermediate parameter; the multiplication module is used for calculating a product of the logarithm calculation result and a second parameter, and recording the product as a multiplication calculation result; and the index calculation module is configured to perform index operation according to the multiplication calculation result of the multiplication module to generate Power function operation results of the first parameter and the second parameter. According to the technical scheme, the hardware operation circuit of the Power function is optimized, so that the hardware operation circuit can provide high calculation precision, support a wider data range and reduce resource occupation.

Owner:HEFEI UNIV OF TECH

Method for improving preprocessing part in low density check code encode realization

InactiveCN1738209AReduce hardware complexityReduce hardware resource consumptionError correction/detection using multiple parity bitsComputer architectureResidual matrix

Disclosed a method for improving the pre-processing part of the coding realization of low-density check code belongs to the coding technique field. First, try to row-deleted of check matrix of said low-density check code to reach the maximum lower triangular submatrix; the row-delete is operated on partial row vectors of first layer of layered check matrix with the diagonalization operation; secondly, if the number of deleted rows in first layer is wrong, the line whose weight is one can not be find in left matrix formed by the rows and lines without diagonalization after the first diagonalization operation, and the diagonalization operation will be stopped. So the row-delete is needed to delete more row vectors in the first layer until the avalanche effect, which means the left matrix reaches the full diagonalization. Actually, it is a kind of adephagia method, which can control the key parameter at least to reduce the consumption of hardware source of relative layered low-density check code coder.

Owner:SHANGHAI JIAO TONG UNIV

Parallel scaling engine for multi-view 3DTV display and method thereof

ActiveUS9924153B2Save resourcesImprove system resource utilizationGeometric image transformationSteroscopic systemsViewpointsFloating point

A parallel synchronous scaling engine for multi-view 3D display and a method thereof are provided, wherein selection and combination calculation are provided to an interpolation pixel window, then interpolation calculation is provided to a combined interpolation pixel window of a combined view field, calculation results are directly displayed on a display terminal. That is to say, interpolation is originally provided before stereoscopic pixel rearrangement, which is now improved, in such a manner that screening and combination of pixel points is provided before interpolation calculation. According to the present invention, computation and memory resource is greatly saved. The method is suitable to be implemented by hardware, for satisfying various numbers of viewpoints and interpolation algorithm, and being compatible with multi-view 3D display with the integrated and floating-point pixel arrangement, wherein the computation resource does not need to be increased with increasing of the viewpoints.

Owner:XI AN JIAOTONG UNIV

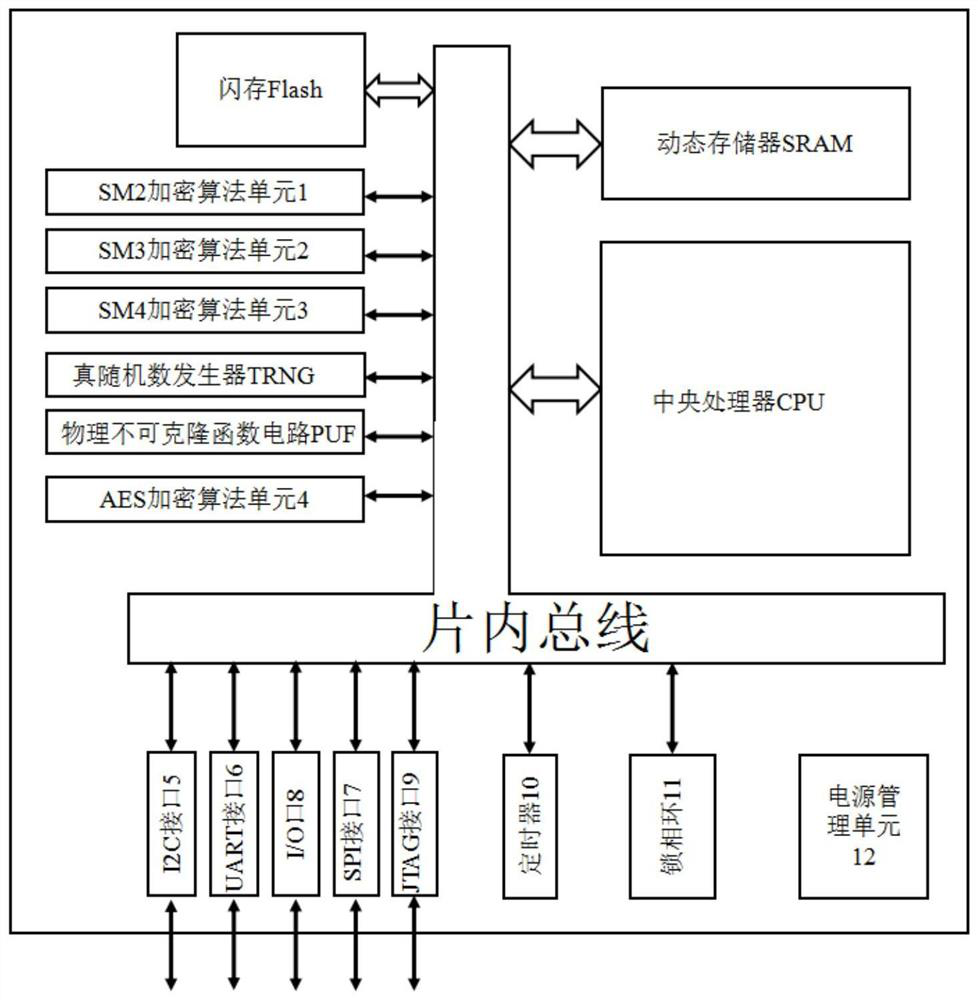

Internet of things information security chip

ActiveCN109818745BReduce areaPrevent copyingEncryption apparatus with shift registers/memoriesPublic key for secure communicationPhysical unclonable functionInformation security

The invention discloses an Internet of Things information security chip, comprising a central processing unit, a dynamic memory, a flash memory, an SM2 encryption algorithm unit, an SM3 encryption algorithm unit, an SM4 encryption algorithm unit, an AES encryption algorithm unit, a true random Number generator, physical unclonable function circuit, I2C interface, UART interface, SPI interface, I / O port, JTAG interface and timer; true random number generator is used to generate true random numbers, and physical unclonable function circuit is used for chip authentication and key generation, when the key needs to be used, the true random number generated by the true random number generator is input to the physical unclonable function circuit through the on-chip bus, and the physical unclonable function circuit outputs a unique response sequence, the response sequence is key. The encryption and decryption operation speed of the invention is faster, the consumption of hardware resources and power consumption is less, the key cannot be copied and stolen, and the security and anti-counterfeiting level is higher.

Owner:佛山芯珠微电子有限公司

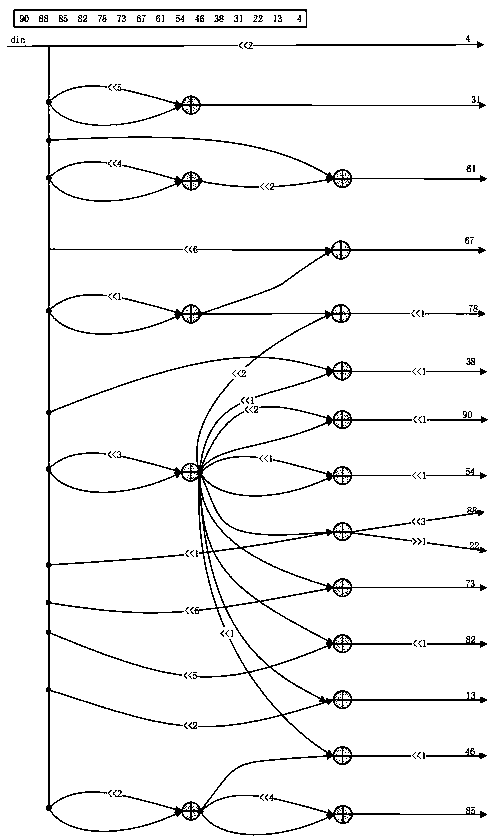

DCT/IDCT multiplier circuit optimization method and application

ActiveCN110737869AReduce hardware resource consumptionImprove computing efficiencyComputation using non-contact making devicesDigital video signal modificationDigital videoEngineering

The invention discloses a DCT / IDCT multiplier circuit optimization method and application, and relates to the technical field of digital video coding and decoding. A DCT / IDCT device used under an HEVCstandard comprises an optimization processing module which is used for collecting a row number contained in each type and elements in the corresponding set A according to the obtained information ofthe set A and the type N, enabling all elements in the set A corresponding to each type to serve as a group, and sequentially carrying out subtraction optimization and maximum correlation optimizationon the elements in the type, wherein maximum correlation optimization can take the process variables as related items when the process variables in a multiplication circuit can be used to reduce thetotal number of summators when any element in a group where the element is located is achieved when implementing judging of elements, and for all elements of each type, acquires the related item withthe highest occurrence frequency to serve as the maximum related item to achieve the related elements. According to the DCT / IDCT multiplier circuit optimization method, the hardware resource consumption is effectively reduced, and the operation efficiency is improved.

Owner:MOLCHIP TECH (SHANGHAI) CO LTD

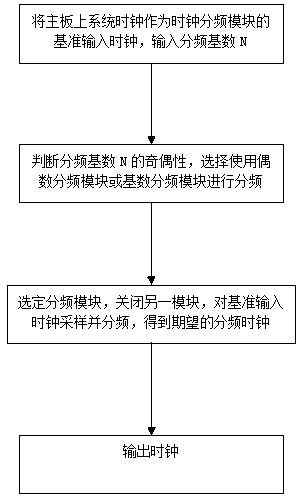

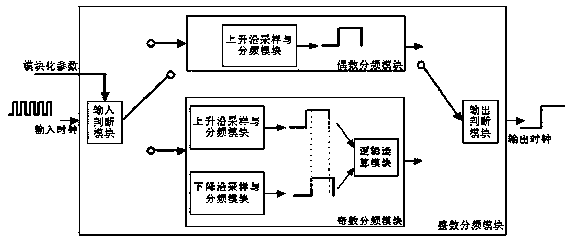

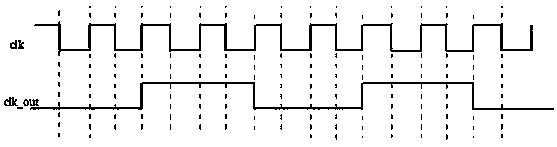

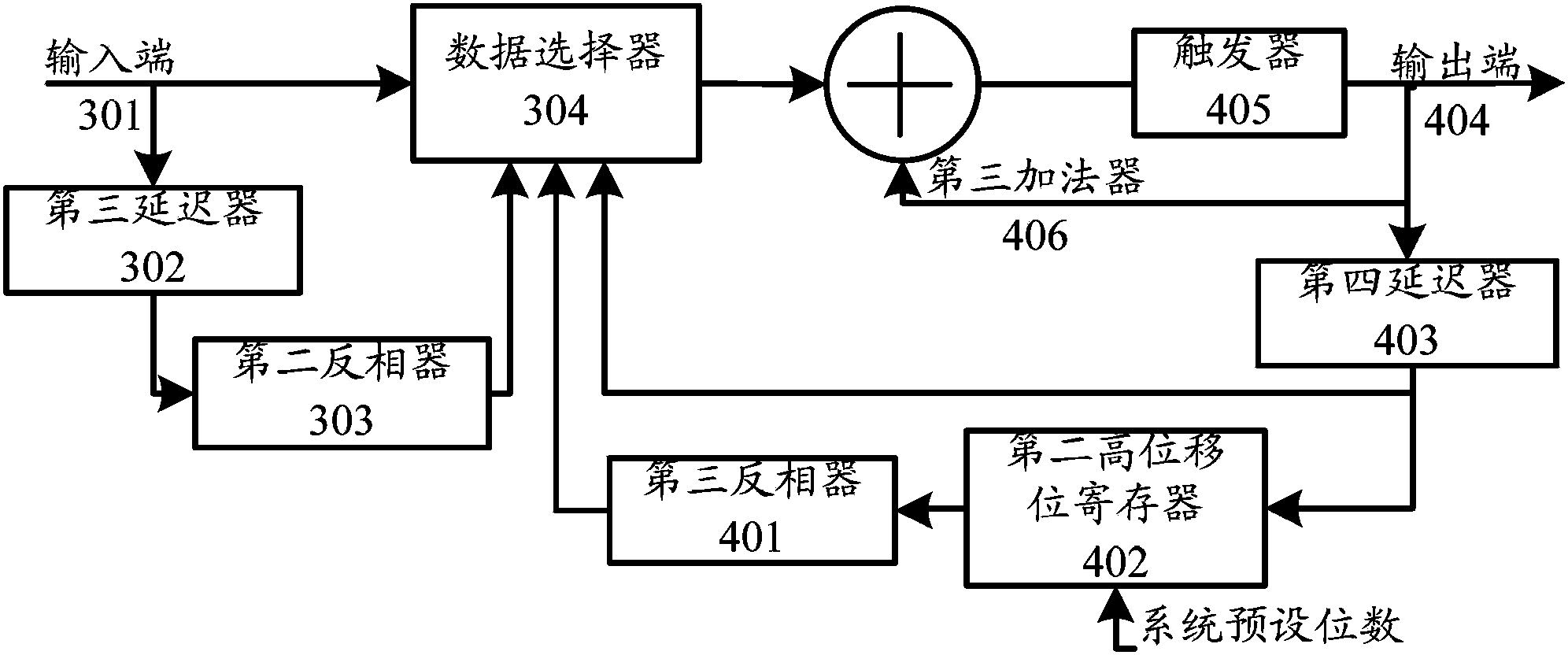

CPLD/FPGA-based clock frequency division module design method

InactiveCN107563020AReduce hardware resource consumptionOvercoming large hardware resource requirementsPulse automatic controlSpecial data processing applicationsDesign methodsMotherboard

The invention discloses a CPLD / FPGA-based clock frequency division module design method. The method comprises the following steps of 1: taking a system clock on a mainboard as a reference input clockof a clock frequency division module, and inputting a frequency division cardinal number N; 2: judging the parity of the frequency division cardinal number N, selectively using an even number frequency division module or a cardinal number frequency division module to perform frequency division, selecting the frequency division module, and turning off the other module; 3: performing sampling and frequency division on the reference input clock to obtain an expected frequency division clock; and 4: outputting the clock. The problems of high consumption of instantiated PLL IP core hardware resources in a CPLD / FPGA and non 50% duty ratio of odd number frequency division are solved.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

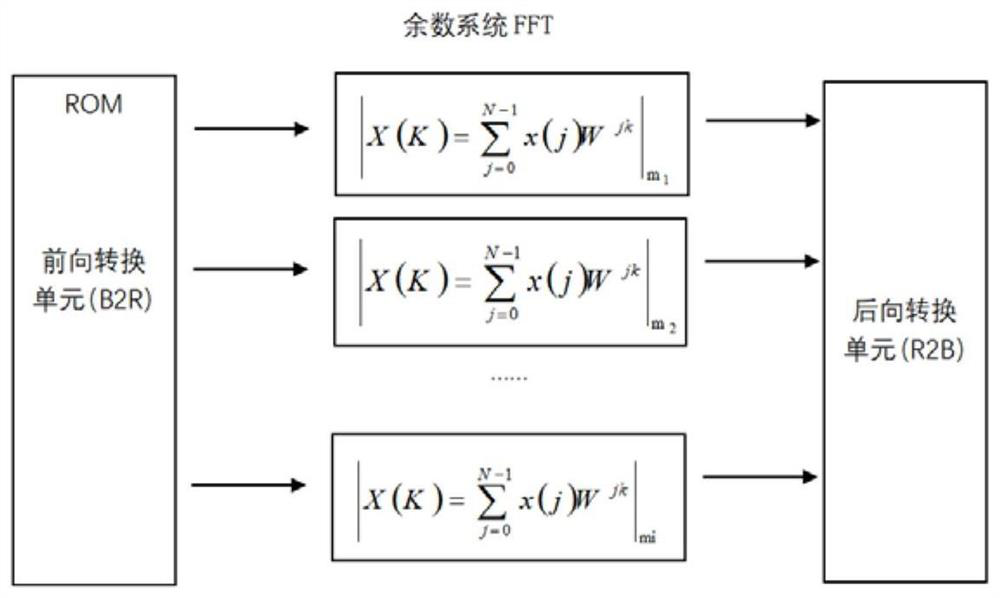

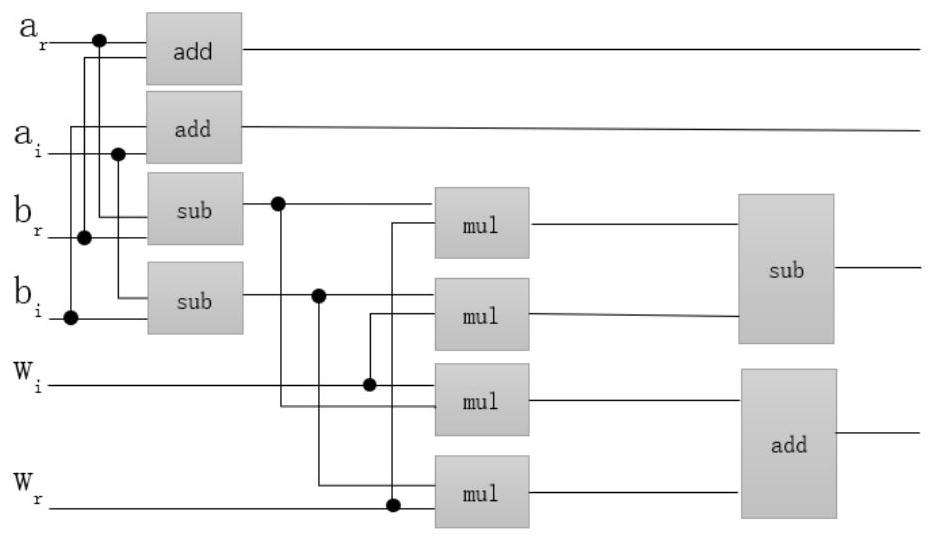

FFT system based on RNS dynamic range expansion

PendingCN113378110AReduce in quantityReduce occupancyComputations using residue arithmeticComplex mathematical operationsFast Fourier transformBinary multiplier

The invention discloses an FFT (Fast Fourier Transform) system based on RNS dynamic range expansion. The system is applied to the field of digital circuit design optimization and aims at solving the problem of inevitable complicated multiplier in the existing FFT algorithm. The FFT system based on the RNS comprises a forward conversion unit, an operation unit and a backward conversion unit, the forward conversion unit converts a binary number into a remainder field based on the determined remainder base; the operation unit adopts butterfly operation channels with the number equal to that of the remainder base modulus, and each parallel channel carries out independent modular addition and modular multiplication operation; and the backward conversion unit converts the output result of the operation unit to a binary number field. By the adoption of the FFT system, not only can the circuit area of a system circuit be reduced, but also occupied resources can be reduced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

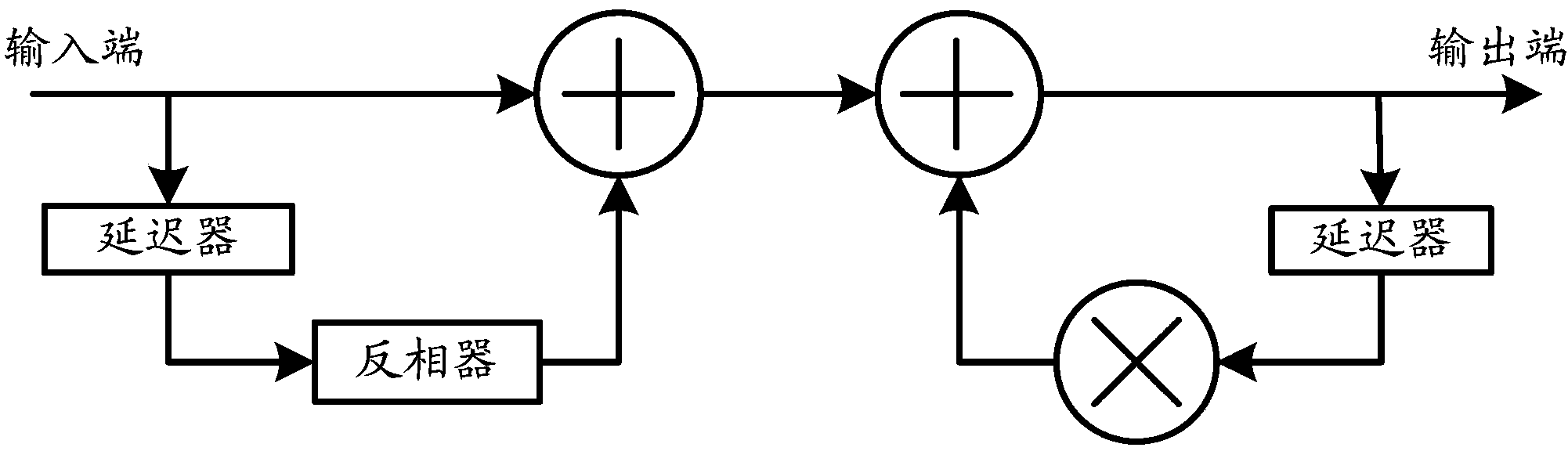

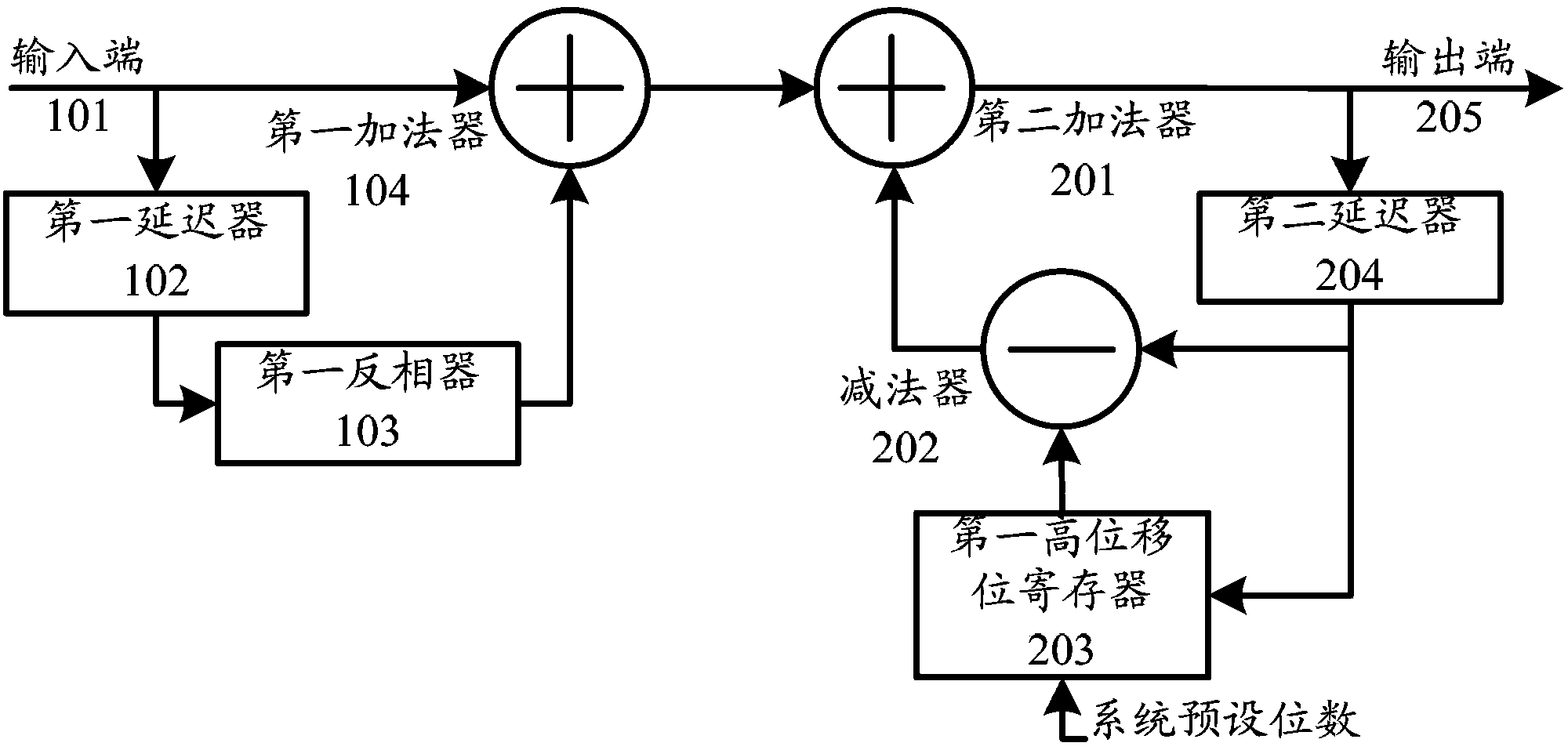

Direct-current filter circuit for realizing ASIC (Application Specific Integrated Circuit) audio processing function

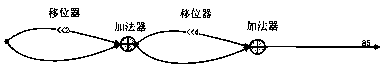

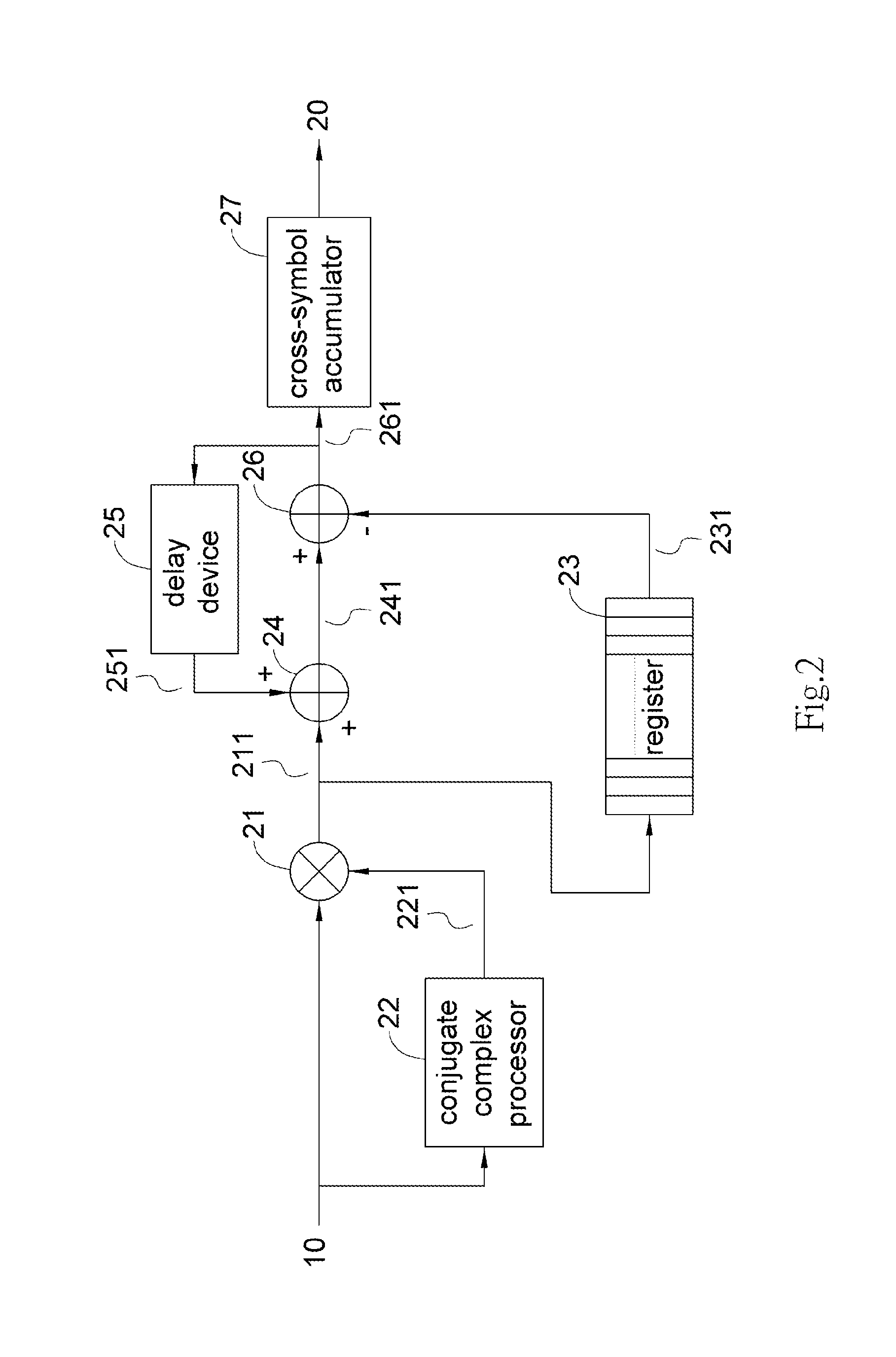

InactiveCN104218918AReduce hardware resource consumptionSimple circuit structureDigital technique networkVIT signalsAudio signal

The invention relates to a direct-current filter circuit for realizing an ASIC (Application Specific Integrated Circuit) audio processing function. The direct-current filter circuit comprises an input function processing module and an output function feedback module, wherein the input function processing module is used for performing delay phase reversal on an input signal of the direct-current filter circuit and outputting the input signal which is subjected to delay phase reversal together with an input signal of the direct-current filter circuit; and the output function feedback module is used for intercepting a high-order field from an output delay signal of the direct-current filter circuit, performing phase reversal on the output delay signal, and adding the output delay signal which is subjected to phase reversal with an output signal of the input function processing module and the output delay signal of the direct-current filter circuit. Through adoption of the direct-current filter circuit for realizing the ASIC audio processing function disclosed by the invention, a direct-current component in an ASIC audio signal can be removed; moreover, a multiplier is optimized, so that the hardware resource consumption during processing is lowered greatly, and resources accounting for 70 percent of total resources are reduced below 30 percent; and the circuit is simple and practical in structure, has more stable working performance, and is wider in application range.

Owner:CRM ICBG (WUXI) CO LTD

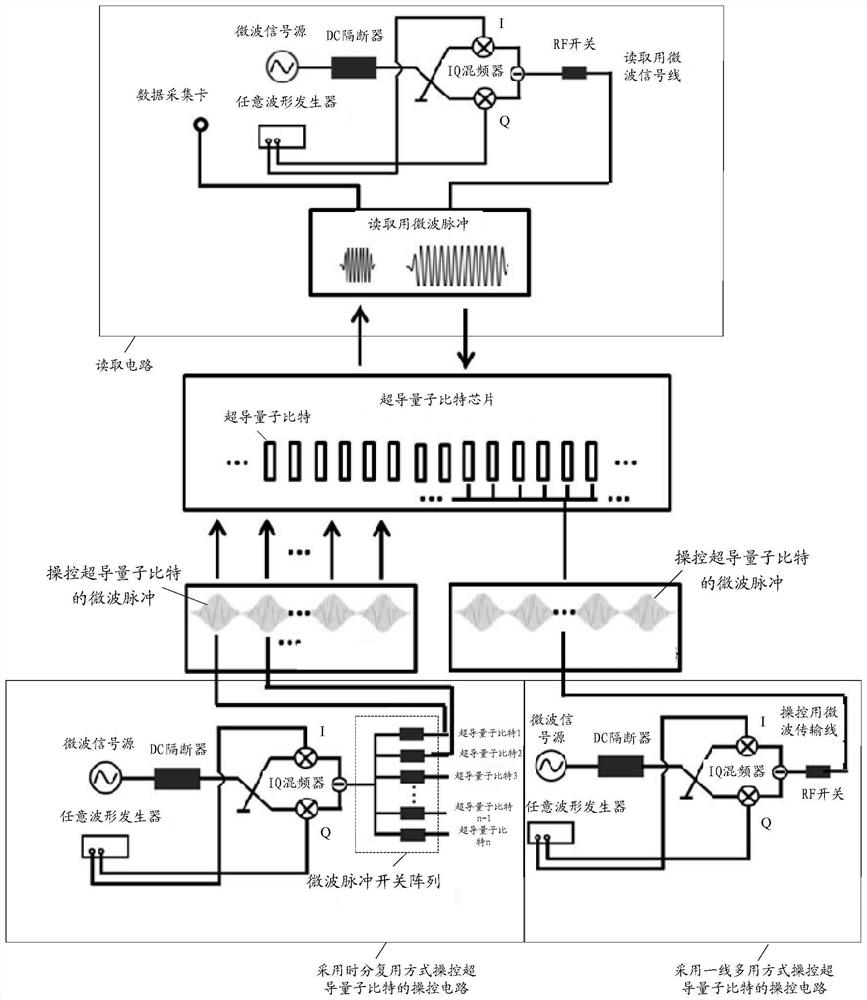

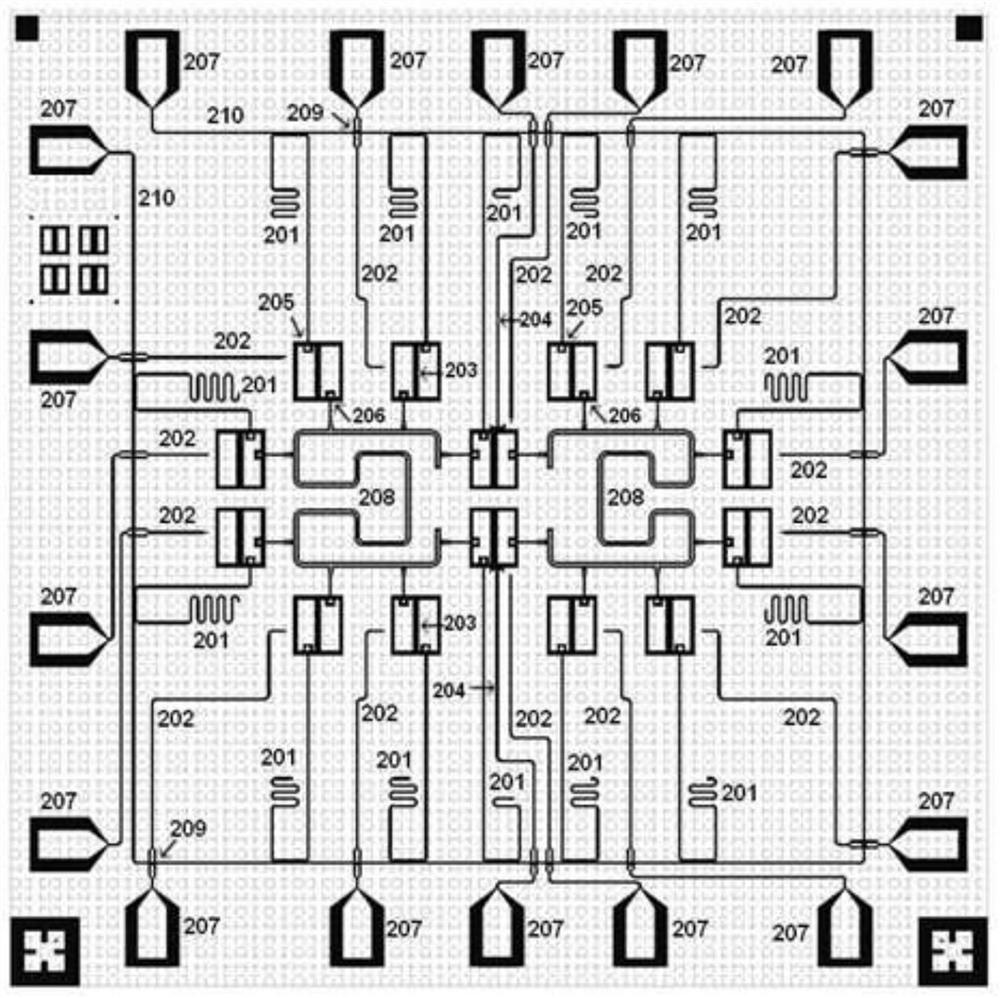

a quantum computer

ActiveCN109685216BReduce hardware resource consumptionReduce hardware costsQuantum computersSoftware engineeringBit array

Owner:TSINGHUA UNIV

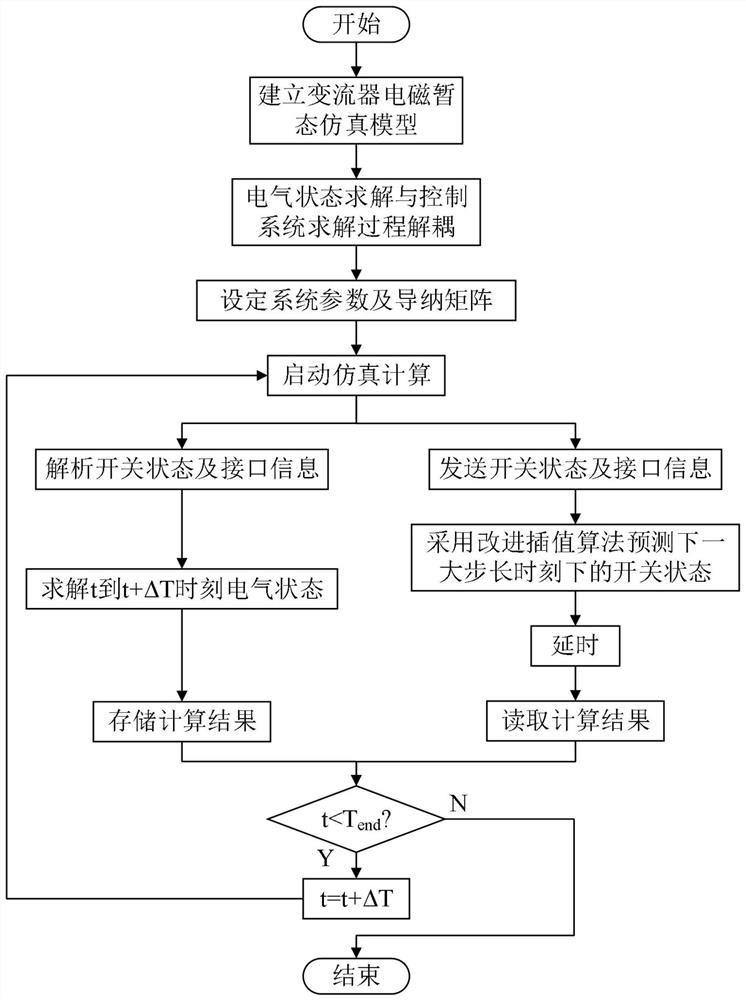

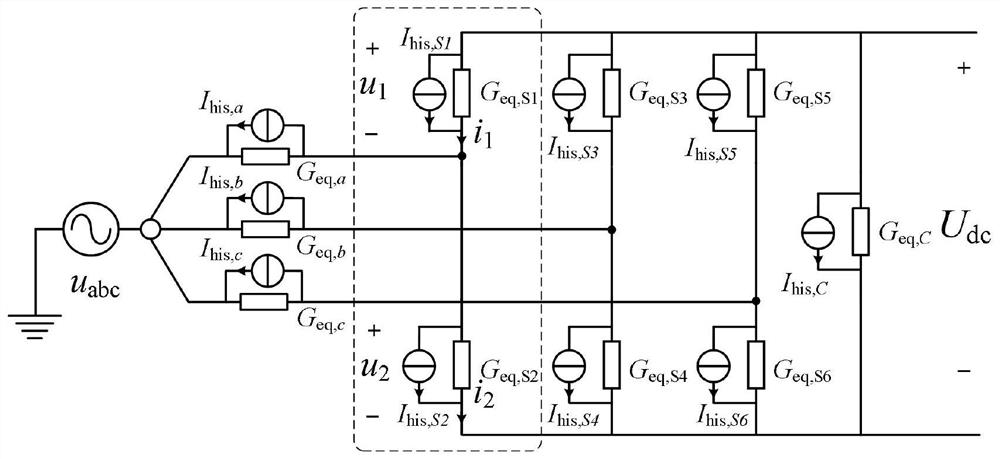

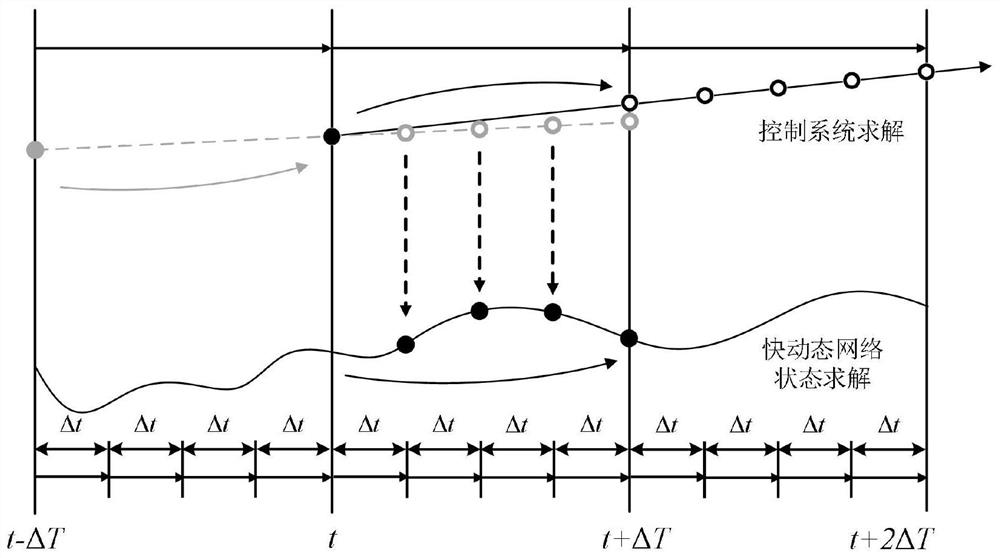

A hardware-accelerated parallel multi-rate electromagnetic transient real-time simulation method for converters

ActiveCN113359513BReduce Timing ErrorReduce hardware resource consumptionSimulator controlConvertersComputation process

The invention relates to the technical field of power system simulation, and discloses a hardware-accelerated parallel multi-rate electromagnetic transient real-time simulation method of a converter. Initialized parametric constant admittance model modeling; step 2 realizes the cross-platform decoupling of the converter electrical system and control system solution process; step 3 pre-stores the converter model matrix in FPGA; step 4 is on the host computer Start the parallel simulation and predict the switch state at the next big step; step 5, the FPGA side analyzes the switching state calculation result of the host computer side and solves the electrical state at the current moment in parallel with step 4; step 6, the host computer side reads the FPGA side. The electrical state solves the results and updates the simulation time. The invention is applied to the FPGA-based hardware acceleration simulation scenario of the converter model, effectively reducing the error in the multi-rate decoupling calculation process of the control system and improving the accuracy of real-time simulation.

Owner:SOUTHEAST UNIV

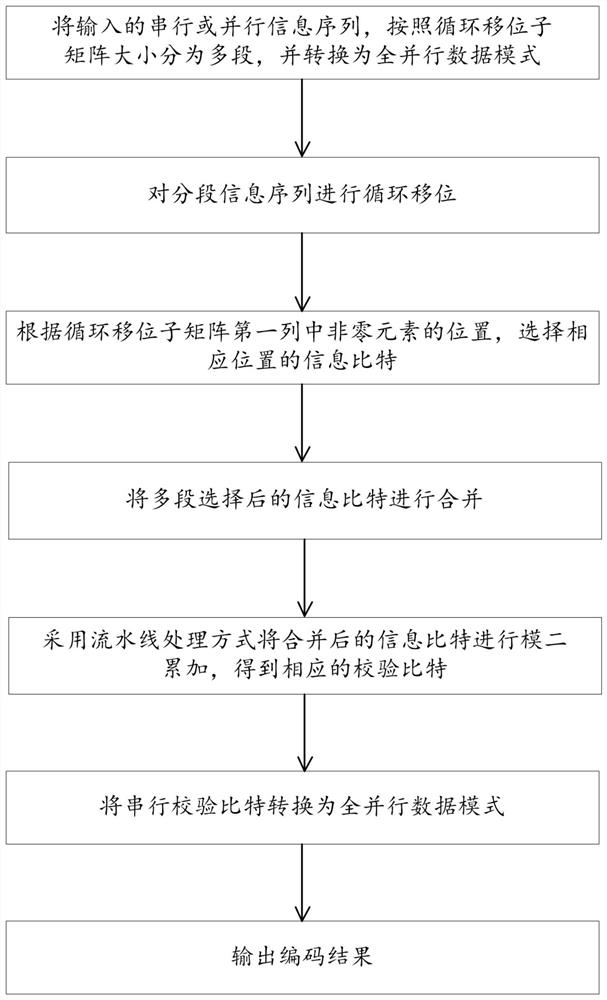

A high-energy-efficiency high-speed parallel ldpc encoding method and encoder

ActiveCN113055023BReduce operandsReduce hardware resource consumptionError correction/detection using multiple parity bitsCode conversionHigh energyParallel computing

Owner:UNIV OF SCI & TECH BEIJING

Method and apparatus for cell search and synchronization in mobile communication

ActiveUS9503996B2Smooth transmissionImprove communication qualitySynchronisation arrangementTime-division multiplexData synchronizationControl signal

The present invention provides a method and an apparatus for cell search and synchronization for subscriber stations of the Long Term Evolution (LTE) system. The invention uses primary synchronizing signal of primary synchronization code in each frame structure to establish synchronization with the base station when a subscriber station accesses the LTE network. With such synchronization between the subscriber station and the base station, control signals and transmission data may be correctly exchanged between them.

Owner:NAT TAIWAN UNIV

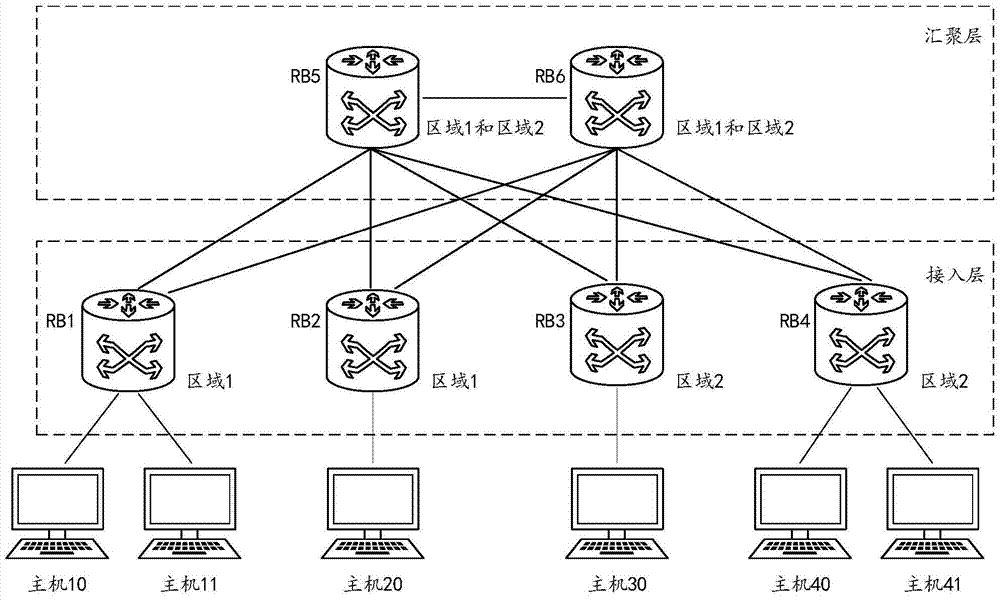

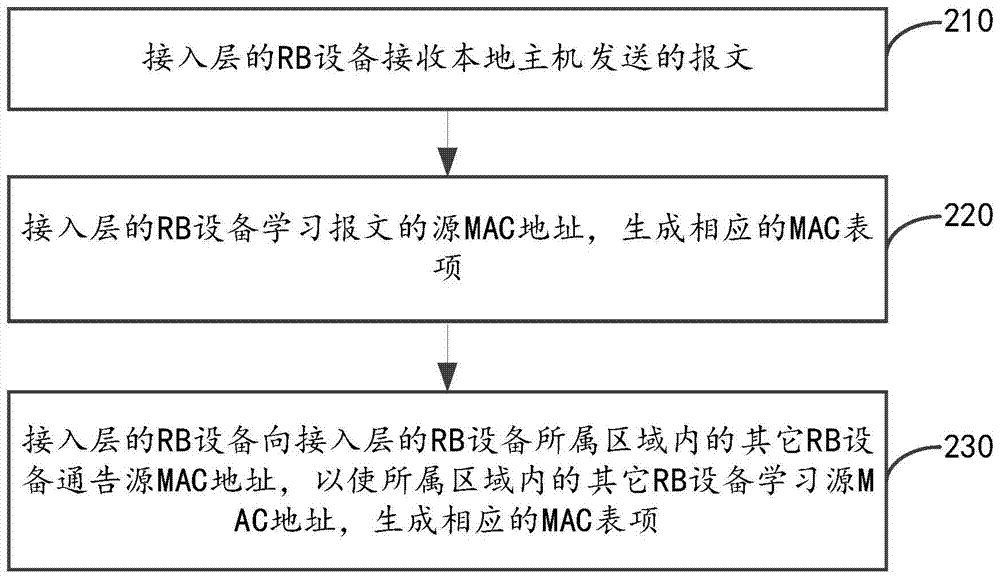

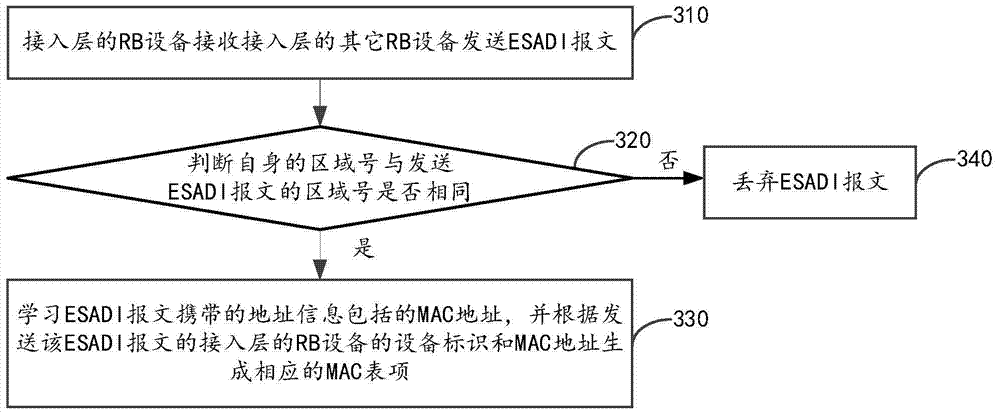

Mac address learning method and device

ActiveCN104618524BReduce hardware resource consumptionSave spaceTransmissionResource consumptionLocalhost

The present invention provides a MAC address learning method and device. The method is applied to a TRILL network. The TRILL network includes at least two areas. The RB equipment of the convergence layer in the TRILL network belongs to all areas in the at least two areas. The access layer in the TRILL network The RB devices in the TRILL network belong to one of at least two areas, and the RB devices in the TRILL network are all enabled with ESADI. The method includes: the RB device at the access layer receives the message sent by the local host; the RB device at the access layer learns the message The source MAC address of the document, generate the corresponding MAC entry; notify the source MAC address to other RB devices in the area to which the RB device of the access layer belongs, so that other RB devices in the area can learn the source MAC address and generate the corresponding MAC table item. Therefore, the present invention can save the MAC address space of the RB device at the access layer, and reduce the hardware resource consumption of the RB device at the access layer.

Owner:NEW H3C TECH CO LTD

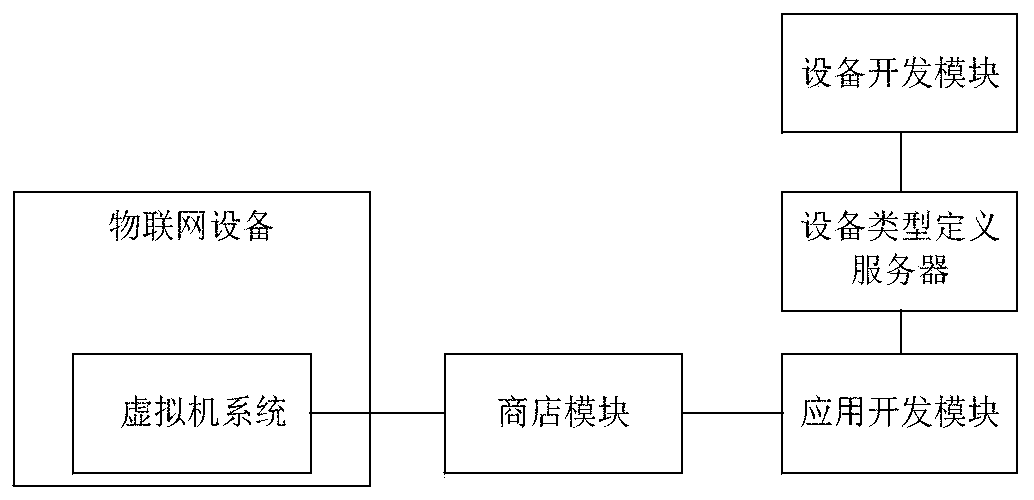

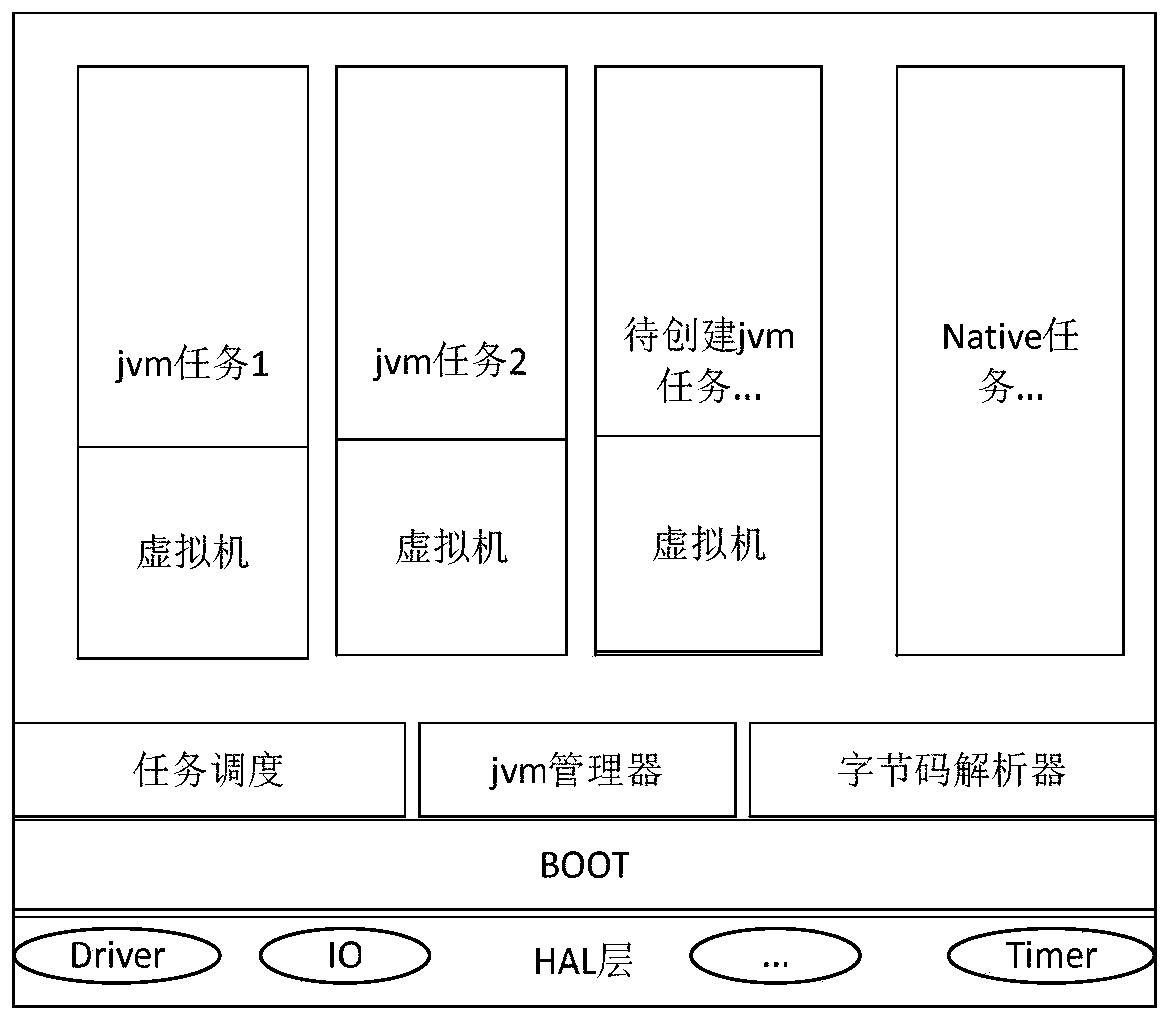

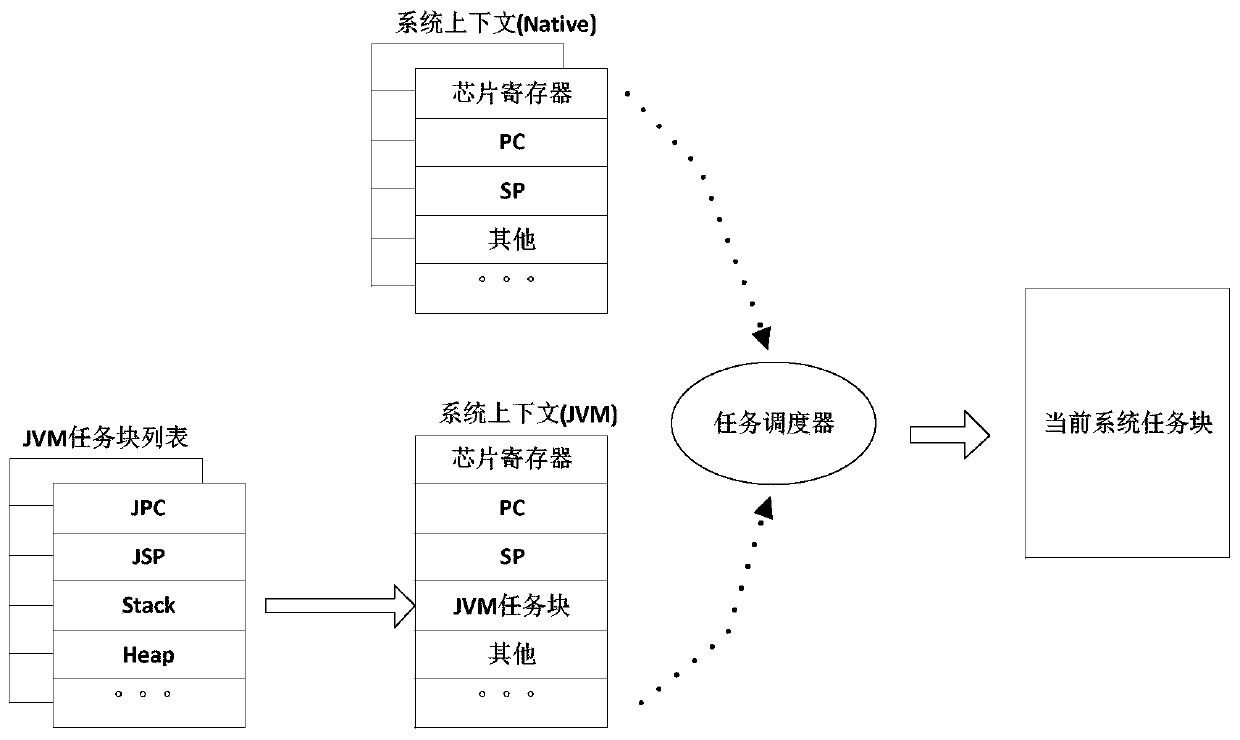

Novel Internet of Things multi-task operation system and method based on java virtual machine

PendingCN110262874AWide range of applicationsReduce hardware resource consumptionSoftware simulation/interpretation/emulationCross-platformCable television

The invention relates to a novel Internet of Things multi-task operation system and method based on a java virtual machine. The system and the method are used for implementing: a software and hardware combination technology is used on the embedded equipment to realize a small multi-task operation system. The operation system supports one or more local built-in tasks and java virtual machine tasks, and meanwhile, public and characteristic function module interfaces are established for different equipment types, so that a third party can develop a program to control equipment, and the problem of closing of Internet of Things terminal device is solved. The system has the beneficial effects that cross-platform and one-time development is realized, and the system can be operated anywhere, the application range is wide and is as small as that of a single-application intelligent card, as large as multi-application intelligent air conditioners and televisions. The consumption of hardware resources is very low, and a low-end single chip microcomputer can also meet the requirement. The cost is low, the flexibility is higher, and the system expansibility is high.

Owner:EASTCOMPEACE TECH

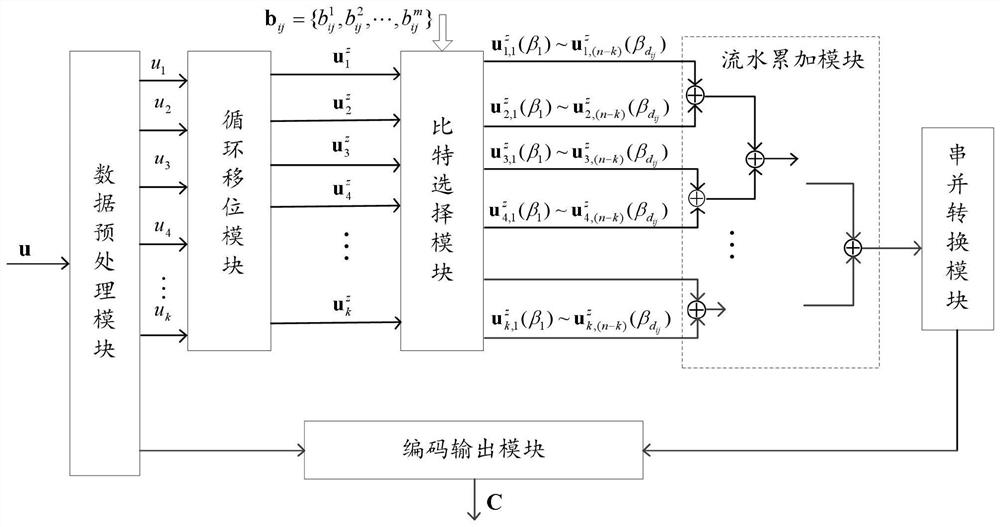

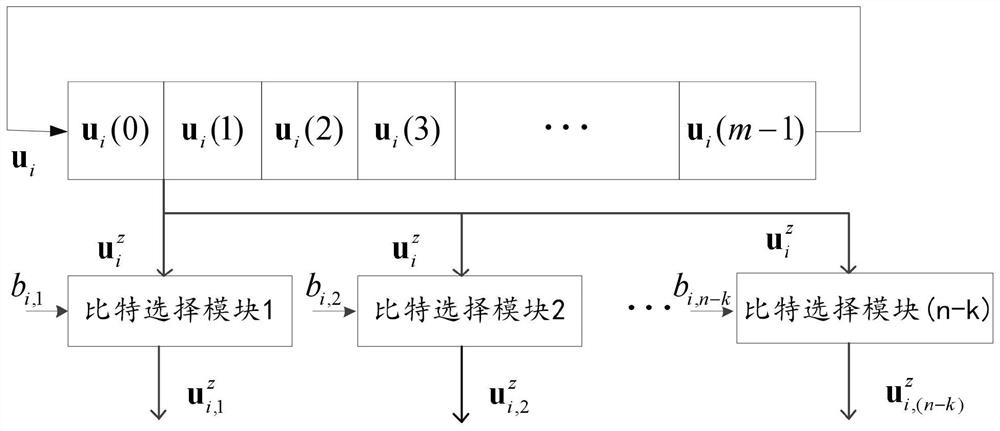

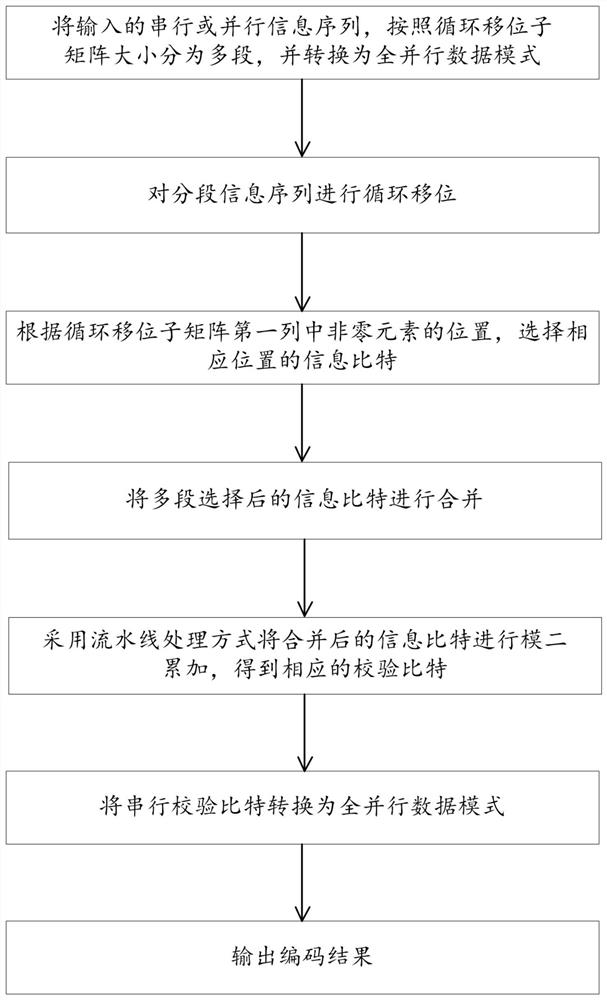

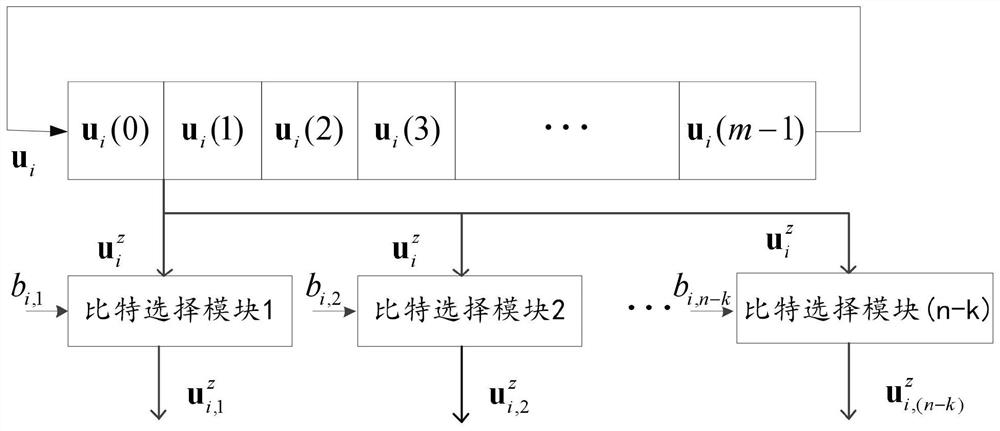

High-energy-efficiency high-speed parallel LDPC encoding method and encoder

ActiveCN113055023AReduce operandsReduce hardware resource consumptionError correction/detection using multiple parity bitsCode conversionEngineeringOperand

The invention discloses a high-energy-efficiency high-speed parallel LDPC encoding method and encoder, and the encoding method comprises the steps: dividing an input serial or parallel information sequence into multiple segments according to the size of a quasi-cyclic LDPC code cyclic shift sub-matrix, and converting the serial or parallel information sequence into a full parallel data mode; performing cyclic shift on the segmented information sequence; selecting information bits at corresponding positions according to the positions of non-zero elements in the first column of the cyclic shift sub-matrix; combining the information bits after the multiple sections of selection; carrying out modulo-two accumulation on the combined information bits by adopting a pipeline processing mode to obtain corresponding check bits; converting the serial check bits into a full parallel data mode; and outputting a coding result. According to the positions of the non-zero elements in the generated matrix, bit selection is firstly performed on the information sequence, and then coding calculation is performed, so the operation of invalid information bits can be effectively avoided, the operand required by coding calculation is reduced, and the overall hardware resource consumption of the encoder is remarkably reduced.

Owner:UNIV OF SCI & TECH BEIJING

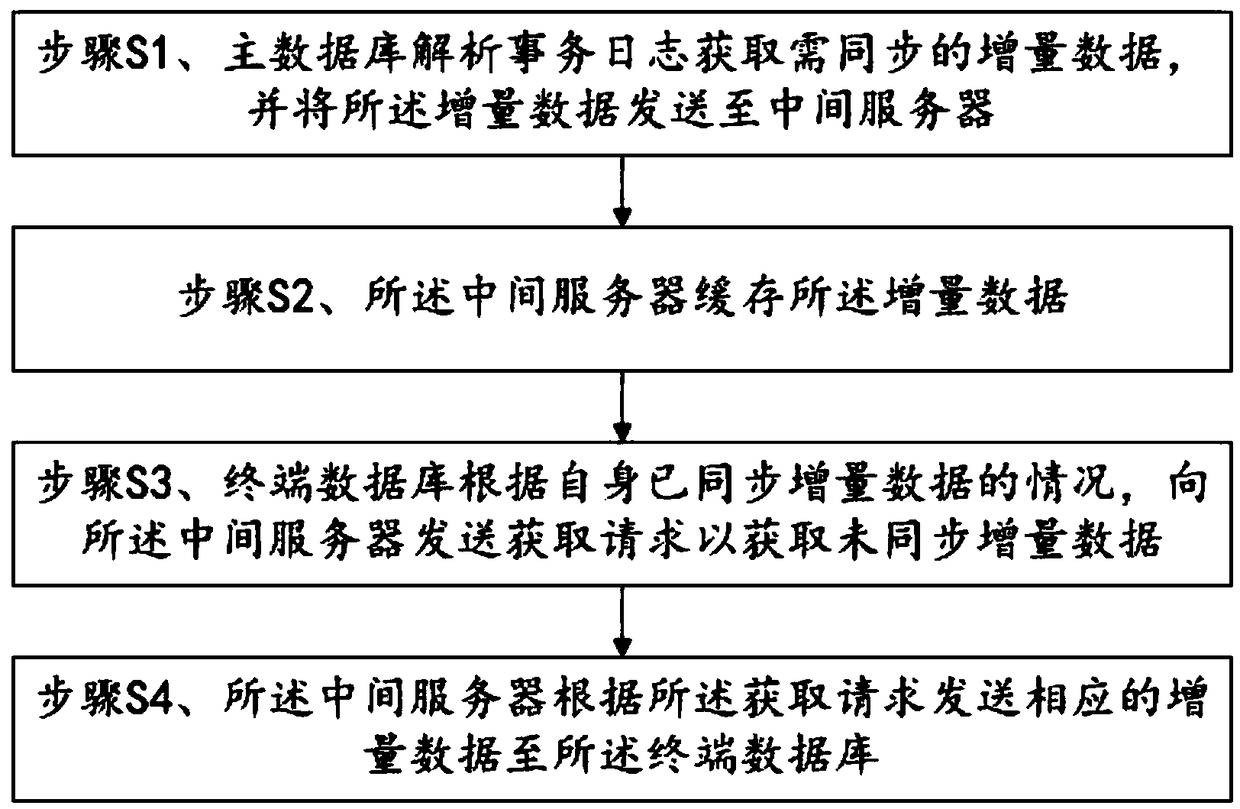

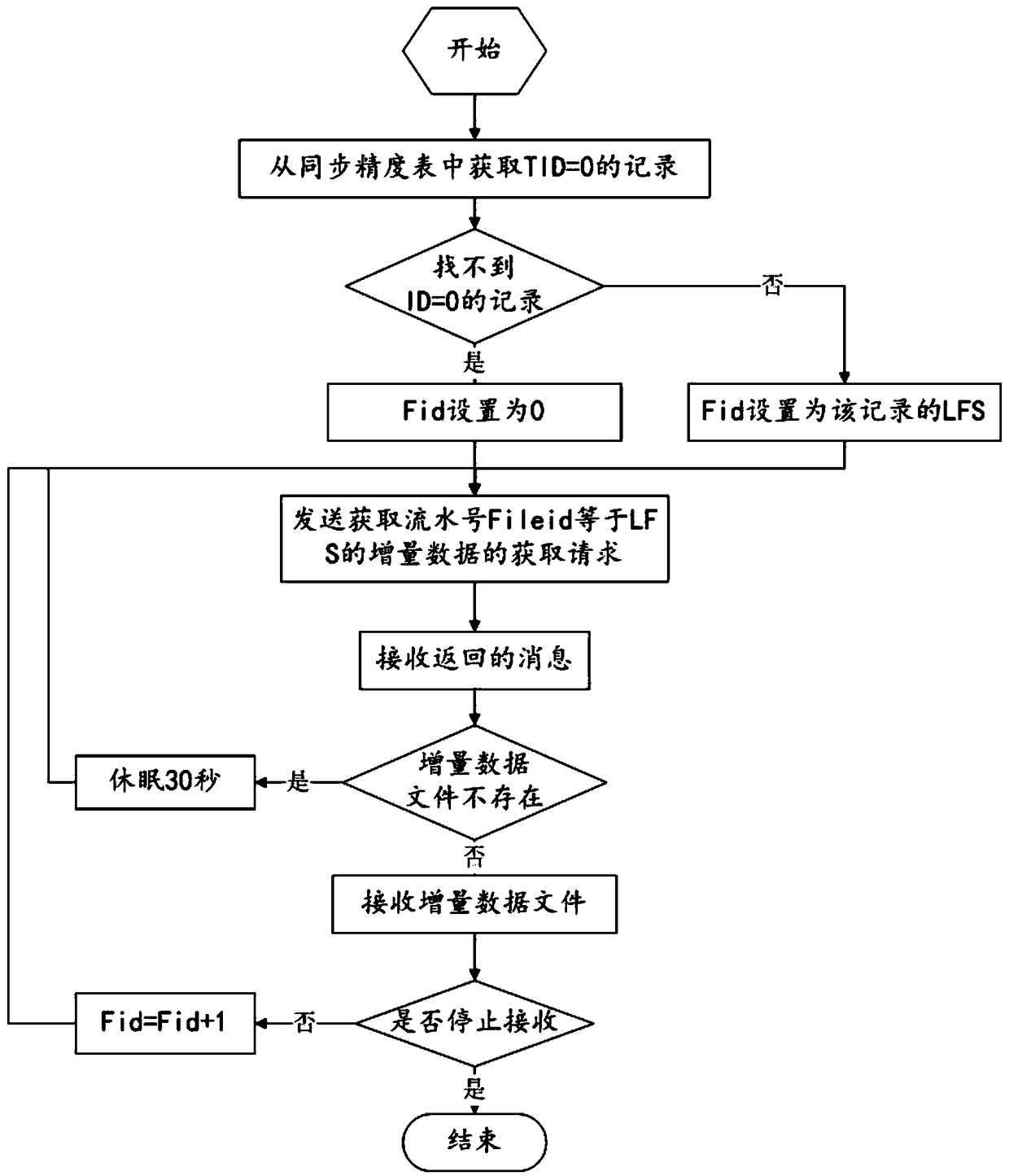

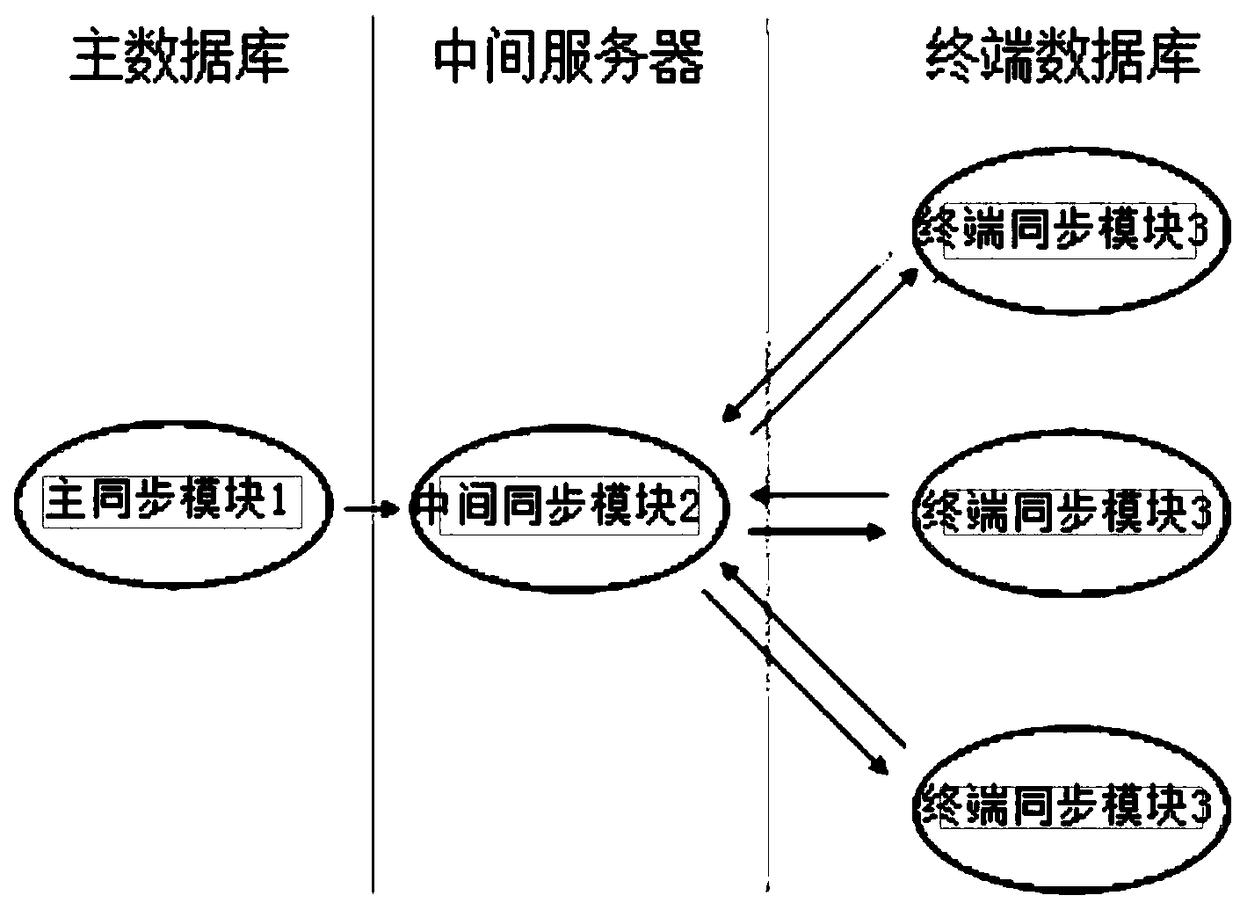

A method and system for passive data synchronization

ActiveCN109344200AReduce data synchronization pressureReduce hardware resource consumptionDatabase distribution/replicationData synchronizationTransaction log

The invention discloses a passive data synchronization method, comprising the following steps: step S1, a master database analyzes a transaction log to obtain incremental data to be synchronized, andsends the incremental data to an intermediate server; step S2, the master database analyzes the transaction log to obtain incremental data to be synchronized; step S1, the master database analyzes thetransaction log to obtain incremental data to be synchronized, and sends the incremental data to an intermediate server; step S1, the master database analyzes the transaction log to obtain incremental data to be synchronized. 2, that intermediate serv caches the incremental data; 3, that terminal database sends an acquisition request to the intermediate serv to acquire the unsynchronized incremental data according to the synchronized incremental data of the terminal database; Step S4, the intermediate server sends corresponding incremental data to the terminal database according to the acquisition request. The invention can minimize the resource occupancy of the server where the main database is located, and has good system expansibility at the same time.

Owner:WUHAN DAMENG DATABASE