DCT/IDCT multiplier circuit optimization method and application

A multiplier and circuit technology, applied in the field of digital video encoding and decoding, can solve the problems of high hardware overhead and high requirements for hardware connection design, and achieve the effect of reducing hardware resource consumption and improving computing efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0058] For the relationship between the N×N signal matrix f and its N×N coefficient matrix F of the two-dimensional discrete cosine transform (DCT), it can be expressed by the following matrix multiplication:

[0059] f=C T ·F C ·C

[0060] f C =C f C T

[0061] Among them, C is the transformation matrix.

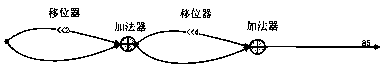

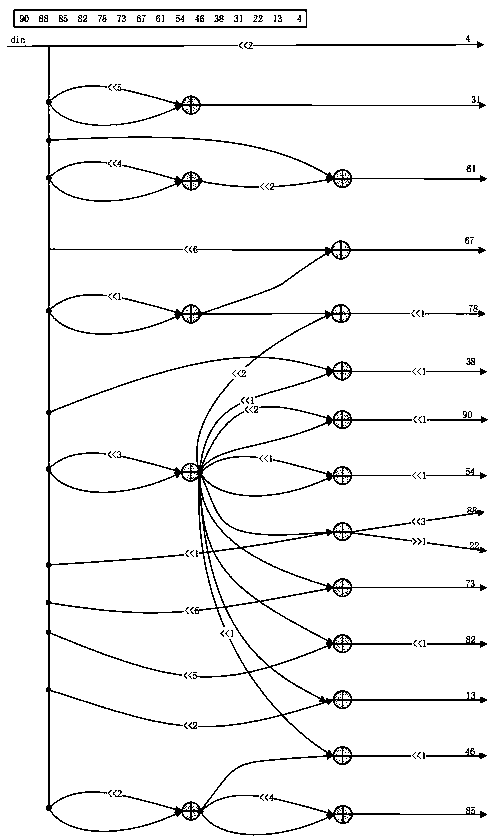

[0062] The multiplication of the matrix requires a large number of multipliers. The hardware basis of the multiplier is the adder structure, which is based on the algorithm of shift and addition. In a multiplier circuit, each bit of the multiplier is ANDed with each bit of the multiplicand to produce its corresponding product bit. These local products are shifted and fed into the array of full adders to obtain the multiplication results.

[0063] The transformation matrix C is a constant matrix, that is, the elements of the transformation matrix C are constants. In this embodiment, at first, the multipliers of the matrix are converted into a series of adders and subt...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More