Bufferable mode verification method

A verification method and mode of technology, applied in the fault hardware test method, detection of faulty computer hardware, instruments, etc., can solve the problem that the verification platform cannot perform data comparison, etc., to achieve the effect of convenient data comparison

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

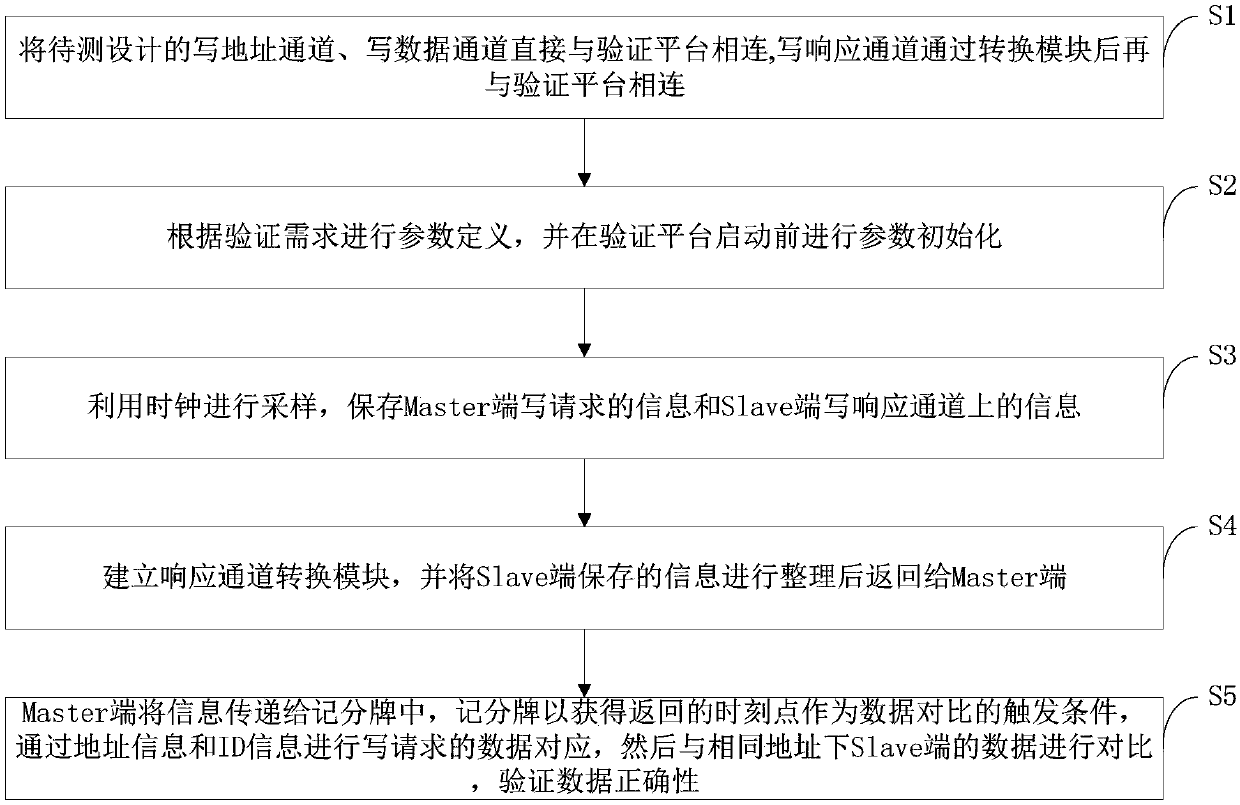

Method used

Image

Examples

Embodiment Construction

[0017] Embodiments of the present invention are described in detail below, examples of which are shown in the drawings, wherein the same or similar reference numerals designate the same or similar elements or elements having the same or similar functions throughout. The embodiments described below by referring to the figures are exemplary only for explaining the present invention and should not be construed as limiting the present invention.

[0018] In the description of the present invention, it should be understood that the terms "first" and "second" are used for description purposes only, and should not be understood as indicating or implying relative importance.

[0019] These and other aspects of embodiments of the invention will become apparent with reference to the following description and drawings. In these descriptions and drawings, some specific implementations of the embodiments of the present invention are specifically disclosed to represent some ways of implemen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More