Soc (System-on-Chip) chip verification method

A verification method and chip technology, applied in the direction of program control design, instruments, electrical digital data processing, etc., can solve the problems of low efficiency of positioning problems, no seed generation mechanism, no debugging means, etc., to achieve the effect of interaction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

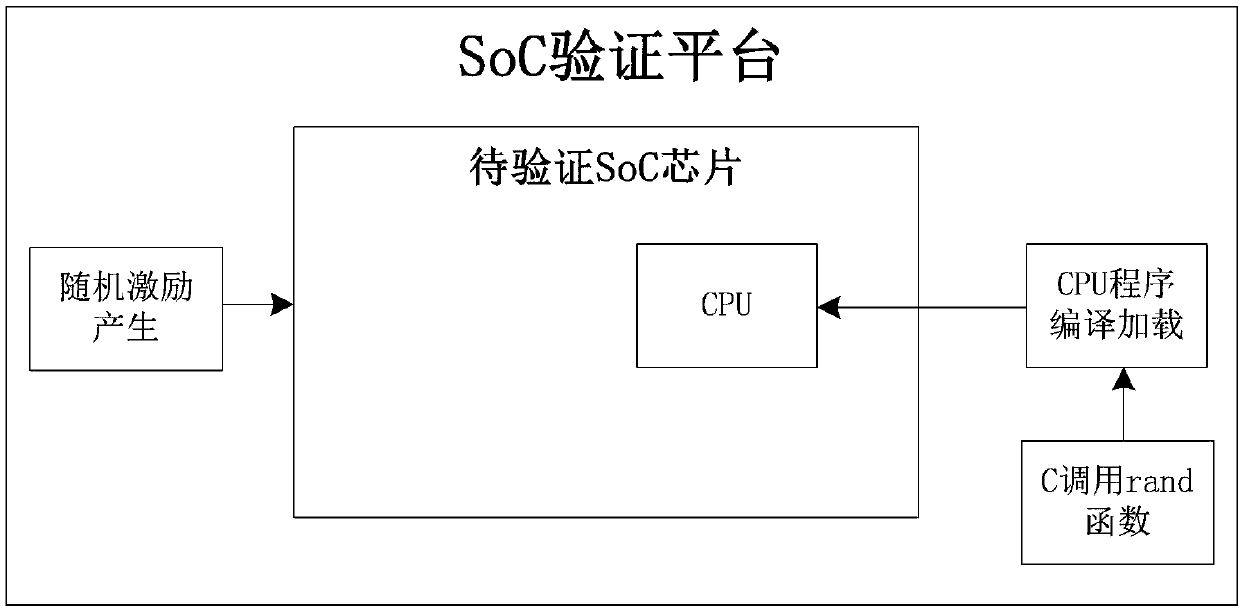

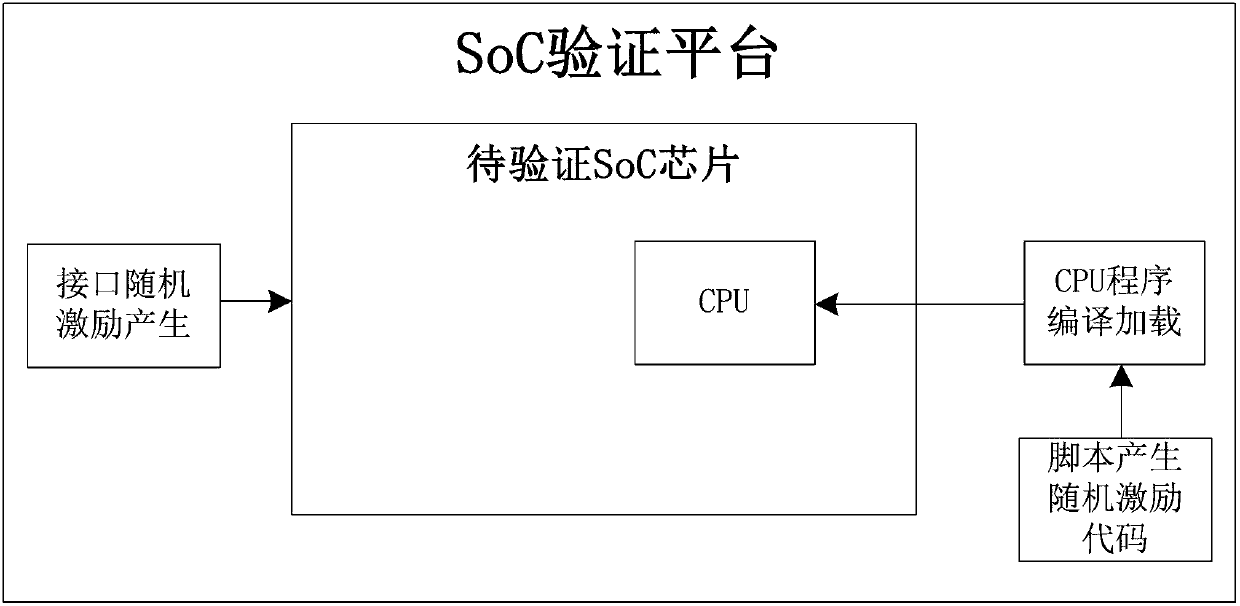

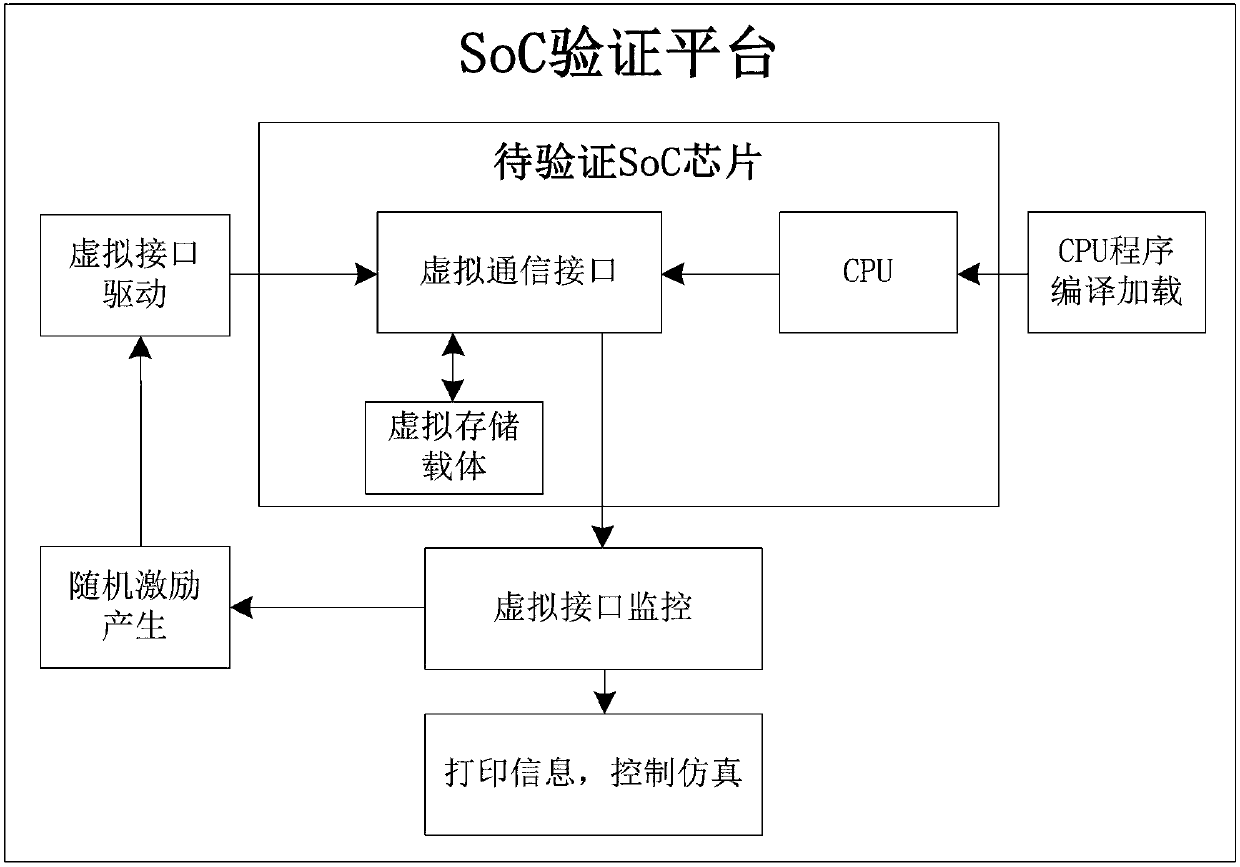

[0015] image 3 It is a schematic diagram of the new Soc verification platform. The main difference between the traditional program-generated random number Soc verification platform and the script-generated random number Soc verification platform is that the dynamic randomization of CPU program incentives can be realized through the virtual communication interface, and the constraints of the incentives can be finer. At the same time, virtual communication can be mo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More