Self-aligned top gate indium-tin-zinc oxide thin film transistor and manufacturing method thereof

A technology of oxide film and gate indium tin zinc, which is applied in the direction of transistor, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problems of poor proportional reduction capability, device short circuit, increased production cost, etc., and achieve proportional reduction capability Strong, save process steps, reduce production costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

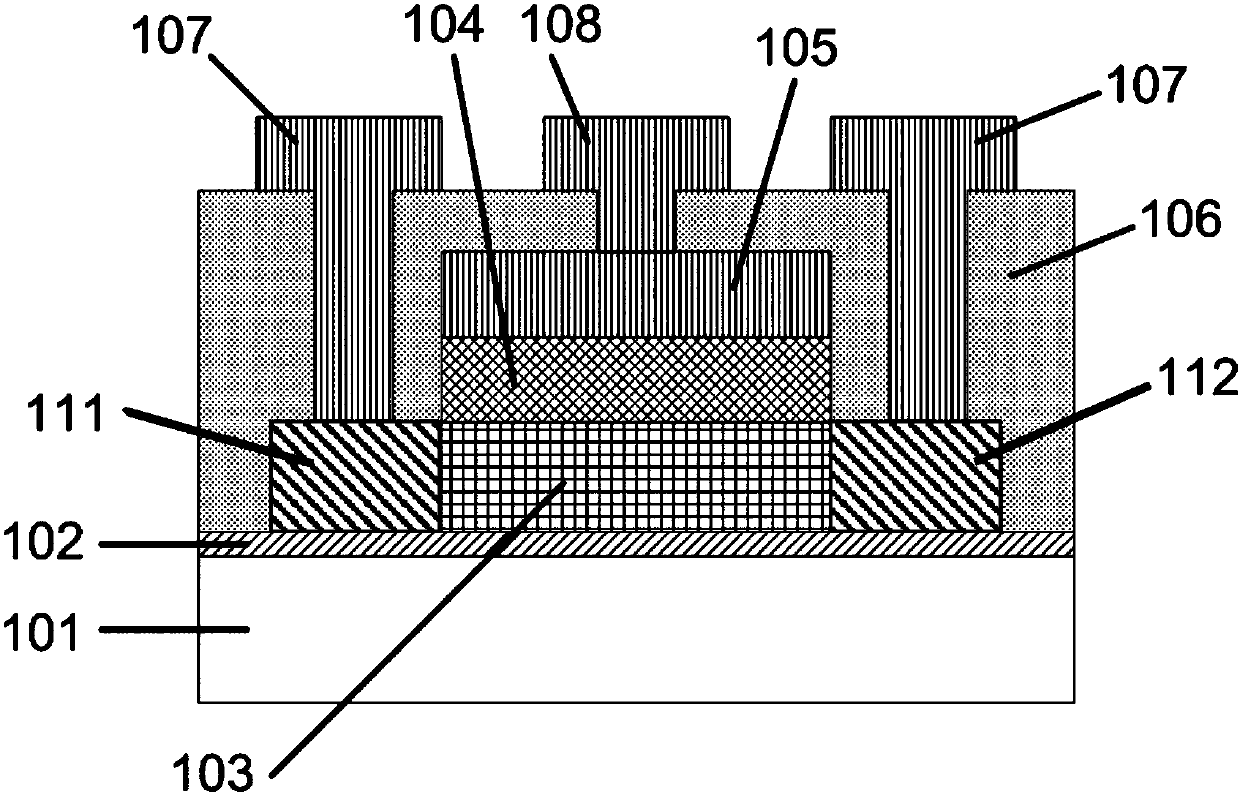

[0061] refer to figure 1 , an indium tin zinc oxide thin film transistor, comprising a substrate 101, the substrate 101 is provided with a buffer layer 102 composed of silicon dioxide, and the buffer layer 102 is provided with an indium tin zinc oxide thin film 103, The indium tin zinc oxide film 103 includes two low-resistance source-drain regions (the first low-resistance source-drain region 111 and the second low-resistance source-drain region 112) and a high-resistance channel region, and the indium tin zinc oxide A gate dielectric layer 104 composed of silicon dioxide is also provided on the object film 103, a conductive film 105 composed of metal aluminum is provided on the gate dielectric layer 104, and a conductive film 105 composed of metal aluminum is provided on the conductive film 105. The passivation layer 106 of silicon, the parts of the conductive film 105 and the indium tin zinc oxide film 103 not covered by the gate dielectric layer 104 are all covered by the ...

Embodiment 2

[0064] refer to Figure 1 to Figure 7 , a method for manufacturing a self-aligned top gate indium tin zinc oxide thin film transistor, comprising the following steps:

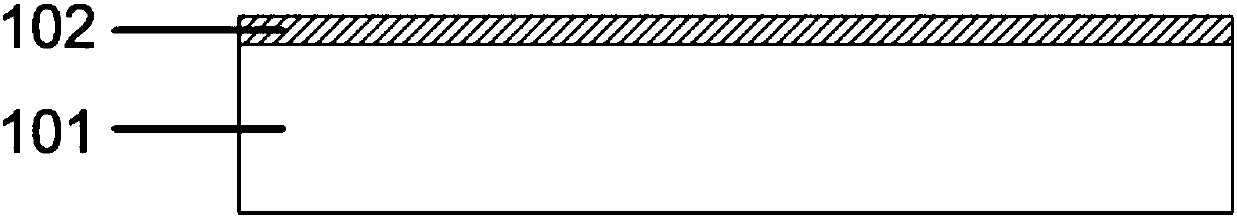

[0065] S1. Deposit a buffer layer 102 on a substrate 101 using a thermal oxidation growth method, such as figure 2 shown;

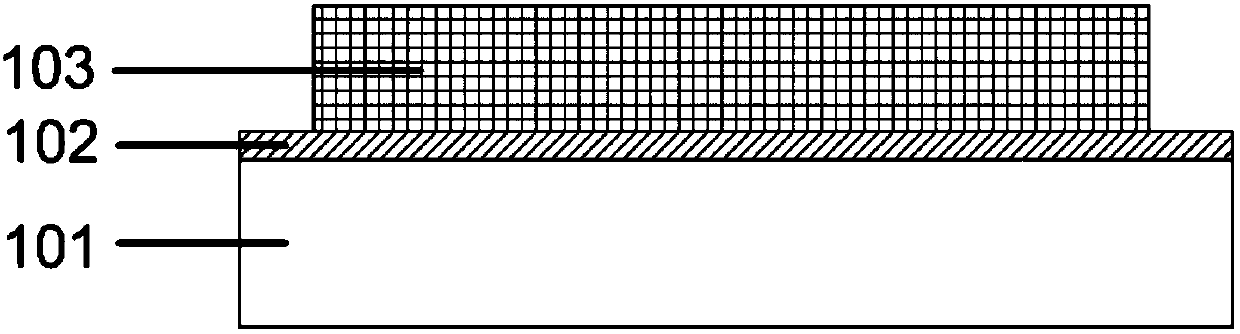

[0066] S2, on the buffer layer 102, use the magnetron sputtering method to deposit the indium tin zinc oxide film 103, such as image 3 As shown, the magnetron sputtering method is DC magnetron sputtering method and RF radio frequency magnetron sputtering method, and the targets used in the magnetron sputtering method are ITO targets and ZnO targets, wherein, Use a DC power supply when sputtering the ITO target, and the input power of the DC power supply is 120W; use a radio frequency power supply when sputtering the ZnO target material, and the input power of the radio frequency power supply is 150W; the reaction atmosphere is oxygen and argon, and the working pressure is 3 milliTorr ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More