A self-aligned top-gate indium tin zinc oxide thin film transistor and its manufacturing method

一种氧化物薄膜、栅铟锡锌的技术,应用在晶体管、半导体/固态器件制造、半导体器件等方向,能够解决等比例缩小能力差、增加生产成本、器件短路等问题,达到等比例缩小能力强、生产成本降低、省去工艺步骤的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

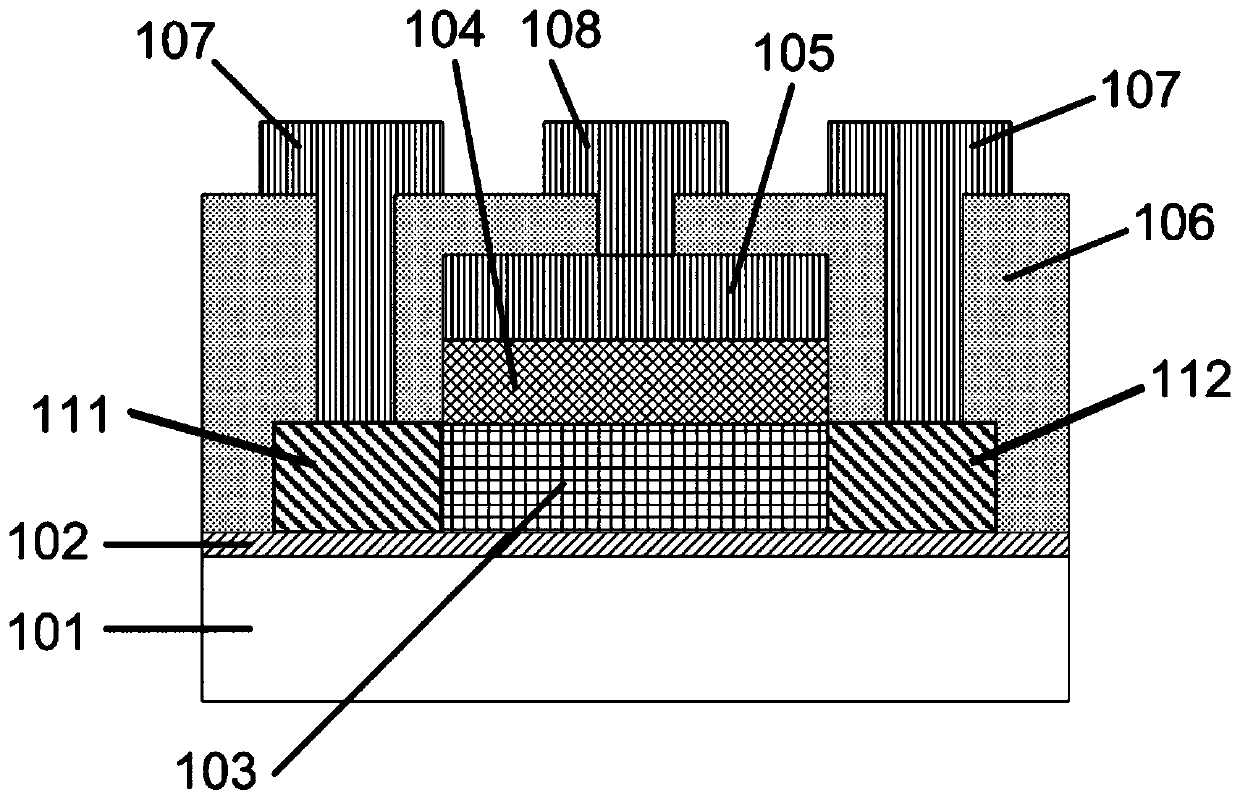

[0061] Reference figure 1 , An indium tin zinc oxide thin film transistor, comprising a substrate 101 on which a buffer layer 102 composed of silicon dioxide is provided, and an indium tin zinc oxide film 103 is provided on the buffer layer 102, The indium tin zinc oxide film 103 includes two low resistance source and drain regions (a first low resistance source and drain region 111 and a second low resistance source and drain region 112) and a high resistance channel region. The material film 103 is also provided with a gate dielectric layer 104 composed of silicon dioxide, the gate dielectric layer 104 is also provided with a conductive film 105 composed of metal aluminum, and the conductive film 105 is also provided with a composition of silicon dioxide. The passivation layer 106 of silicon, the conductive film 105 and the part of the indium tin zinc oxide film 103 that are not covered by the gate dielectric layer 104 are all covered by the passivation layer 106, and the pass...

Embodiment 2

[0064] Reference Figure 1 to Figure 7 , A manufacturing method of a self-aligned top gate indium tin zinc oxide thin film transistor, comprising the following steps:

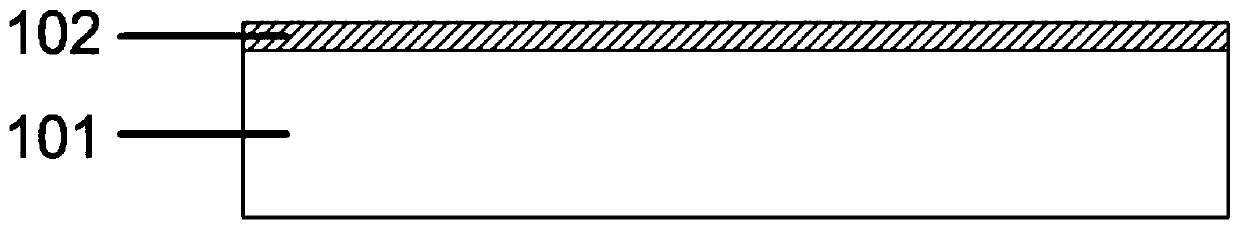

[0065] S1. Use a thermal oxidation growth method to deposit a buffer layer 102 on the substrate 101, such as figure 2 Shown

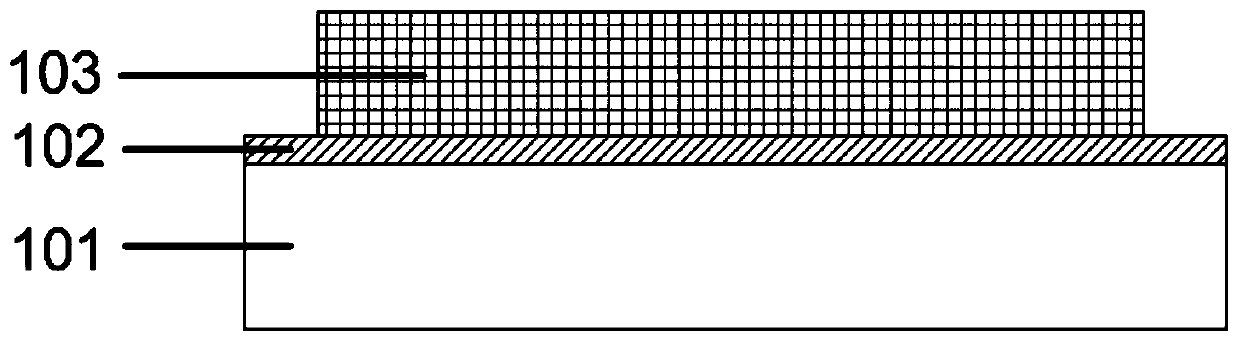

[0066] S2. Use magnetron sputtering to deposit an indium tin zinc oxide film 103 on the buffer layer 102, such as image 3 As shown, the magnetron sputtering method is a DC DC magnetron sputtering method and an RF radio frequency magnetron sputtering method, and the target materials used in the magnetron sputtering method are an ITO target material and a ZnO target material, wherein, When sputtering ITO targets, use a DC power supply, the input power of the DC power supply is 120W; when sputtering ZnO targets, use a radio frequency power supply, the input power of the RF power supply is 150W; the reaction atmosphere is oxygen and argon, working pressure 3 millitorr (mTorr);

[0067] S3, perfo...

PUM

| Property | Measurement | Unit |

|---|---|---|

| power | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More