Method and system for protecting CPU Cache data after AC power failure

A data and data protection technology, applied in the storage field, can solve the problems that data cannot be effectively protected, increase write delay, increase delay, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The core of the present invention is to provide a method for protecting CPU Cache data after AC power failure, for protecting the data in CPU Cache from being lost after AC power failure, and without affecting NVDIMM-N or other non-volatile storage media Excellent read and write performance, reducing latency.

[0043] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

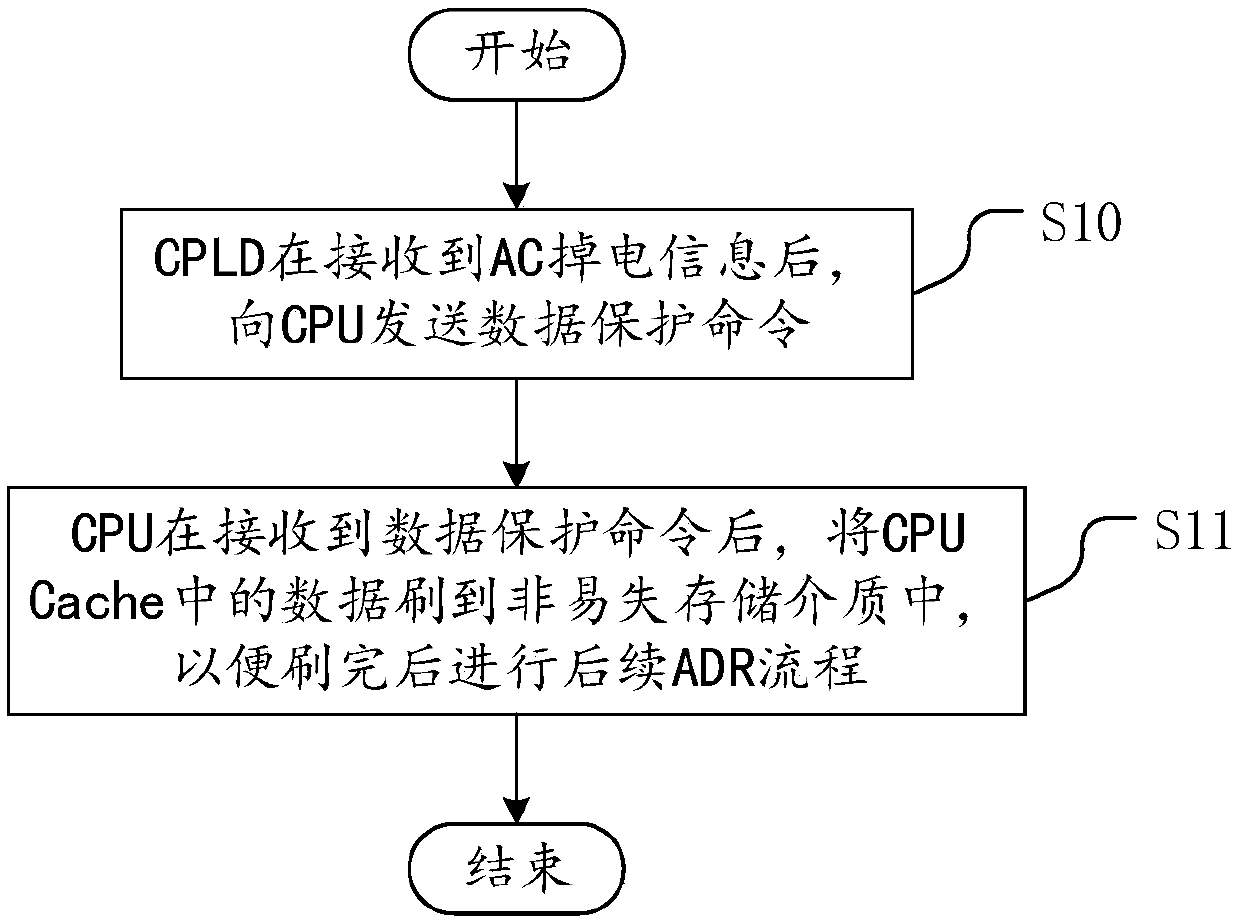

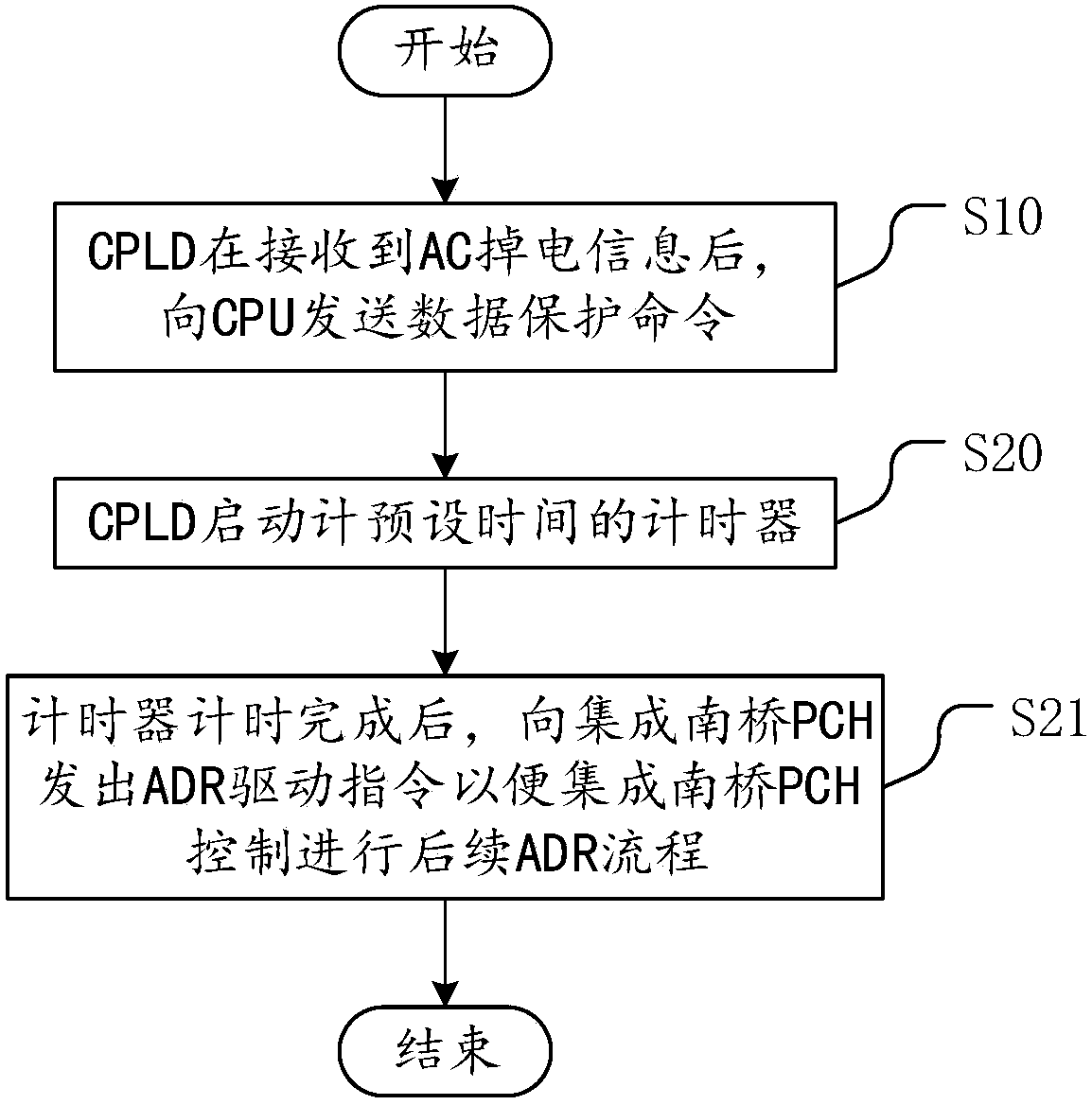

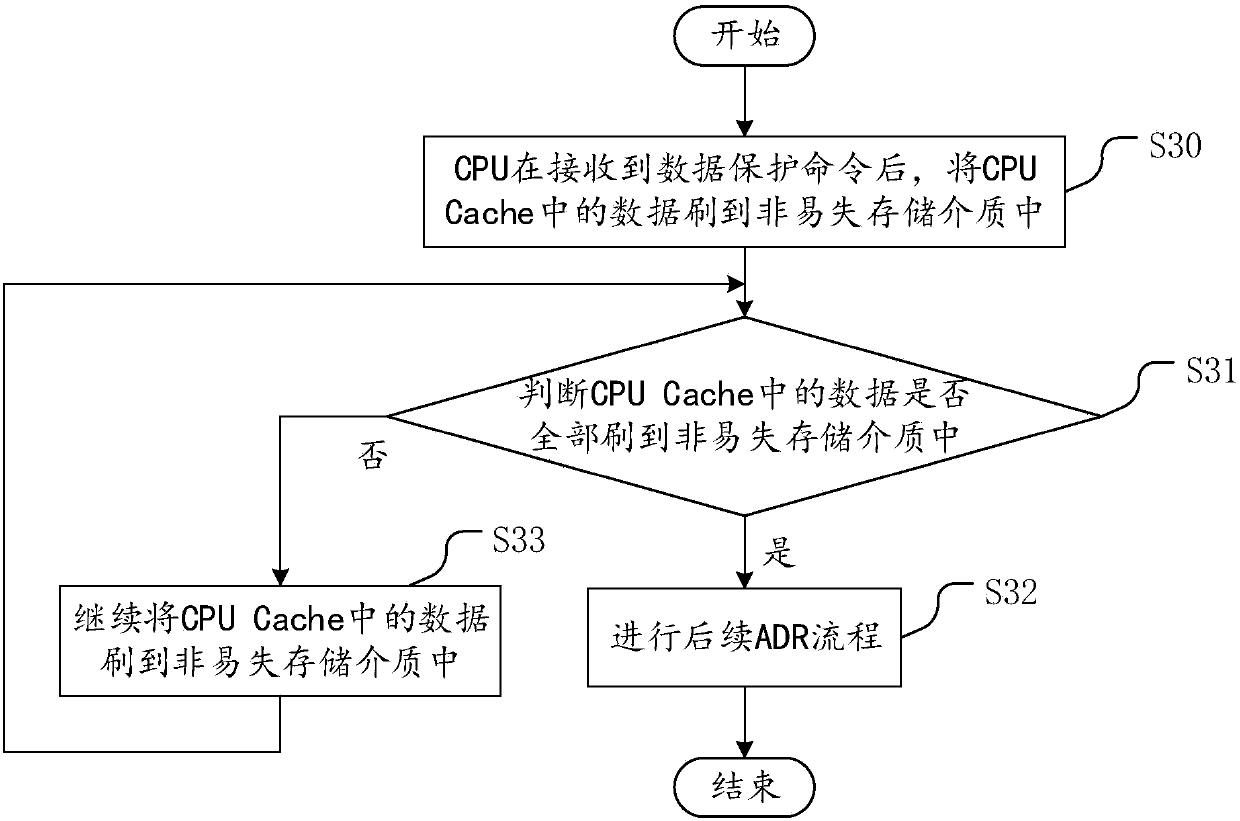

[0044] figure 1 It is a flow chart of the first method for protecting CPU Cache data after AC power failure provided by the embodiment of the p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More