High Performance X-structure Multilayer General Routing Method in VLSI

A large-scale integrated circuit and overall wiring technology, applied in the field of integrated circuit computer-aided design, can solve problems such as the overall wiring algorithm that has not yet been developed, and achieve the effect of increasing the overflow number

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0053] The technical solution of the present invention will be specifically described below in conjunction with the accompanying drawings.

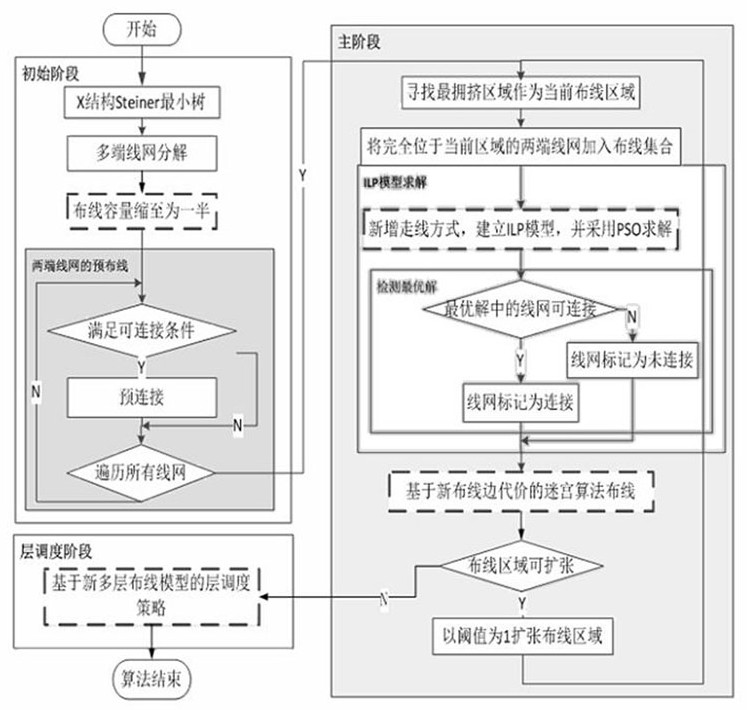

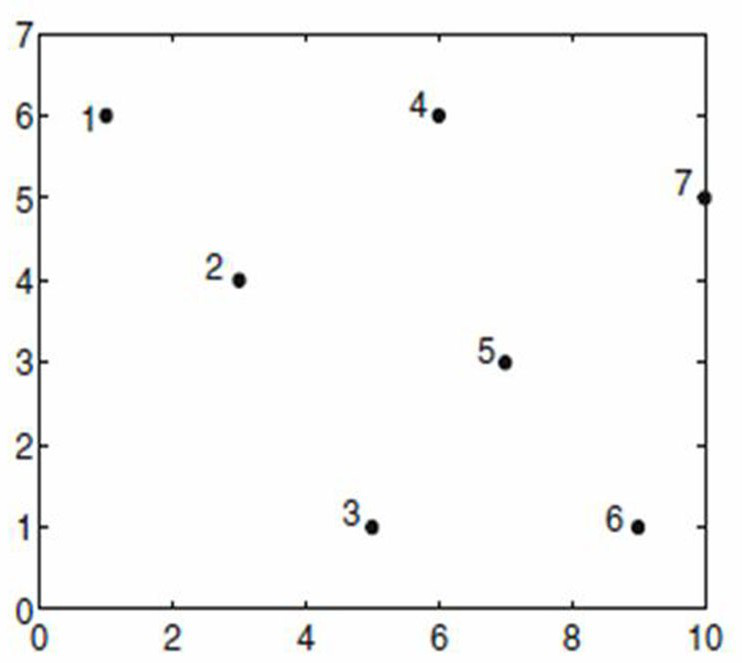

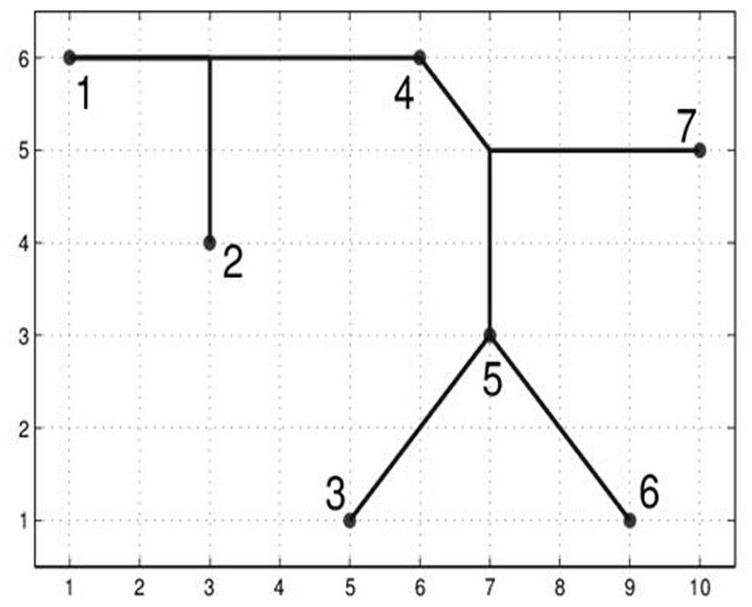

[0054] Aiming at the overall wiring problem considering the two important conditions of non-Manhattan structure and multi-layer wiring structure, the X structure is used as the representative of non-Manhattan structure. On the basis of the previous single-layer overall wiring algorithm research, the present invention is based on the integer programming model (integer Linear programming (ILP for short) and particle swarm optimization (PSO for short), aiming at a series of deficiencies in the existing work, proposed four effective improvement strategies, and introduced a multi-layer wiring model and a layer scheduling strategy. Thus, a high-performance X-structure multilayer overall router is constructed, which is called FZU-Router. The work of the present invention is the first effective solution to the X-structure multilayer overall wirin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More