SAB process method for semiconductor devices

A process method and semiconductor technology, applied in semiconductor devices, electrical solid devices, electrical components, etc., can solve the problems of film filling holes, polysilicon gate pitch reduction, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

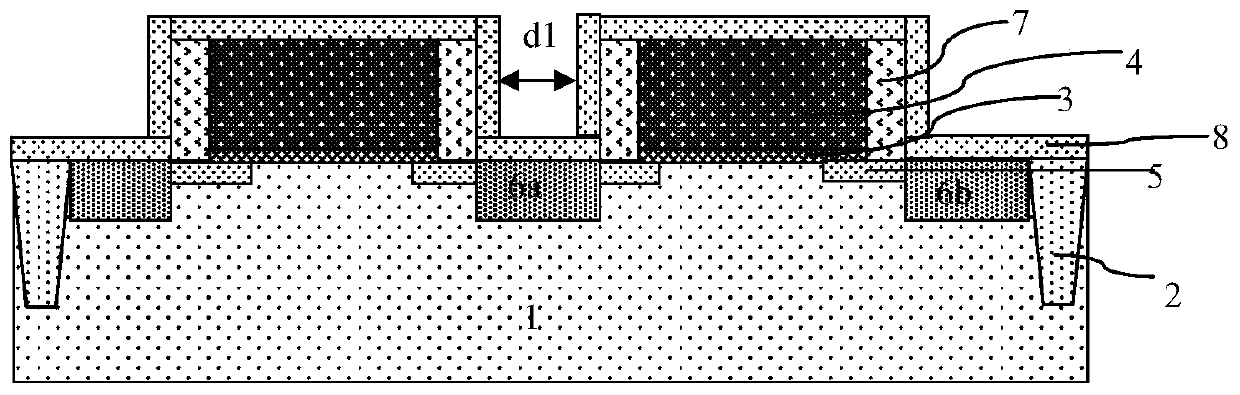

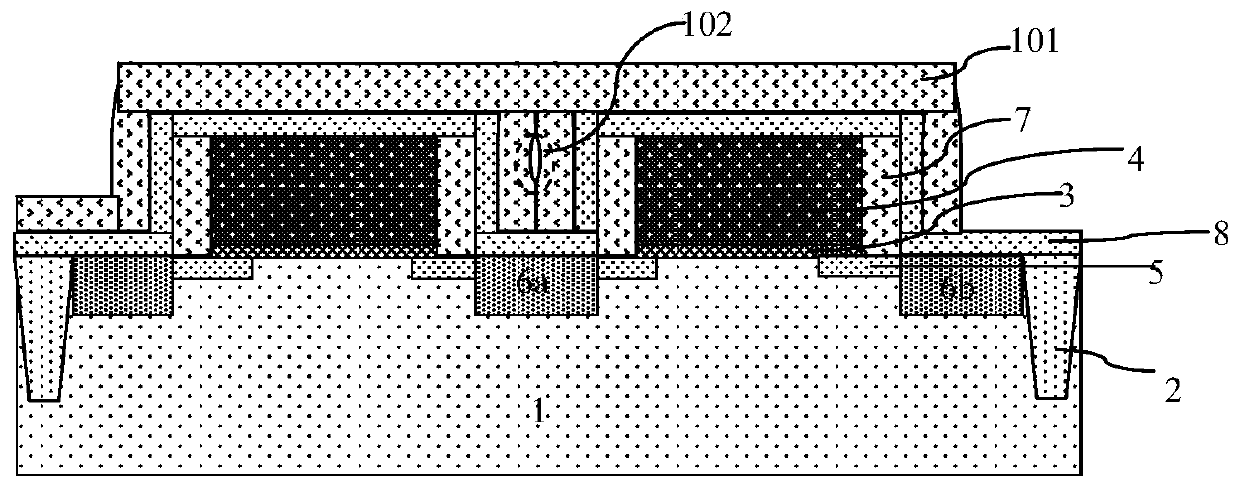

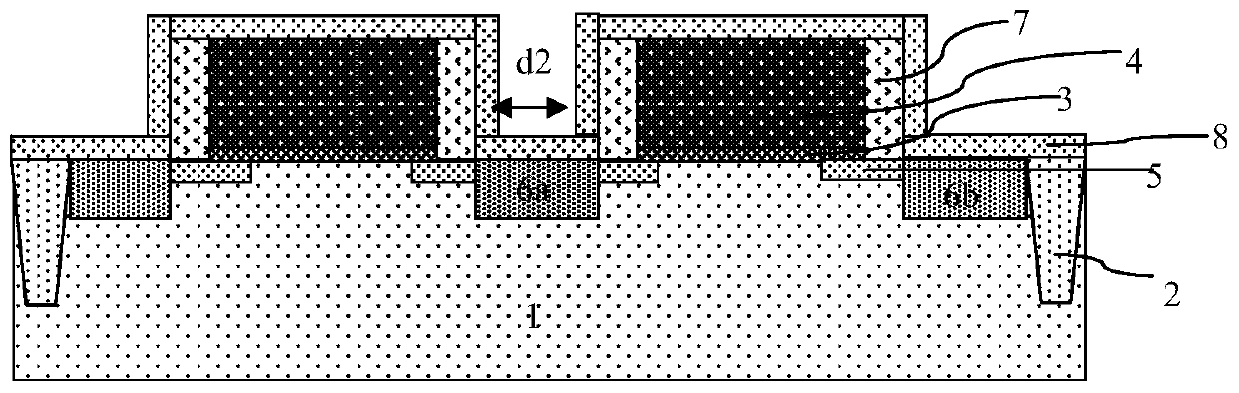

[0030] The existing method is obtained on the basis of analyzing the technical problems of the existing method, so before introducing the existing method in detail, describe the existing method; Figure 1A to Figure 1C As shown, it is a device structure diagram in each step of the SAB process method of the existing semiconductor device. The SAB process method of the existing semiconductor device includes the following steps:

[0031] Step 1, such as Figure 1A As shown, a gate structure, a source region 6a and a drain region 6b of a semiconductor device are formed, the gate structure includes a gate dielectric layer 3 and a polysilicon gate 4 sequentially formed on the surface of a semiconductor substrate 1, and the source region 6a and the drain region 6b are self-aligning quasi-formed on both sides of the corresponding polysilicon gate 4; the integration degree of the semiconductor device is improved by reducing the distance between two adjacent polysilicon gates 4. Figure...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More