Patents

Literature

33results about How to "Fully etched" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

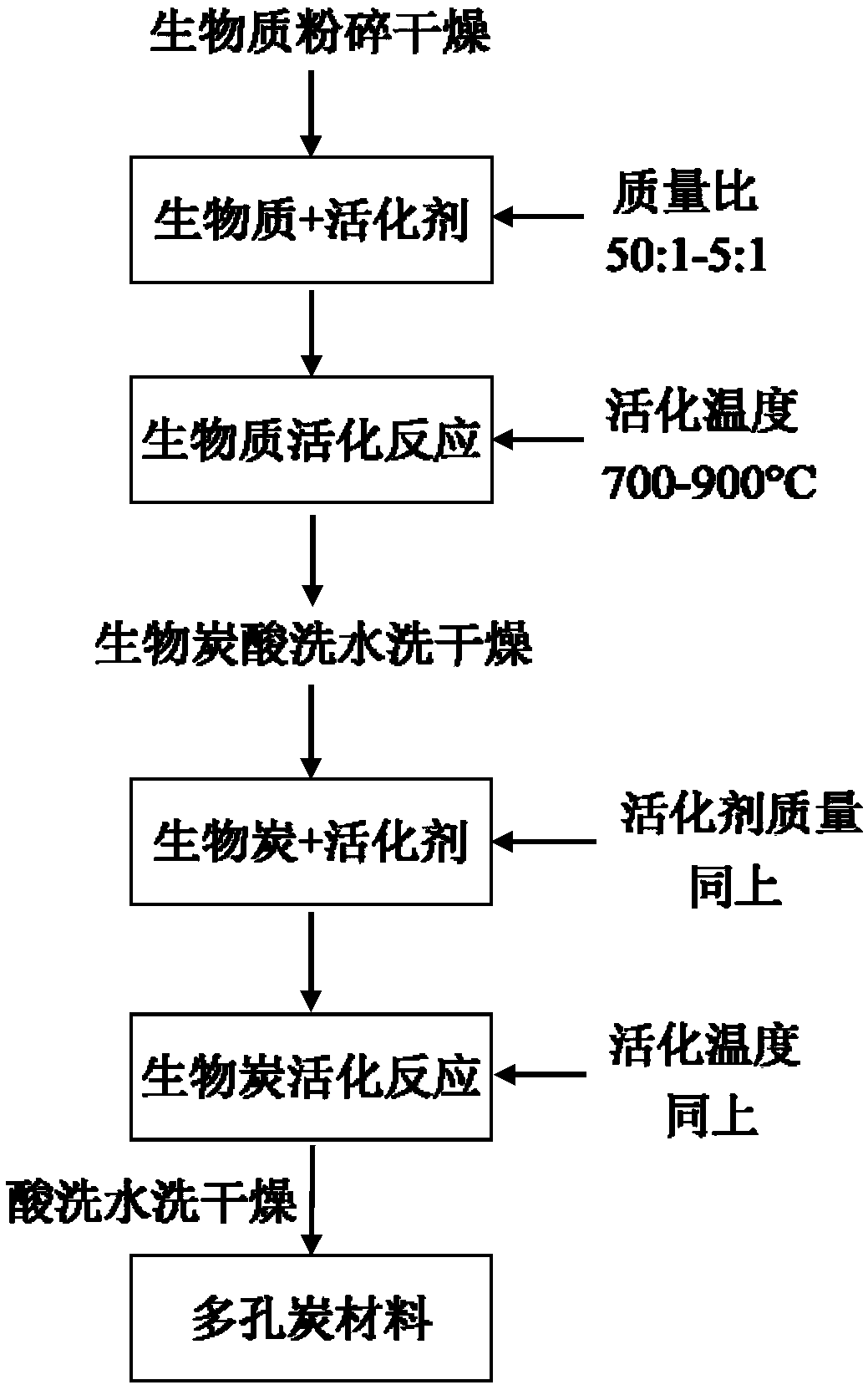

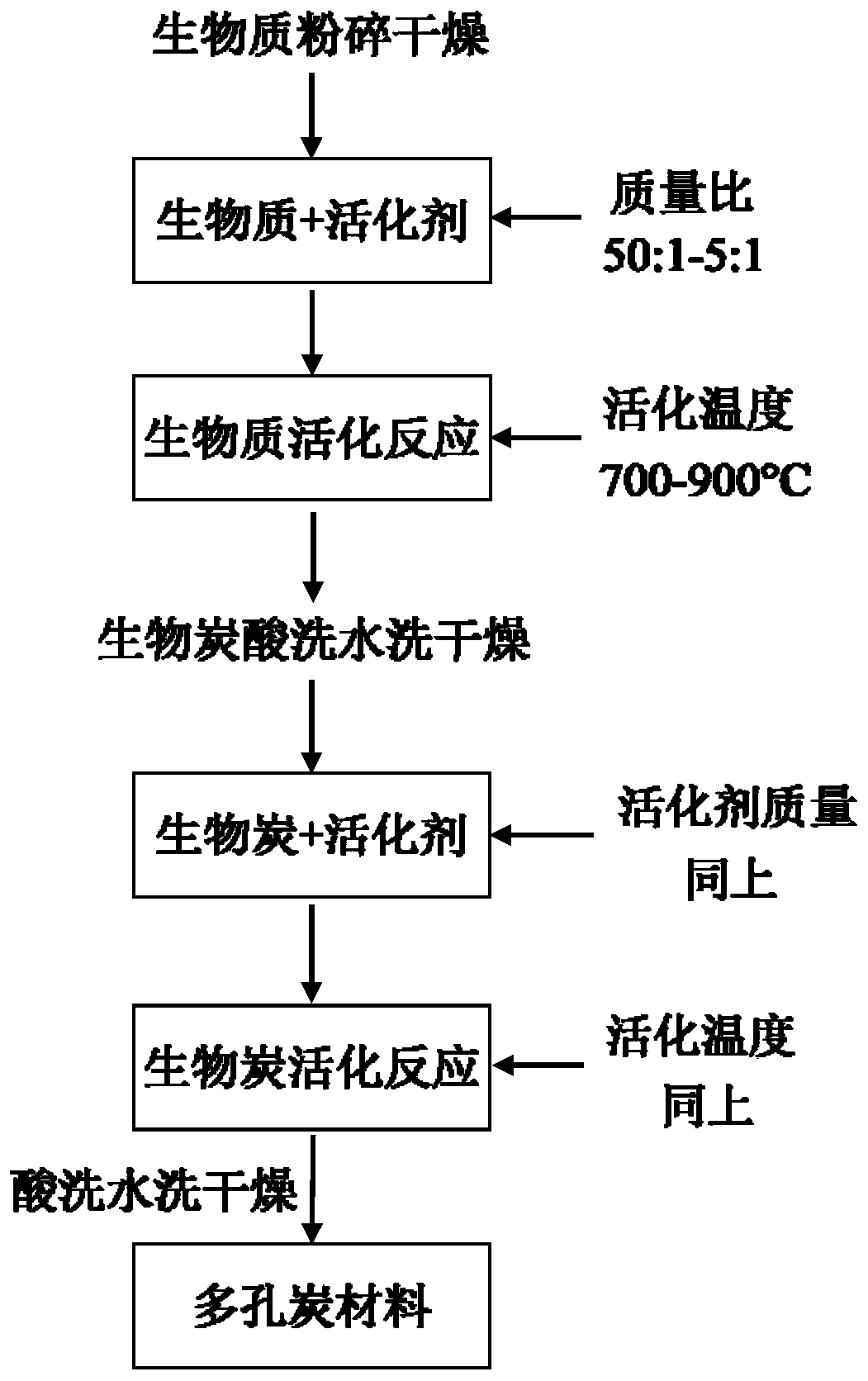

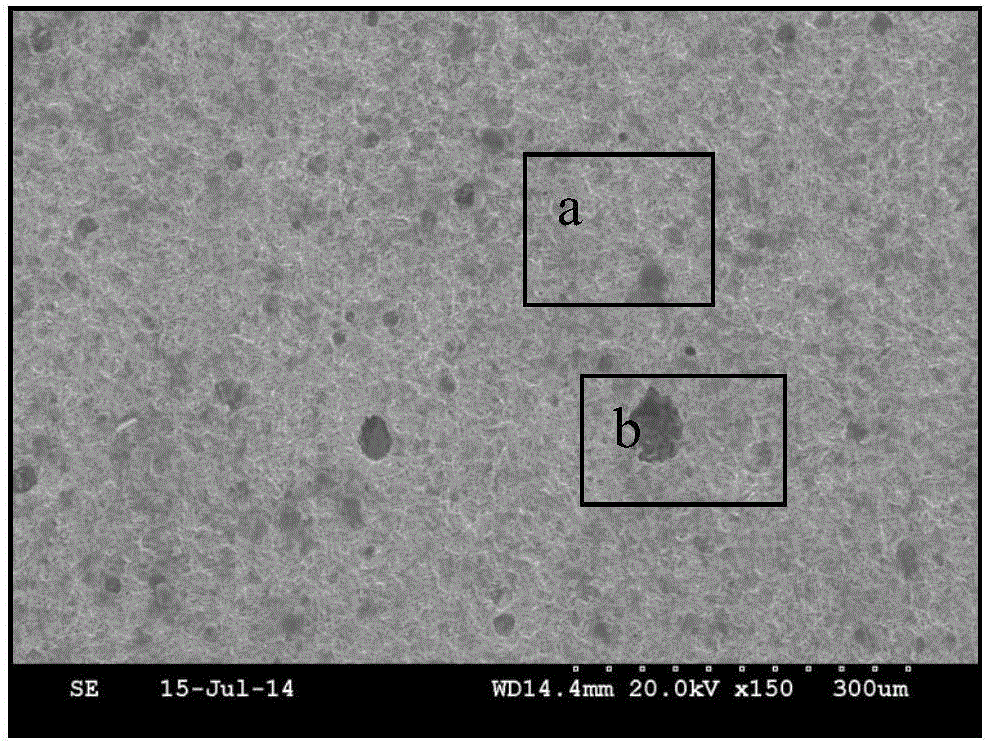

Method for preparing porous carbon by stepwise activation of biomass

The invention discloses a method for preparing porous carbon by stepwise activation of biomass. The method comprises the following preparation process with the steps: after the biomass is crushed anddried and is mixed with an activating agent, activating treatment is carried out under an inertial atmosphere, and the activating agent and the biomass generate activating reaction to initially form biochar with certain porosity; the biochar and the activating agent are dipped uniformly and mixed again, then the activating agent enters pores of the biochar fully, the effective utilization rate ofthe activating agent with good dispersity is greatly increased in the process of secondary activation, and a carbon skeleton can be fully etched to generate a large amount of micropores and mesopores,so that the porous carbon material with a developed porous structure also can be formed even though a little amount of activating agent is used. The method disclosed by the invention has wide application prospect in the fields of catalysis, adsorption and energy storage and the like so as to realize green preparation of the porous carbon material by the biomass and be conductive to push the high-value utilization progress of the biomass.

Owner:HUAZHONG UNIV OF SCI & TECH

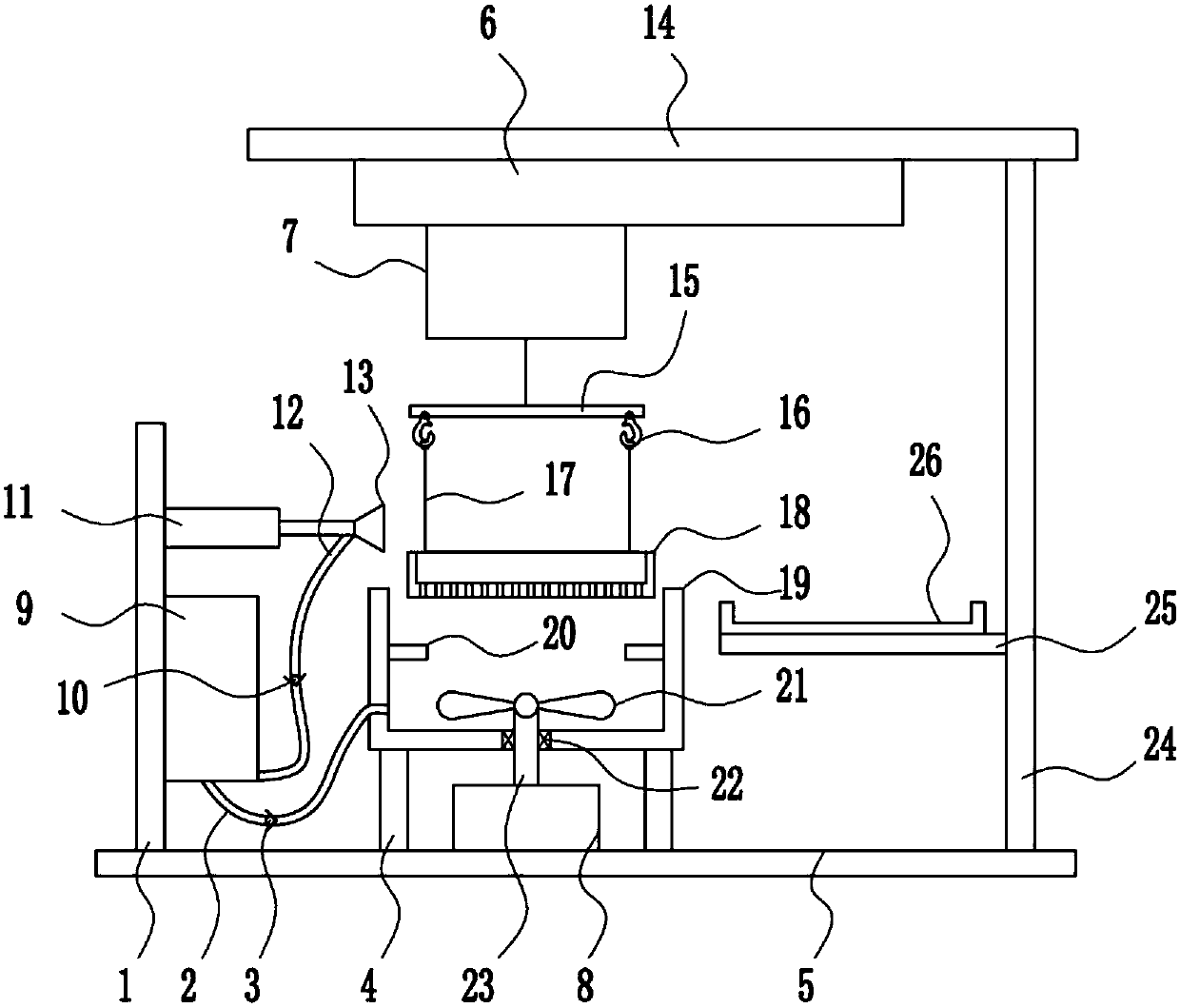

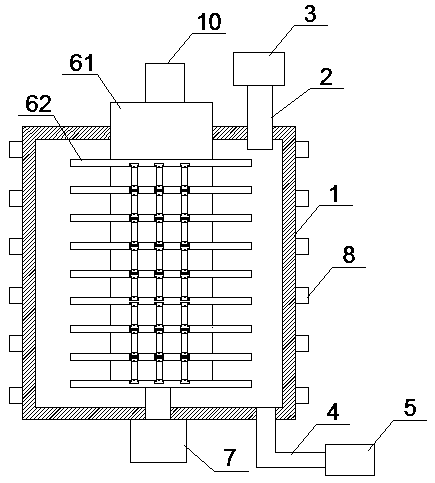

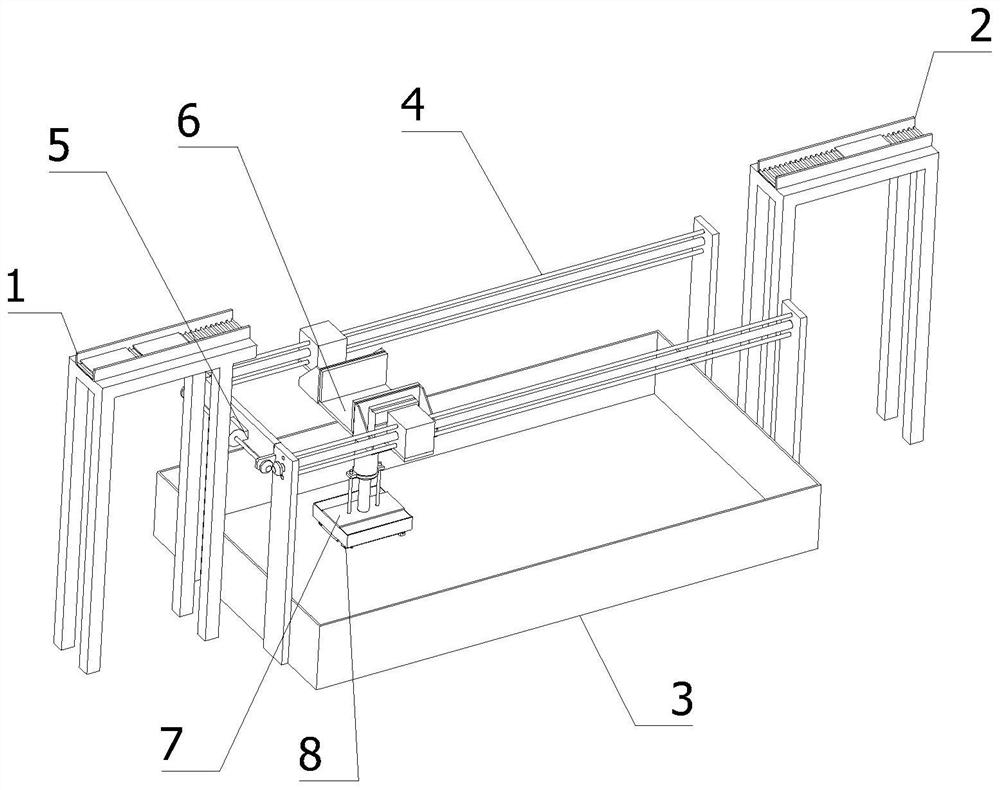

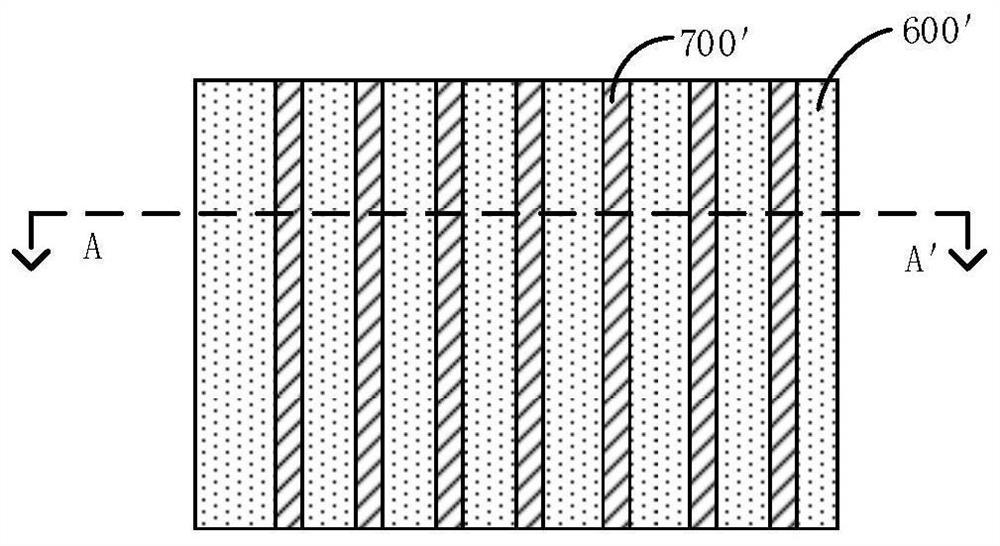

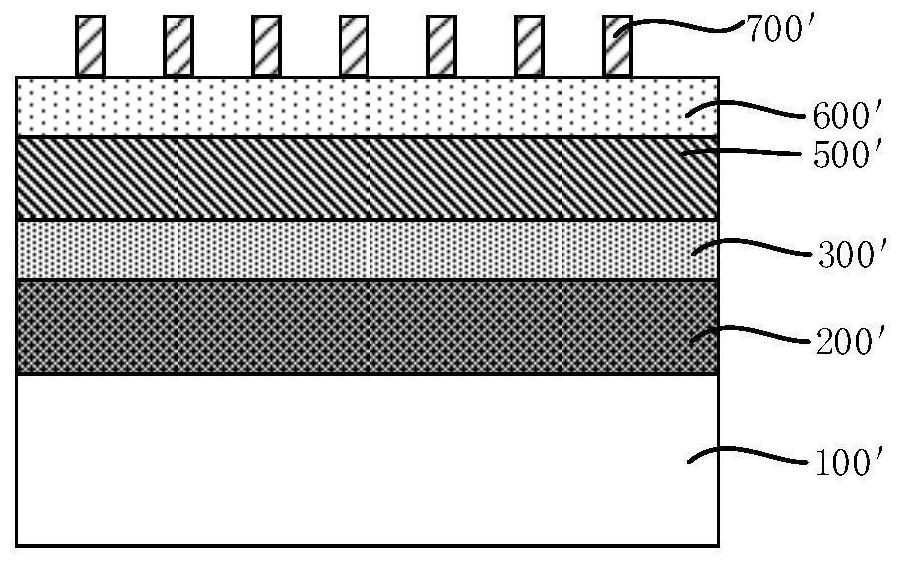

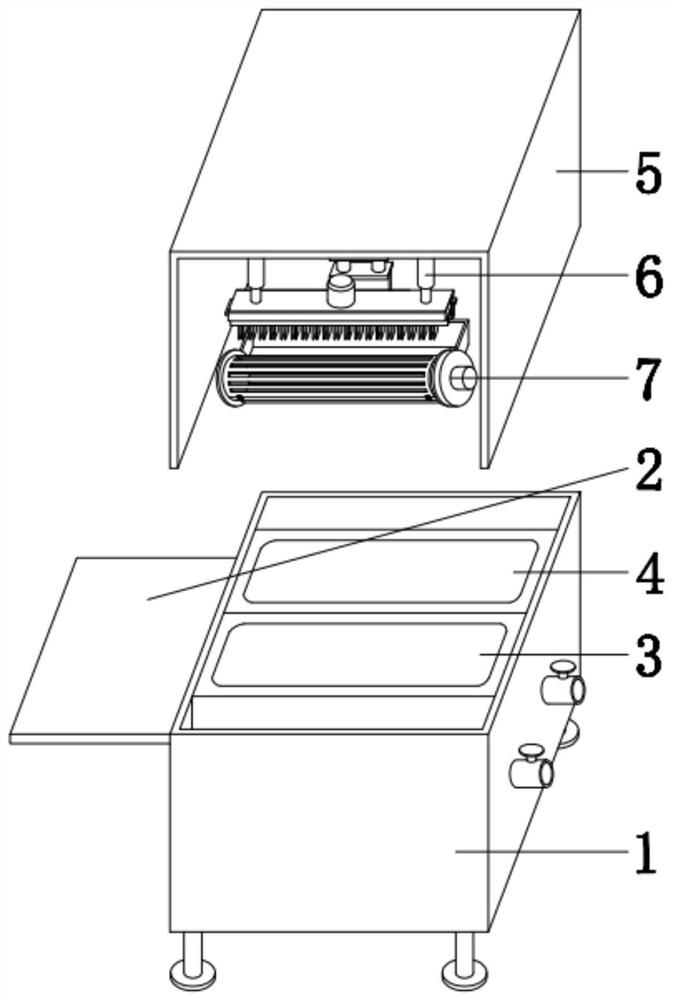

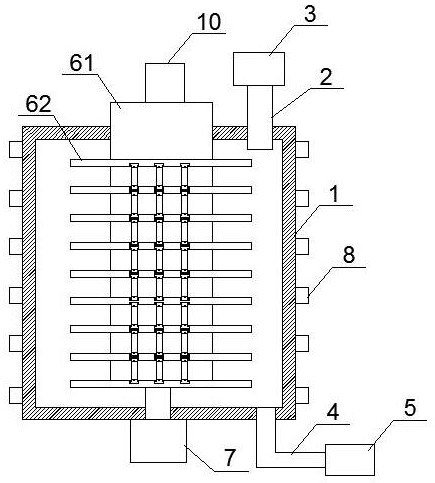

Printed circuit board (PCB) etching equipment for production of electronic display screen

InactiveCN107683026AQuick collectionQuick drop effectConductive material chemical/electrolytical removalEngineeringCam

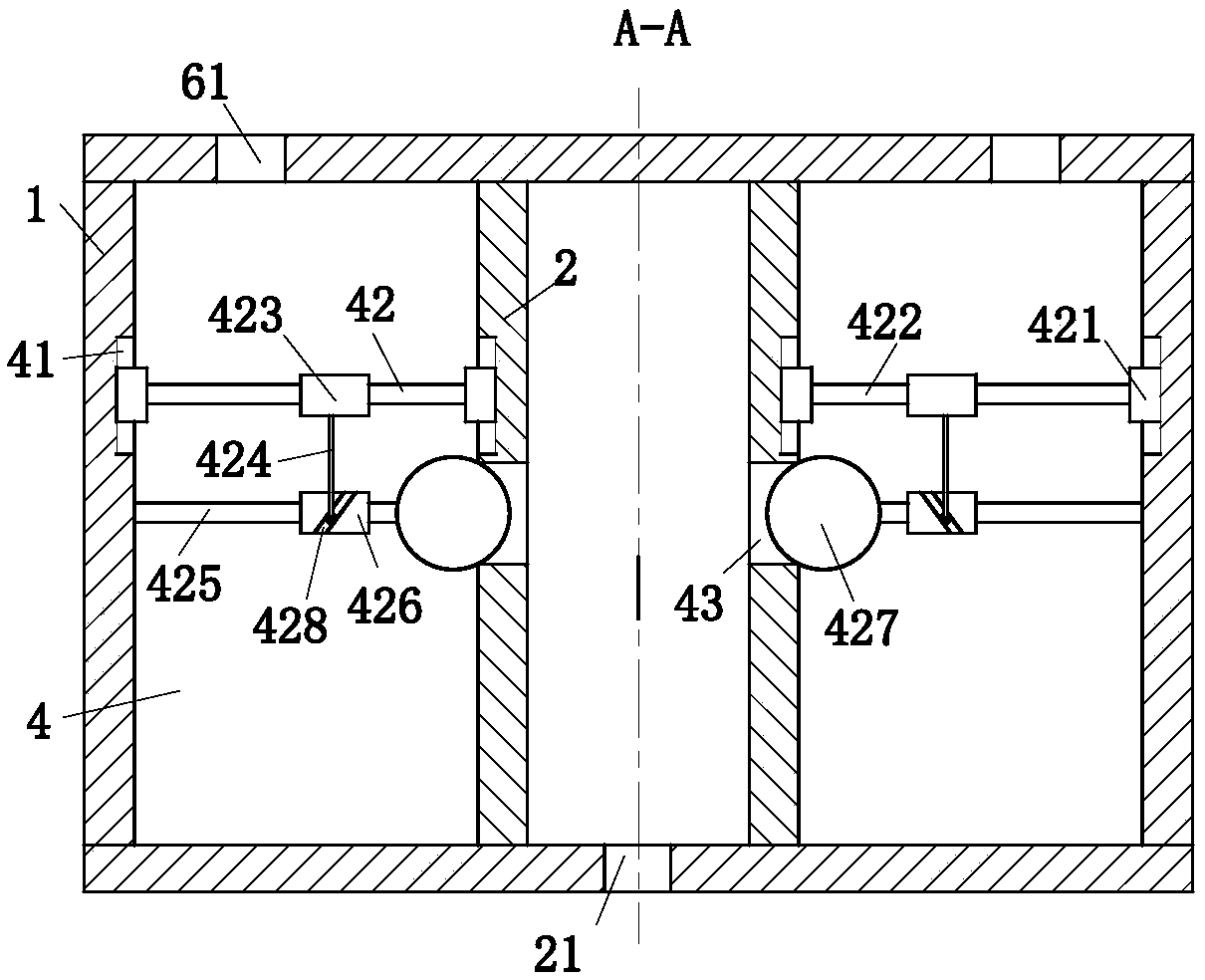

The invention relates to etching equipment, in particular to printed circuit board (PCB) etching equipment for production of an electronic display screen. The PCB etching equipment, which can be usedfor reducing labor intensity of a worker, is high in etching efficiency and is convenient to operate, for the production of the electronic display screen is provided by the invention. In order to solve the technical problem, the PCB etching equipment for the production of the electronic display screen comprises a left rack, a first pipeline, a first one-way valve, a support rod, a bottom plate, amobile device, a lifting device, a rotation device, a liquid transmission device and a second one-way valve, wherein the left rack is welded at a left side of the top of the bottom plate, and the liquid transmission device is arranged at a lower part of a right side of the left rack. By the PCB etching equipment, the rotation direction of an electric winding wheel is controlled, the effects of rapidly collecting and placing a PCB is achieved by matching of the electric winding wheel and a first spring, a rotation motor is controlled to rotate, a cam and a second spring are matched with each other, an etching liquid is stirred by rotating rotation blades, so that the PCB and the etching liquid are in full contact, and the etching efficiency is improved.

Owner:郑诗青

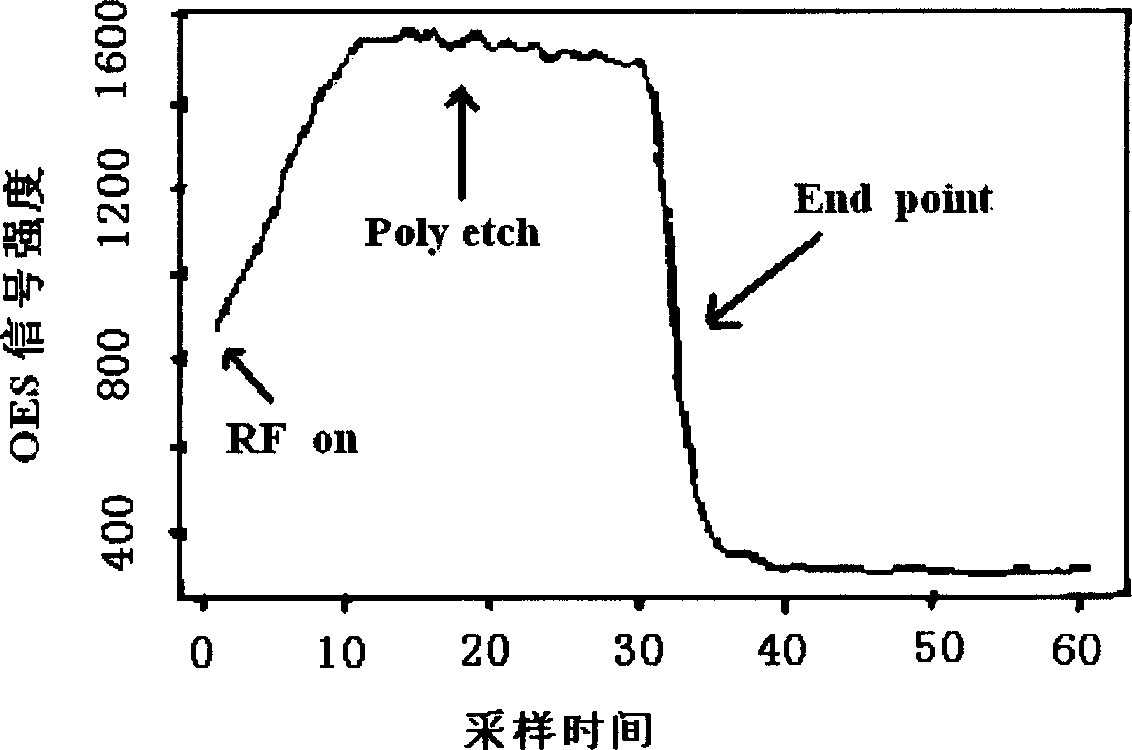

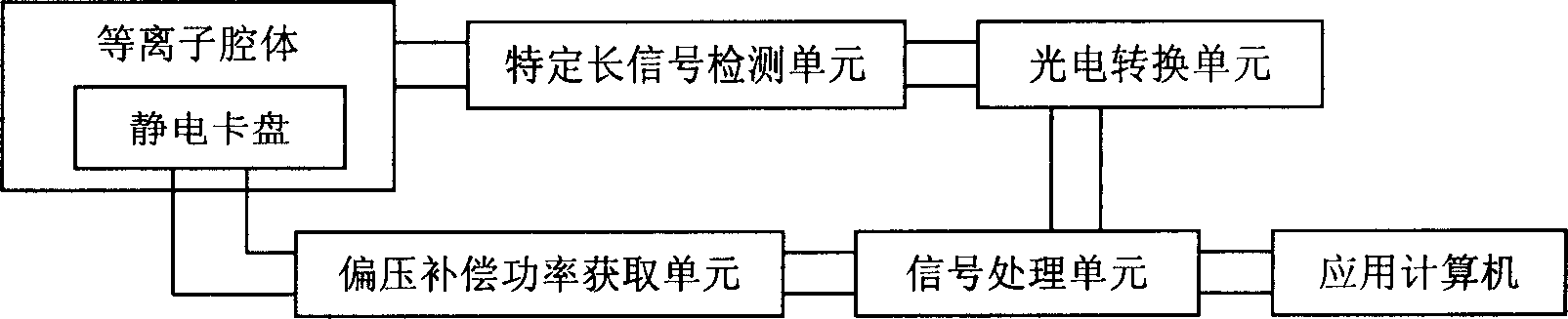

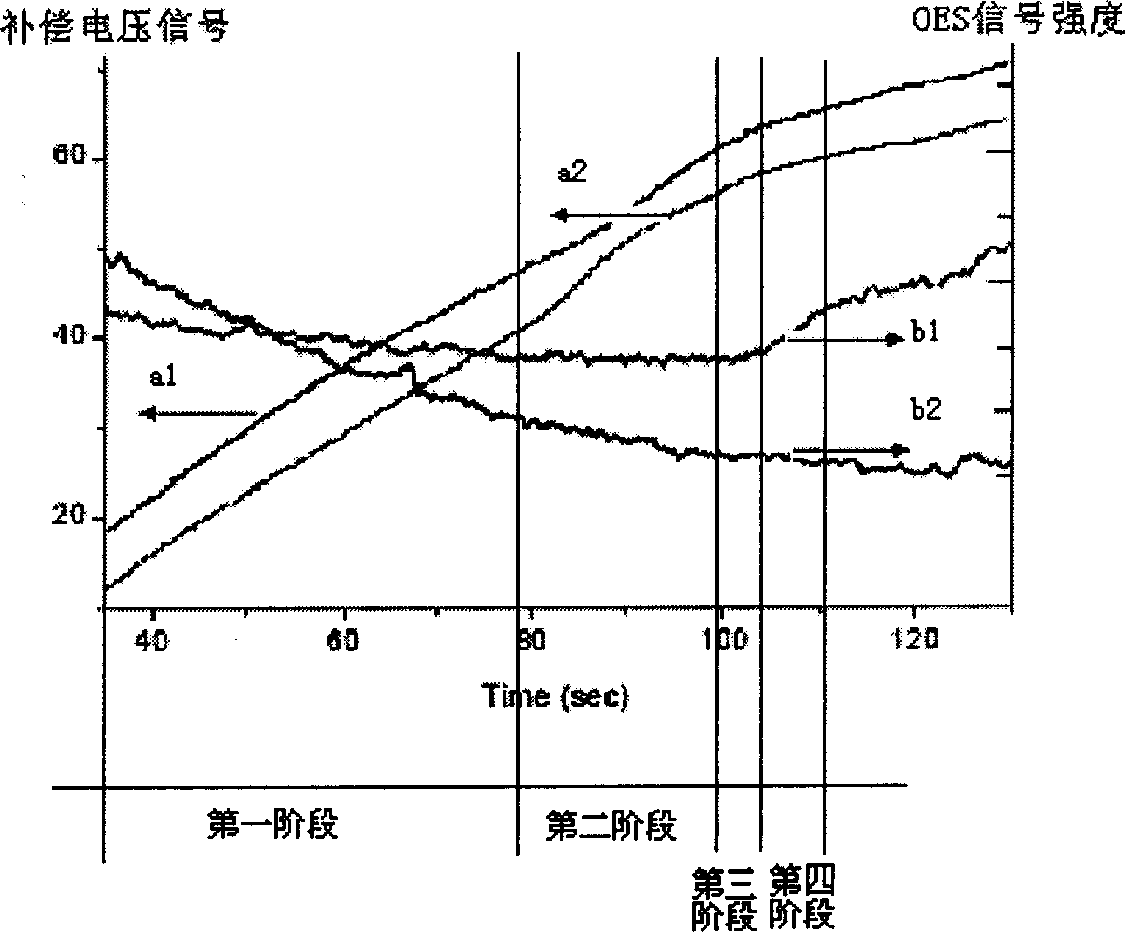

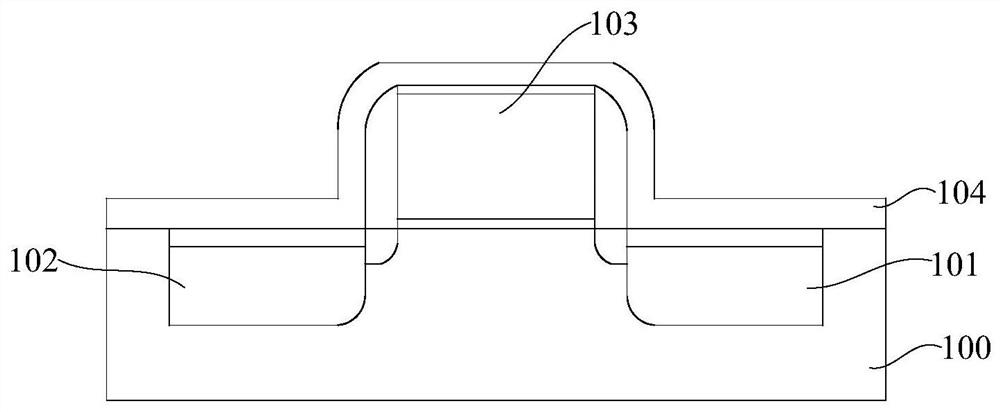

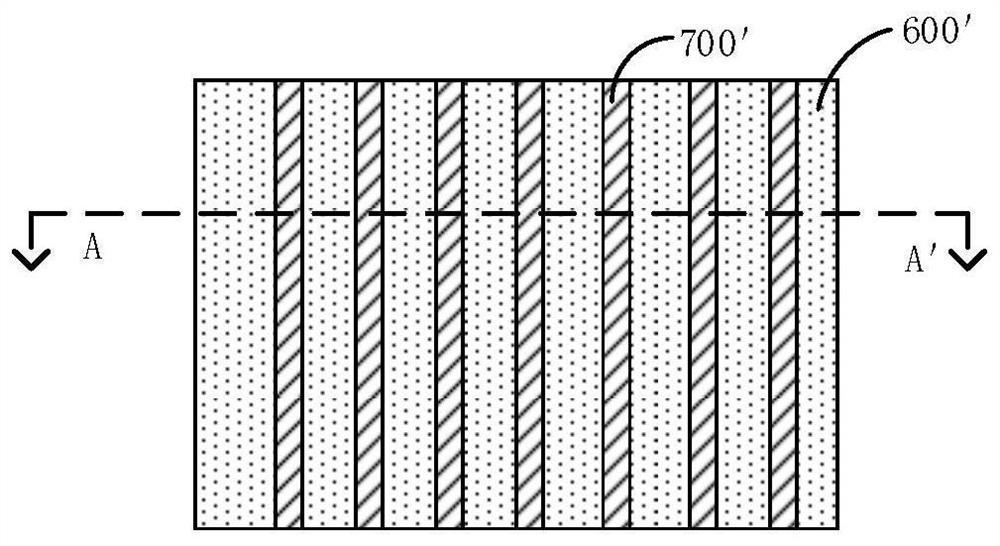

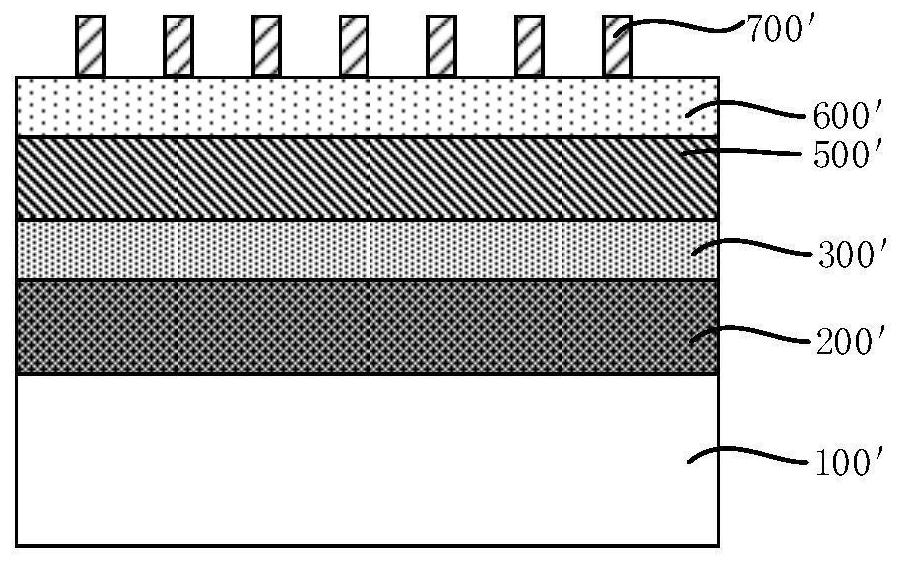

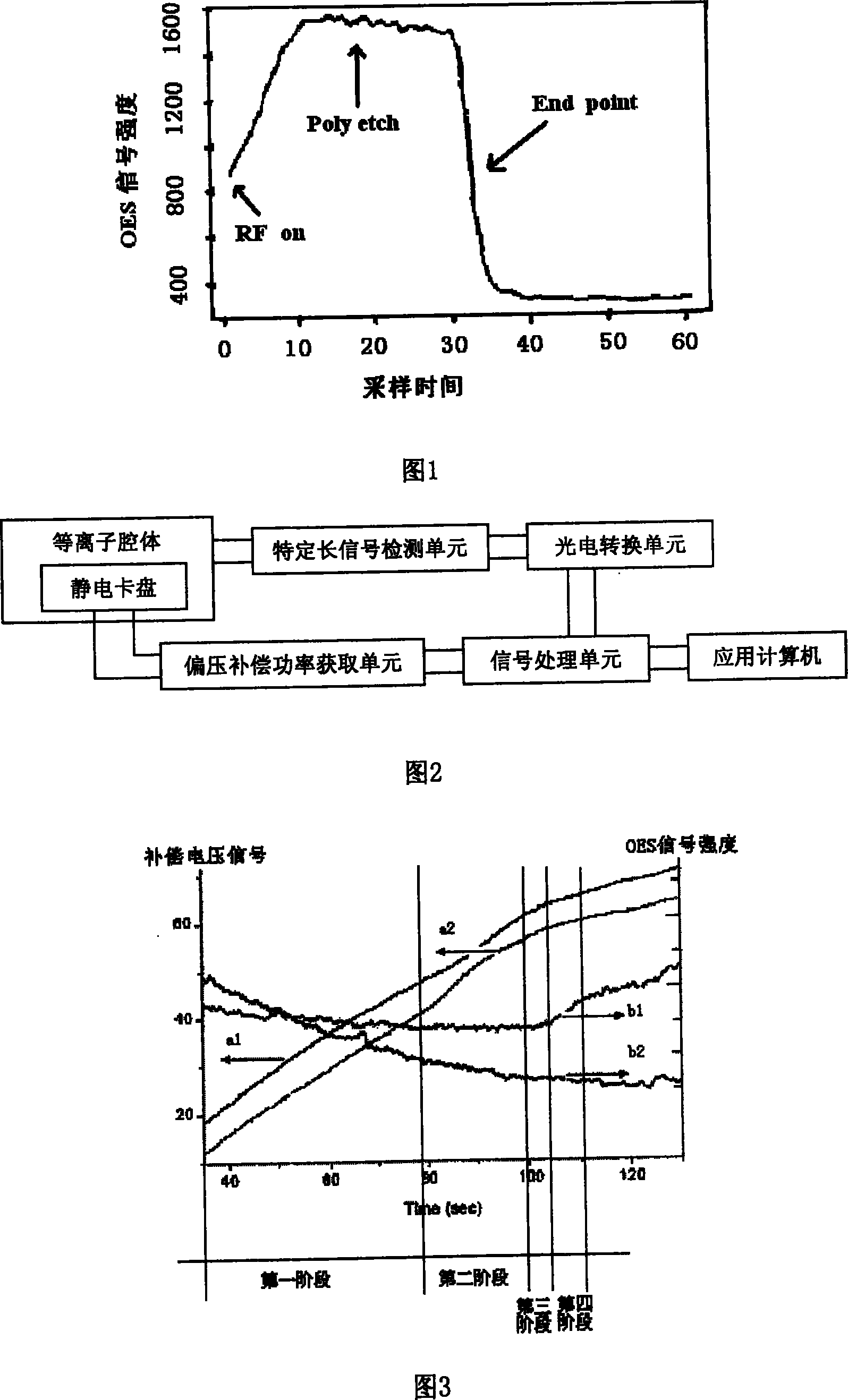

Method and apparatus for detecting polysilicon gate etching terminal

ActiveCN1812066AFully etchedGuaranteed Advance ProtectionSemiconductor/solid-state device testing/measurementGratingOxygen

This invention is a kind of end point checking method and checking apparatus of polycrystalline silicon grating etching. The etching process has four steps which have different end point checking method. Bias voltage compensating end point checking predicts the end point of etching process that has relative low etching selecting rate. Use this sensitive method can ensure oxidation layer pre-protected before etching drawing near grate oxygen. Though OES end point checking method, checking etching process of high selecting rate ensures polycrystalline silicon etched fully and grate oxygen layer protected effectively.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

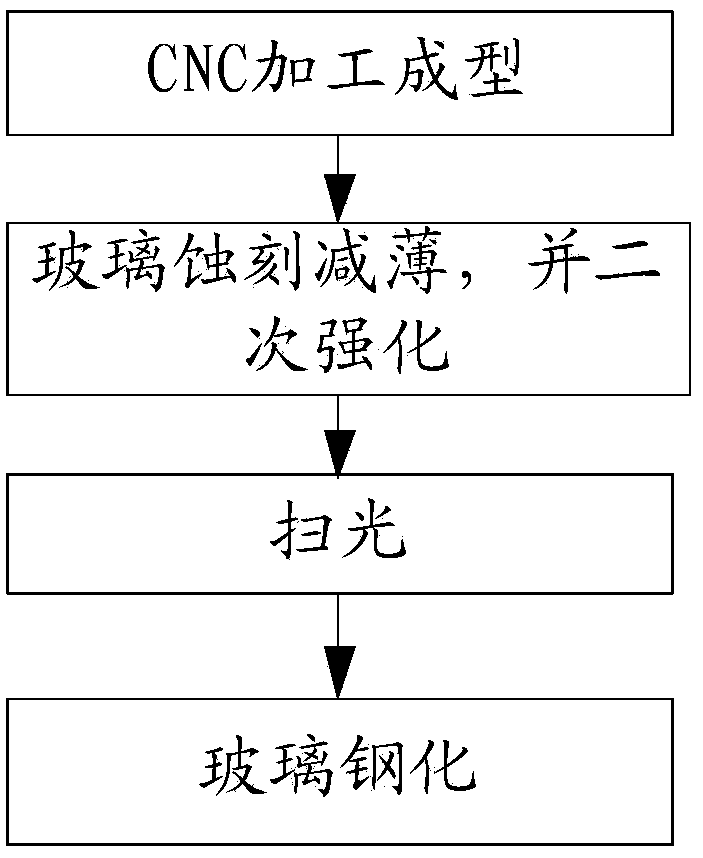

Method for increasing strength of ultra-thin glass

The invention relates to a method for increasing the strength of ultra-thin glass. The method comprises the following steps: step A, carrying out CNC (Computer Numerical Control) processing molding ona glass substrate; step B, etching and thinning the processed glass substrate, and carrying out secondary reinforcement; step C, carrying out light sweeping treatment on the reinforced glass substrate through a glass light sweeping machine; step D, tempering the glass substrate after light sweeping. According to the technical scheme disclosed by the invention, the strength of the ultra-thin glassof which the thickness range is 0.10 to 0.33 mm can be increased, the requirement of existing mobile phone cover plate and a protective piece on strength can be met, and accident breakage during a dropping process of a mobile phone, a tablet PC (Personal Computer) and the like can be reduced, so that electronic products can be protected.

Owner:YONGZHOU FUXING ELECTRONICS SCI & TECH

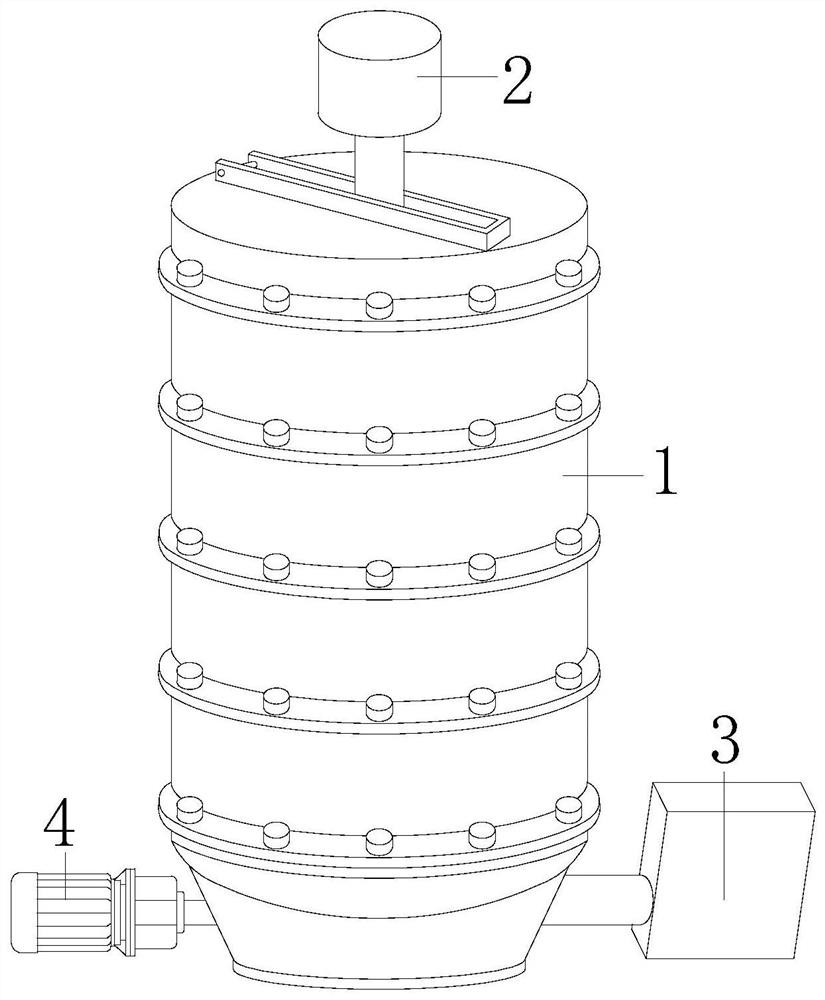

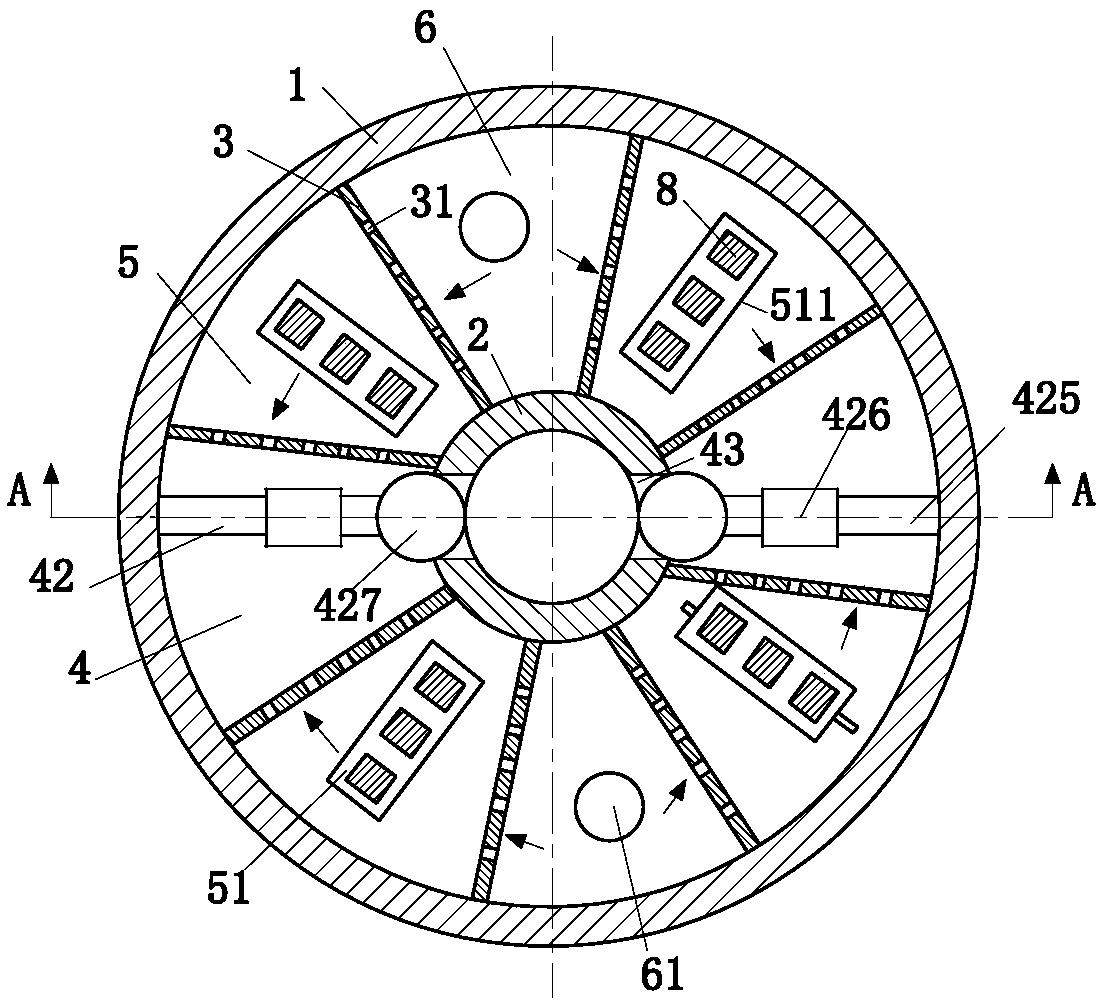

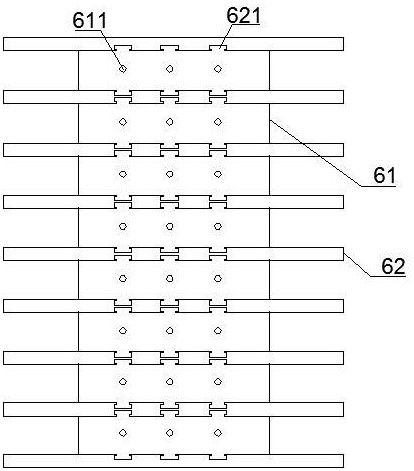

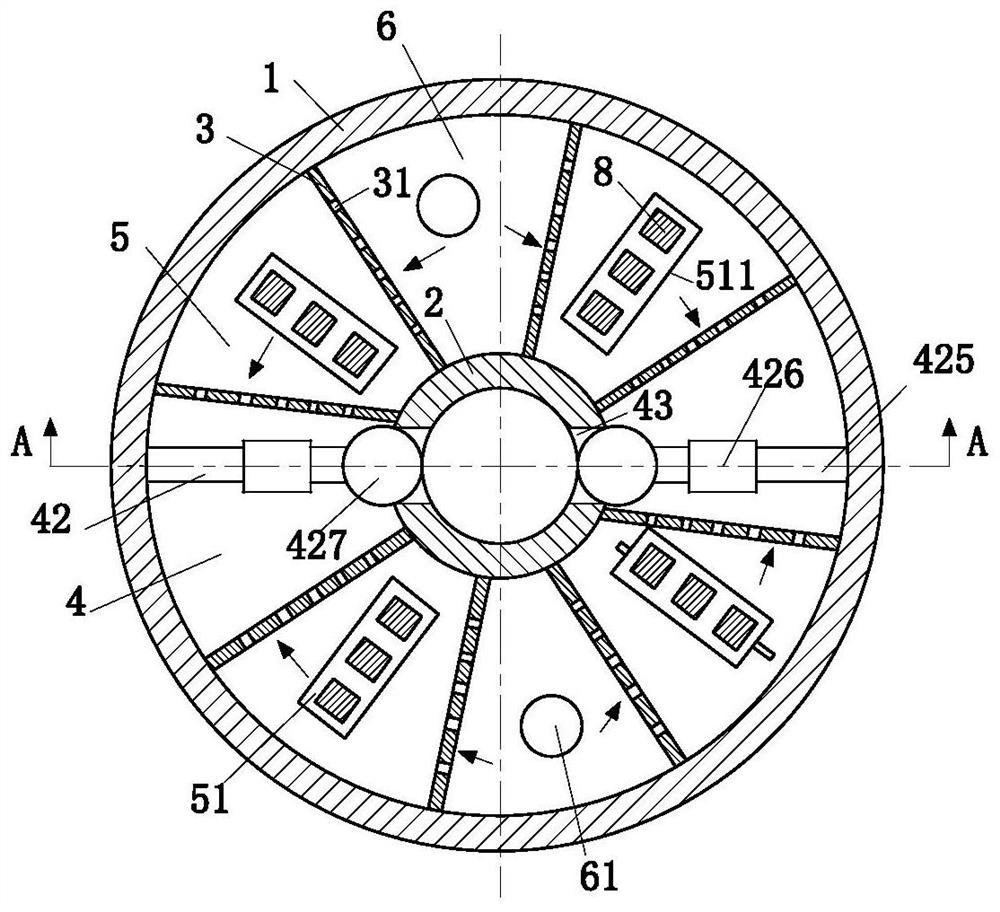

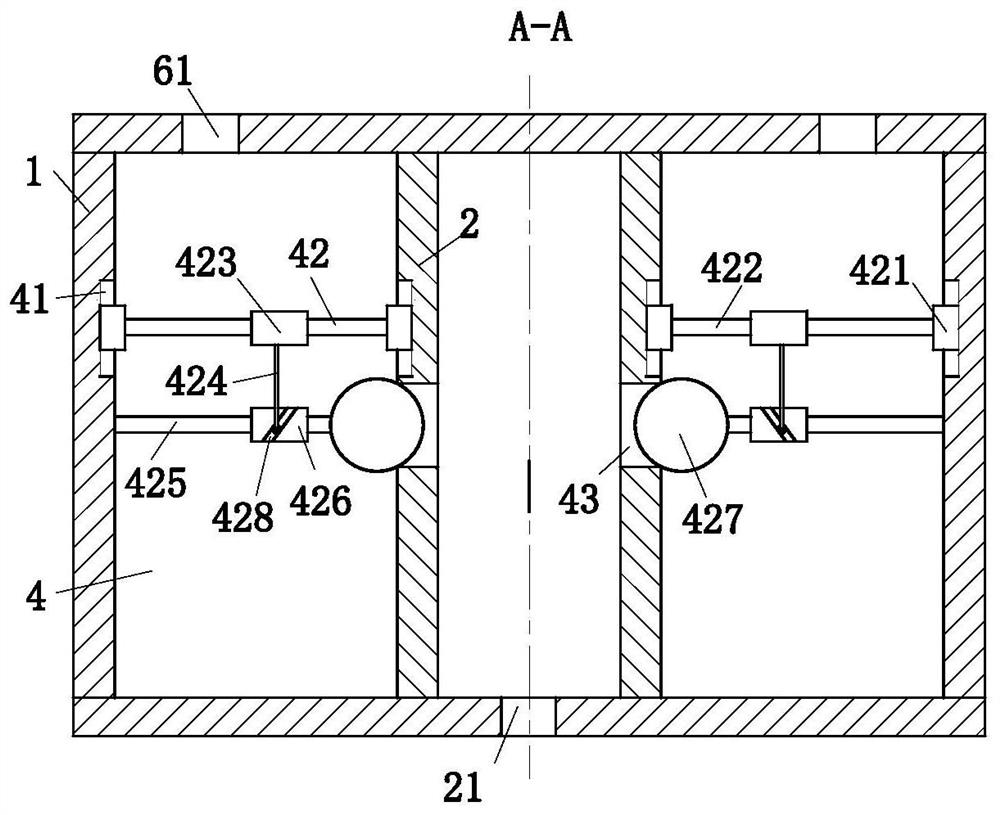

Sensor monocrystalline silicon etching device capable of etching uniformly

ActiveCN109461672AEasy to placeEasy to removeElectric discharge tubesSemiconductor/solid-state device manufacturingUltimate tensile strengthMechanical engineering

The invention relates to the technical field of sensors, in particular to a sensor monocrystalline silicon etching device capable of etching uniformly. A wafer shelf is composed of hollow cylindricalrotating columns and annular plates which are uniformly and fixedly connected with the outer walls of the rotating columns, and the lower end of the rotating column is sealed; a plurality of sliding holes with equal height are uniformly formed in the outer wall of each rotating column between every two adjacent annular plates, and the sliding holes are communicated with the inner walls of the rotating columns; a plurality of sliding chutes corresponding in position are respectively and uniformly formed in opposite surfaces of every two adjacent annular plates; each sliding hole is internally and slidably connected with a clamping plate penetrating the sliding hole, and each clamping plate is used for fixing a monocrystalline silicon wafer; and each clamping plate is slidably connected withthe sliding chutes, corresponding in the position, on the two adjacent annular plates. The sensor monocrystalline silicon etching device provided by the invention has the advantages that the device is easy to use, etching efficiency is improved, etching effect is improved and labor intensity of a worker is reduced.

Owner:蚌埠市龙子湖区金力传感器厂

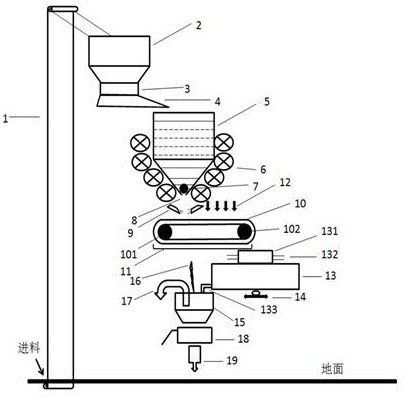

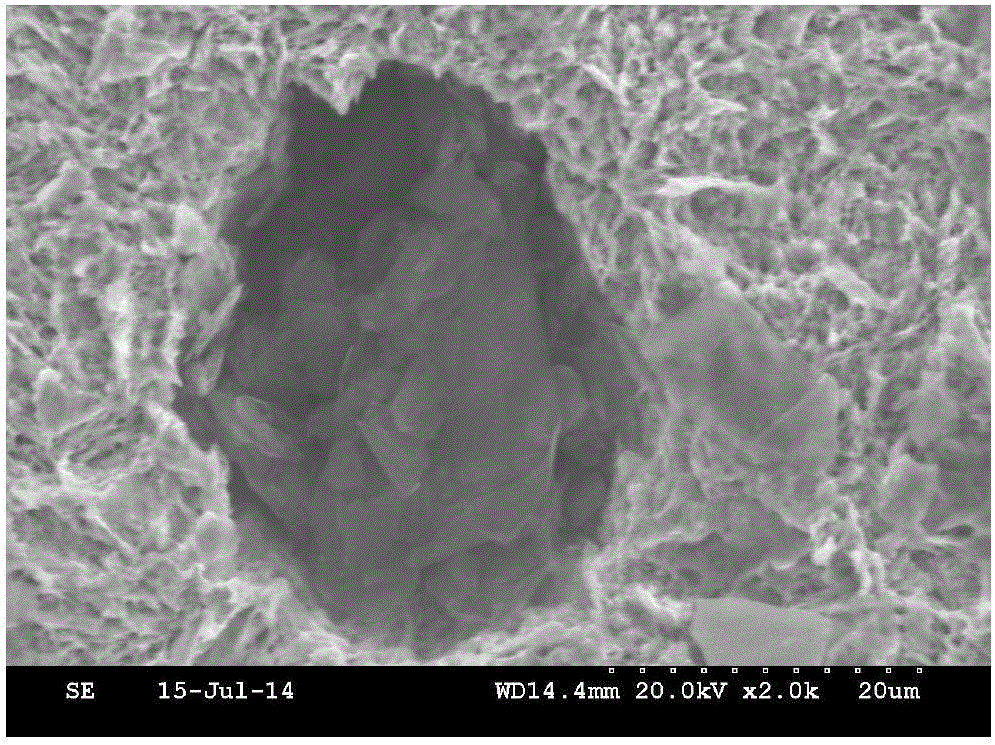

Production system and production process of high-purity quartz raw material

ActiveCN112062131AEffective crack existsFully etchedSilicaGlass shaping apparatusQuenchingMineralogy

The invention belongs to the technical field of production of high-purity quartz raw materials, and particularly relates to a production system and a production process of a high-purity quartz raw material. The production system of the high-purity quartz raw material comprises a raw material conveying device, a melting device, a melt cooling and conveying device, an acid pickling device, a centrifugal machine, a vacuum drying furnace and a vacuum packaging machine, and can be used for melting and purifying quartz mineral powder with the purity of 3-4N to prepare the 5-6N high-purity quartz rawmaterial. The production process comprises the following main steps: charging, heating and melting of materials, flowing out of a melt, water quenching and air cooling, transporting of water-quenchedparticles, pickling, solid-liquid separation, drying and packaging. The system and the process designed by the invention are beneficial to fully damaging the structure of the quartz mineral raw material and exposing impurities so as to be beneficial to acid pickling and impurity removal.

Owner:QILU UNIV OF TECH +1

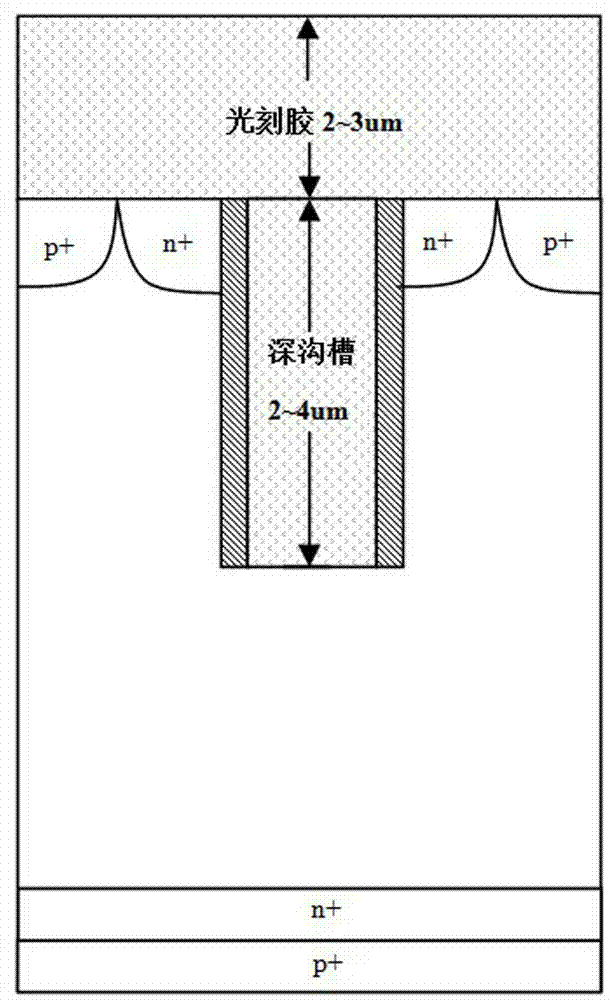

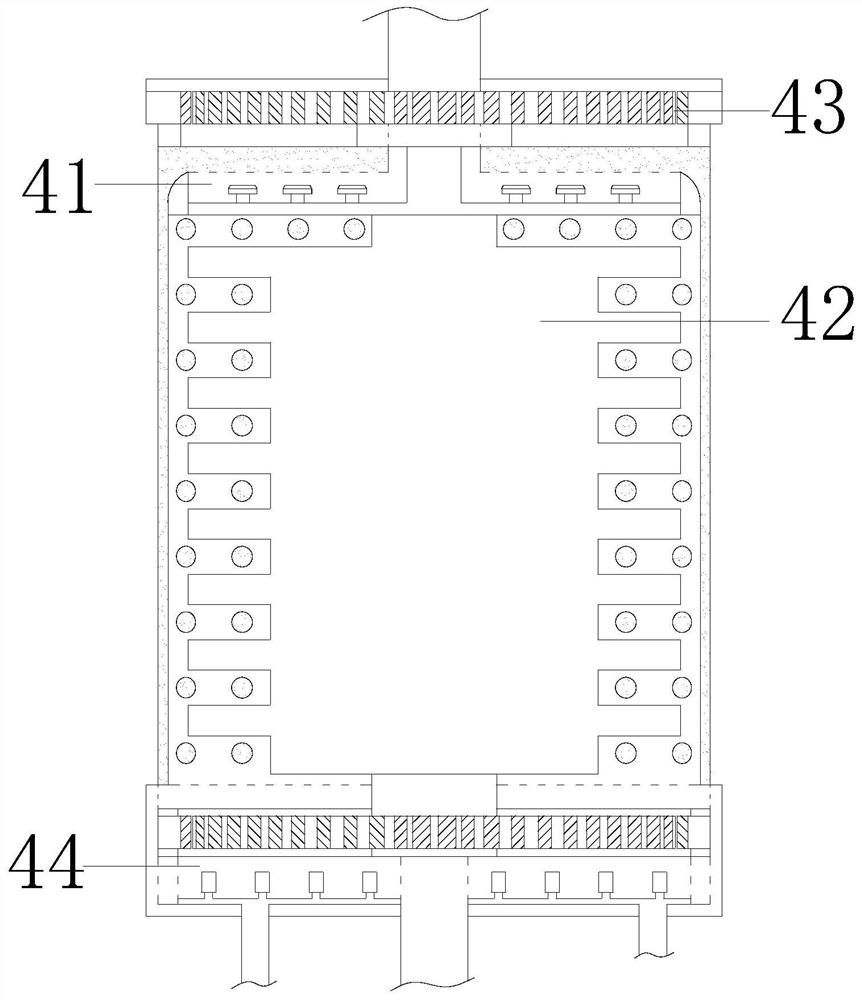

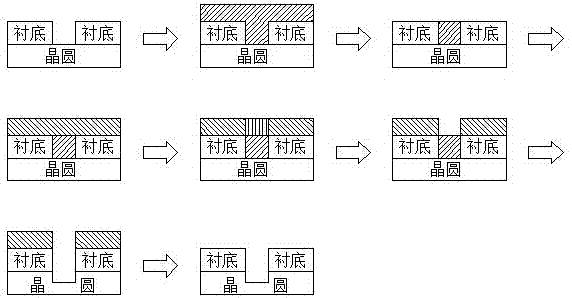

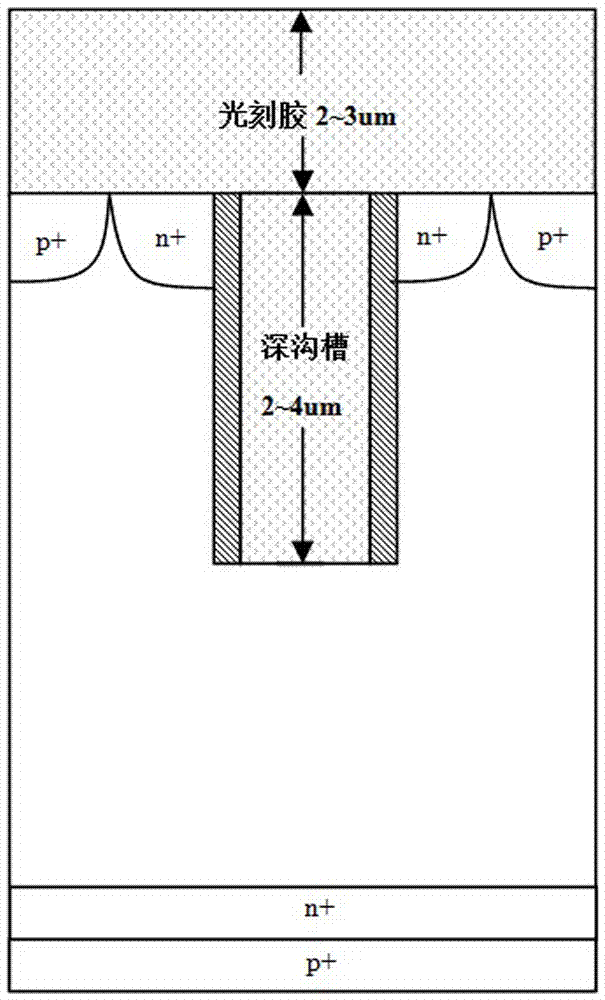

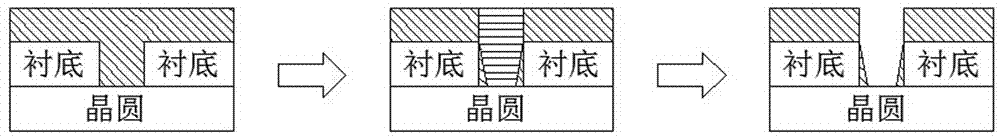

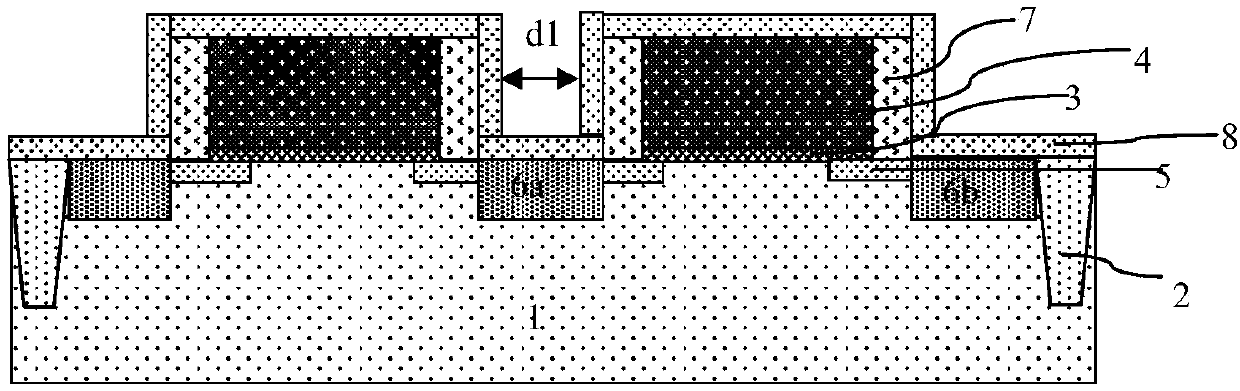

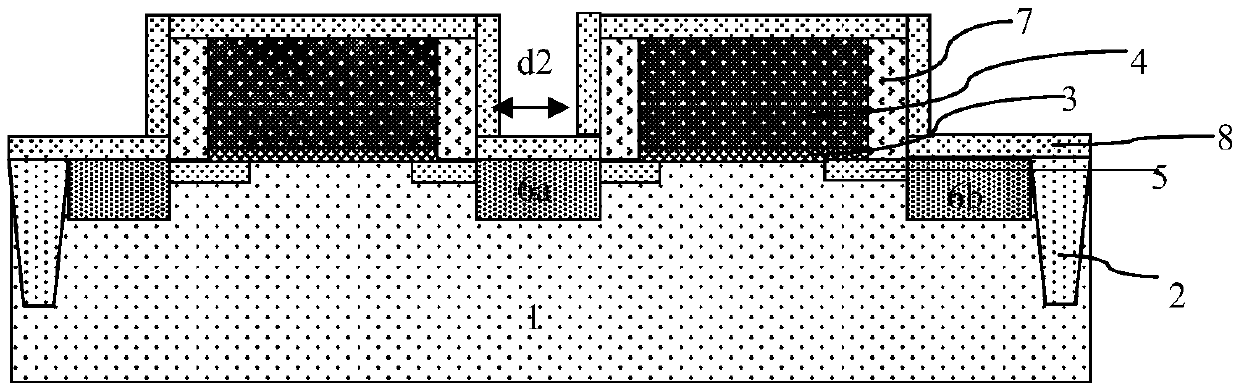

Insulated gate bipolar transistor (IGBT) deep-trench photolithographic process

ActiveCN104505339AFully etchedRegular etchingPhotomechanical apparatusSemiconductor/solid-state device manufacturingEtchingEngineering

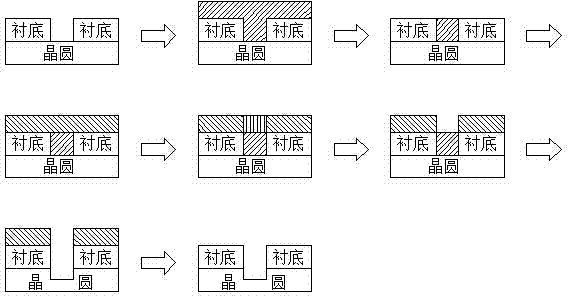

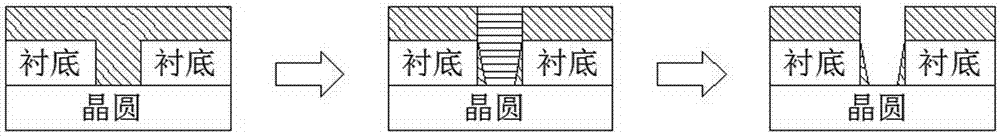

The invention relates to an insulated gate bipolar transistor (IGBT) deep-trench photolithographic process, and belongs to the field of microelectronics. The IGBT deep-trench photolithographic process aims to solve the problem of insufficient photoetching of patterns at the bottom of a deep trench. The process comprises the following steps: (1), coating an organic material on the surface of a substrate and in the deep trench, wherein the organic material is insoluble in a developer and can be etched; (2), removing the organic material on the surface of the substrate to make the remaining organic material to be filled in the deep trench; (3), coating photoresist on the surface of the substrate and the surface of the organic material; (4), exposing the photoresist; (5), removing the photoresist on the deep trench by using the developer; (6), etching the organic material in the deep trench and a wafer at the bottom of the deep trench; and (7), removing the photoresist on the surface of the bottom of the substrate to complete the etching of the IGBT deep trench. The IGBT deep-trench photolithographic process has the advantages that the organic material is filled in the IGBT deep trench, so that sufficient and regular etching of the bottom of the deep trench can be realized.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

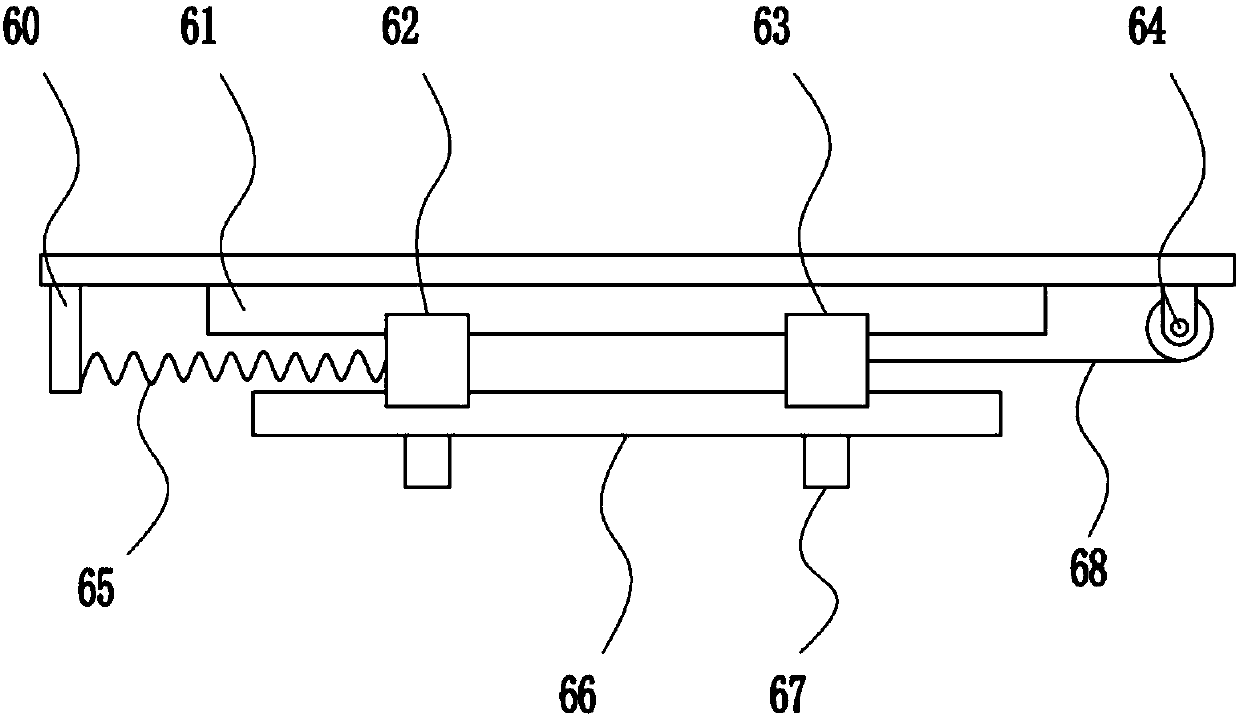

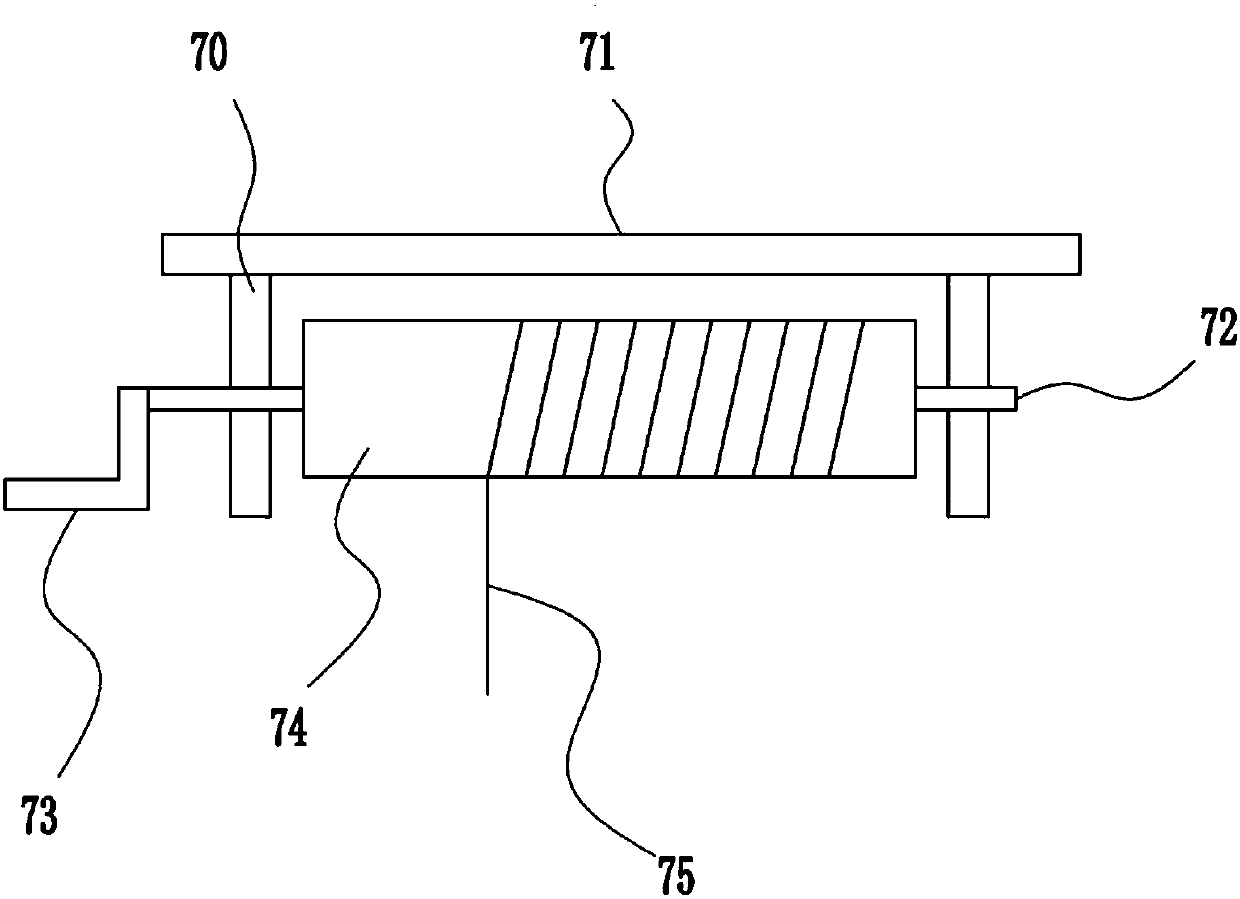

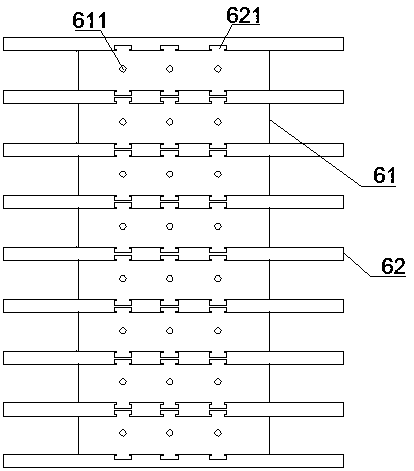

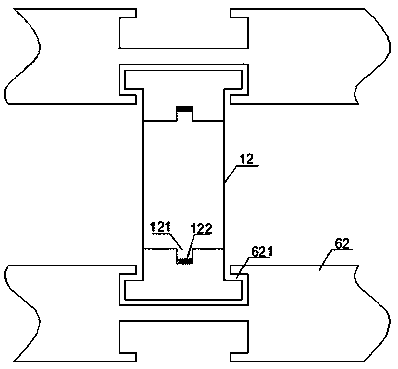

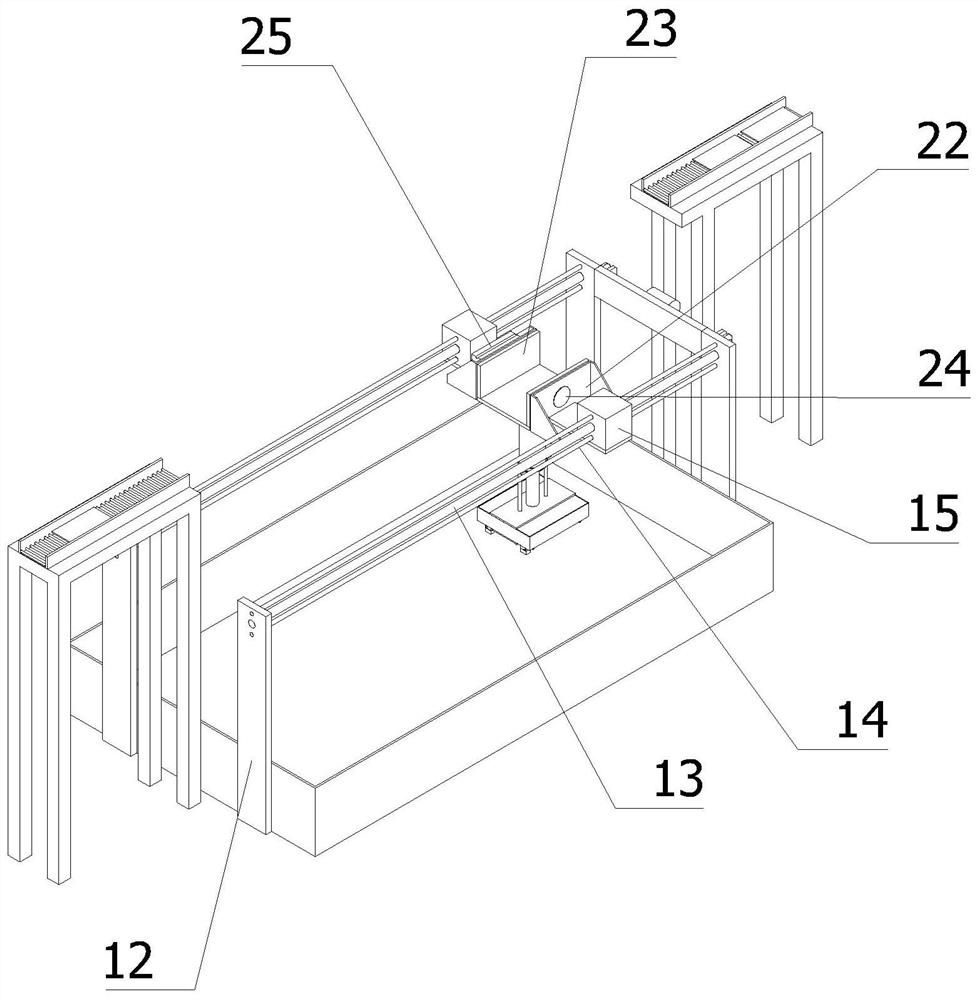

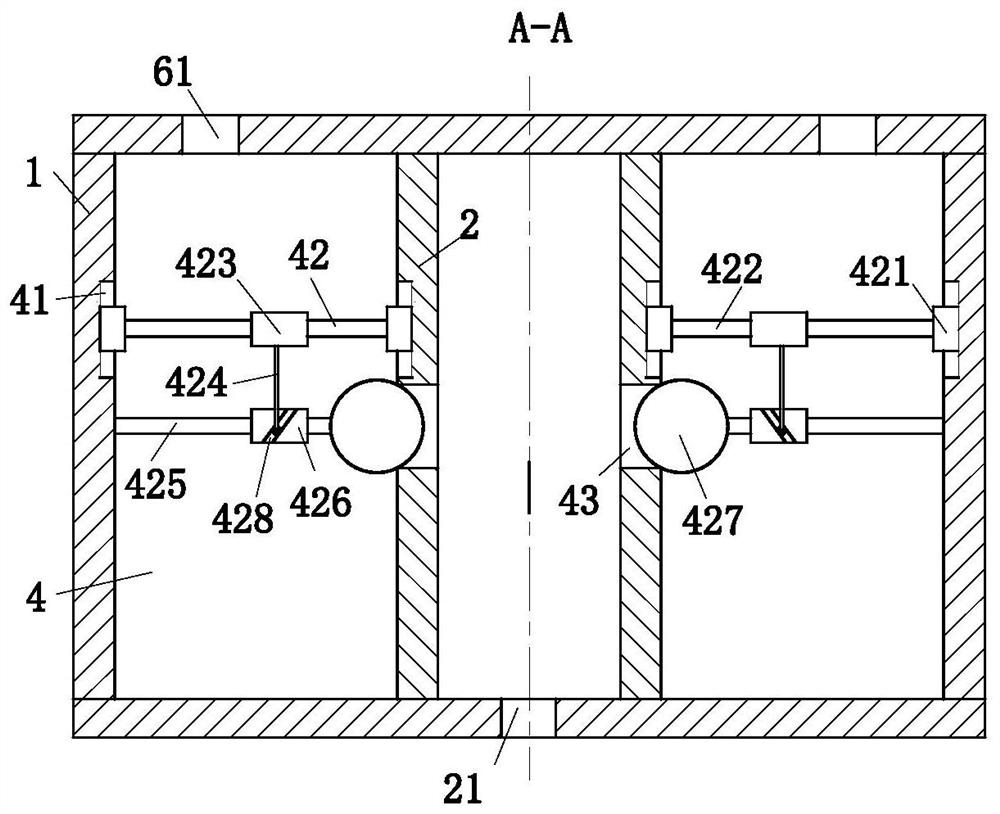

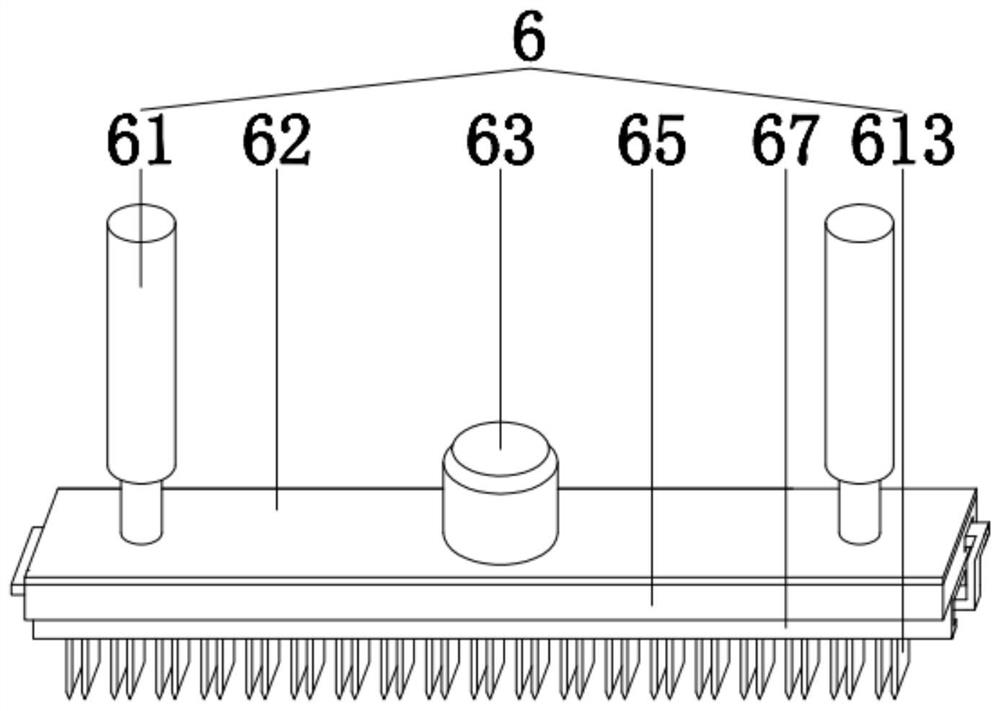

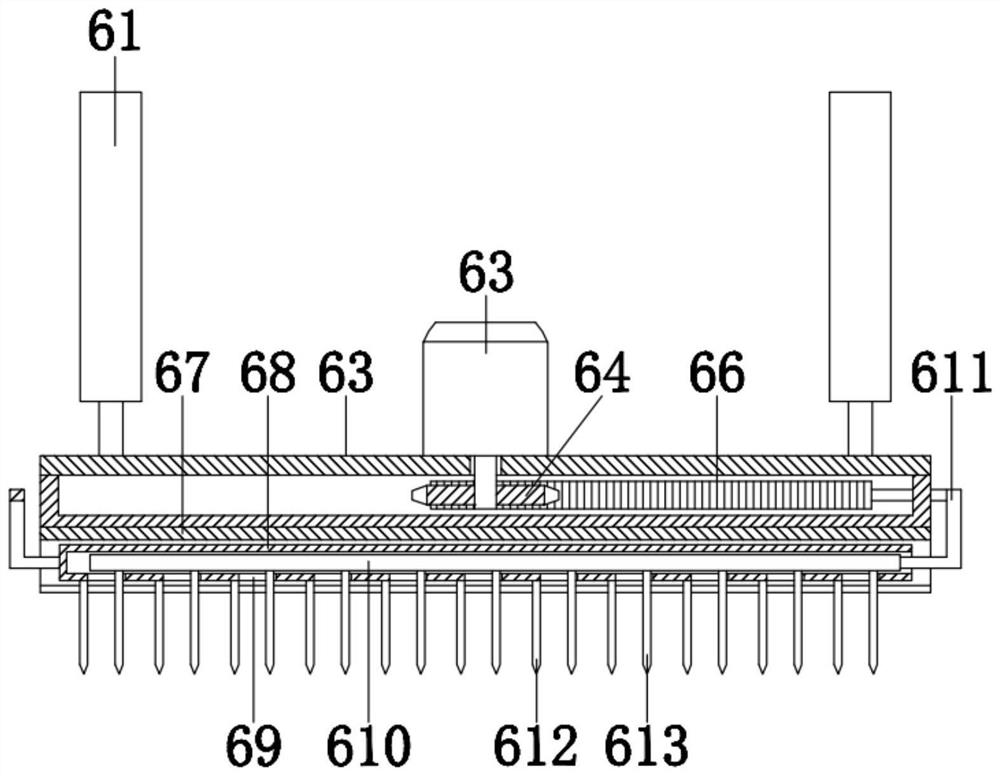

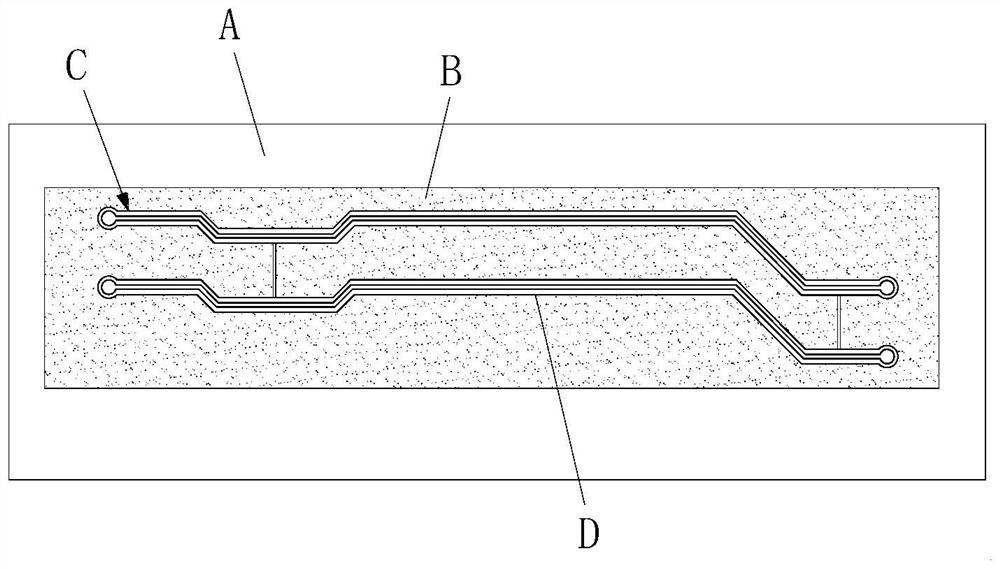

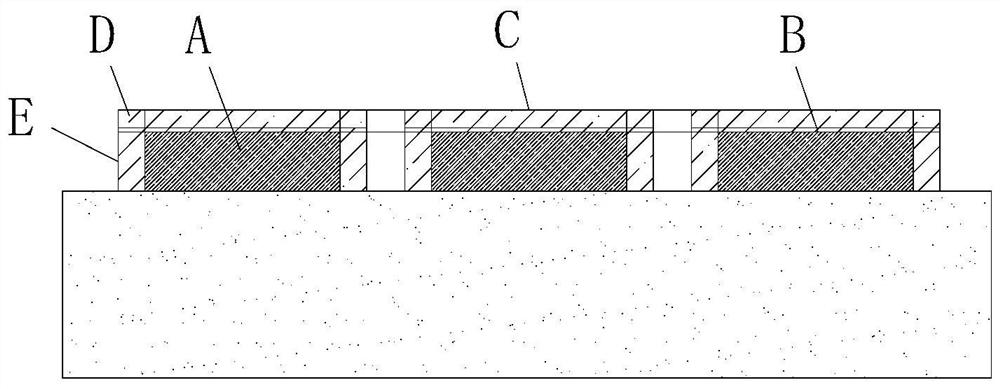

Printed circuit board etching device and method

InactiveCN113473730AFully etchedSolve technical problems of etchingConductive material chemical/electrolytical removalStructural engineeringMechanical engineering

The invention relates to the technical field of circuit board processing, in particular to a printed circuit board etching device which comprises a feeding conveyor; a discharging conveyor; an etching box; and a positioning, overturning and conveying mechanism. The positioning, overturning and conveying mechanism comprises two groups of translation assemblies arranged on the two sides above the etching box, a synchronous assembly is arranged between the two translation assemblies, an overturning frame is arranged between the two translation assemblies, the two sides of the overturning frame are in transmission connection with the working end of each translation assembly, and a lifting plate is arranged at the bottom of the overturning frame; and two clamping parts are arranged at the top of the lifting plate, each clamping part comprises a [-shaped frame, first synchronous wheels are arranged on the two sides of the interior of each [-shaped frame, and a plurality of protruding parts are arranged on the exterior of each synchronous belt. A circuit board is driven to translate repeatedly through the protruding parts arranged on the two first synchronous belts, so that the circuit board is fully etched during etching, and the etching precision and integrity of the circuit board are improved.

Owner:山西汇诚晋海科技有限公司

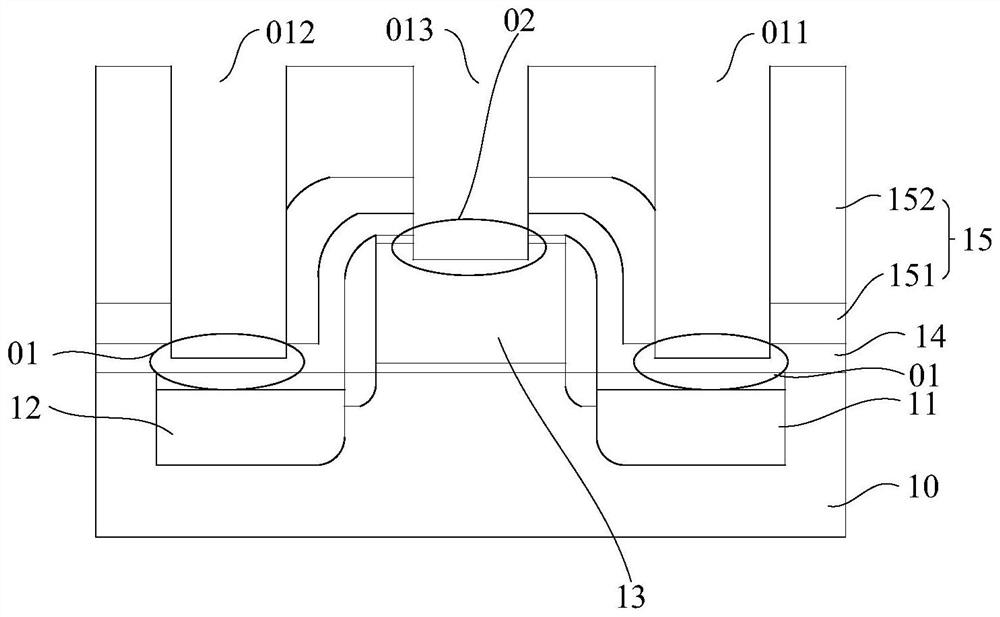

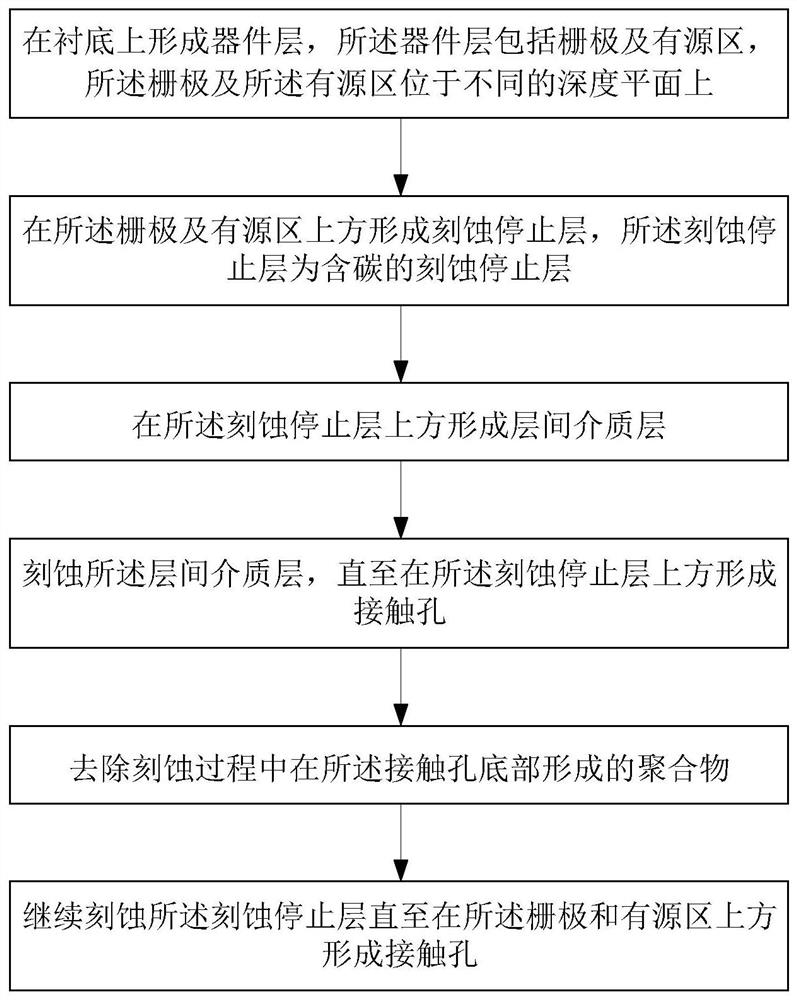

Contact hole etching method of CMOS device and CMOS device manufacturing method

PendingCN114843221AFully etchedNo over-etchingTransistorSemiconductor/solid-state device manufacturingCarbon layerCMOS

Owner:SIEN QINGDAO INTEGRATED CIRCUITS CO LTD

Method for removing suspension copper in blind hole of circuit board

InactiveCN105555062AFully etchedNo etching abilityPrinted element electric connection formationChemical industryEtching

The invention relates to a method for removing suspension copper in a blind hole of a circuit board, belonging to the technical field of chemical industry. The method comprises the following steps of (1) respectively preparing a liquid A and a liquid B, wherein the liquid A comprises an acidic or alkaline substance and a wetting agent, and the liquid B comprise one or more of hydrogen peroxide, peroxysulphate, nitrate, hypochlorite, copper sulfate and ammonium chloride substances; (2) respectively heating the liquids obtained in the step (1) to be 20-60 DEG C; and (3) immersing a workpiece with suspension copper in the blind hole in the liquid A for 1 to 10 minutes, taking out the workpiece, dropping the liquid for several seconds, immersing the workpiece in the liquid B for 1 to 10 minutes, and finally washing and drying the workpiece. By the method, chemical etching can be carried out on the suspension copper in the blind hole, and no etching is carried out on copper outside the hole and copper at the bottom of the hole. The process is simple, economic and efficient.

Owner:GUANGDONG UNIV OF TECH

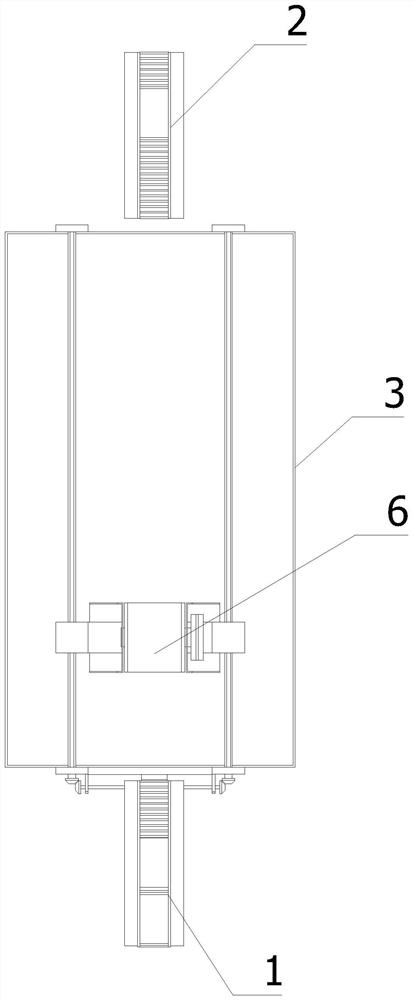

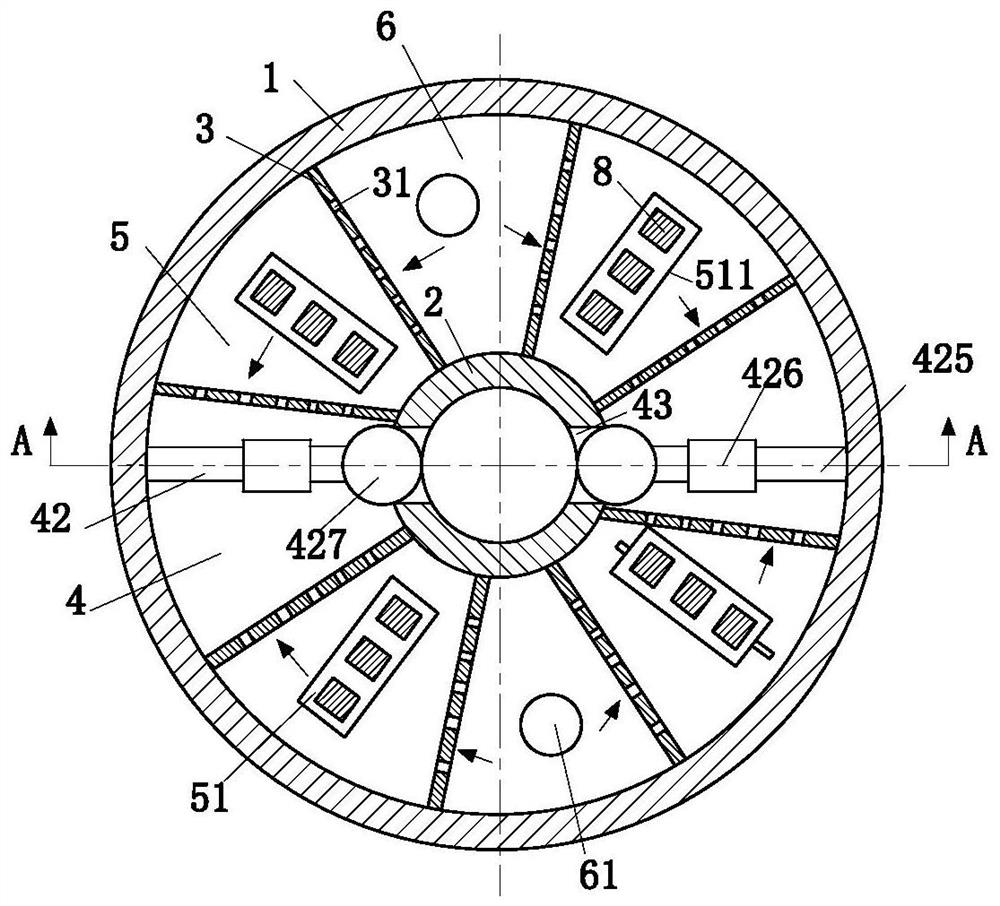

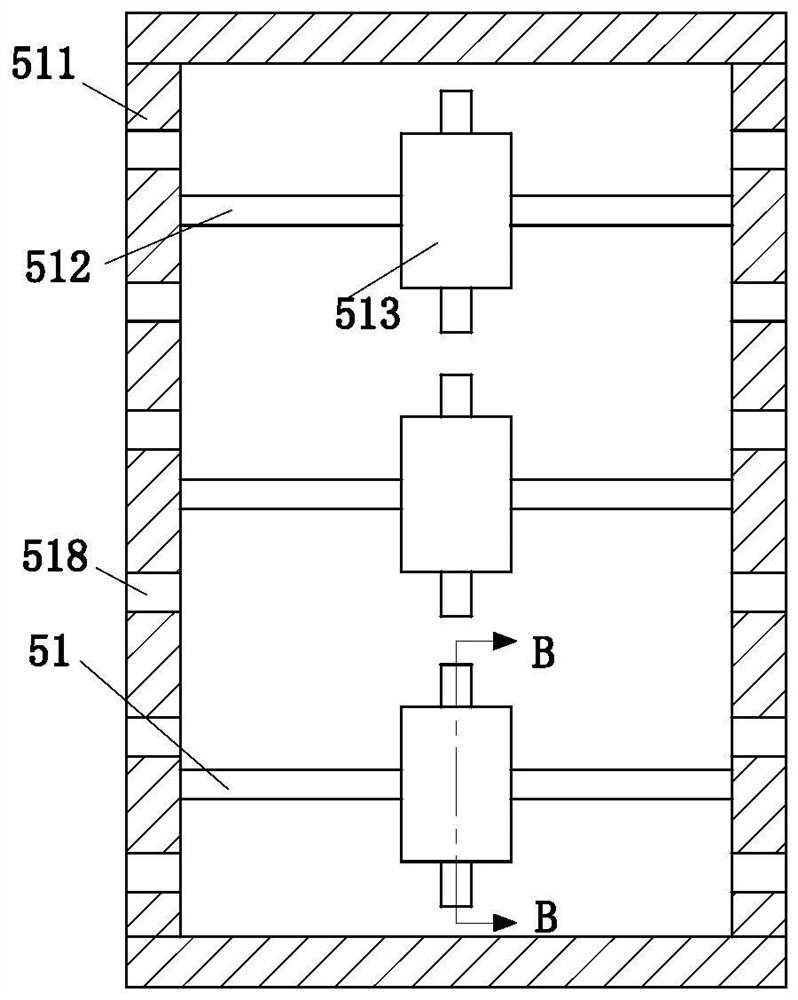

Sensor monocrystalline silicon etching device

InactiveCN113337895AFully etchedAchieve chemical etchingPolycrystalline material growthAfter-treatment detailsEtchingChemical reaction

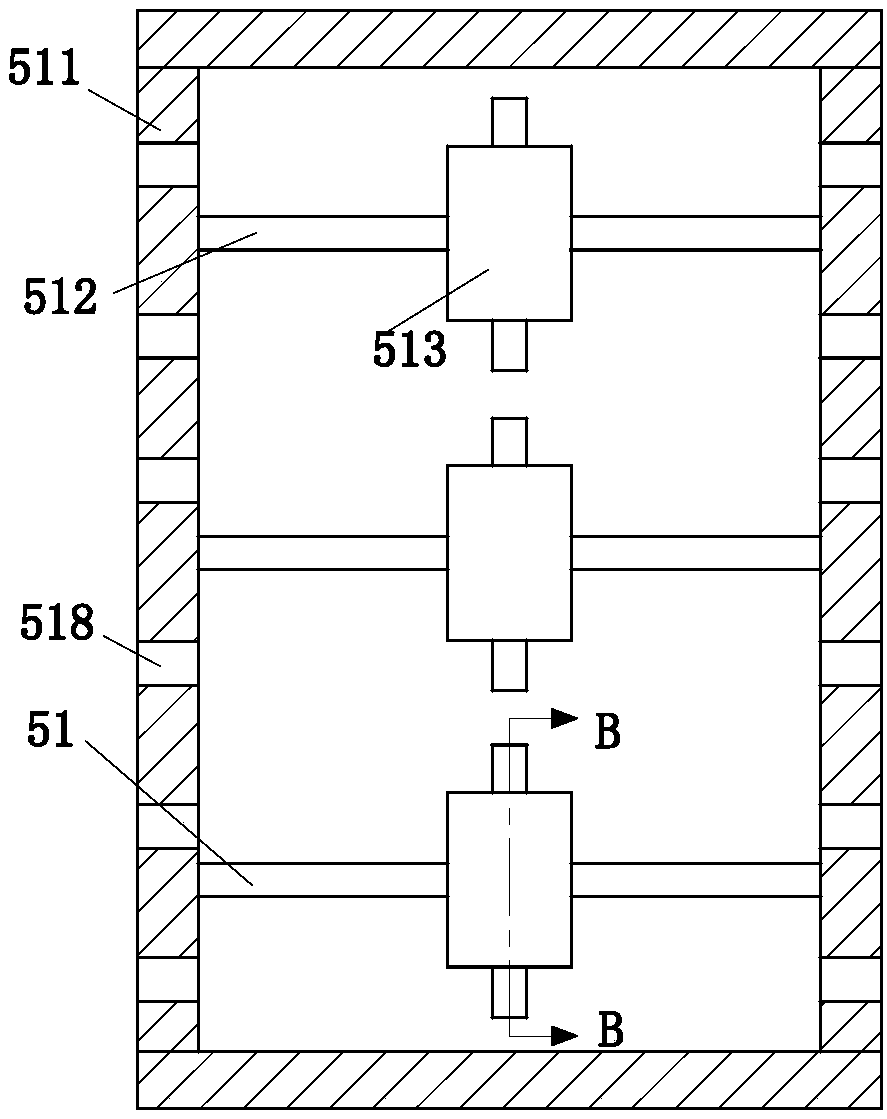

The invention discloses a sensor monocrystalline silicon etching device which structurally comprises an etching mechanism, a gas source chamber, a vacuum pump and a driving motor, wherein the lower end of the gas source chamber is connected with a flange at the upper end of the etching mechanism, the vacuum pump is arranged on the right side below the gas source chamber, the driving motor is arranged on the left side below the gas source chamber, the driving motor drives a reaction chamber mechanism in the etching mechanism to rotate in a shell, the gas source chamber conveys gas through a gas supply port, the gas is conveyed into a wafer rack mechanism through a gas distribution net of the gas supply mechanism, the gas generates glow discharge under the action of an electromagnetic coil, the reaction gas and an etched material generate a chemical reaction, and the wafer rack rotates during etching, so that an etched material can be etched more sufficiently, volatile compounds which can be taken away by a gas suction mechanism are generated, chemical etching is realized, and the vacuum pump sucks the volatile compounds in the gas suction mechanism through the gas suction pipeline to reach the maximum vacuum degree.

Owner:徐丽红

A method for removing suspended copper in blind holes of circuit boards

InactiveCN105555062BFully etchedNo etching abilityPrinted element electric connection formationChemical industryHypochlorite

The invention relates to a method for removing suspension copper in a blind hole of a circuit board, belonging to the technical field of chemical industry. The method comprises the following steps of (1) respectively preparing a liquid A and a liquid B, wherein the liquid A comprises an acidic or alkaline substance and a wetting agent, and the liquid B comprise one or more of hydrogen peroxide, peroxysulphate, nitrate, hypochlorite, copper sulfate and ammonium chloride substances; (2) respectively heating the liquids obtained in the step (1) to be 20-60 DEG C; and (3) immersing a workpiece with suspension copper in the blind hole in the liquid A for 1 to 10 minutes, taking out the workpiece, dropping the liquid for several seconds, immersing the workpiece in the liquid B for 1 to 10 minutes, and finally washing and drying the workpiece. By the method, chemical etching can be carried out on the suspension copper in the blind hole, and no etching is carried out on copper outside the hole and copper at the bottom of the hole. The process is simple, economic and efficient.

Owner:GUANGDONG UNIV OF TECH

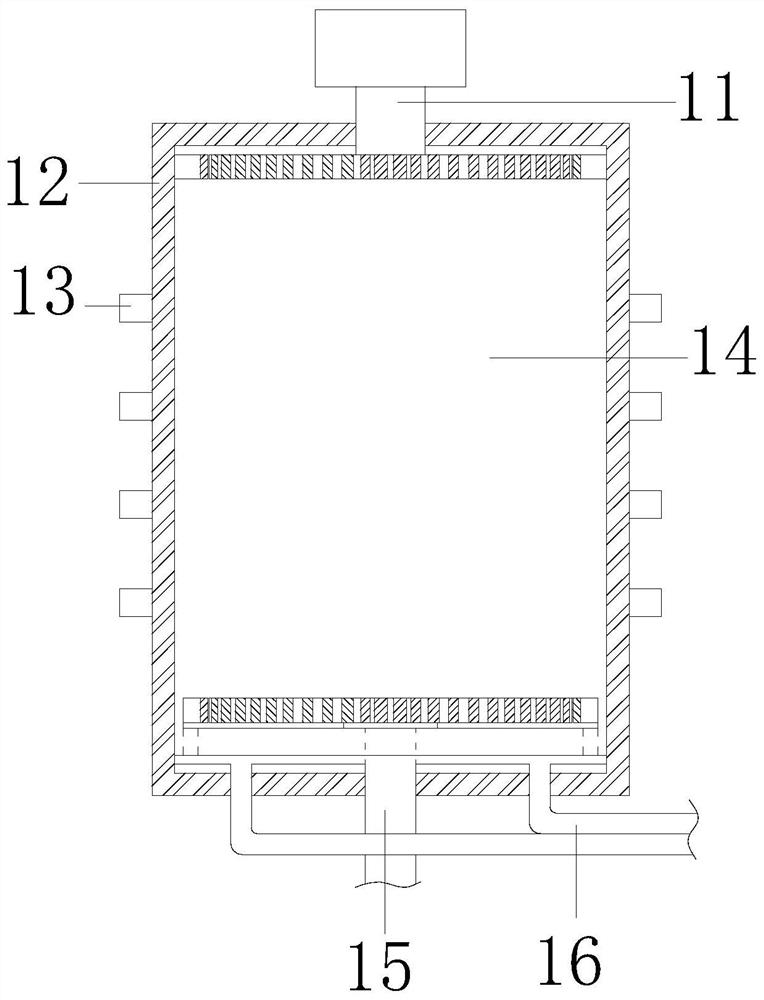

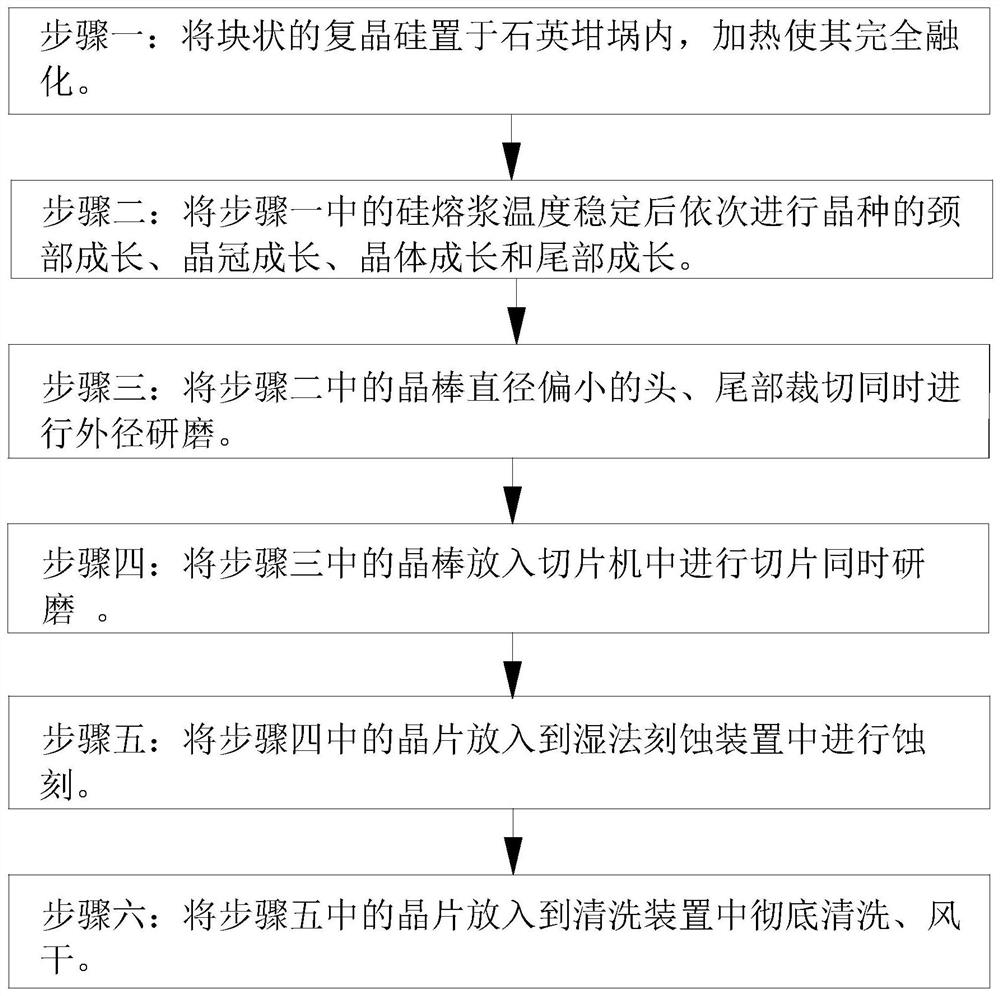

A wafer production process

ActiveCN108754612BFully etchedImprove etching effectPolycrystalline material growthAfter-treatment detailsEtchingWafer

The invention belongs to the technical field of semiconductor manufacturing and in particular discloses a wafer production process. The process adopts a wet etching device, and the wet etching devicecomprises a cylinder I, a cylinder II and baffles, wherein the cylinder II is coaxially arranged inside the cylinder I; the baffles are circumferentially arranged inside the cylinder I; the cylinder Iis segmented into a sealing bin I, a sealing bin II and a sealing bin III by the baffles. According to the wet etching device, due to mutual match of a sliding telescopic rod II sleeving with a spring I and a spiral plate, the sliding telescopic rod II retracts in the vibrating process of the spiral plate, the wafer produces displacement, and the wafer is clamped again by the clamping unit afterthe displacement, so that the wafer is uniformly etched by the etching solution. Meanwhile, due to vibration of the spiral plate, etched and precipitated particles are separated from the wafer, and contact between the etching solution and the wafer is enlarged, so that the etching effect is improved.

Owner:深圳市克拉尼声学科技有限公司

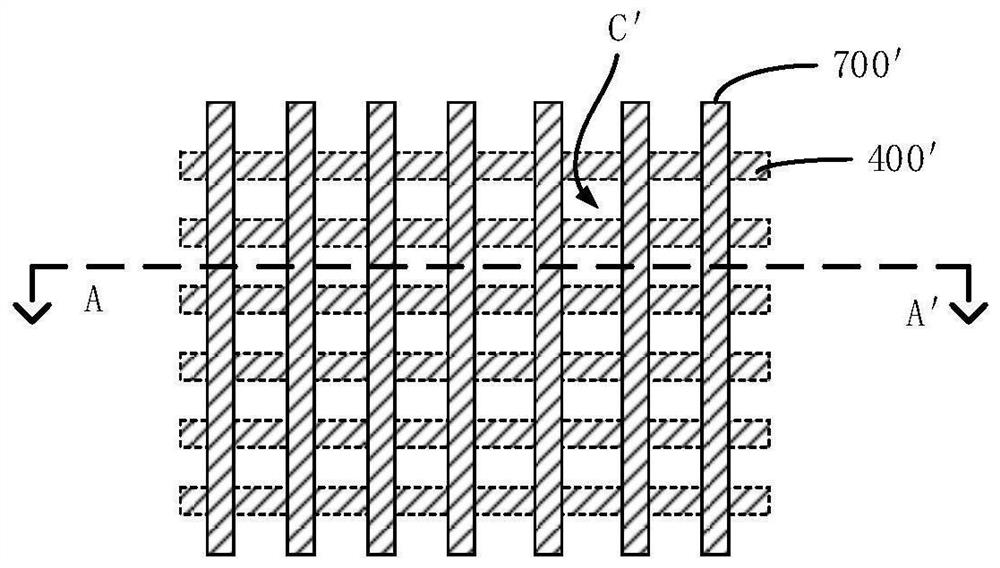

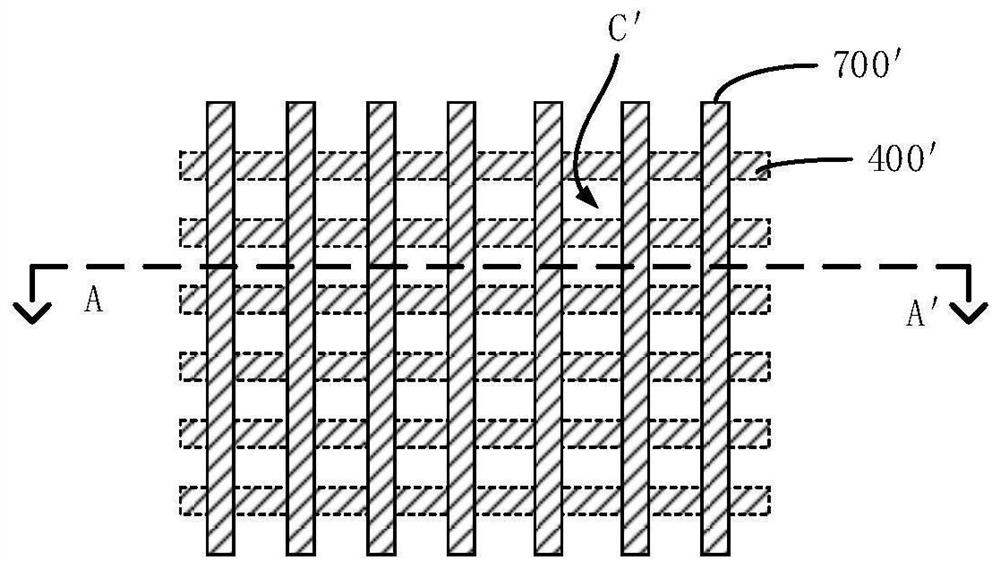

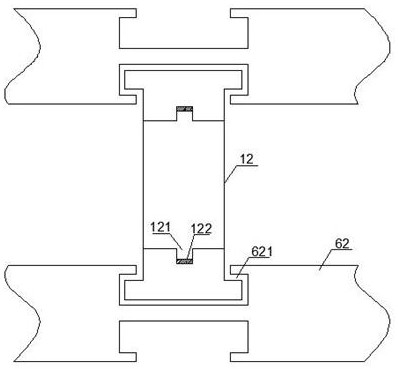

Semiconductor device and capacitor hole preparation method of semiconductor device

ActiveCN112652529BReduce thicknessPrevent collapseTransistorSemiconductor/solid-state device manufacturingCapacitanceDevice material

The present application relates to a preparation method of a capacitor hole and a semiconductor device including the capacitor hole. The preparation method includes: forming a stacked first dielectric layer, a first mask layer, a first pattern layer, a second dielectric layer, and a second dielectric layer on a substrate. A mask layer and a second pattern layer; the first pattern layer and the second pattern layer form a grid; a third mask layer is formed on the second pattern layer to cover the second mask layer of the edge area and expose the middle area the second mask layer; etch the exposed second mask layer until the second dielectric layer is exposed; etch the exposed second dielectric layer until the first pattern layer and the first mask layer are exposed; remove the third mask film layer, etch the exposed first mask layer and the second pattern layer and the second mask layer in the edge area until the first dielectric layer is exposed, the etching selectivity ratio of the second mask layer and the first mask layer If it is greater than 1, the exposed first dielectric layer is etched to form a capacitor hole. In the present application, while etching the first mask layer in the middle area, the line height in the edge area is etched and reduced.

Owner:CHANGXIN MEMORY TECH INC

A method for preparing porous carbon by stepwise activation of biomass

ActiveCN109231204BWell-developed pore structureFully etchedCarbon compoundsPorous carbonEnvironmental engineering

The invention discloses a method for preparing porous carbon by stepwise activation of biomass. The method comprises the following preparation process with the steps: after the biomass is crushed anddried and is mixed with an activating agent, activating treatment is carried out under an inertial atmosphere, and the activating agent and the biomass generate activating reaction to initially form biochar with certain porosity; the biochar and the activating agent are dipped uniformly and mixed again, then the activating agent enters pores of the biochar fully, the effective utilization rate ofthe activating agent with good dispersity is greatly increased in the process of secondary activation, and a carbon skeleton can be fully etched to generate a large amount of micropores and mesopores,so that the porous carbon material with a developed porous structure also can be formed even though a little amount of activating agent is used. The method disclosed by the invention has wide application prospect in the fields of catalysis, adsorption and energy storage and the like so as to realize green preparation of the porous carbon material by the biomass and be conductive to push the high-value utilization progress of the biomass.

Owner:HUAZHONG UNIV OF SCI & TECH

Wet etching apparatus for wafer

InactiveCN108695214AIncrease contact areaImprove etching effectSemiconductor/solid-state device manufacturingMechanical engineeringSemiconductor

The invention, which belongs to the field of semiconductor technology, in particular relates to a wet etching apparatus for a wafer. The wet etching apparatus is composed of a cylinder I, a cylinder II, and baffles. The cylinder II is installed inside the cylinder I coaxially. The baffles are arranged inside the cylinder I in a circumferential direction and divide the cylinder I into a sealing chamber I, a sealing chamber II, and a sealing chamber III. According to the invention, on the basis of mutual cooperation of a sliding telescopic rod II sleeved by a spring I and a spiral plate, the sliding telescopic rod II stretches and contracts during the vibration process of the spiral plate and a wafer moves; and after the displacement, a clamping unit clamps the wafer again and thus an etching solution etches the wafer uniformly. Meanwhile, etched precipitated particles are separated from the wafer based on vibration of the spiral plate, so that contact between the etching solution and the wafer is increased and thus the etching effect is improved.

Owner:如东汇盛通半导体科技有限公司

Silicon chip etching method

InactiveCN101179021APrecise controlFully etchedSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingSilicon chipEtching

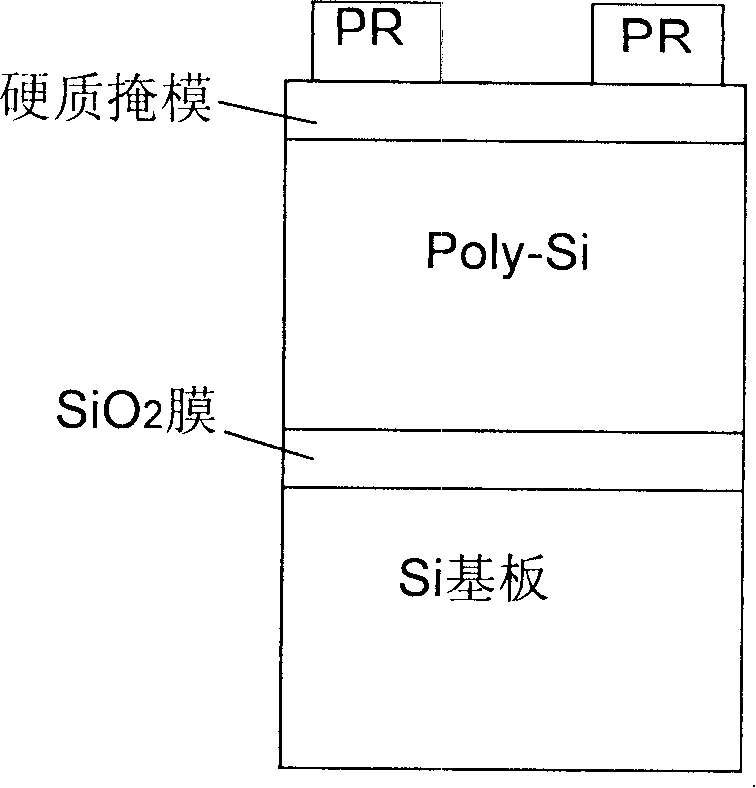

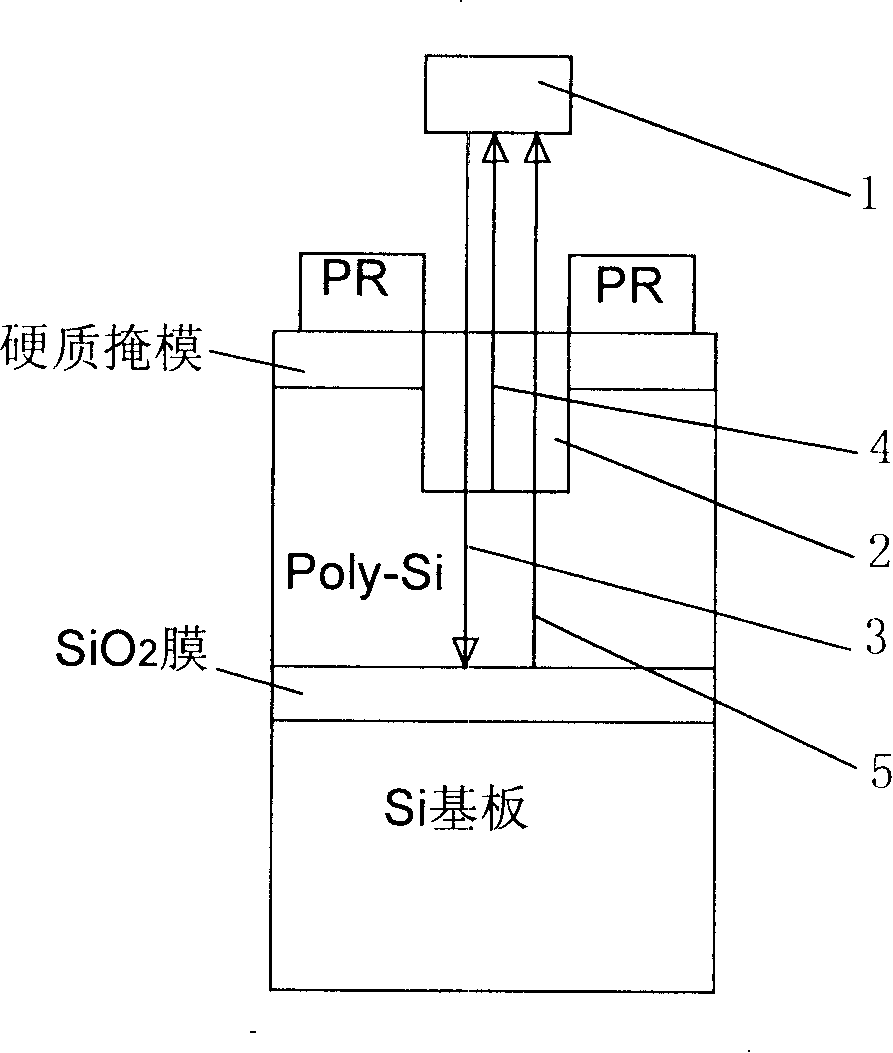

The invention discloses a method for etching a silicon wafer. In the method, the silicon wafer is etched by process gas, which lower layer is an oxide layer, and the process of etching the silicon wafer is detected by a laser detector. The laser detector transmits a laser beam to an etching slot on the silicon wafer and then the lower surface of the silicon wafer and the bottom of the etching slot respectively reflect one laser beam, and thus the depth of the etching slot is analyzed by the two reflected laser beams. When the etching depth closes to the upper surface of the oxide layer or when any part of the bottom of the slot formed by etching exposes the upper surface of the oxide layer, the content of oxygen in the process gas is increased with the flow rate of oxygen of 2-50sccm in order to protect the oxide layer. Later, the process of etching can be detected by a spectrum analyzer and also estimated according to the time by experience. The invention can not only fully etch the silicon wafer but also fully protect the oxide layer beneath the silicon wafer. And the invention is especially suitable for the etching of polysilicon besides the etching of other silicon wafers.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

Titanium chip alkaline etching and smoothing process

The invention discloses a titanium chip alkaline etching and smoothing process. The titanium chip alkaline etching and smoothing process includes the steps that 1, titanium chips are put into a cleaning tank; 2, the cleaning tank is lifted into an alkaline water tank with the temperature of 55-65 DEG C and washed through alkaline cleanout fluid for 5-6 minutes under the high temperature; 3, the cleaning tank is lifted into a first clean water tank and soaked for 10-15 minutes and is lifted out for being dried in the shade for 5-8 minutes; 4, the cleaning tank is lifted into an acidity tank with the temperature of 40-50 DEG C and washed through acid fluid for 3-5 minutes under the high pressure; and 5, the cleaning tank is lifted into a second clean water tank and soaked for 10-15 minutes. The titanium chip alkaline etching and smoothing process is scientific, selected raw materials are configured scientifically, pressing stirring is conducted in the alkaline cleanout fluid preparation process, existing structures of the raw materials can be changed, molecules are dispersed, recombined and fused, alkaline etching can be fully conducted on titanium chips through the cleanout liquid, alkaline etching treatment of the titanium chips can be effectively achieved, the surfaces of the titanium chips are smooth and flat, and the separated-out precipitating amount is reduced; and the situation that an etching reaction is insufficient or severe is avoided, the titanium loss and alkaline consumption are lowered, and the produced cleanout liquid is good in stability and long in service life.

Owner:SUZHOU HAIAN TITANIUM IND CO LTD

Chip processing equipment capable of fully etching wafer

PendingCN114242617APrevent hand skinFully etch and cleanSemiconductor/solid-state device manufacturingConveyor partsPhysicsElectric machinery

The invention relates to the field of chips, in particular to chip processing equipment sufficient in wafer etching, which comprises a box body, a supporting plate, a cleaning tank and an etching tank, the supporting plate is fixedly connected to the top end of the left side wall of the box body, the cleaning tank is mounted on the front side of an inner cavity of the box body, the etching tank is mounted on the rear side of the inner cavity of the box body, and the chip processing equipment further comprises a dustproof shell, the box body is fixedly connected to the top end of the box body; the feeding and discharging mechanism is mounted on the front side of the top end of the inner cavity of the dustproof shell; the diving mechanism is mounted at the top end of the inner cavity of the dustproof shell; the feeding and discharging mechanism comprises two first air cylinders which are installed on the left side and the right side of the top end of an inner cavity of the dustproof shell correspondingly. The top plate is mounted at the output end of the first air cylinder; and the first motor is mounted in the center of the top end of the top plate. According to the invention, automatic feeding and discharging of the wafer are realized, time and labor are saved, hand skin of a worker is prevented from being corroded, in addition, the purpose of fully etching and cleaning the wafer is achieved, the etching effect is strong, and the etching effectiveness is ensured.

Owner:智多多(沈阳)科技有限公司

Semiconductor device, and capacitance hole preparation method thereof

ActiveCN112652529AReduce thicknessPrevent collapseTransistorSemiconductor/solid-state device manufacturingCapacitanceDevice material

The invention relates to a capacitor hole preparation method and a semiconductor device comprising a capacitor hole. The preparation method comprises the following steps: forming a first dielectric layer, a first mask layer, a first pattern layer, a second dielectric layer, a second mask layer and a second pattern layer which are stacked on a substrate; enabling the first pattern layer and the second pattern layer to enclose a grid; forming a third mask layer on the second pattern layer to cover the second mask layer in the edge region and expose the second mask layer in the middle region; etching the exposed second mask layer until the second dielectric layer is exposed; etching the exposed second dielectric layer until the first pattern layer and the first mask layer are exposed; and removing the third mask layer, etching the exposed first mask layer and the second pattern layer and the second mask layer in the edge region until the first dielectric layer is exposed, etching the exposed first dielectric layer until the etching selection ratio of the second mask layer to the first mask layer is greater than 1, and forming a capacitor hole. According to the invention, while the first mask layer in the middle area is etched, the line height of the edge area is etched and reduced.

Owner:CHANGXIN MEMORY TECH INC

Method and apparatus for detecting polysilicon gate etching terminal

ActiveCN100365788CFully etchedGuaranteed Advance ProtectionSemiconductor/solid-state device testing/measurementGratingOxygen

This invention is a kind of end point checking method and checking apparatus of polycrystalline silicon grating etching. The etching process has four steps which have different end point checking method. Bias voltage compensating end point checking predicts the end point of etching process that has relative low etching selecting rate. Use this sensitive method can ensure oxidation layer pre-protected before etching drawing near grate oxygen. Though OES end point checking method, checking etching process of high selecting rate ensures polycrystalline silicon etched fully and grate oxygen layer protected effectively.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

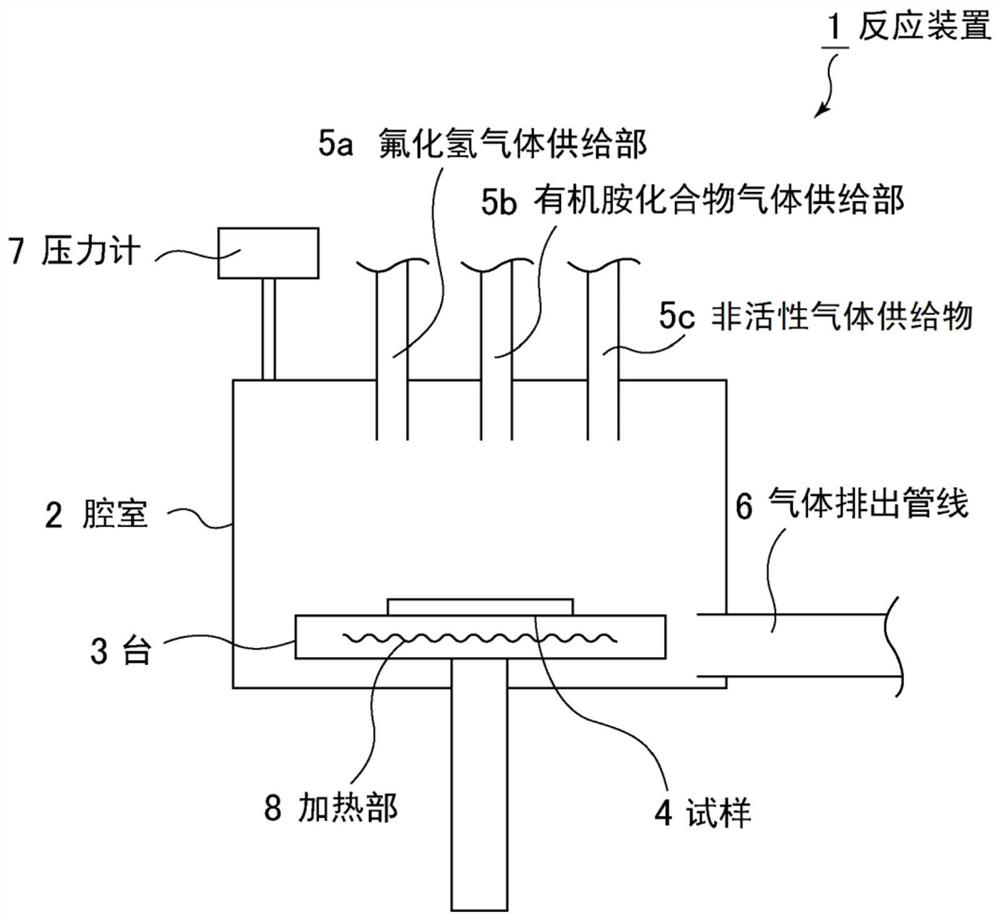

Method and device for etching silicon oxide

PendingCN112534550AFully etchedSemiconductor/solid-state device manufacturingSurface treatment compositionsHydrogen fluoridePhysical chemistry

Owner:CENT GLASS CO LTD

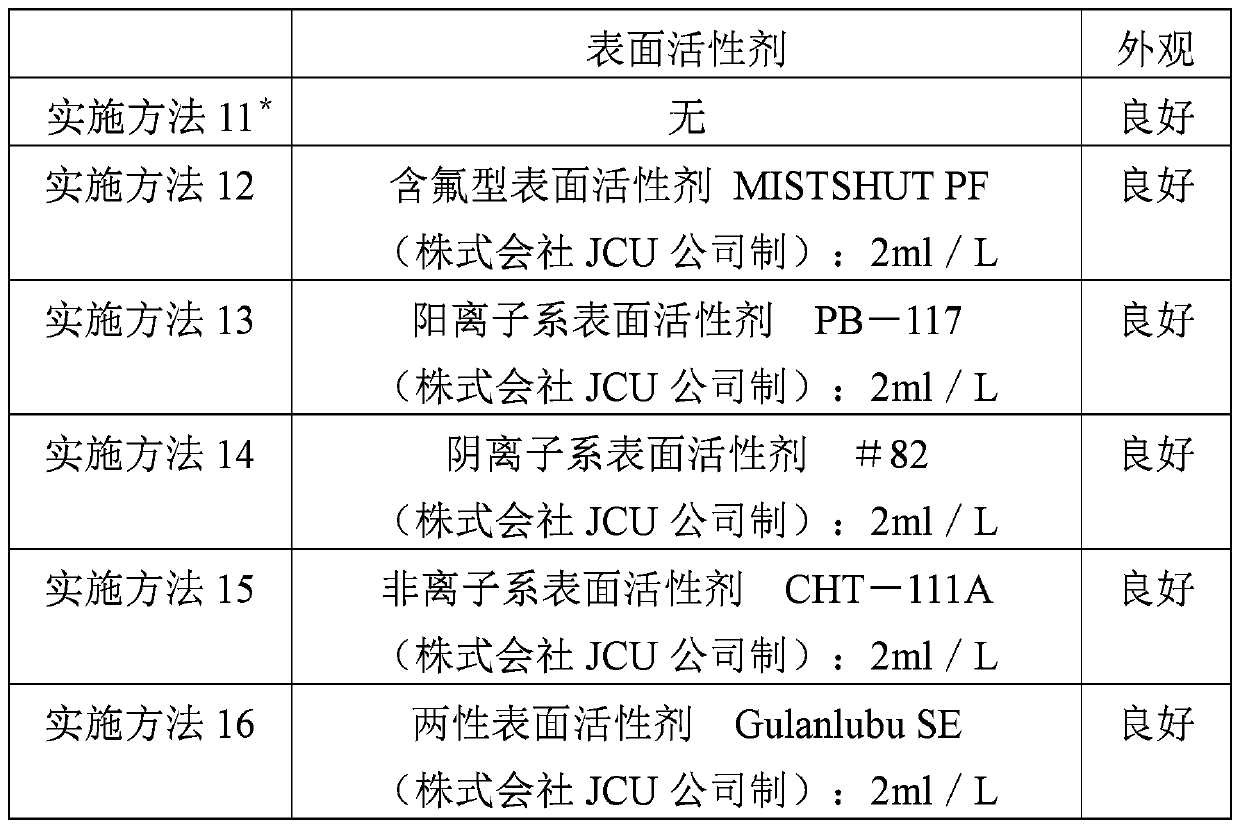

Multi-stage resin surface etching method, and plating method on resin using same

PendingCN110709535AAvoid decompositionEfficient etchingLiquid/solution decomposition chemical coatingPolymer sciencePolymer chemistry

Owner:JCU CORP

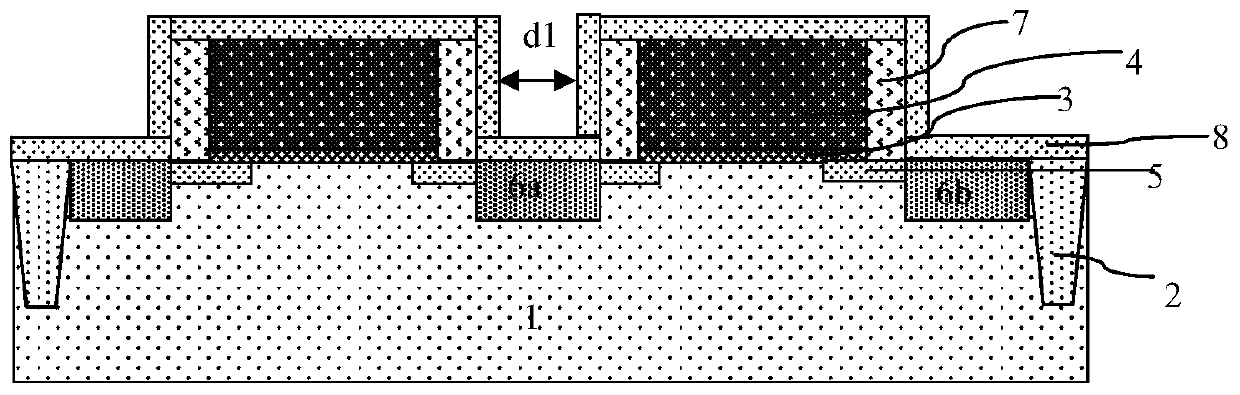

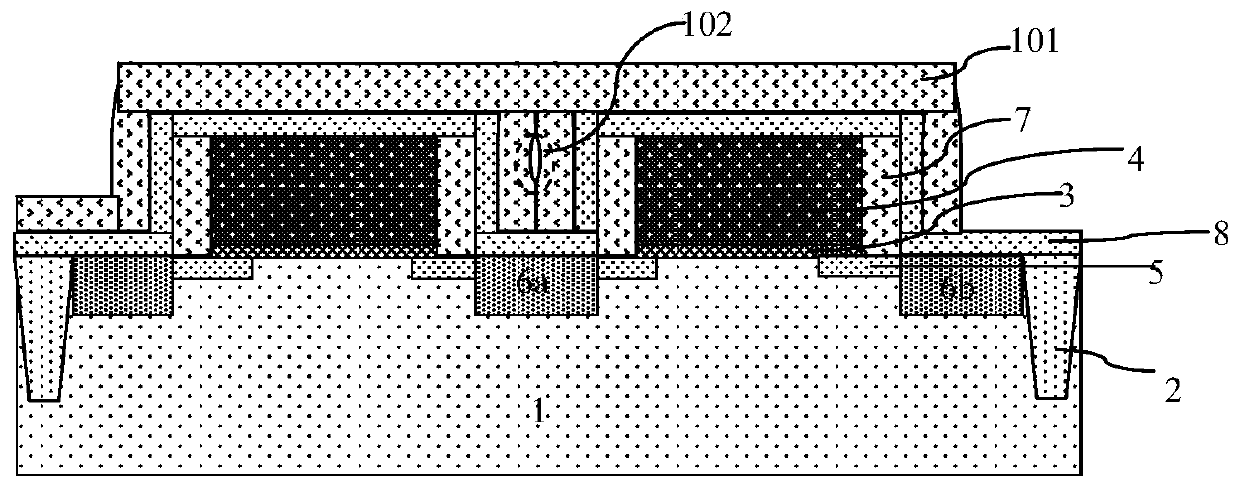

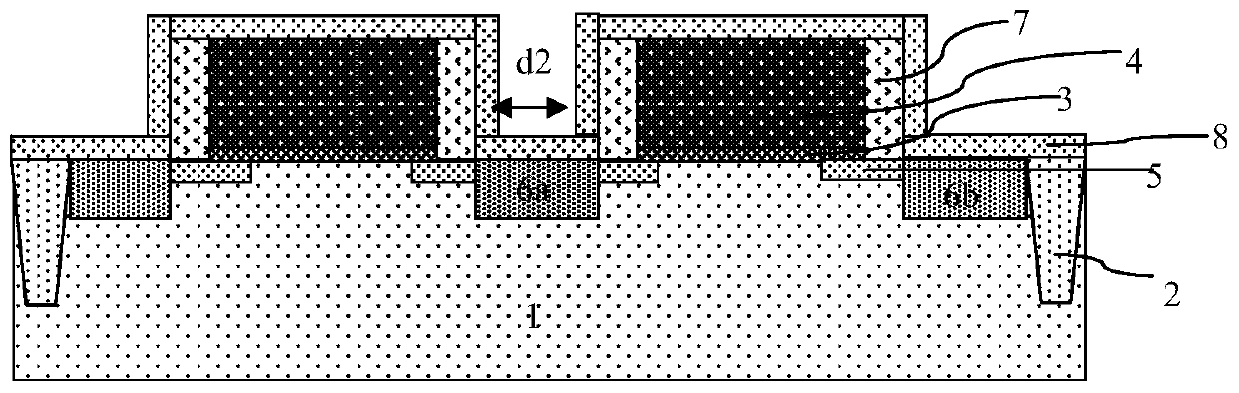

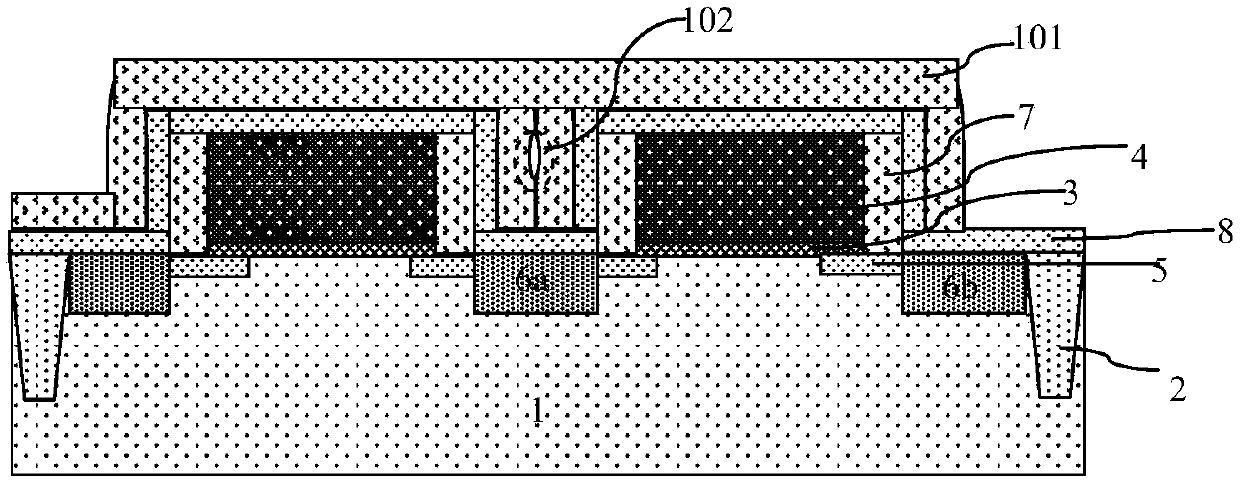

SAB process method for semiconductor devices

ActiveCN107910329BGuaranteed spacingFully etchedSolid-state devicesSemiconductor devicesEtchingDevice material

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

A sensor monocrystalline silicon etching device with uniform etching

ActiveCN109461672BEffective exposureFully etchedElectric discharge tubesSemiconductor/solid-state device manufacturingEtchingEngineering

Owner:蚌埠市龙子湖区金力传感器厂

A igbt deep trench photolithography process

ActiveCN104505339BFully etchedRegular etchingPhotomechanical apparatusSemiconductor/solid-state device manufacturingEtchingLithography process

The invention relates to an insulated gate bipolar transistor (IGBT) deep-trench photolithographic process, and belongs to the field of microelectronics. The IGBT deep-trench photolithographic process aims to solve the problem of insufficient photoetching of patterns at the bottom of a deep trench. The process comprises the following steps: (1), coating an organic material on the surface of a substrate and in the deep trench, wherein the organic material is insoluble in a developer and can be etched; (2), removing the organic material on the surface of the substrate to make the remaining organic material to be filled in the deep trench; (3), coating photoresist on the surface of the substrate and the surface of the organic material; (4), exposing the photoresist; (5), removing the photoresist on the deep trench by using the developer; (6), etching the organic material in the deep trench and a wafer at the bottom of the deep trench; and (7), removing the photoresist on the surface of the bottom of the substrate to complete the etching of the IGBT deep trench. The IGBT deep-trench photolithographic process has the advantages that the organic material is filled in the IGBT deep trench, so that sufficient and regular etching of the bottom of the deep trench can be realized.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

A design method for improving etching yield of high-speed line pcb circuit board

ActiveCN112040661BImprove etching yieldAvoid formingConductive material mechanical removalConductive material chemical/electrolytical removalEtchingHemt circuits

The invention belongs to the technical field of PCB circuit board etching, in particular to a design method for improving the etching yield of a high-speed line PCB circuit board, comprising the following steps: S1, design A: covering a copper layer A on a formed circuit board; S2, design B: Pre-plate the lead-tin resist layer B on the copper layer A; S3, designs C and D: set the printed etching board frame C that is suitable for the circuit trace, and set the lead-tin covering on the etching board frame C The resist layer B extends along D on both sides. In the present invention, by arranging an etching plate frame and reserving edges extending to both sides of the covered lead-tin resist layer, it is possible to avoid the formation of "copper roots" on both sides of the lines, narrowing the line spacing, and at the same time avoiding a small part of the photosensitive film along the edges. Covering, leaving "residual glue" under the edge, the etching method and the engraving method are beneficially combined to achieve complete etching, which greatly improves the etching yield, effectively controls the production cost, and ensures the quality of the finished product.

Owner:BRAIN POWER (QING YUAN) CO LTD

A wafer wet etching device

InactiveCN108695214BFully etchedImprove etching effectSemiconductor/solid-state device manufacturingWaferEngineering

The invention, which belongs to the field of semiconductor technology, in particular relates to a wet etching apparatus for a wafer. The wet etching apparatus is composed of a cylinder I, a cylinder II, and baffles. The cylinder II is installed inside the cylinder I coaxially. The baffles are arranged inside the cylinder I in a circumferential direction and divide the cylinder I into a sealing chamber I, a sealing chamber II, and a sealing chamber III. According to the invention, on the basis of mutual cooperation of a sliding telescopic rod II sleeved by a spring I and a spiral plate, the sliding telescopic rod II stretches and contracts during the vibration process of the spiral plate and a wafer moves; and after the displacement, a clamping unit clamps the wafer again and thus an etching solution etches the wafer uniformly. Meanwhile, etched precipitated particles are separated from the wafer based on vibration of the spiral plate, so that contact between the etching solution and the wafer is increased and thus the etching effect is improved.

Owner:如东汇盛通半导体科技有限公司

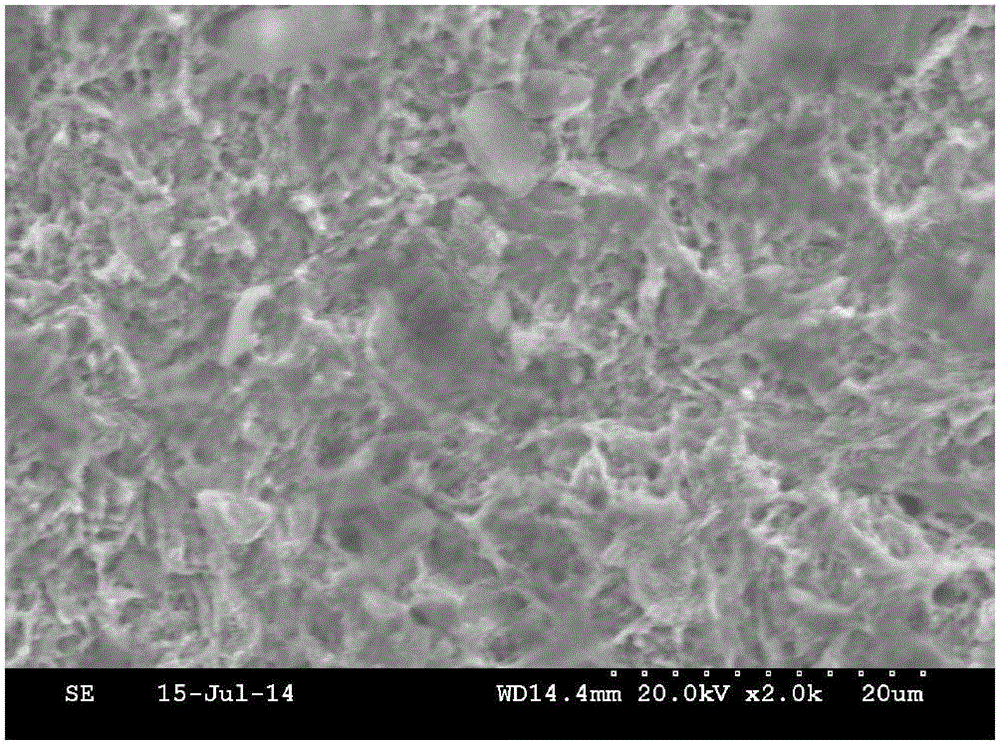

Etching method of medium carbon steel substrate, antifriction and wear-resisting composite lubricating film and preparation method of antifriction and wear-resisting composite lubricating film

ActiveCN106423788ALow priceUniform and dense structurePretreated surfacesCoatingsCarbon steelLubricant

The invention provides an etching method of a medium carbon steel substrate. A mixed solution including FeCl3 and HCl is adopted for etching a medium carbon steel substrate material; and the concentration of the FeCl3 in the mixed solution ranges from 25 g / L to 75 g / L, and the concentration of the HCl in the mixed solution ranges from 25 g / L to 100 g / L. The invention further provides a method for preparing a composite lubricating film through the etching method. After being cleaned, etched medium carbon steel is dried, then the surface of the dried medium carbon steel is coated with a lubricating agent and then cured, and the antifriction and wear-resisting composite lubricating film is obtained. According to the method, only the mixed solution of the FeCl3 and the HCl is adopted for etching the medium carbon steel substrate material, the etching process can be completed within a short time, and the cost can be reduced. The antifriction effect of the composite lubricating film obtained through the scheme is good, the service life is prolonged, and the width of a grinding crack generated after sliding friction of 14400 s is not larger than 250 microns.

Owner:QINGDAO TECHNOLOGICAL UNIVERSITY

SAB technique for semiconductor device

ActiveCN107910329AGuaranteed spacingFully etchedSolid-state devicesSemiconductor devicesSalicideEtching

The invention discloses an SAB technique for a semiconductor device. The SAB technique comprises the steps of (1) forming a gate structure, source regions and drain regions of the semiconductor device; and (2) determining the required thickness of an SAB film and splitting a forming process of the SAB film by combining the spaces between polysilicon gates to ensure that no gap is formed between the polysilicon gates through the thickness of each SAB sub-film, photoetching the SAB sub-films, removing the SAB sub-film in an area in which metal silicide needs to be formed and achieving full etching of the SAB sub-film between the polysilicon gates, thereby preventing a void from appearing in the subsequent film forming process. According to the SAB technique, no void can be formed between thepolysilicon gates of the semiconductor layer in the process of forming the SAB film, so that the SAB film between the polysilicon gates can be fully etched and the SAB technique does not affect the spaces between the polysilicon gates, thereby facilitating filling of the film.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP