Silicon chip etching method

A silicon wafer and oxygen technology, applied in the manufacture of electrical components, semiconductor/solid-state devices, circuits, etc., can solve problems such as etching, affecting device performance, and deterioration of etching uniformity, and achieve sufficient etching and precise control Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

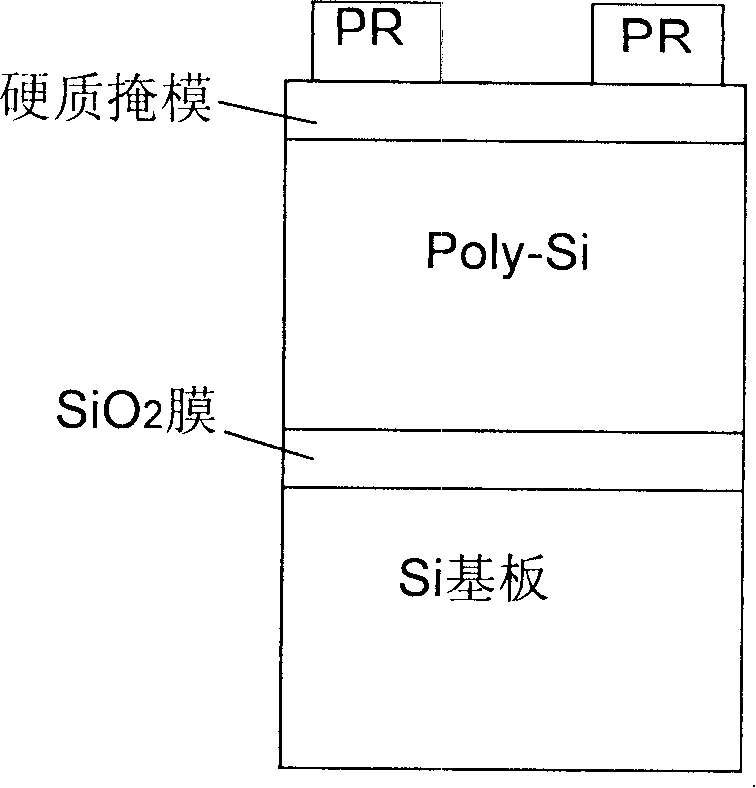

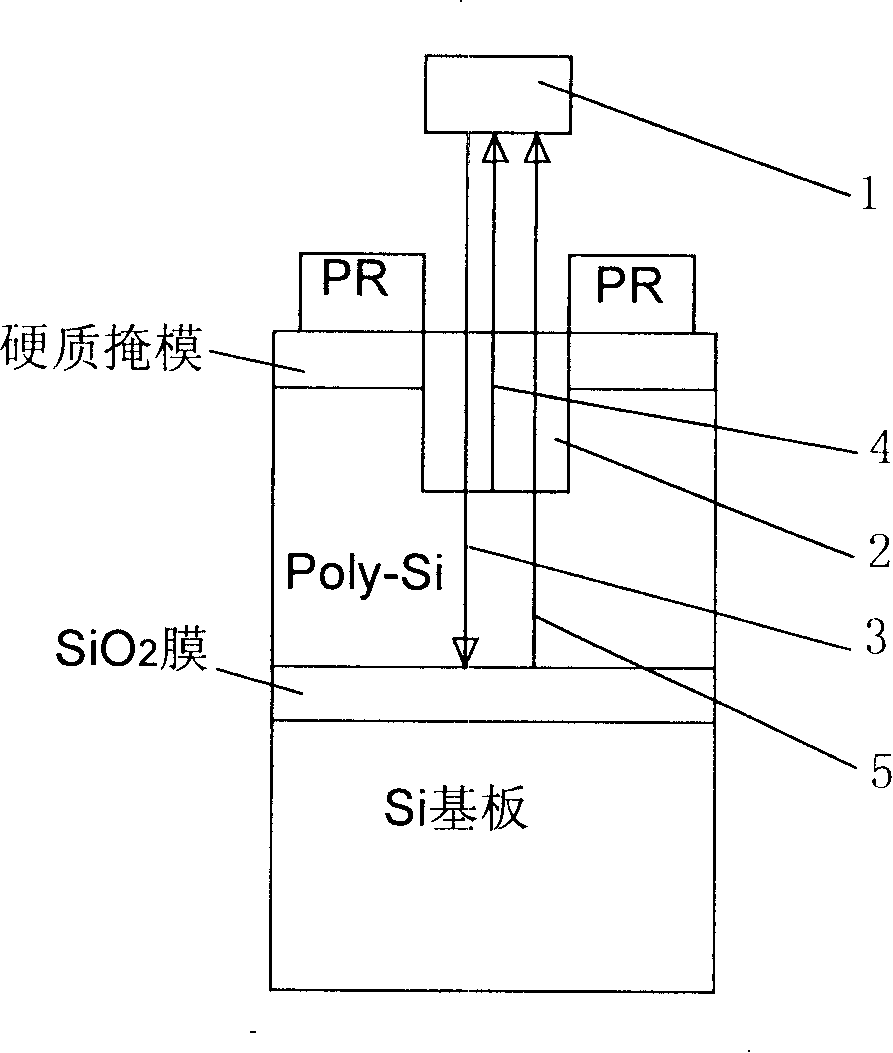

[0027] The invention is mainly used for etching the silicon chip, the silicon chip is etched by process gas, and the lower layer of the silicon chip is an oxide layer. Here poly-si (polysilicon) is taken as an example to illustrate the process of etching silicon wafers in the present invention. Below the polysilicon are SiO2 film (oxide layer), Si silicon base layer, and the top of the polysilicon is a hard mask. Above the mask is a photoresist pattern. However, the present invention is not limited to etching polysilicon, and is also used to etch other silicon wafers, and the SiO2 film in the lower layer may also be other oxide layers.

[0028] Its preferred specific implementation is, as figure 2 As shown, during the etching process of polysilicon, the IEP (laser detector) control mode is used to monitor the etching process. Specifically, the laser detector 1 is used to detect the etching process. When the etching depth is close to the upper surface of the oxide layer , to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More