Patents

Literature

89results about How to "Efficient etching" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

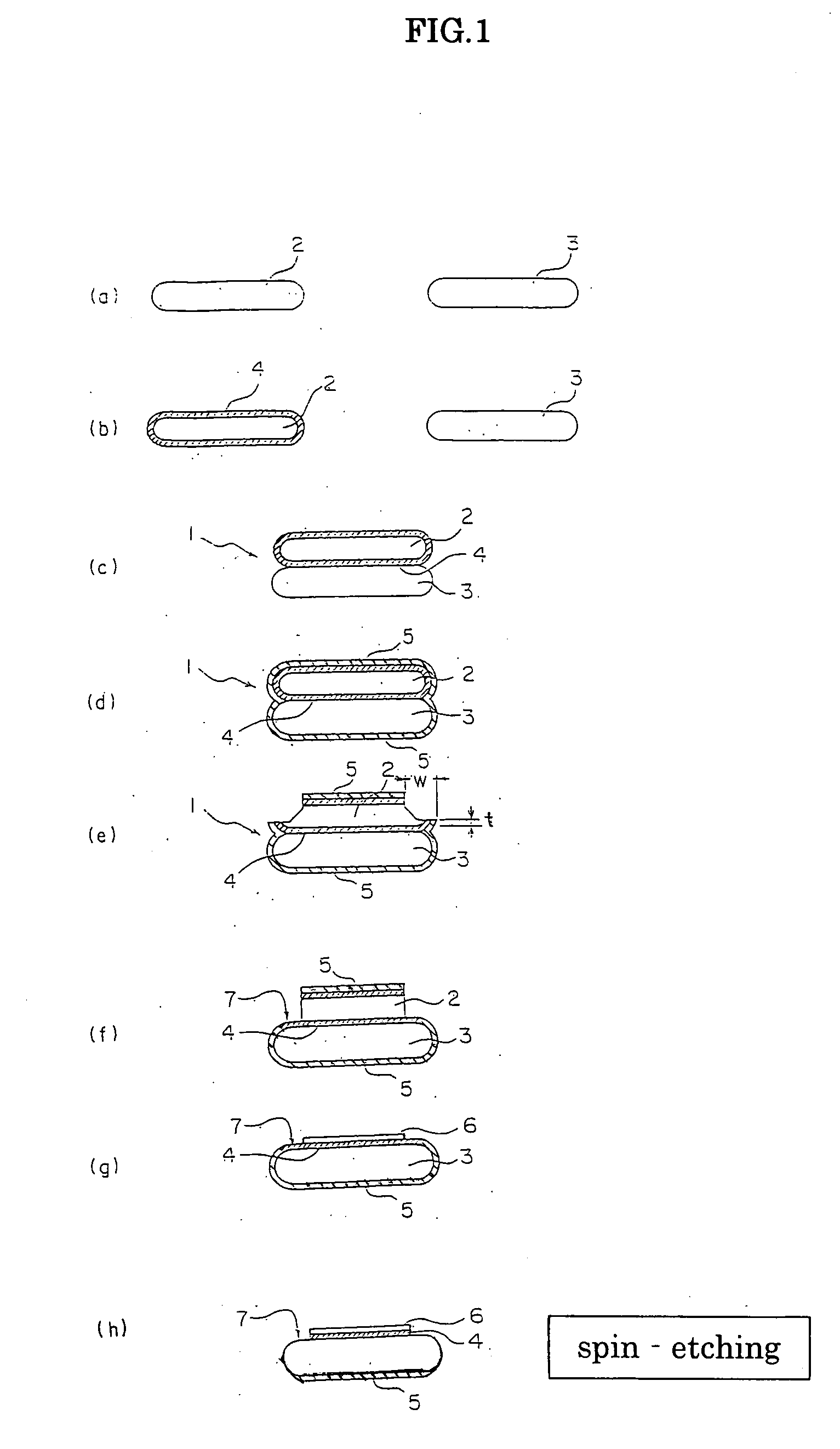

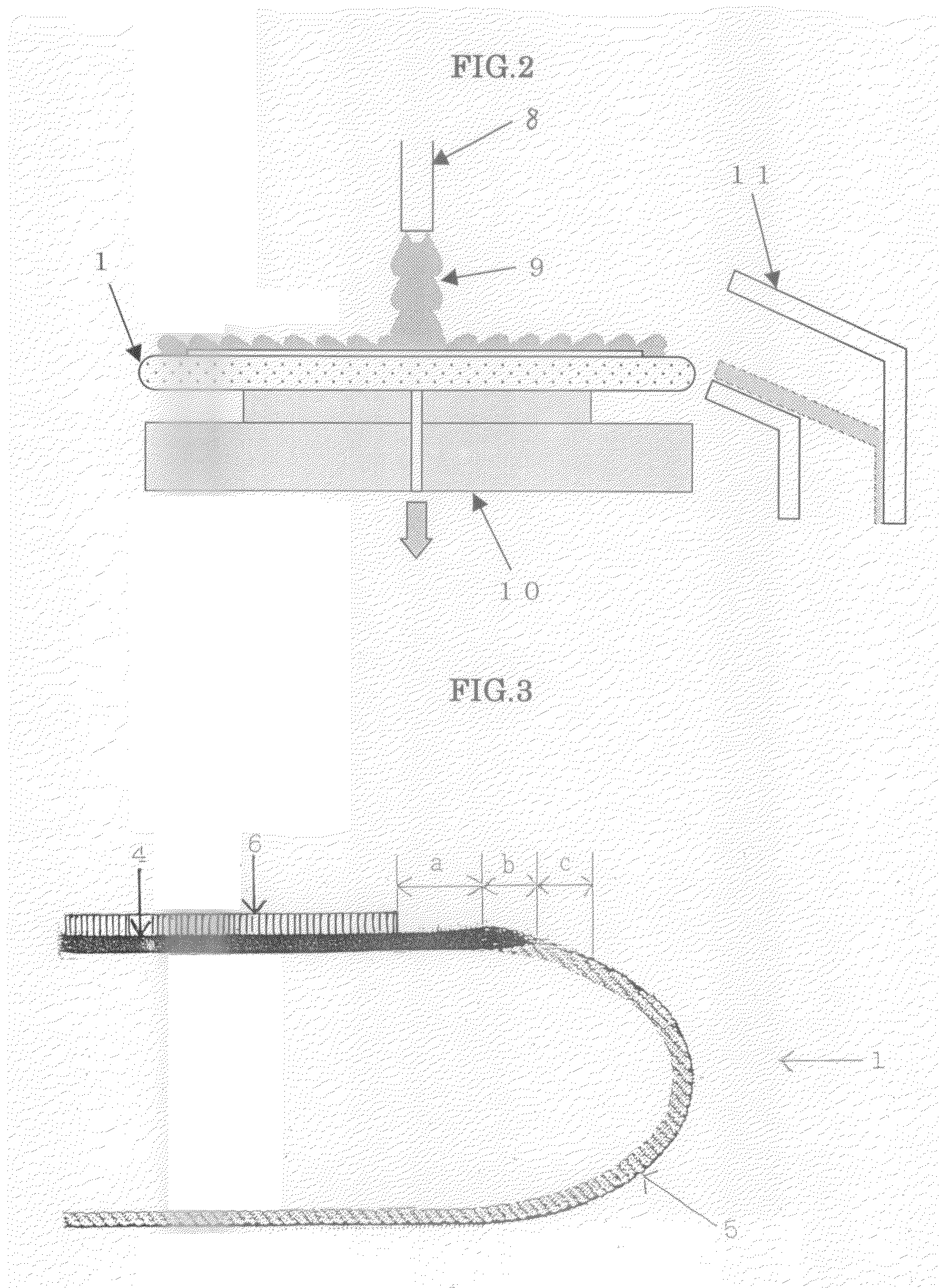

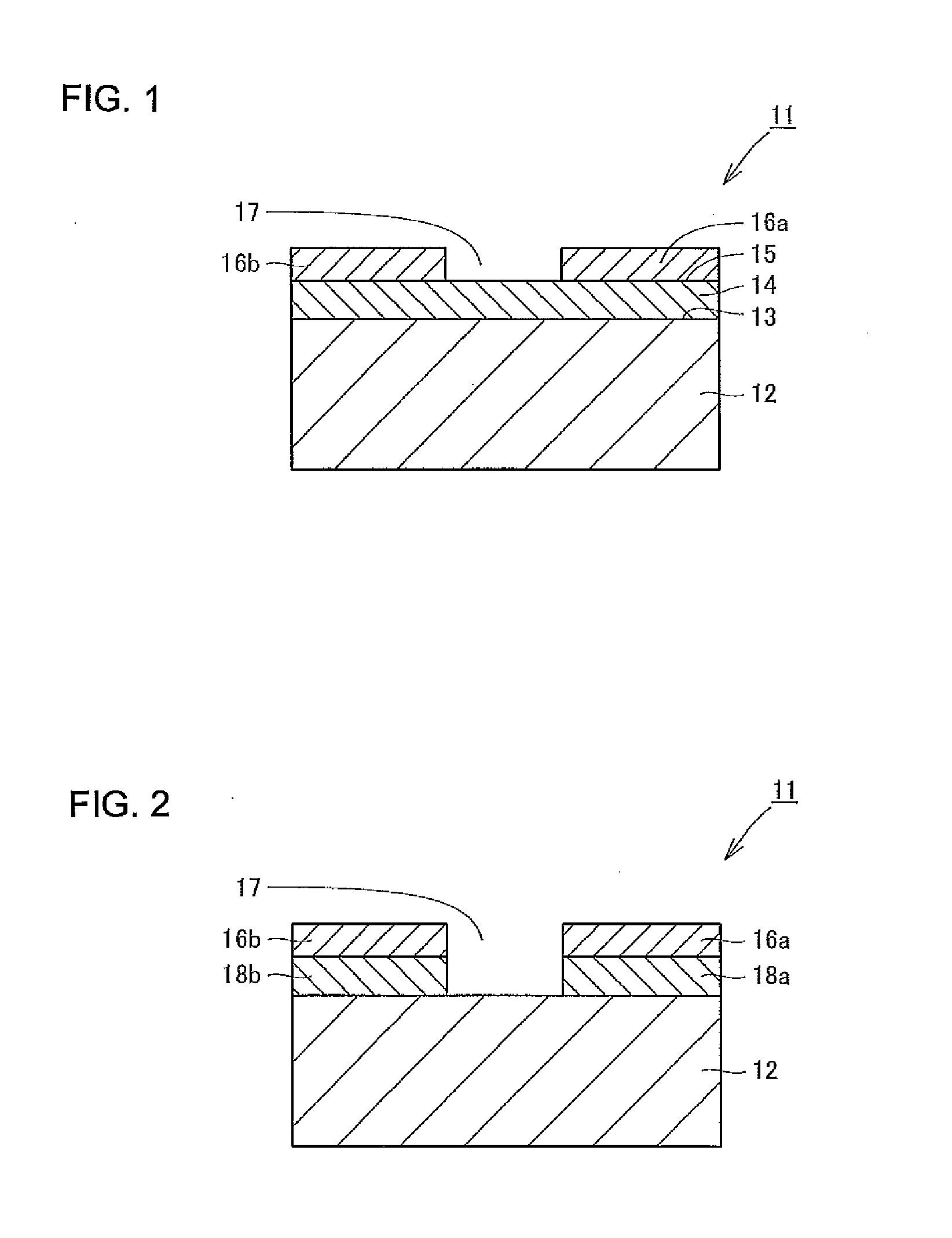

Optical fiber for transmitting ultraviolet ray, optical fiber probe, and method of manufacturing the optical fiber probe

InactiveUS6944380B1High light transmittanceResistant to deteriorationGlass optical fibreGlass making apparatusFiberHydrogen

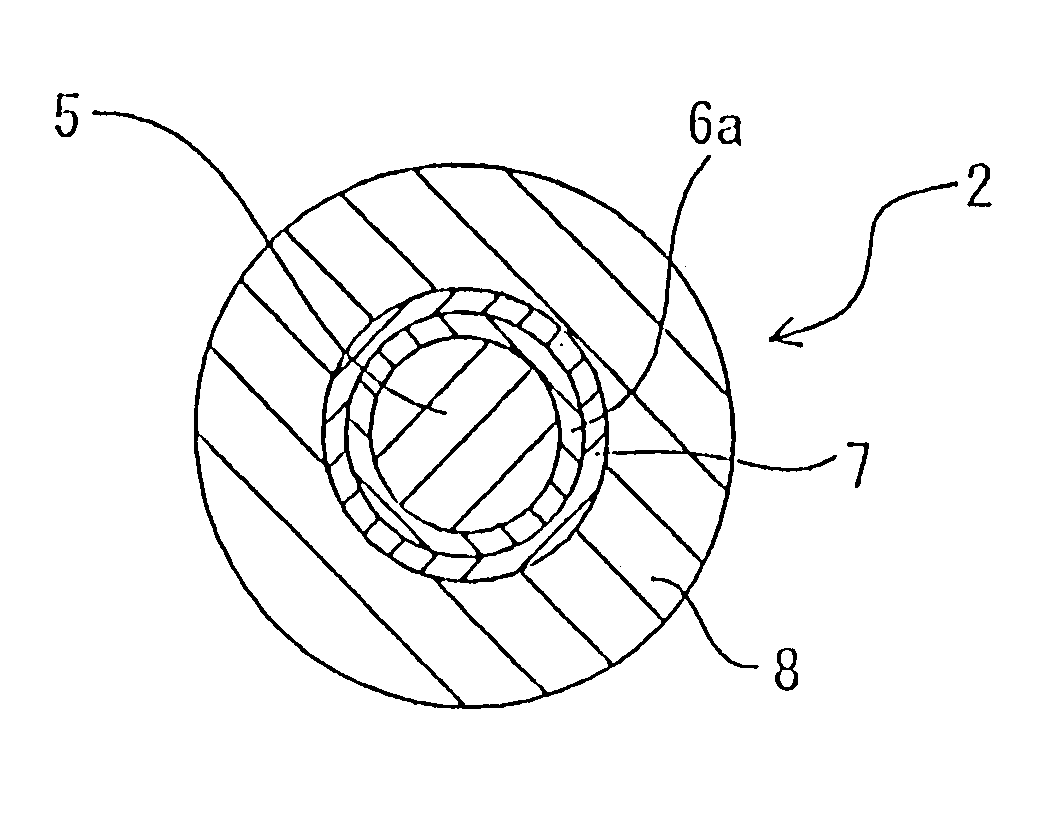

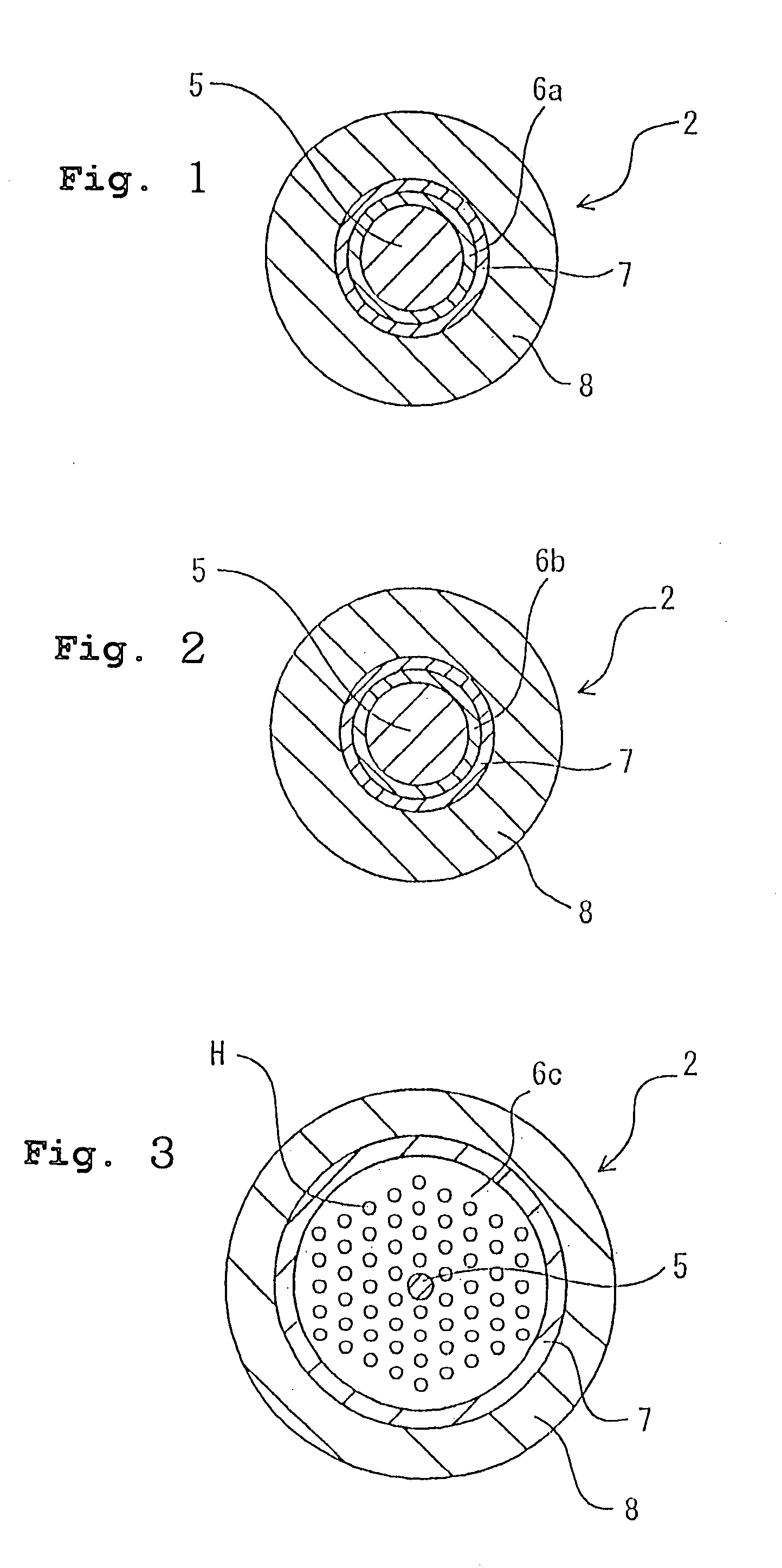

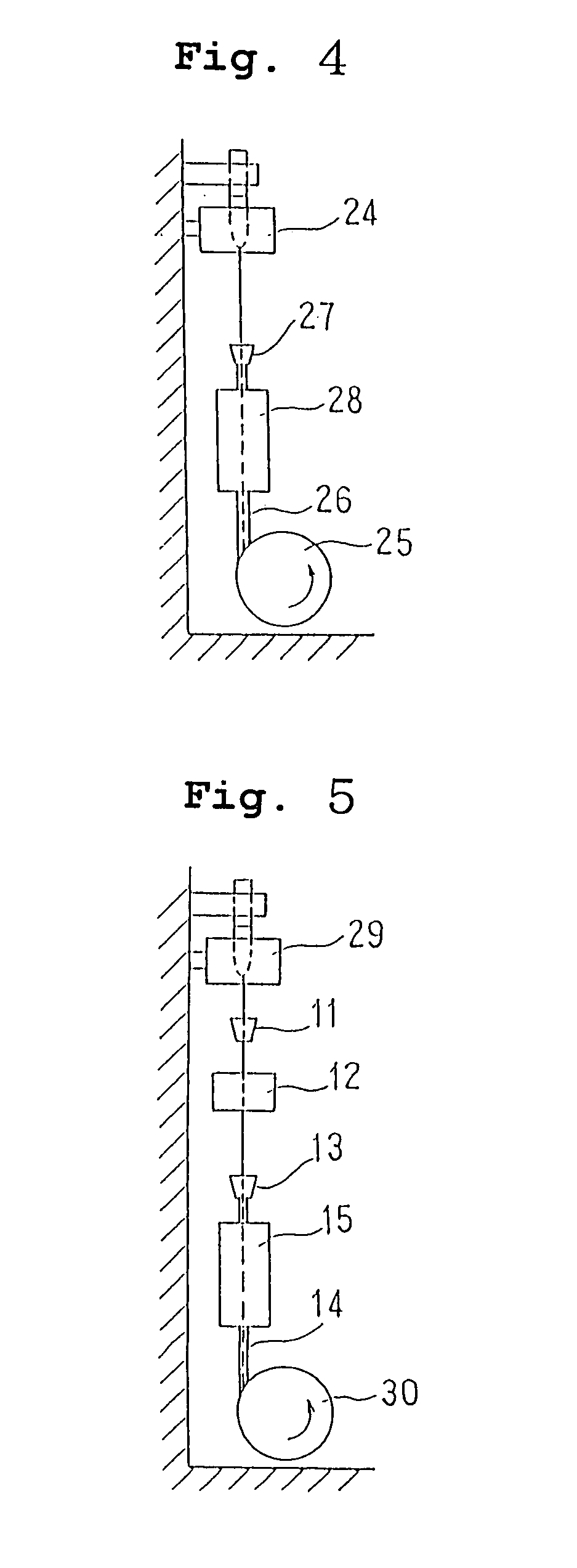

It is an object of the present invention to provide an optical fiber for transmitting ultraviolet ray which has an improve transmittance and is prevented from deterioration by ultraviolet ray with which it is irradiated. It is another object of the present invention to provide an optical fiber probe which can propagate vacuum ultraviolet ray and deep ultraviolet ray at a high transmittance, is deteriorated only to a limited extent when irradiated with ultraviolet ray and can be etched to have a desired shape of the sharpened section at the fiber end.The present invention provides the optical fiber for transmitting ultraviolet ray which has a core 5 of silica glass containing a given content of fluorine and a clad 6a of silica glass containing a given content of fluorine or boron, a clad 6b of a resin which transmits ultraviolet ray or a clad 6c having air holes H. The clad may be coated with a protective layer and further with a covered layer for protection. In particular, the core, clad and protective layer have a high transmittance for ultraviolet ray and resistance to ultraviolet ray with which they are irradiated, when treated with hydrogen.An optical fiber probe 1 has an optical fiber 2 provided with a sharpened section 3 at the end, which is sharpened with an etchant solution, the sharpened section 3 being coated with a light-shielding metallic film 4.

Owner:JAPAN SCI & TECH CORP

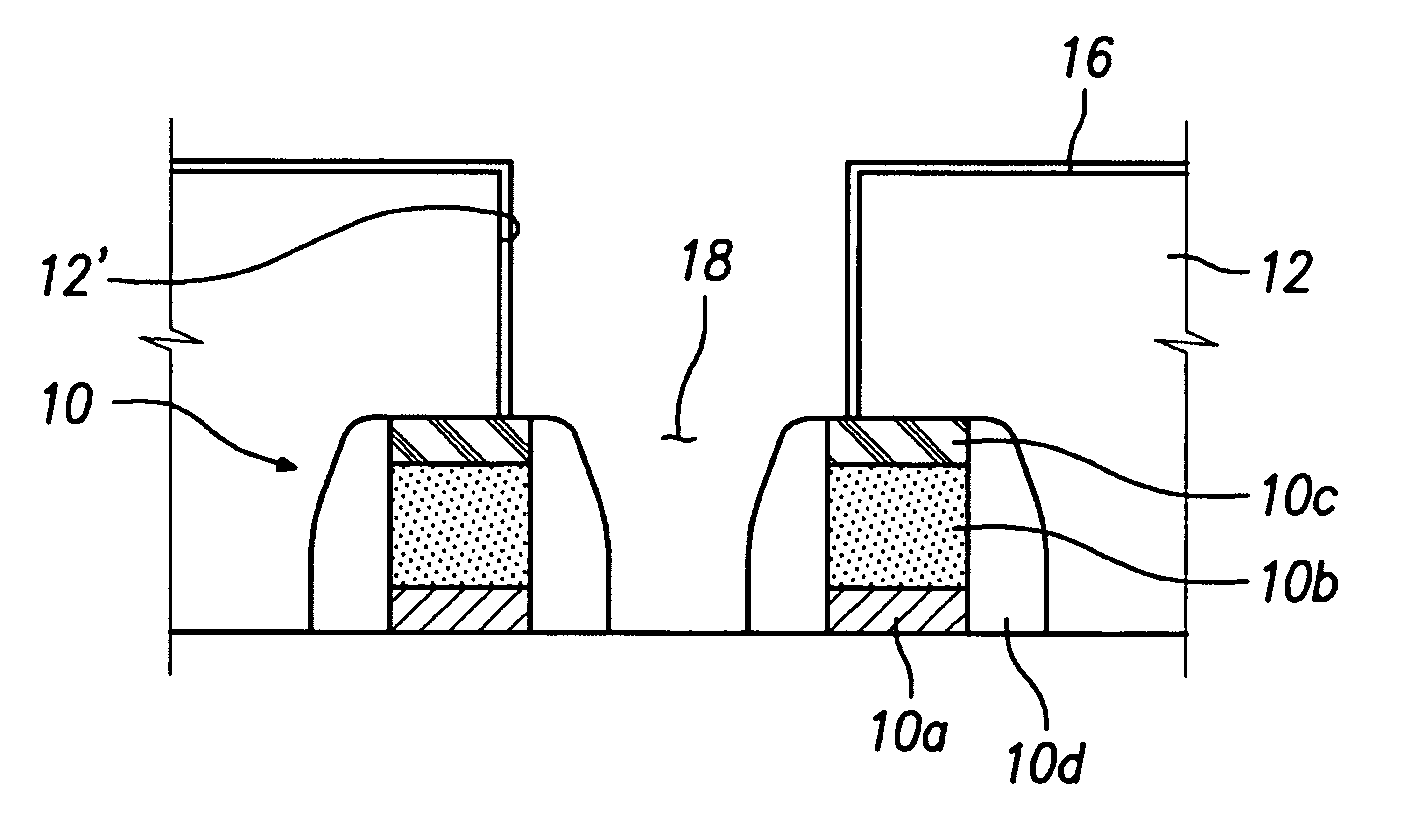

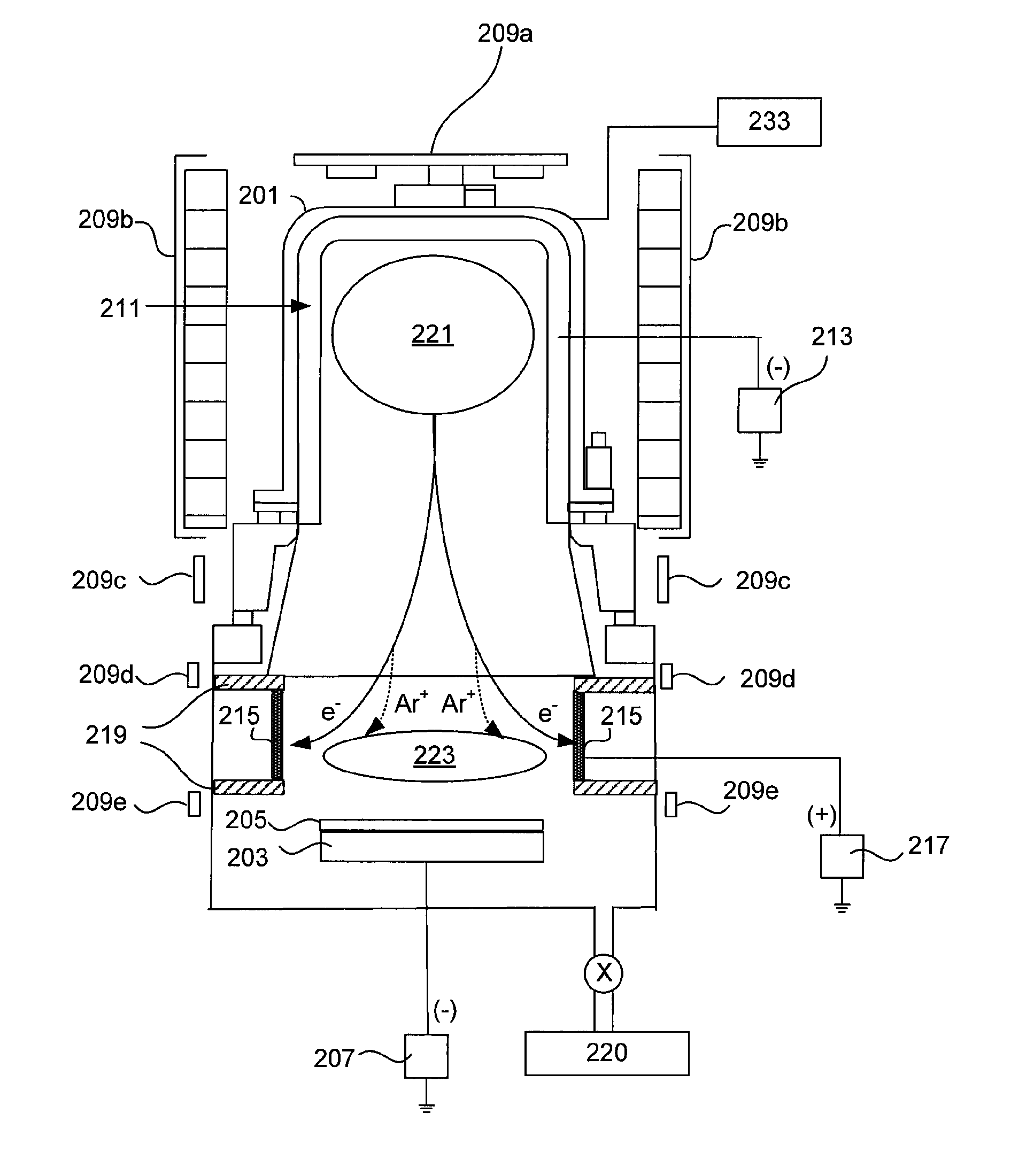

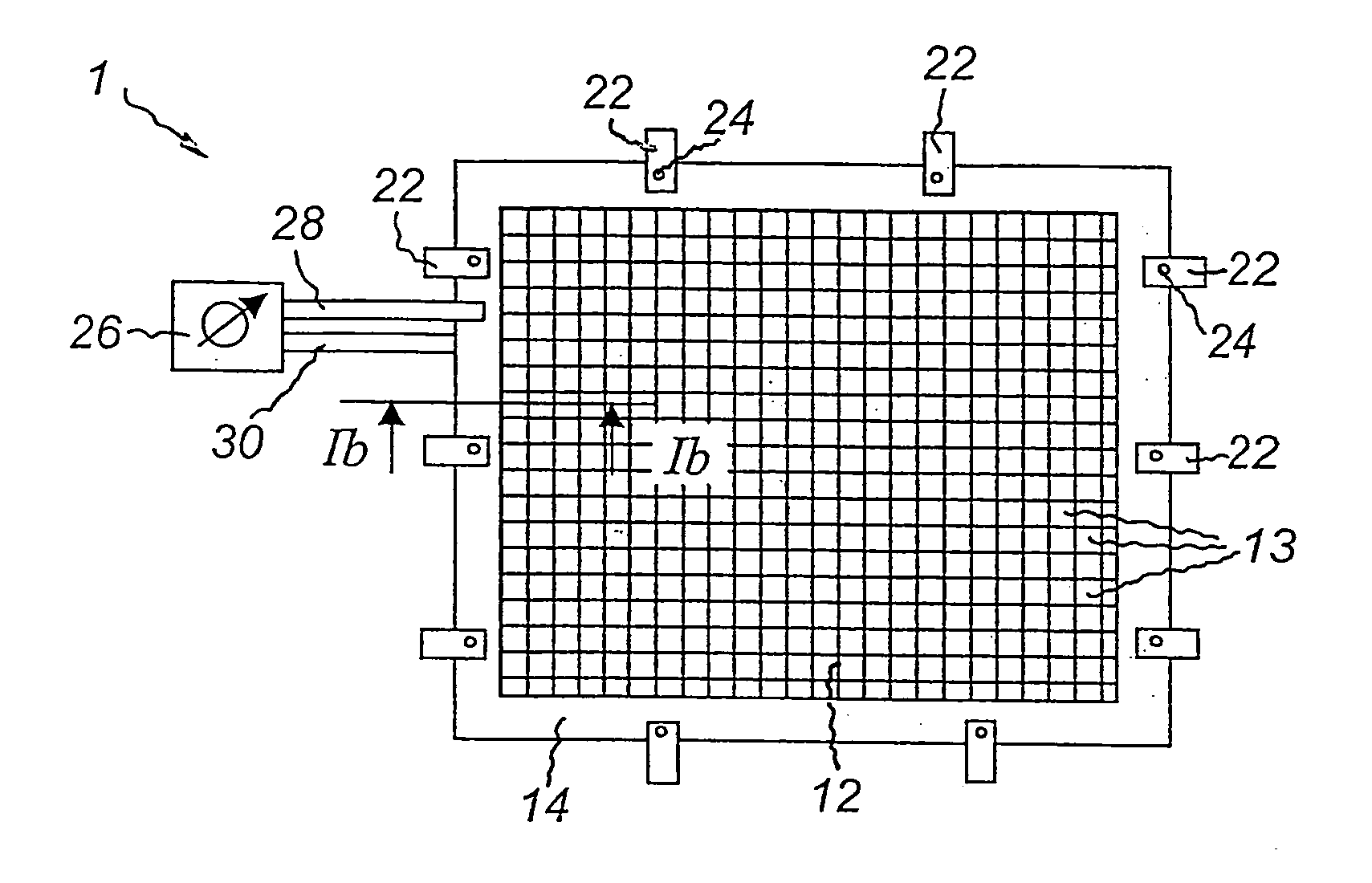

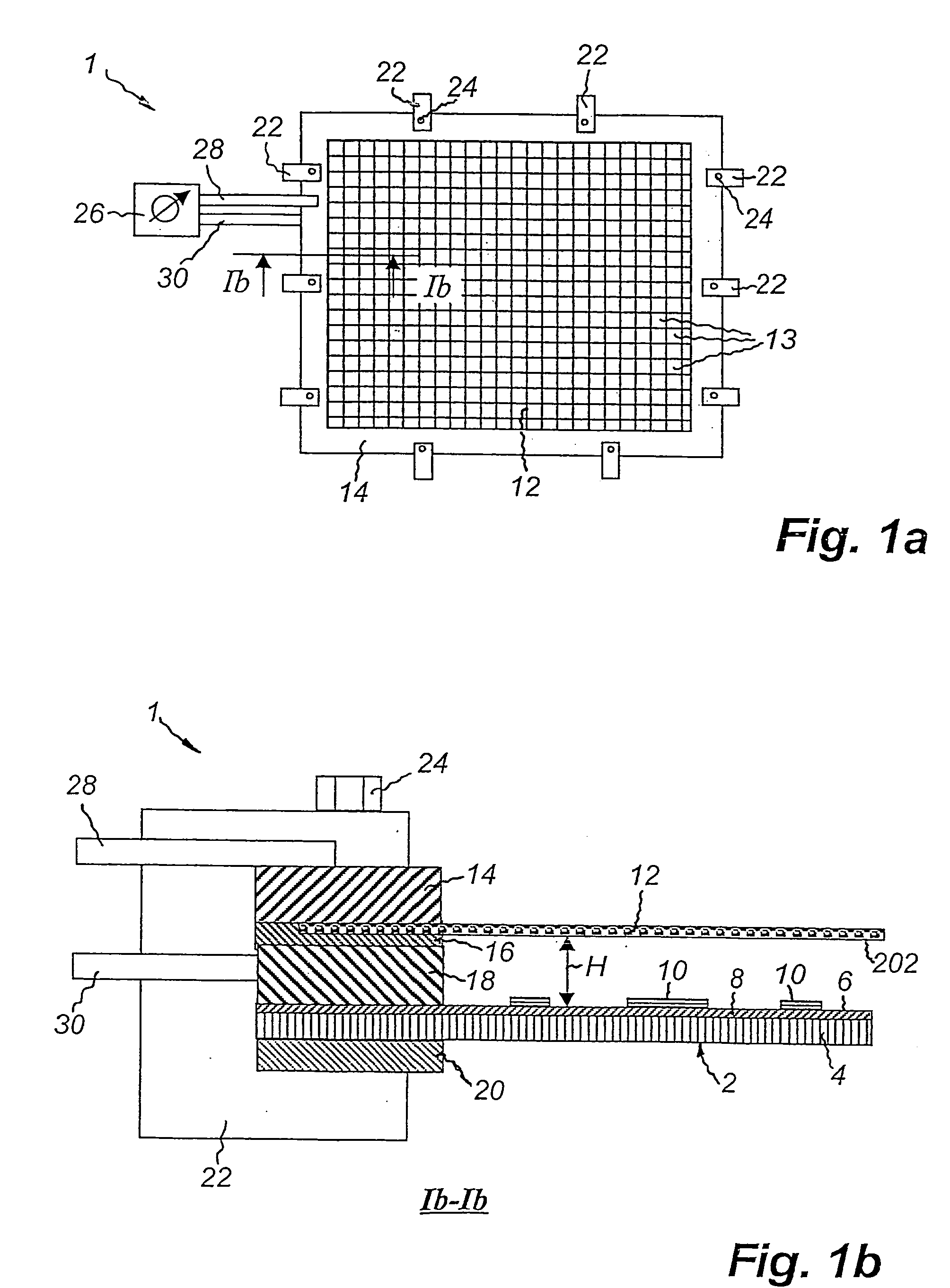

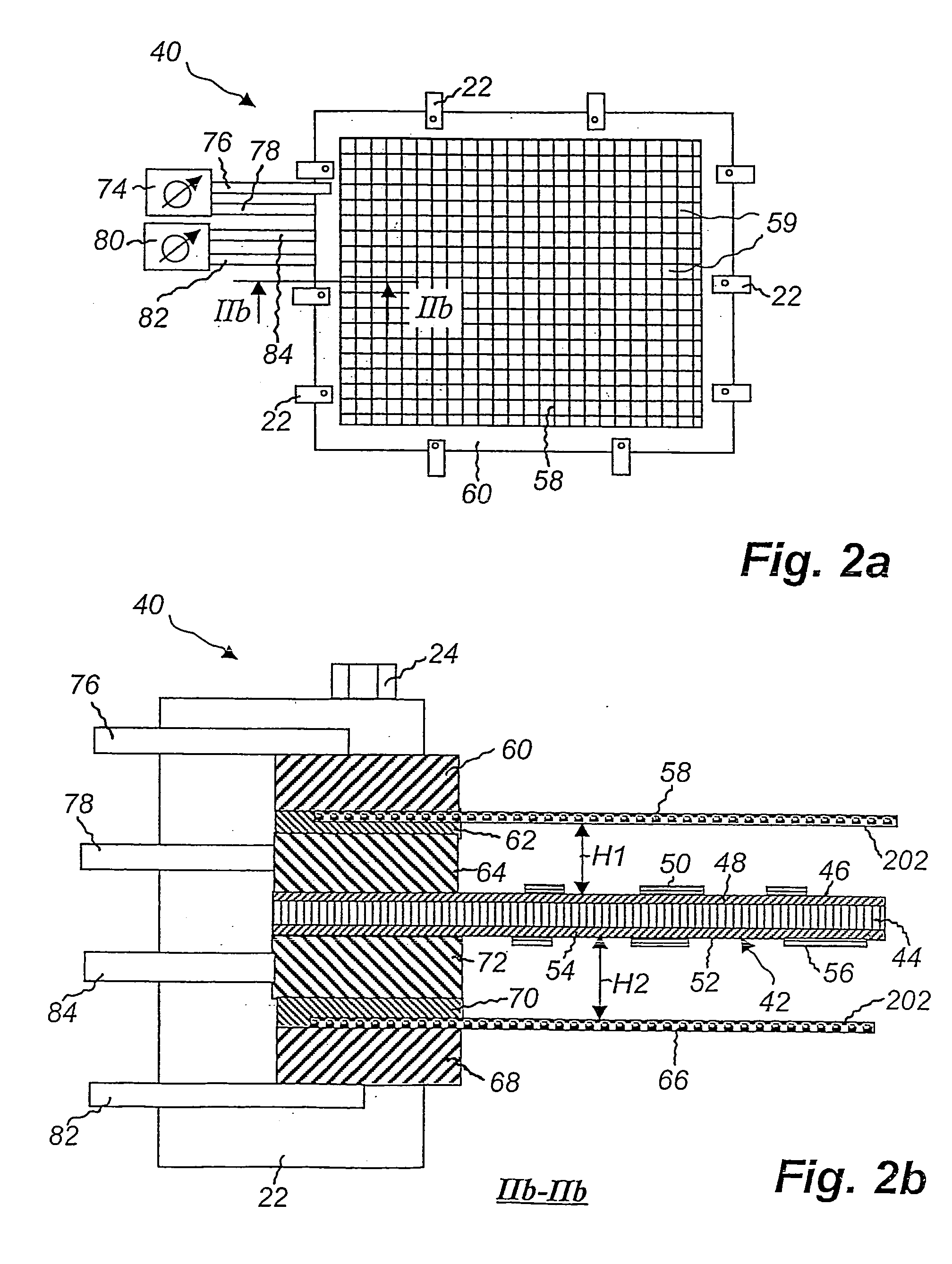

Method and apparatus for increasing local plasma density in magnetically confined plasma

ActiveUS7922880B1Easily damagedLow reliabilityCellsElectric discharge tubesPlasma densityHigh density

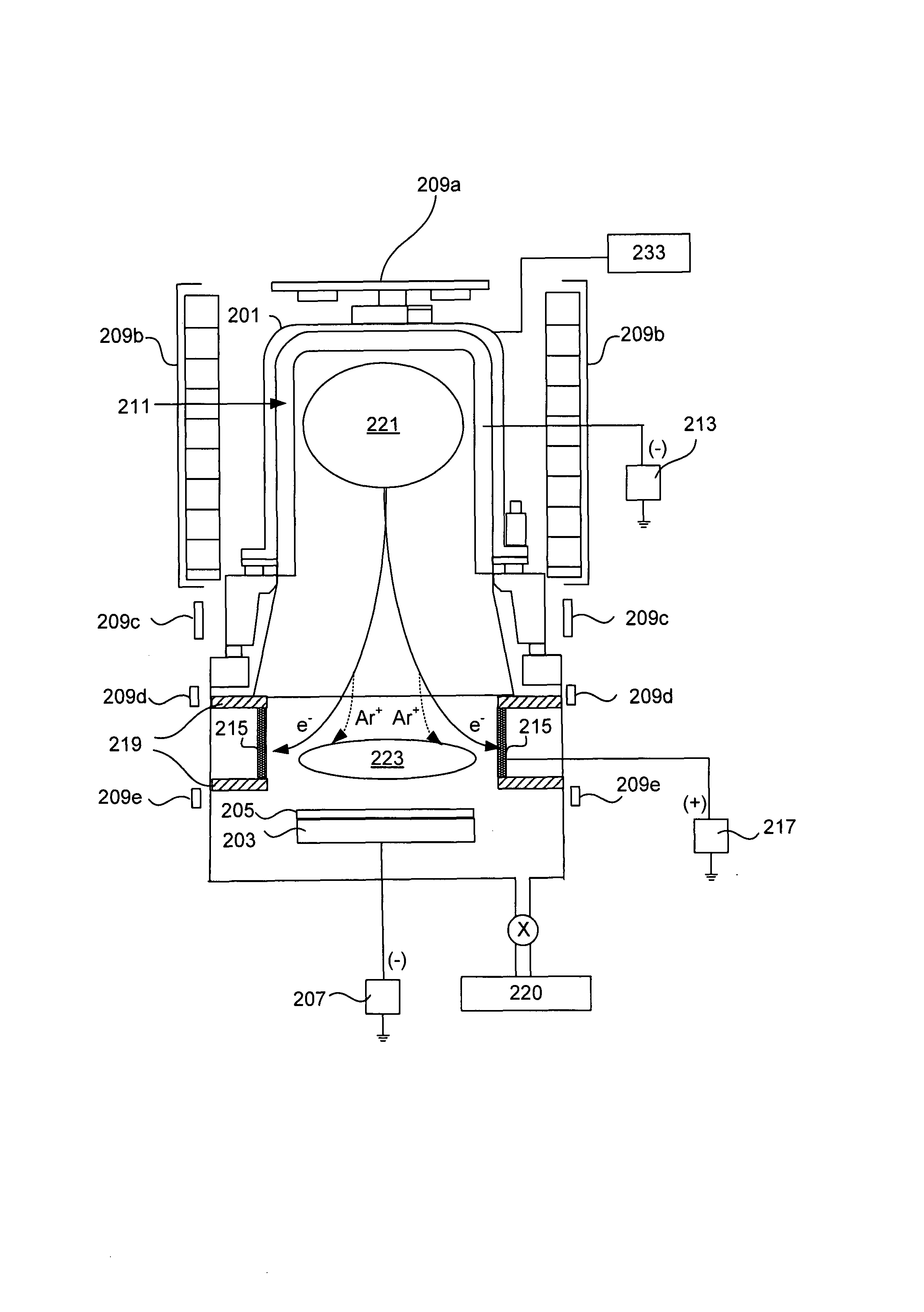

Local plasma density, e.g., the plasma density in the vicinity of the substrate, is increased by providing an ion extractor configured to transfer ions and electrons from a first region of magnetically confined plasma (typically a region of higher density plasma) to a second region of plasma (typically a region of lower density plasma). The second region of plasma is preferably also magnetically shaped or confined and resides between the first region of plasma and the substrate. A positively biased conductive member positioned proximate the second region of plasma serves as an ion extractor. A positive bias of about 50-300 V is applied to the ion extractor causing electrons and subsequently ions to be transferred from the first region of plasma to the vicinity of the substrate, thereby forming higher density plasma. Provided methods and apparatus are used for deposition and resputtering.

Owner:NOVELLUS SYSTEMS

Self-etching primer adhesive and method of use therefor

A self-etching, priming dental adhesive composition comprises an olefinically unsaturated monomer having an -SO3 functionality; a copolymerizable multi-functional (meth)acrylate adhesive; and a curing system. The self-etching, priming dental adhesive may further comprise a copolymerizable adhesion promoter containing an acid functionality, the adhesion promoter being different from the olefinically unsaturated monomer having an -SO3 functionality and the copolymerizable multi-functional (meth)acrylate adhesive, and a solvent system in an amount effective to dissolve the adhesive and / or the adhesion promoter. The adhesive composition provides even further advantages over the art, as all etching, priming, and application of an adhesive can be performed in one step.

Owner:PENTRON CLINICAL TECH

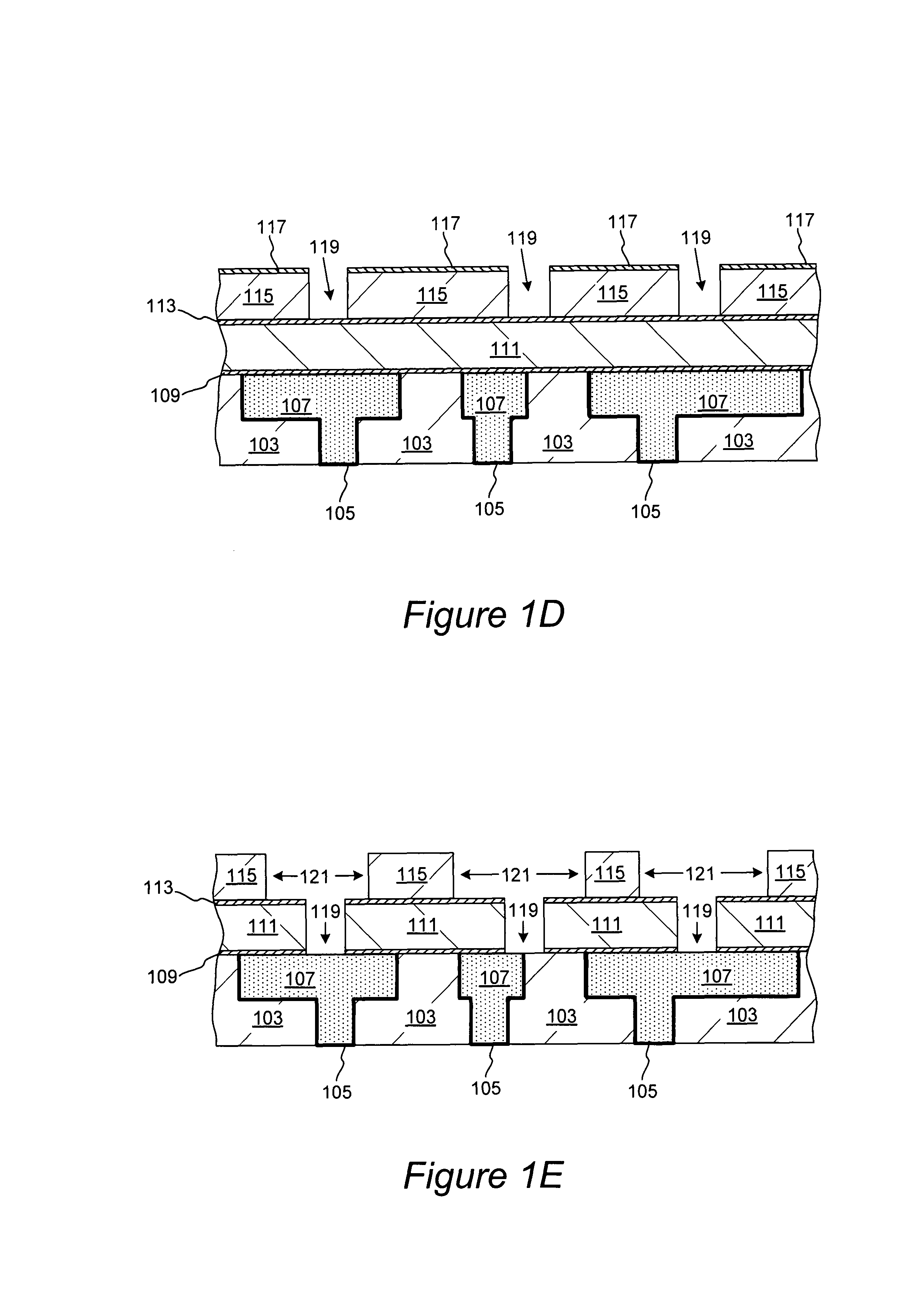

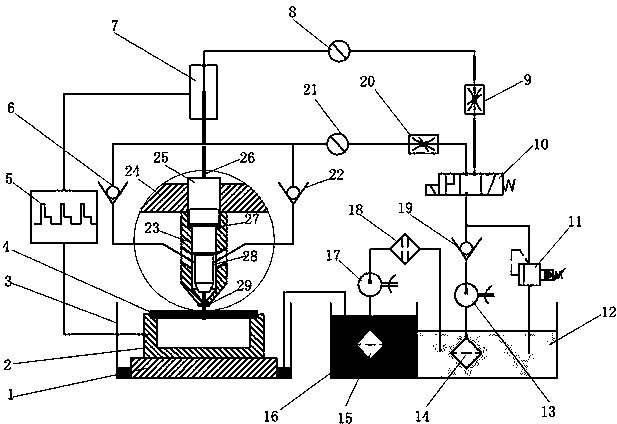

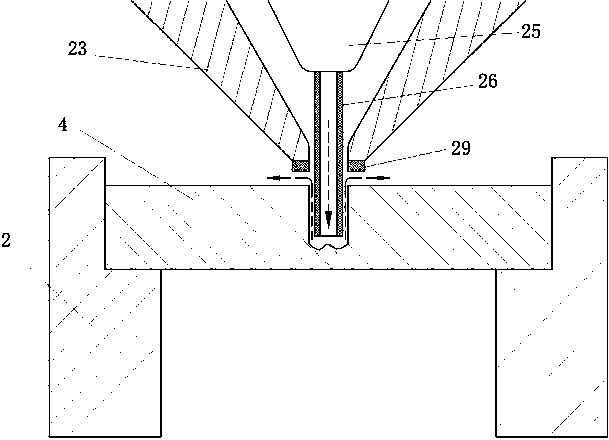

Synchronous composite processing method of micro-hole electric sparks and different electrolytic areas and special tool of synchronous composite processing method

The invention provides a synchronous composite processing method of micro-hole electric sparks and different electrolytic areas and a special tool of the synchronous composite processing method. The synchronous composite processing method includes that a tube electrode is switched to impulse voltage, and a neutral salt solution with ultra-low concentration flows into a processing area via the inner side of the tube electrode at a high speed, and then flows out of the processing area along a gap between the tube electrode and a workpiece; an end face of the tube electrode is subjected to high-speed punch processing with axial feeding of electric sparks under the ultra-low concentration of the neutral salt solution, and a hole wall processed by the electric sparks is subjected to radical electrochemical finishing and machining under the action of low-pressure voltage. By the synchronous composite processing method, processing precision is guaranteed, punching efficiency is improved, and processing requirements on various kinds of holes of an aircraft engine are met. Different from conventional electric spark processing and electrolytic processing, the synchronous composite processing method adopts the neutral salt solution with the ultra-low concentration, so that processing efficiency in electrochemical dissolution can be greatly improved and corrosion degree of equipment can be decreased.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

Self-etching primer and method of use therefor

InactiveUS20020019456A1Efficient etchingEffective primingImpression capsMedical preparationsSelf etchRepair material

A composition for simultaneously etching and priming a tooth surface prior to restoration, comprising a solution of an -SO3 terminated compound resin, and an optional fluoride source. In practice, the composition is applied to the tooth surface and not subsequently washed prior to application of an adhesive or other restorative material.

Owner:JENERIC PENTRON INC

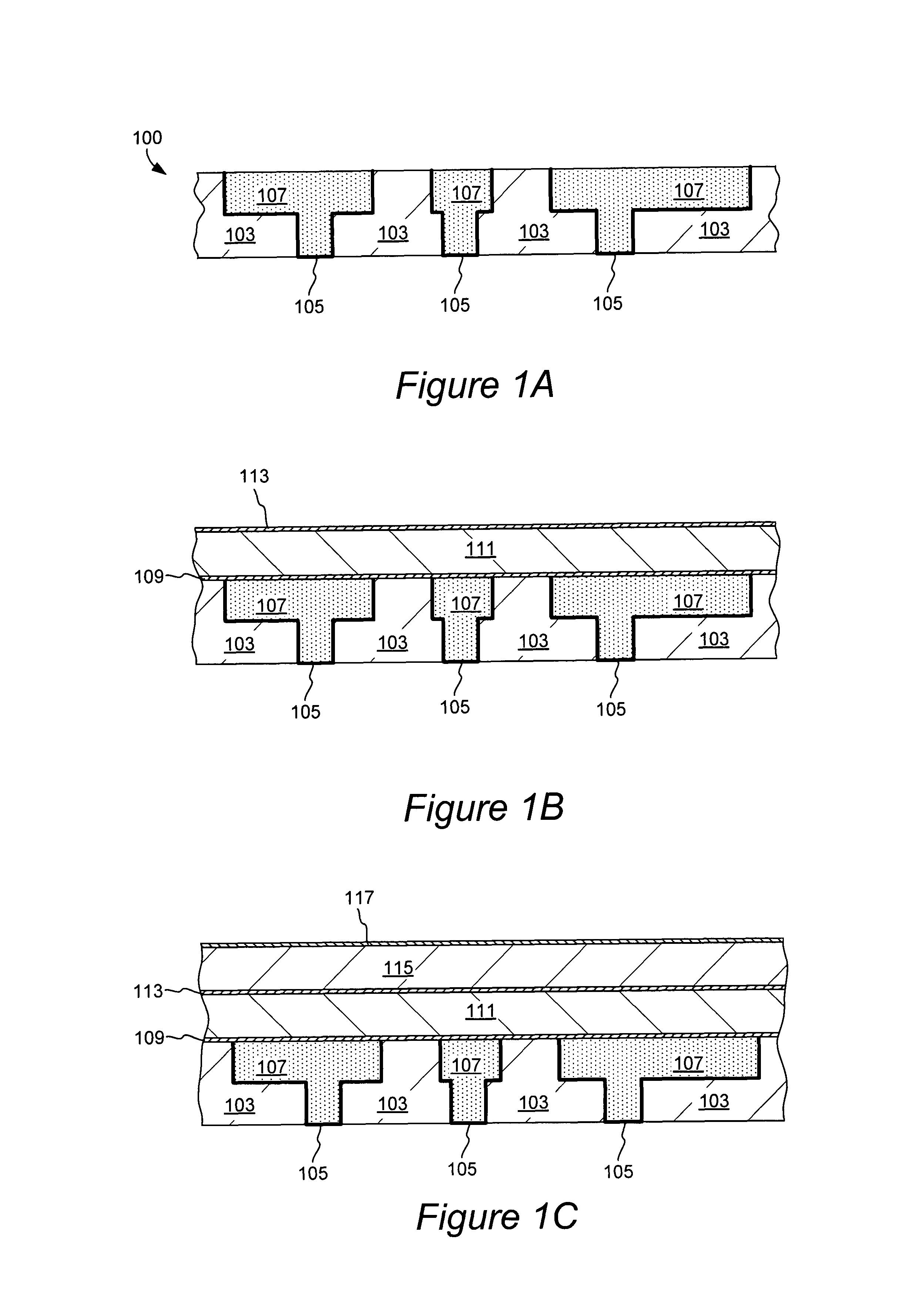

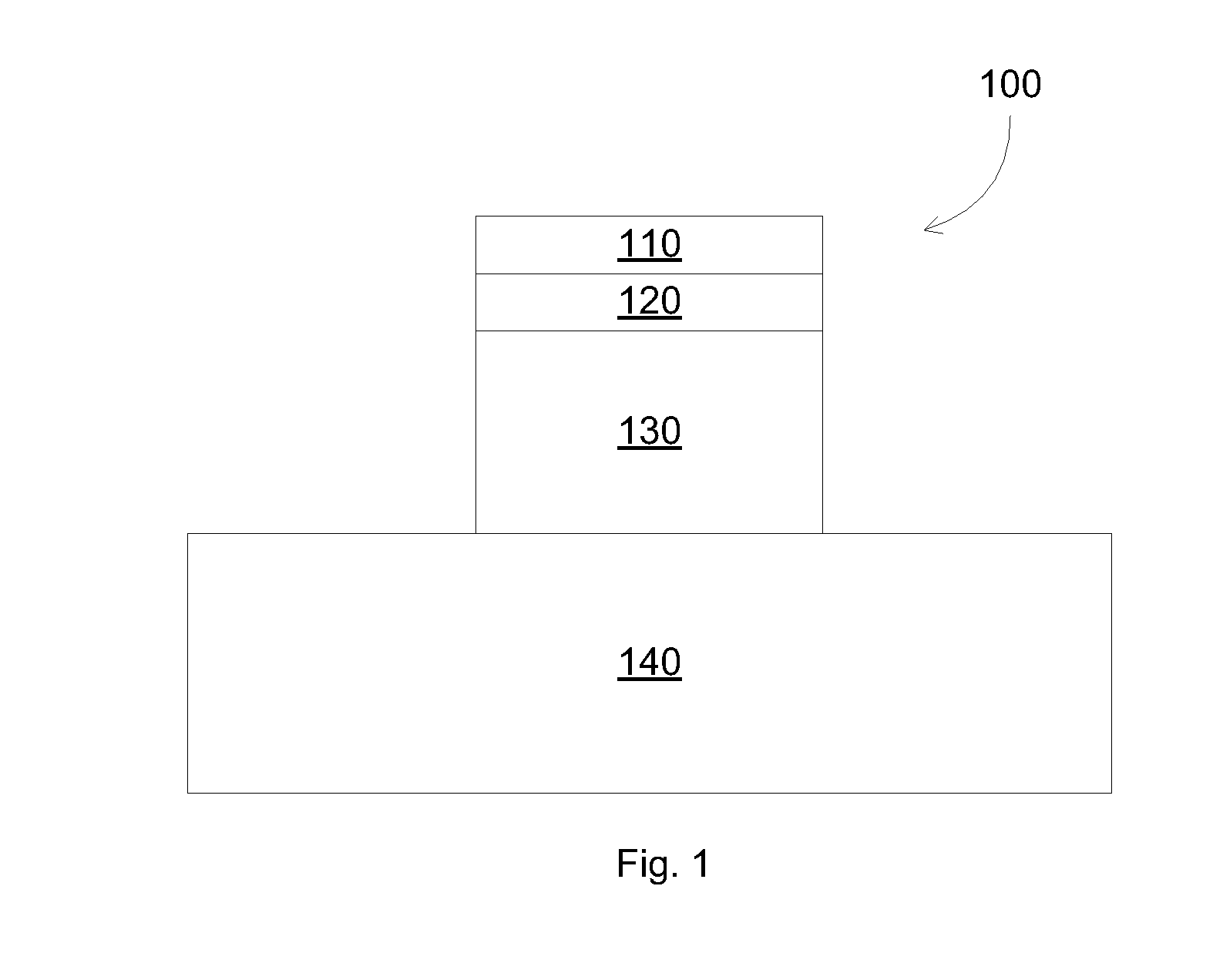

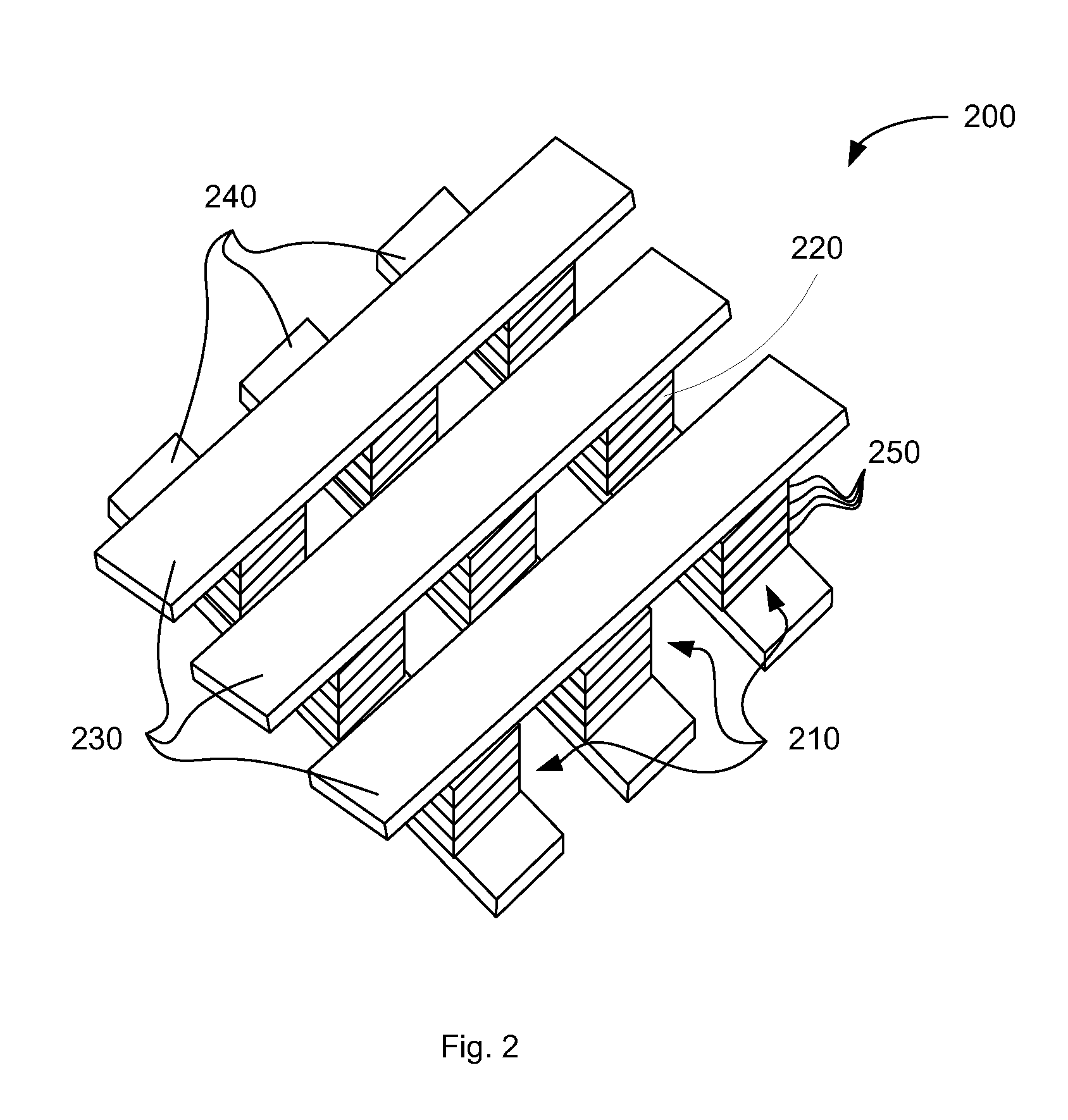

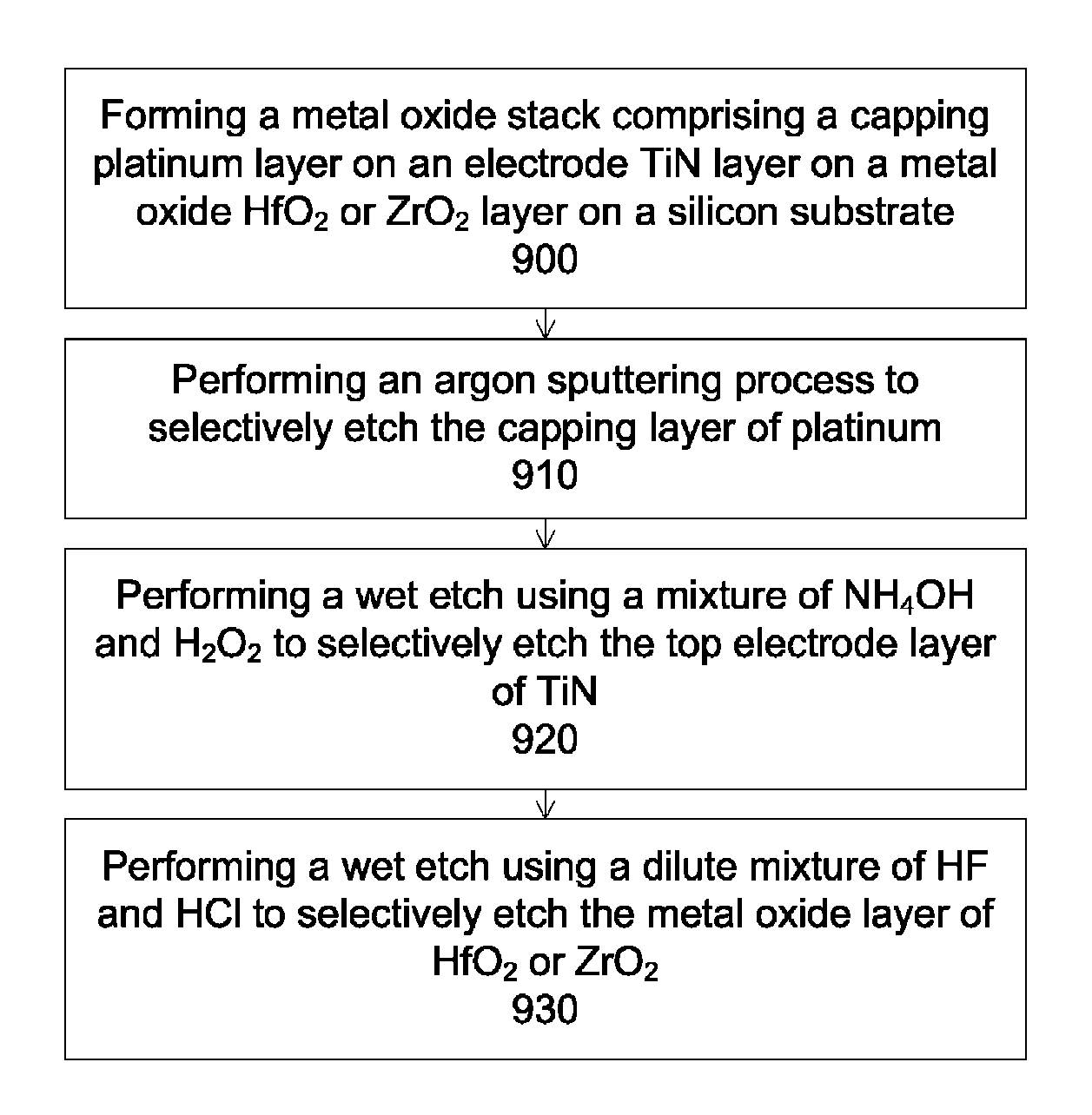

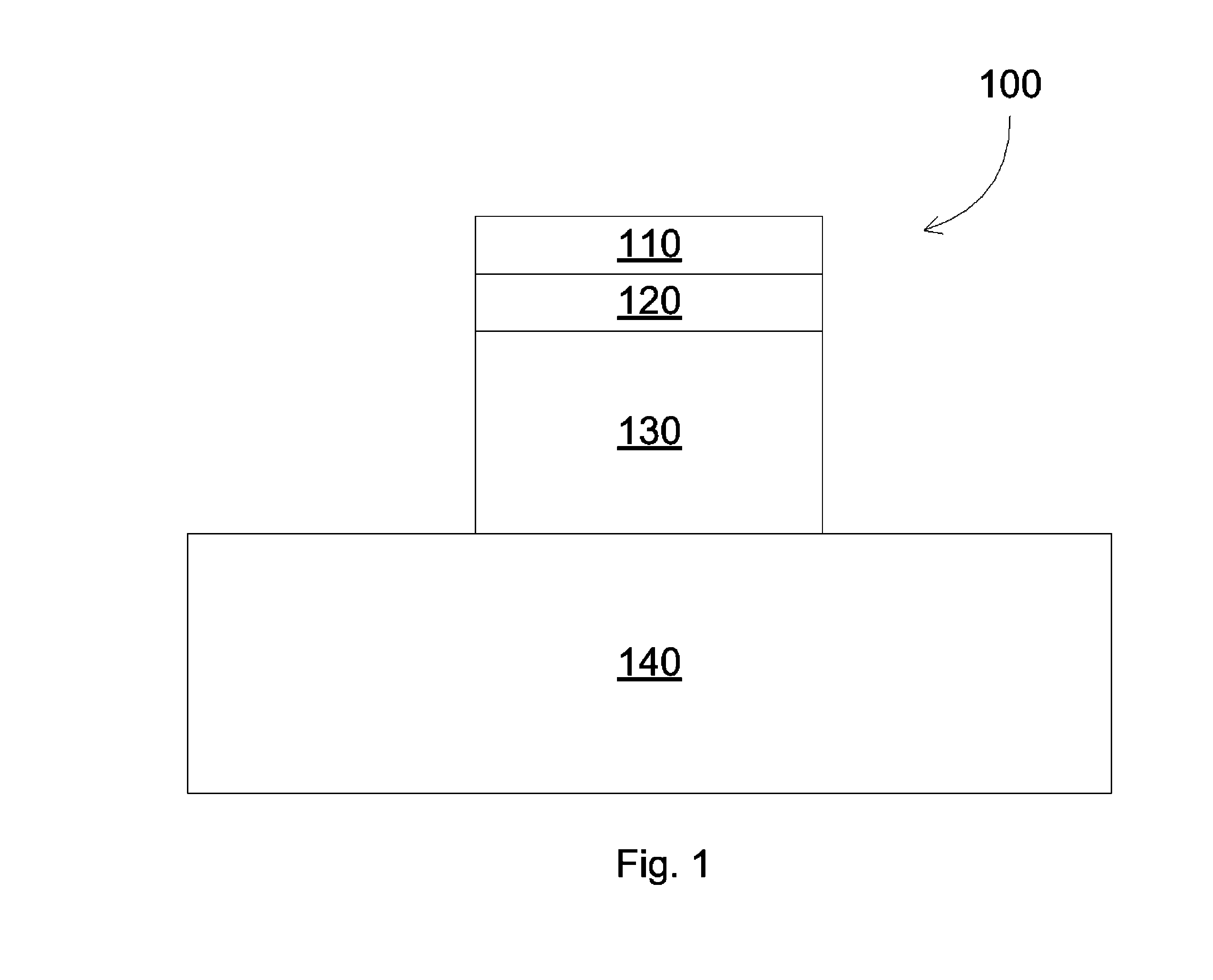

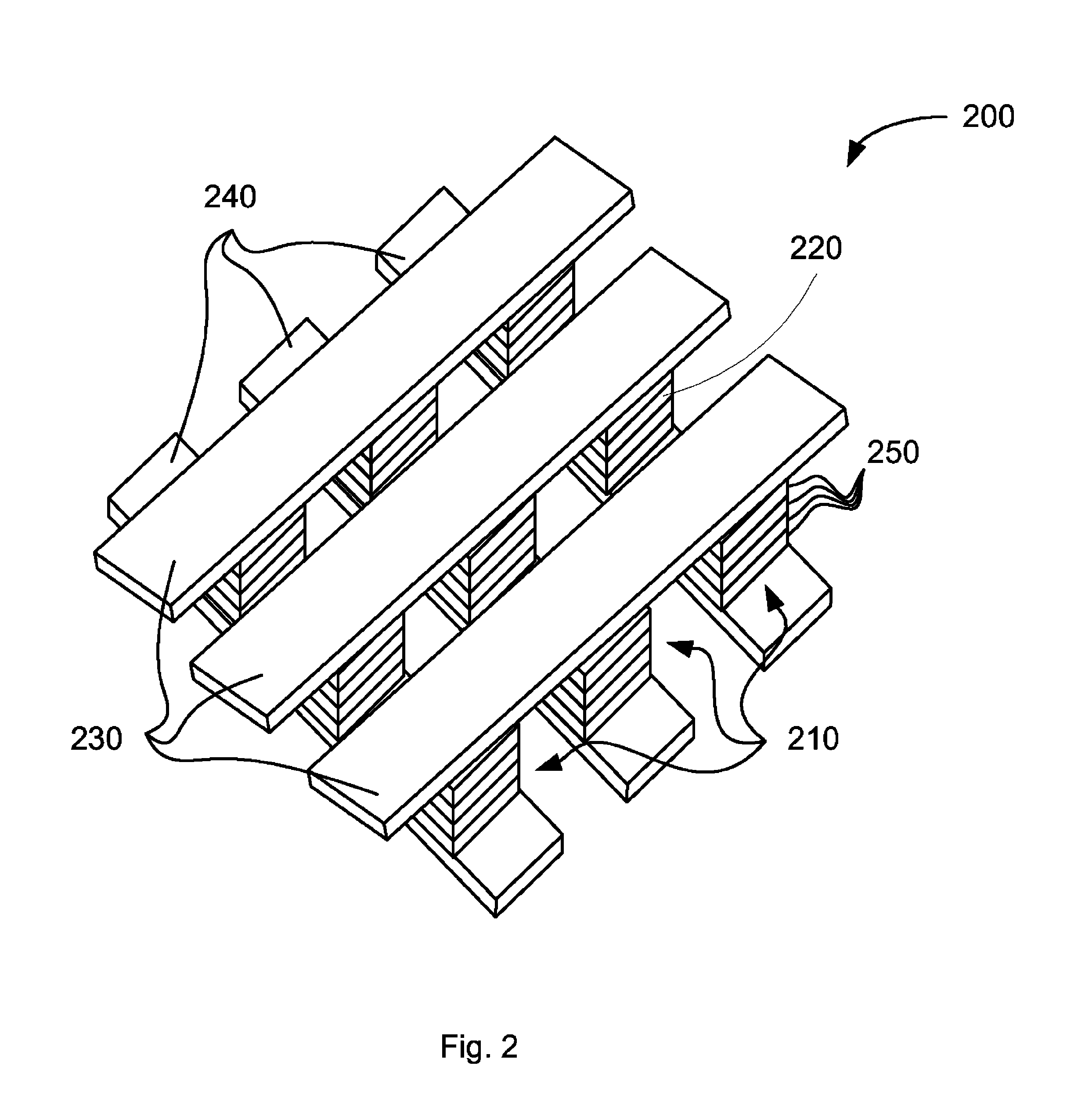

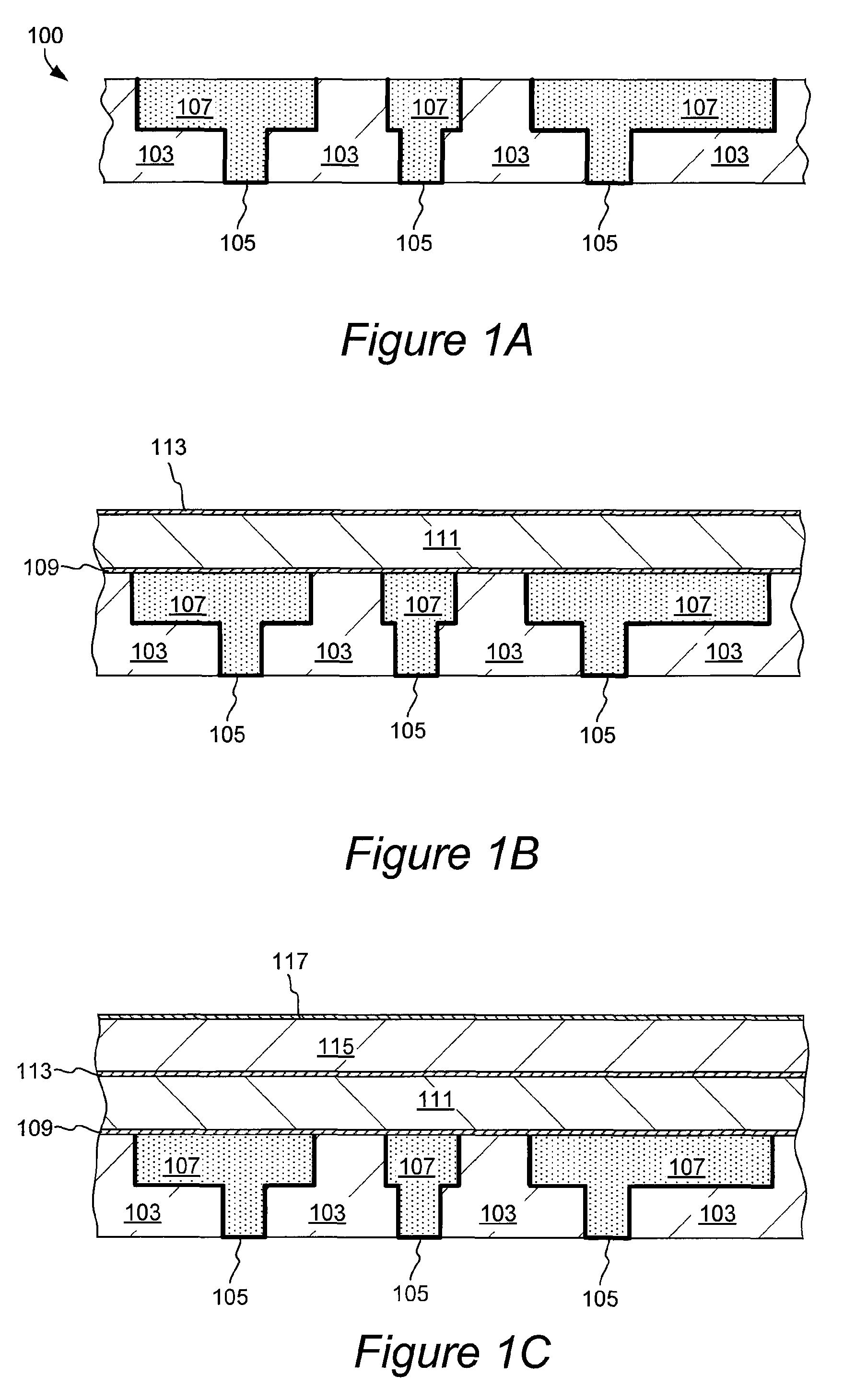

Methods for selective etching of a multi-layer substrate

InactiveUS20130137275A1Efficient etchingMinimal damageSolid-state devicesSemiconductor/solid-state device manufacturingEtchingPhysical chemistry

A method is disclosed for the selective etching of a multi-layer metal oxide stack comprising a platinum or tungsten layer on a TiN layer on an HfO2 or ZrO2 layer on a silicon substrate. In some embodiments, the method comprises a physical sputter process to selectively etch the platinum layer, followed by a first wet etch using a mixture of NH4OH and H2O2 to selectively etch the TiN layer, and a second wet etch using a dilute mixture of HF and HCl to selectively etch the HfO2 or ZrO2 layer.

Owner:INTERMOLECULAR

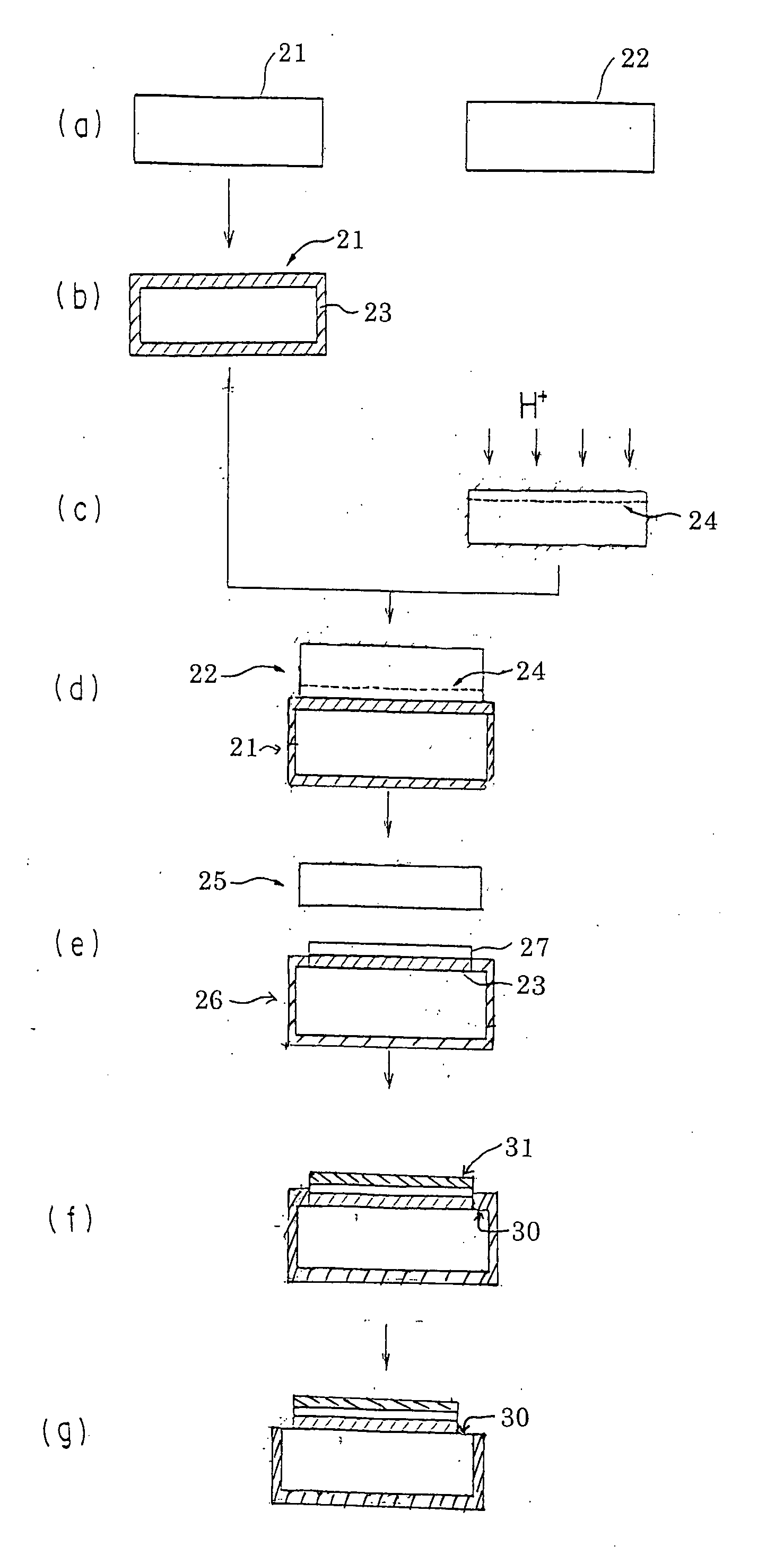

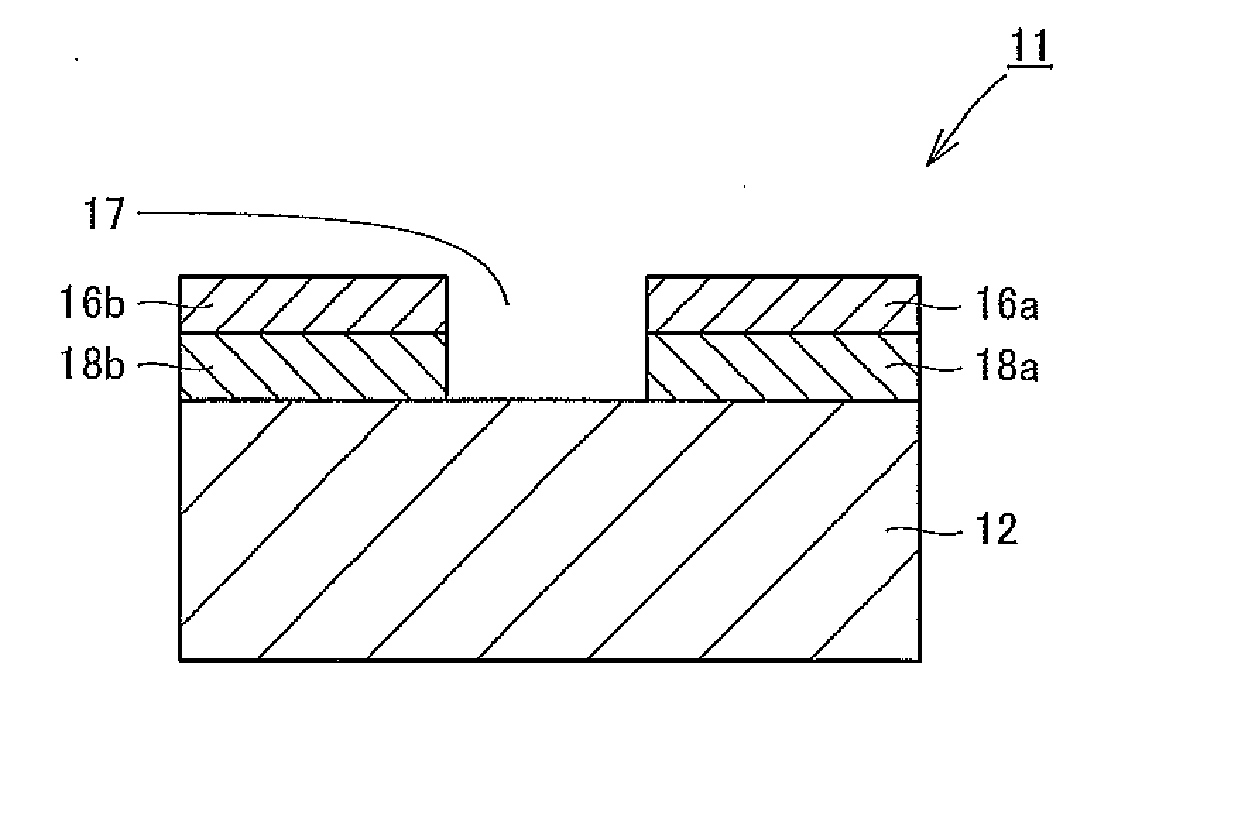

Method for Manufacturing Bonded Wafer and Bonded Wafer

InactiveUS20080315349A1Efficient etchingSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringOxide

The present invention provides a method for manufacturing a bonded wafer prepared by bonding a base wafer and a bond wafer, comprising at least a step of etching an oxide film in a terrace region in an outer periphery of the bonded wafer wherein the oxide film in the terrace region is etched by spin-etching with holding and spinning the bonded wafer. Thereby, there is provided a method for manufacturing a bonded wafer in which an oxide film formed in a terrace region of a base wafer is efficiently etched without removing an oxide film on the back surface of the base wafer.

Owner:SHIN-ETSU HANDOTAI CO LTD

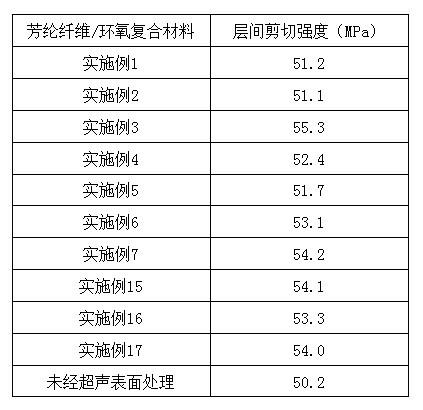

Ultrasonic surface modification treatment method for aramid fibers

InactiveCN102605606AImprove surface conditionQuality improvementFibre typesUltrasonic/sonic fibre treatmentPolymer scienceOrganic solvent

The invention provides an ultrasonic surface modification treatment method for aramid fibers. One or more amidic organic solvents in any proportion are selected as an ultrasonic treatment medium; under an ultrasonic action, fiber surfaces can be etched effectively by the amidic solvents; simultaneously, the sticking points among aramid fiber filaments can be reduced, and the state of the surfaces can be improved, so that the bonding strength between a resin and a fiber is increased; and meanwhile, the online treatment of the fibers is easy to realize by the ultrasonic treatment, and the time for modifying the fiber surfaces is shortened.

Owner:中蓝晨光化工有限公司

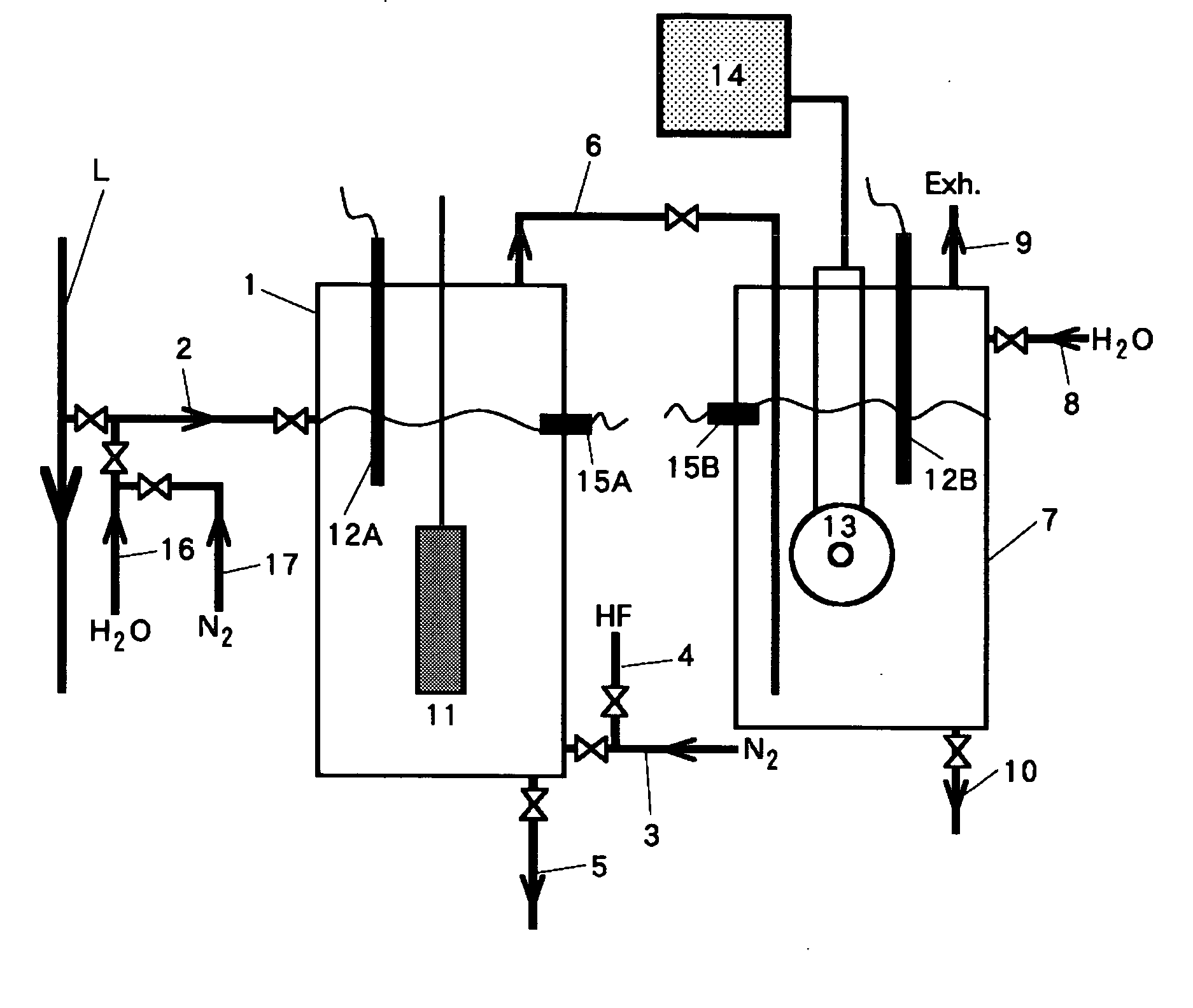

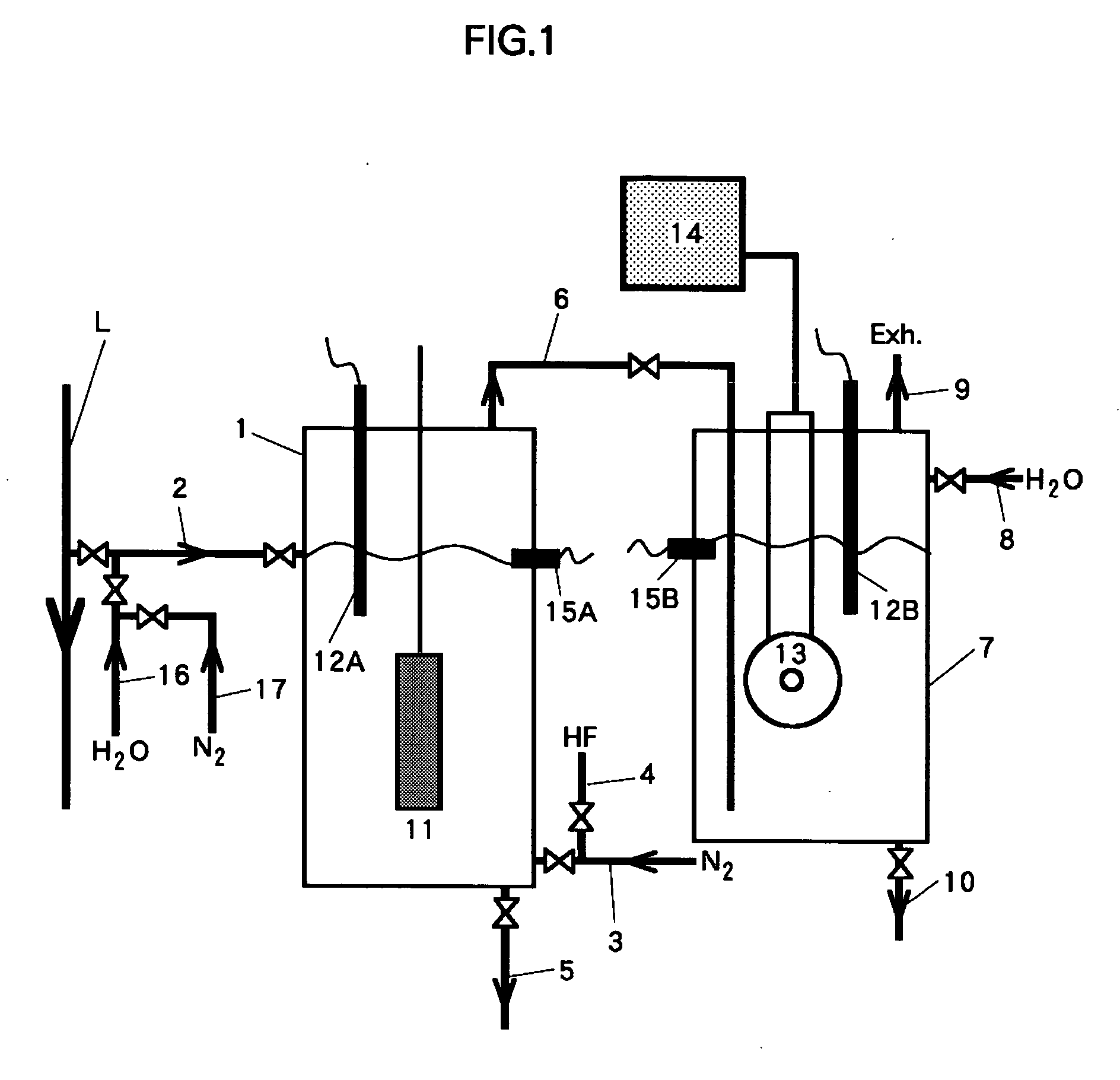

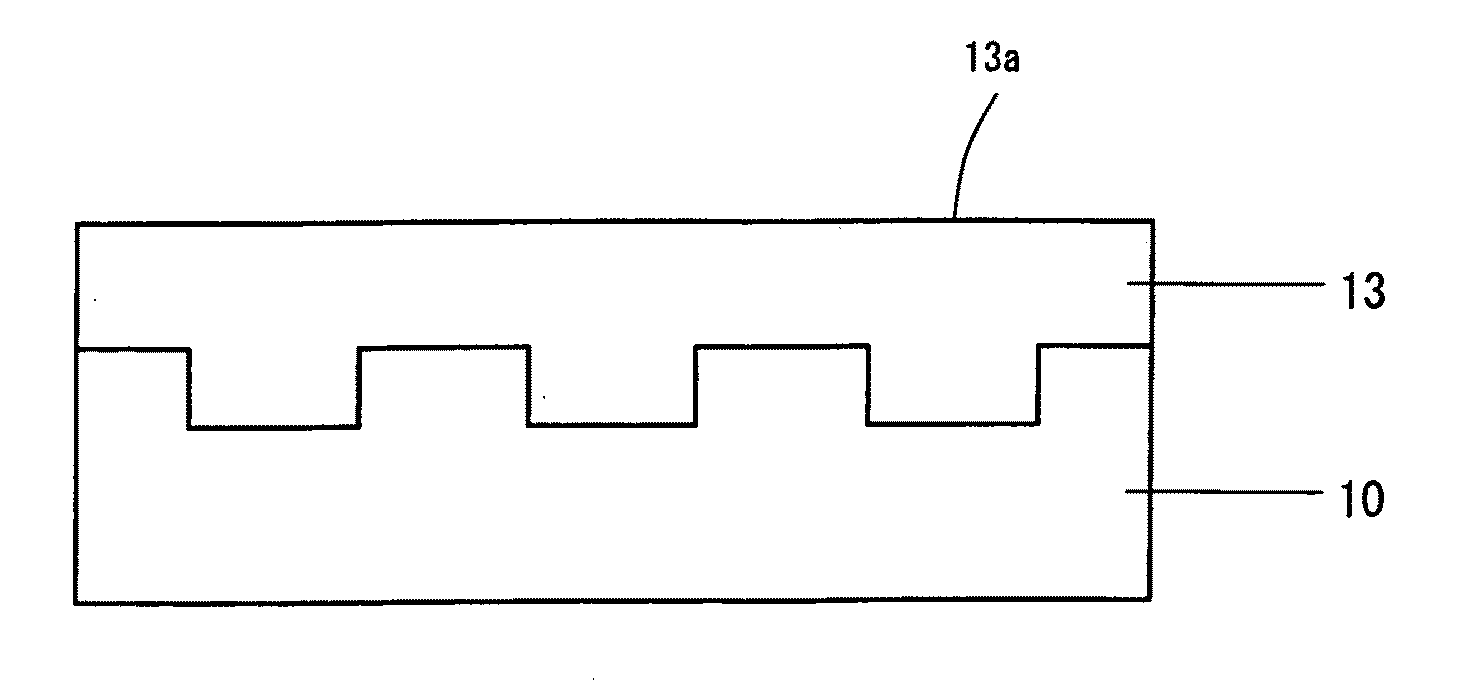

Equipment and method for measuring silicon concentration in phosphoric acid solution

ActiveUS20060263251A1Improve processing performanceReduce amountSemiconductor/solid-state device testing/measurementDecorative surface effectsIonCompound (substance)

Disclosed is equipment for measuring a silicon concentration in a phosphoric acid solution under use as an etching solution during operation of a semiconductor substrate processing system. The equipment is provided with at least a reaction tank and a concentration-measuring tank. The reaction tank includes a reaction unit for adding hydrofluoric acid to a predetermined constant amount of the phosphoric acid solution drawn out of the semiconductor substrate processing system to form a silicon fluoride compound and then causing the silicon fluoride compound to evaporate. The concentration-measuring tank comprises a hydrolysis unit for bubbling the silicon fluoride compound, which has evaporated from the reaction tank, through deionized water to hydrolyze the silicon fluoride compound and a measurement unit for determining a change rate of silicon concentration in the deionized water subsequent to the bubbling. Also disclosed is a method for measuring a silicon concentration in a phosphoric acid solution under recirculation and use as an etching solution in a semiconductor substrate processing system in operation.

Owner:TATSUMO KK

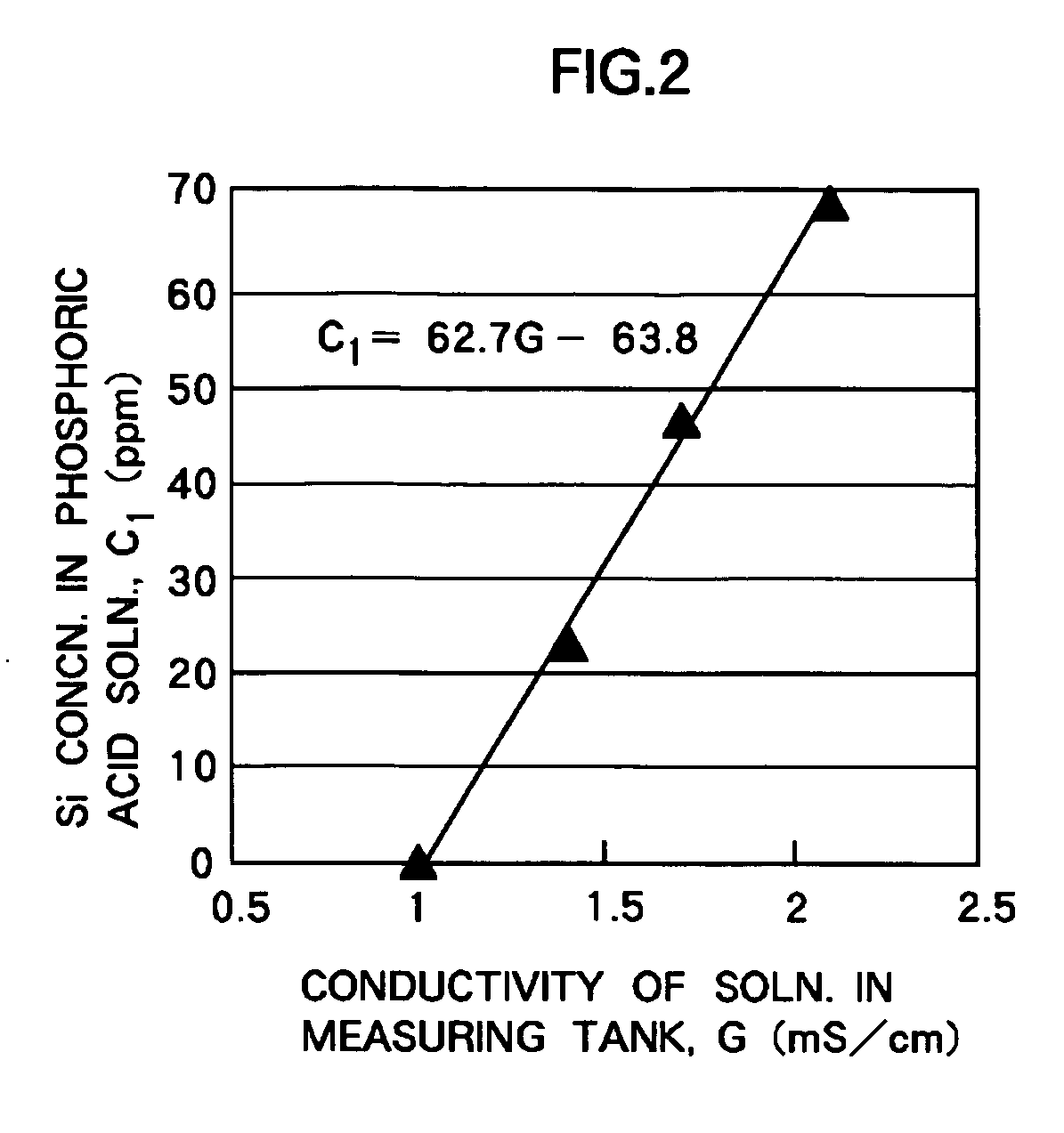

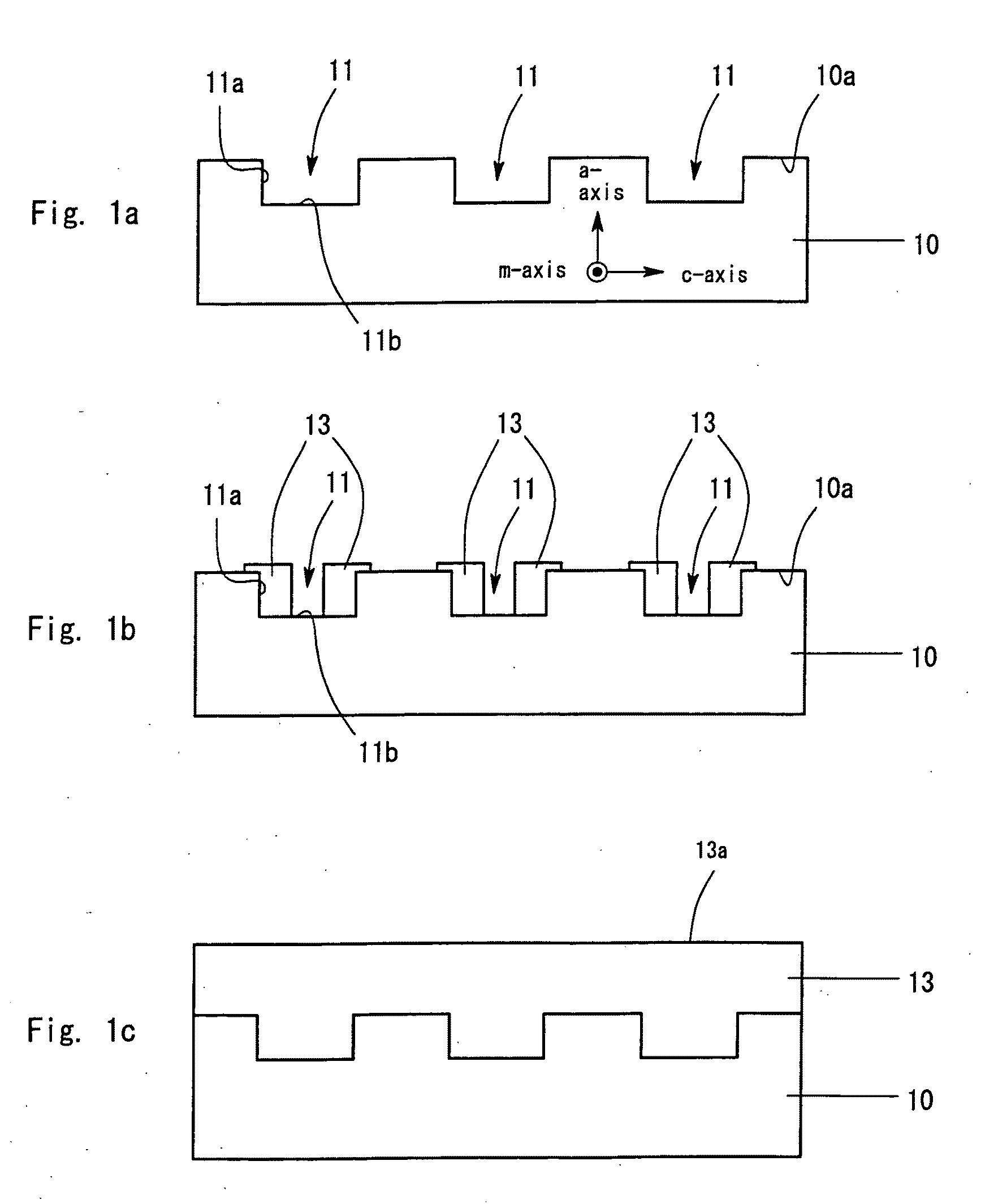

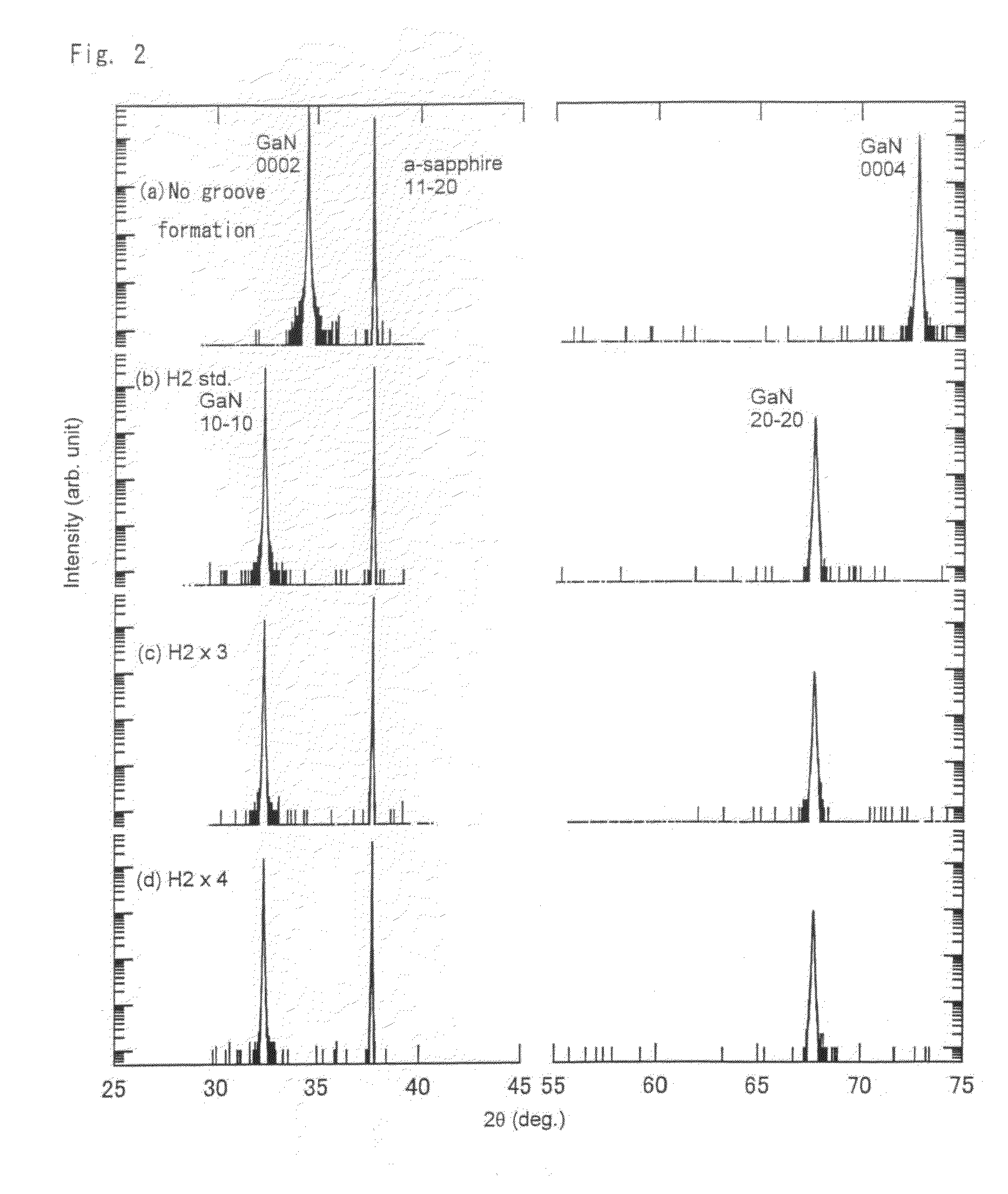

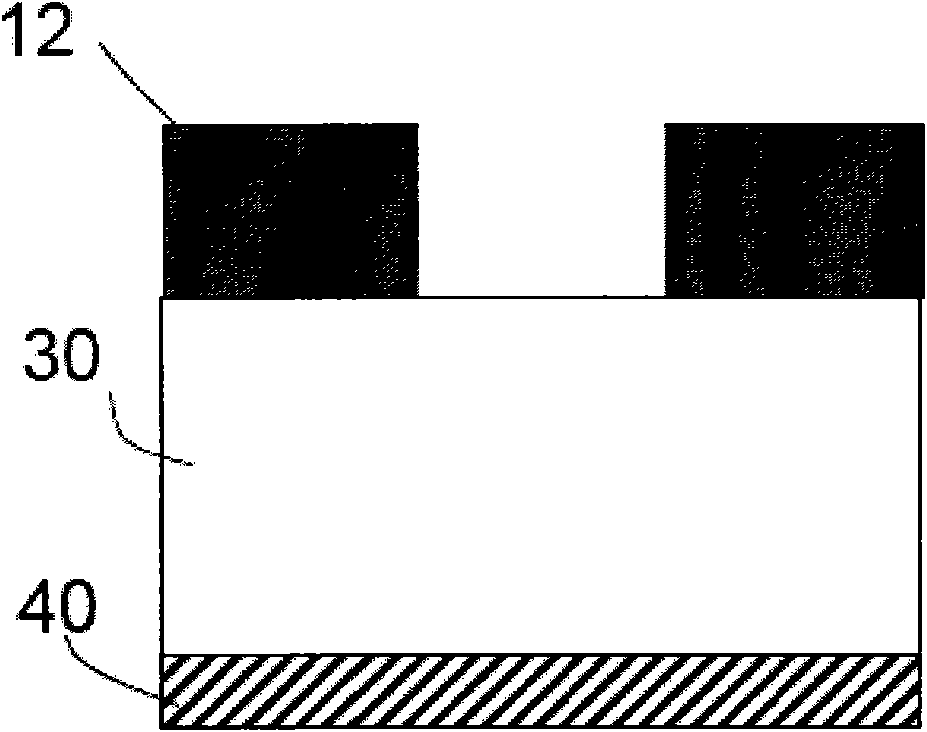

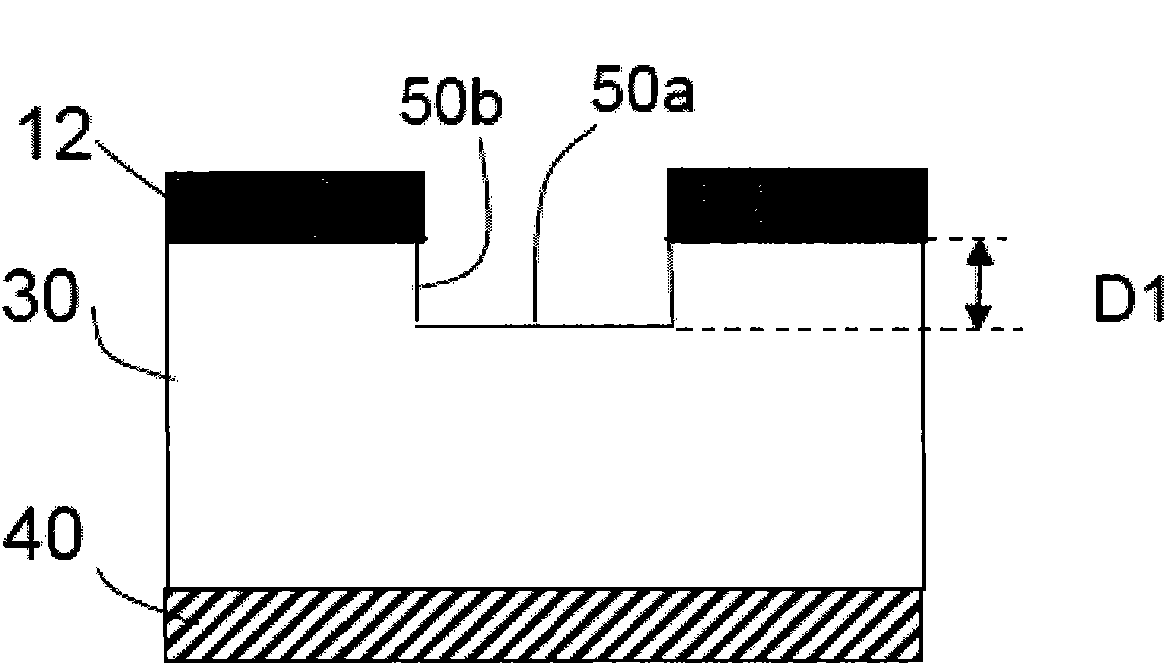

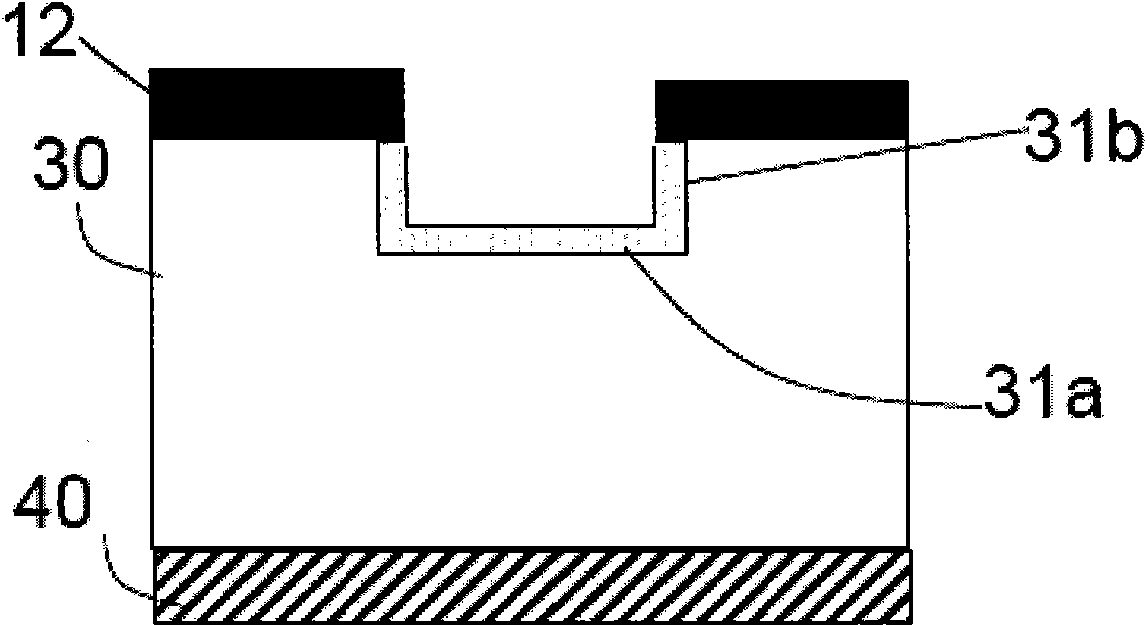

Method for producing group III nitride semiconductor and template substrate

ActiveUS20100102360A1High crystallinityImprove surface flatnessSemiconductor/solid-state device manufacturingSemiconductor devicesSputteringHydrogen

The present invention provides a method for producing a Group III nitride semiconductor. The method includes forming a groove in a surface of a growth substrate through etching; forming a buffer film on the groove-formed surface of the growth substrate through sputtering; heating, in an atmosphere containing hydrogen and ammonia, the substrate to a temperature at which a Group III nitride semiconductor of interest is grown; and epitaxially growing the Group III nitride semiconductor on side surfaces of the groove at the growth temperature. The thickness of the buffer film or the growth temperature is regulated so that the Group III nitride semiconductor is grown primarily on the side surfaces of the groove in a direction parallel to the main surface of the growth substrate. The thickness of the buffer film is regulated to be smaller than that of a buffer film which is employed for epitaxially growing the Group III nitride semiconductor on a planar growth substrate uniformly in a direction perpendicular to the growth substrate. The growth temperature is regulated to be lower than a temperature at which the Group III nitride semiconductor is epitaxially grown on a planar growth substrate uniformly in a direction perpendicular to the growth substrate. The growth temperature is preferably 1,020 to 1,100° C. The buffer film employed is an AlN film having a thickness of 150 Å or less.

Owner:TOYODA GOSEI CO LTD

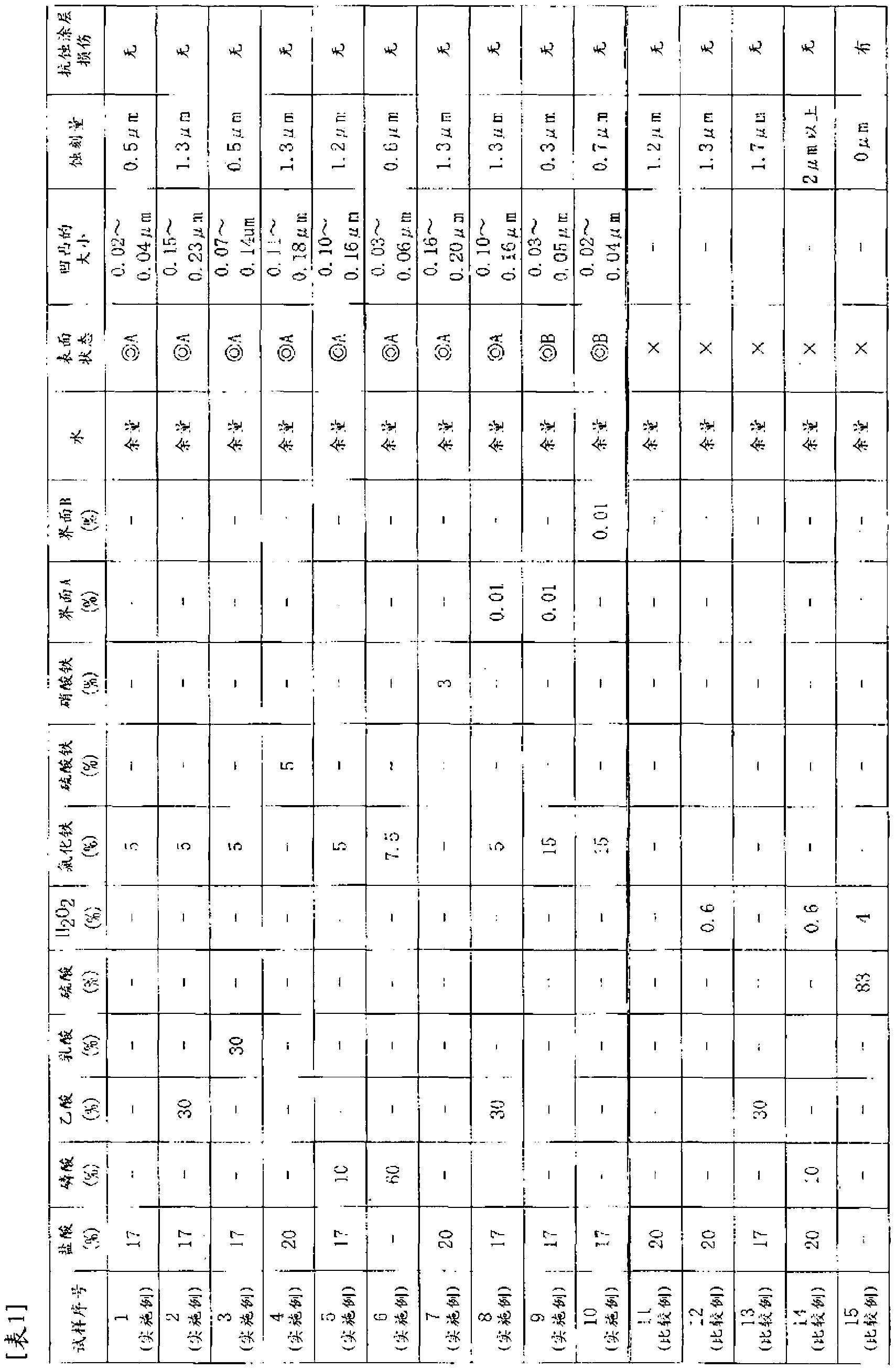

Etching fluid composition and etching method

ActiveCN103125017AEfficient etchingSemiconductor/solid-state device manufacturingSemiconductor devicesOrganic acidPhosphoric acid

A composition is adopted that includes an inorganic acid and a metal compound. The composition further includes an organic acid, an organic acid salt, an inorganic acid salt, or a surfactant. The composition further includes hydrochloric acid, phosphoric acid, sulfuric acid, or nitric acid, as the inorganic acid. Furthermore, an iron-based compound is used as the metal compound. At least one acid selected from a group comprising monocarboxylic acid, polycarboxylic acid, oxycarboxylic acid, phosphonic acid, sulfonic acid and salts thereof is used as the organic acid and the organic acid salt. Using the etching fluid composition according to the present invention, a semiconductor film of AlGaInP film, AlGaAs film or GaAsP film is etched, and the surface is made rough.

Owner:HAYASHI PURE CHEM IND LTD

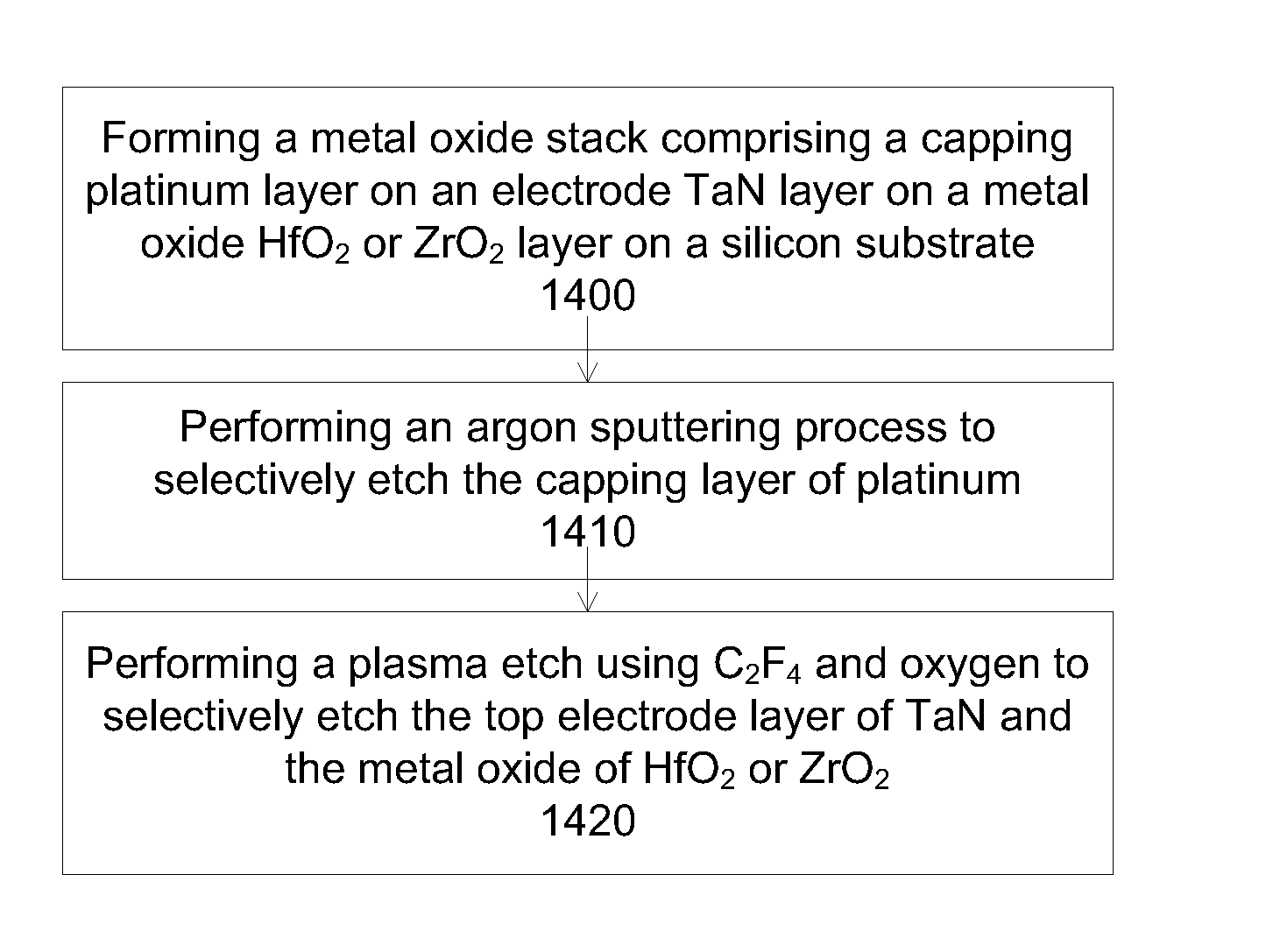

Methods For Selective Etching Of A Multi-Layer Substrate

InactiveUS20140077147A1Efficient etchingMinimal damageSolid-state devicesSemiconductor/solid-state device manufacturingPlatinumOxygen

A method is disclosed for the selective etching of a multi-layer metal oxide stack comprising a platinum layer on a TiN layer on an HfO2 or ZrO2 layer on a substrate. In some embodiments, the method comprises a physical sputter process to selectively etch the platinum layer, followed by a plasma etch process comprises CHF3 and oxygen to selectively etch the TiN, HfO2 or ZrO2 layers with respect to the substrate.

Owner:INTERMOLECULAR

Methods for selective etching of a multi-layer substrate

InactiveUS8613863B2Efficient etchingMinimal damageDecorative surface effectsSolid-state devicesPlatinumEtching

A method is disclosed for the selective etching of a multi-layer metal oxide stack comprising a platinum or tungsten layer on a TiN layer on an HfO2 or ZrO2 layer on a silicon substrate. In some embodiments, the method comprises a physical sputter process to selectively etch the platinum layer, followed by a first wet etch using a mixture of NH4OH and H2O2 to selectively etch the TiN layer, and a second wet etch using a dilute mixture of HF and HCl to selectively etch the HfO2 or ZrO2 layer.

Owner:INTERMOLECULAR

Etchant composition and etching method

ActiveUS20140235064A1Maintain good propertiesHigh selectivity ratioSemiconductor/solid-state device manufacturingSurface treatment compositionsHydrofluoric acidInorganic salts

This invention is concerning an etchant composition used to etch a silicon-containing film formed on a target substrate. The etchant composition includes at least one selected from the group consisting of an organic compound containing a hydroxyl group, an organic compound containing a carbonyl group, an inorganic acid and inorganic salt, hydrofluoric acid, ammonium fluoride and an organic acid.

Owner:HAYASHI PURE CHEM IND LTD

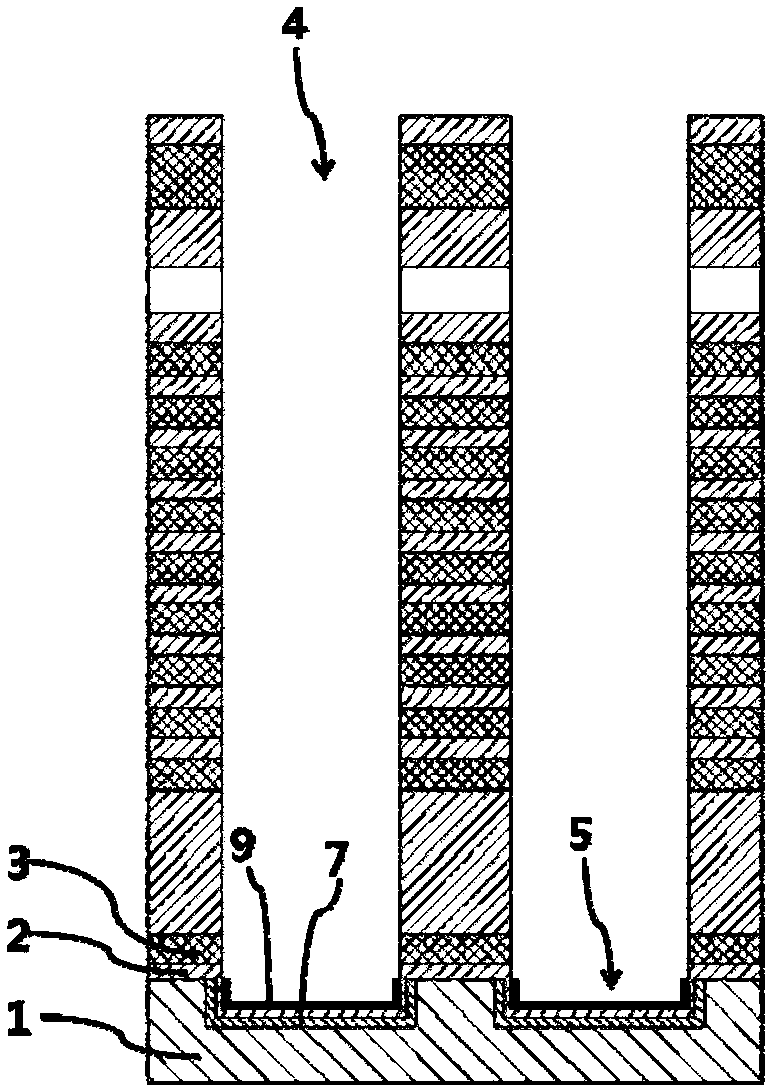

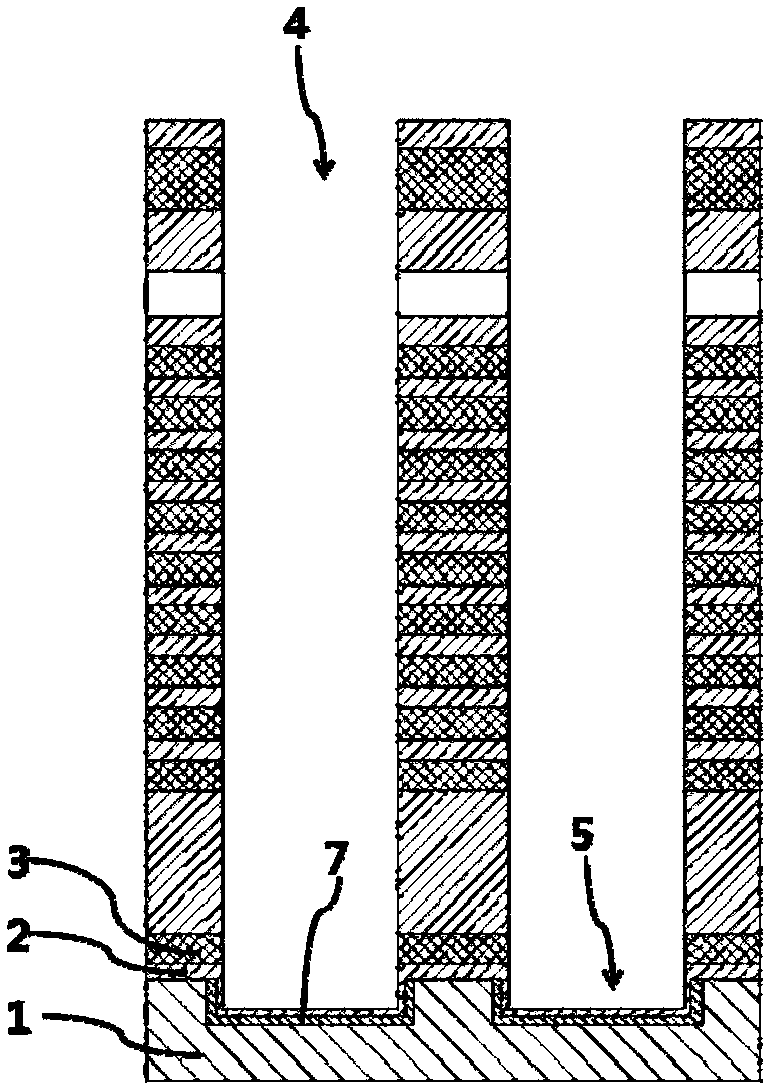

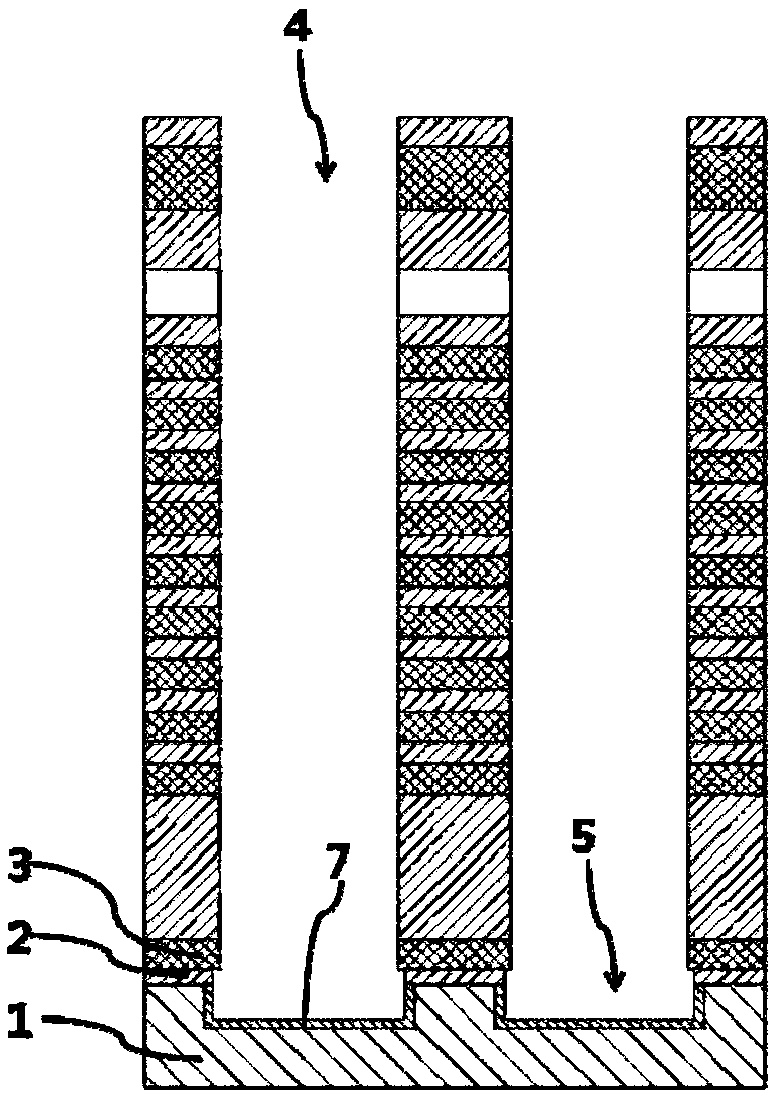

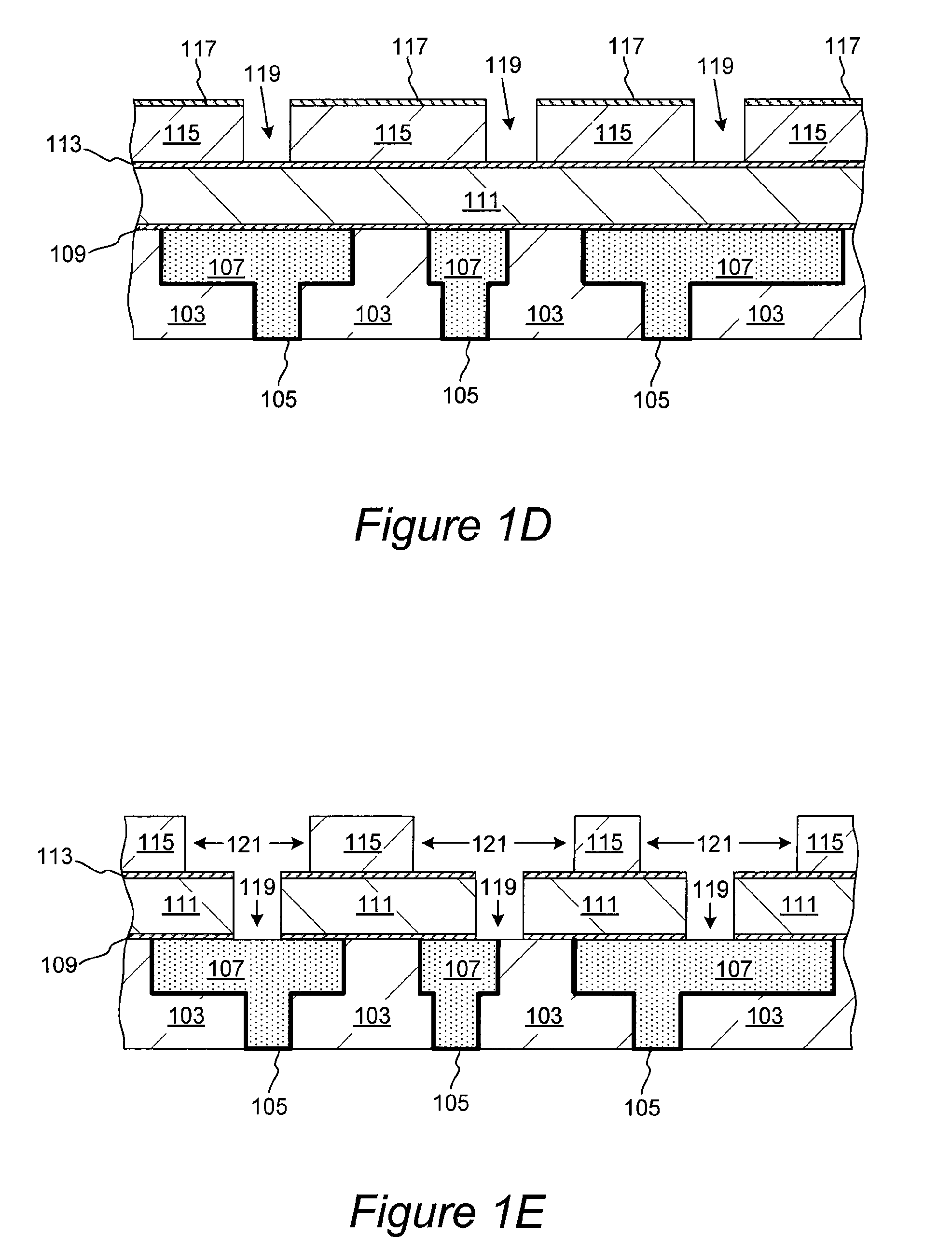

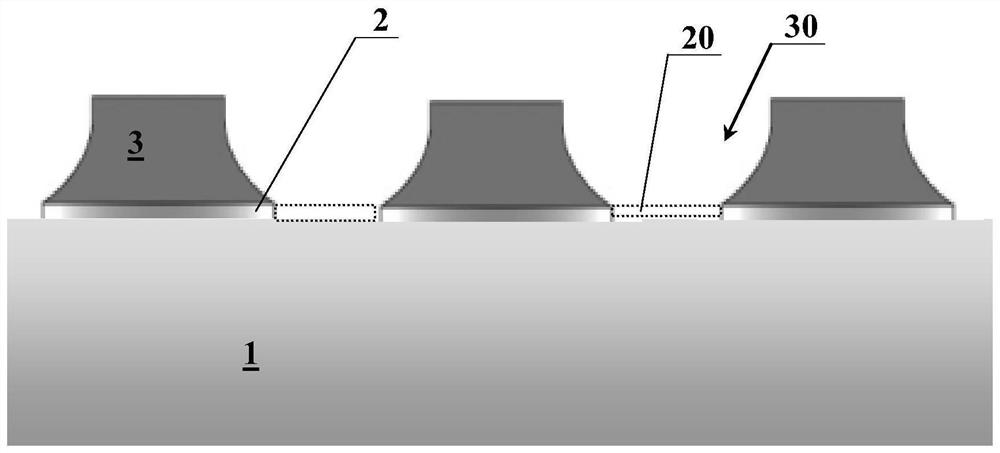

Process for epitaxial growth of silicon in three-dimensional (3D) NAND flash structure

InactiveCN107611130AEliminate residueEfficient etchingSolid-state devicesSemiconductor devicesGrowth heightLattice defects

The invention provides a process for epitaxial growth of silicon in a three-dimensional (3D) NAND flash structure. The method comprises the steps of depositing a substrate lamination structure; etching the substrate lamination structure to form a channel and a silicon groove in a substrate surface; cleaning the channel and the silicon groove; performing high-temperature annealing; forming epitaxial growth of the silicon, and cleaning the silicon in advance; and performing epitaxial growth of the silicon. By high-temperature annealing, the surface of the silicon groove damaged by etching is oxidized, so that resided polymer in the silicon groove in the bottom of the channel is eliminated, meanwhile, a certain oxidization repair effect also can be generated on the surface, which is damaged,of the silicon subsequently and epitaxially grown, and interface damage and lattice defect are eliminated; the step of wet cleaning is added before high-temperature annealing, the subsequent and better effects of oxidization annealing and interface repair can be obtained; and by the process, the deep channel can be effectively etched, oxide residue is prevented, damage to an interface layer by etching is prevented, so that the epitaxial growth height uniformity of the silicon is improved, an epitaxial growth gap of the silicon is prevented, and the comprehensive performance of a 3D NAND flashis improved.

Owner:YANGTZE MEMORY TECH CO LTD

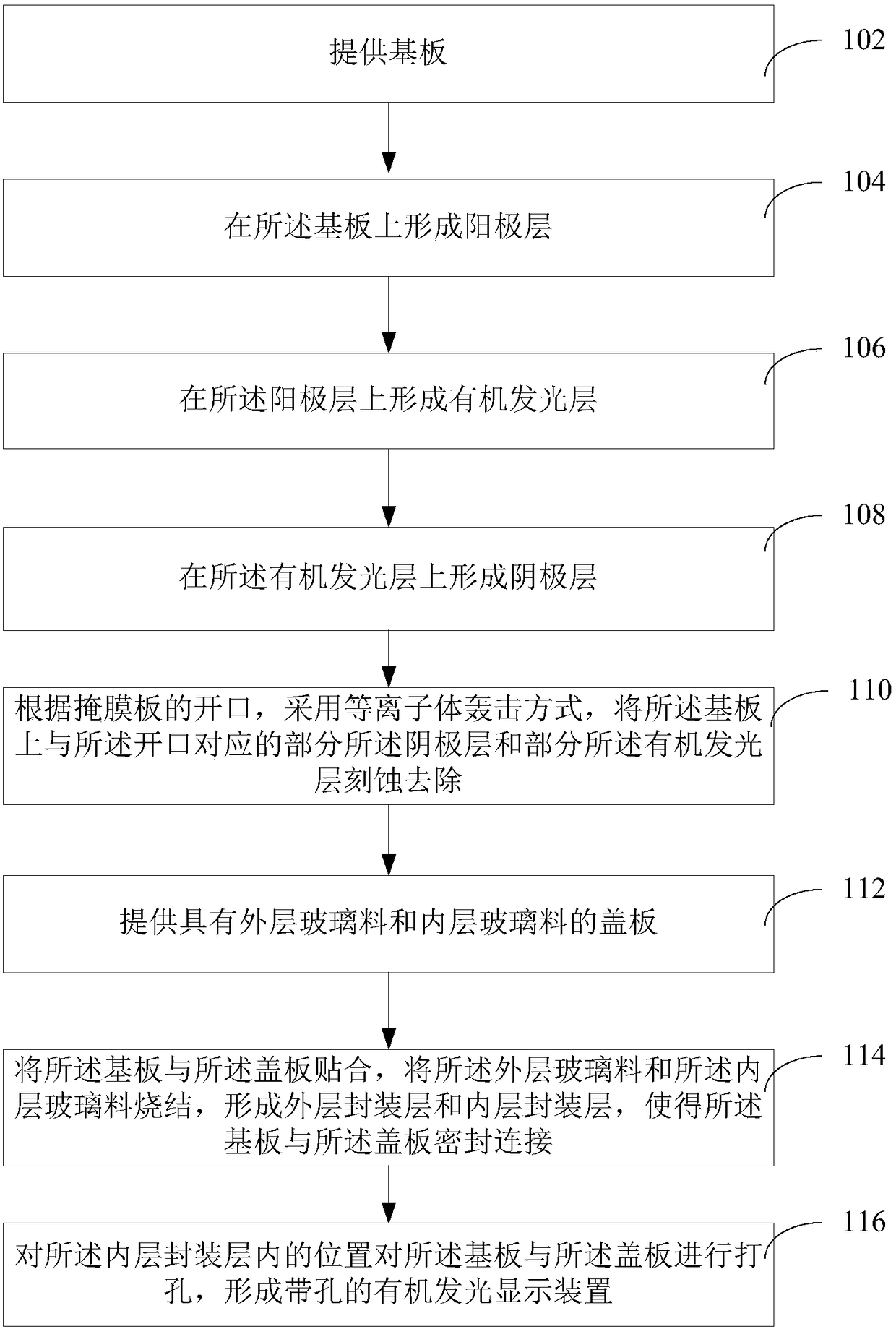

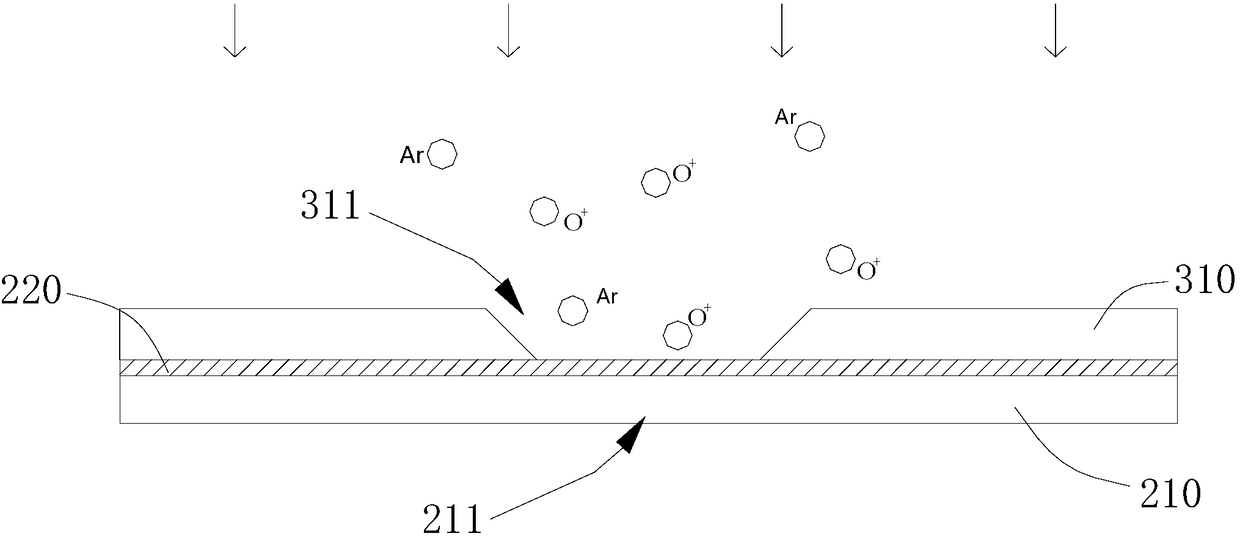

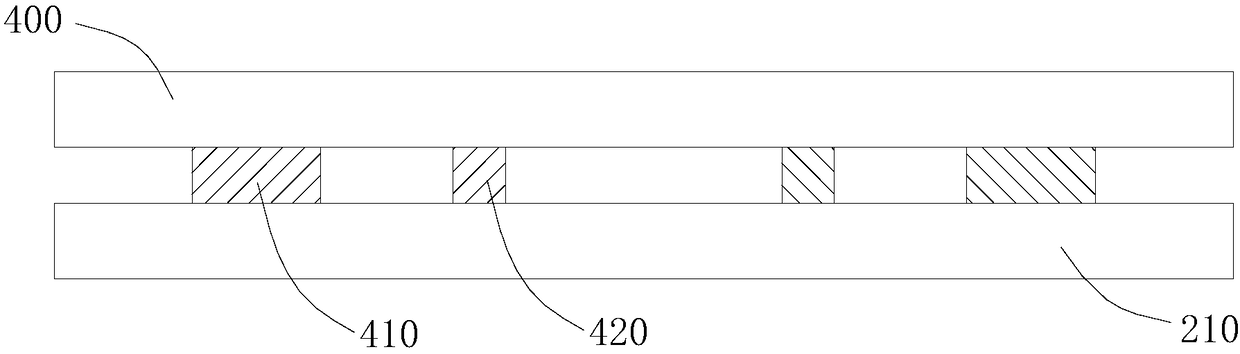

Organic light-emitting display apparatus and preparation method thereof

InactiveCN108206244AEfficient etchingWon't burnSolid-state devicesSemiconductor/solid-state device manufacturingEtchingChemistry

The invention relates to an organic light-emitting display apparatus and a preparation method thereof. The preparation method comprises the steps of providing a substrate; forming a positive electrodelayer on the substrate; forming an organic light-emitting layer on the positive electrode layer; forming a negative electrode layer on the organic light-emitting layer; removing a part of the negative electrode layer and a part of the organic light-emitting layer which are corresponding to an opening in the substrate through etching by adopting a plasma bombardment mode through the opening of a mask plate; providing a cover plate with an outer layer glass material and an inner layer glass material; enabling the substrate to be laminated with the cover plate, and performing sintering on the outer layer glass material and the inner layer glass material to form an outer layer packaging layer and an inner layer packaging layer, and enabling the substrate and the cover plate to be connected ina sealing manner; and performing hole punching on the substrate and the cover plate in the inner layer packaging layer to form the organic light-emitting display apparatus with holes. By virtue of the plasma bombardment mode, more efficient organic material etching can be realized, and higher production efficiency and higher etching precision are achieved; and in addition, scalding to a pixel region can be avoided, the etching cost can be lower and the production cost can be lowered effectively.

Owner:TRULY HUIZHOU SMART DISPLAY

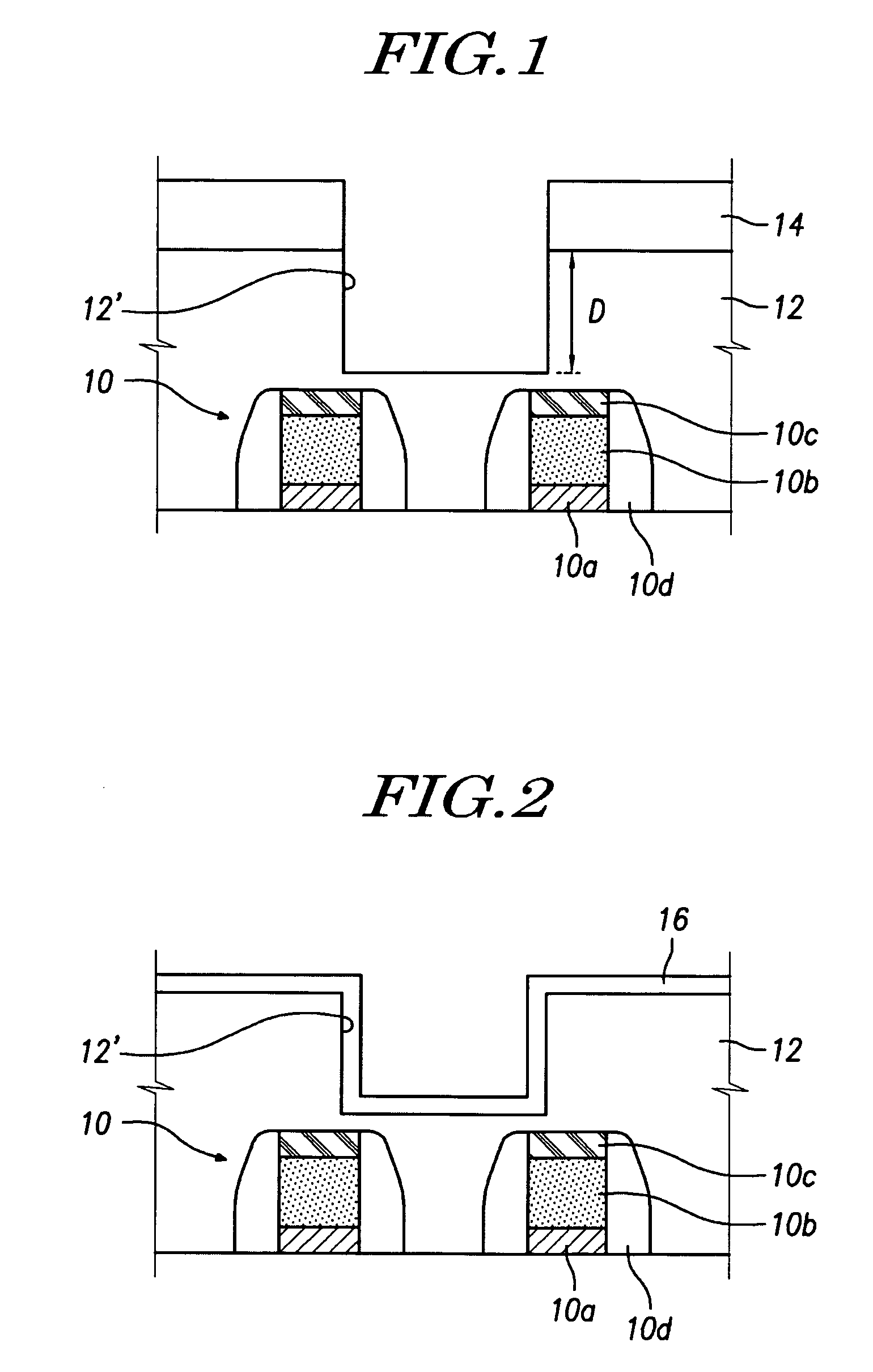

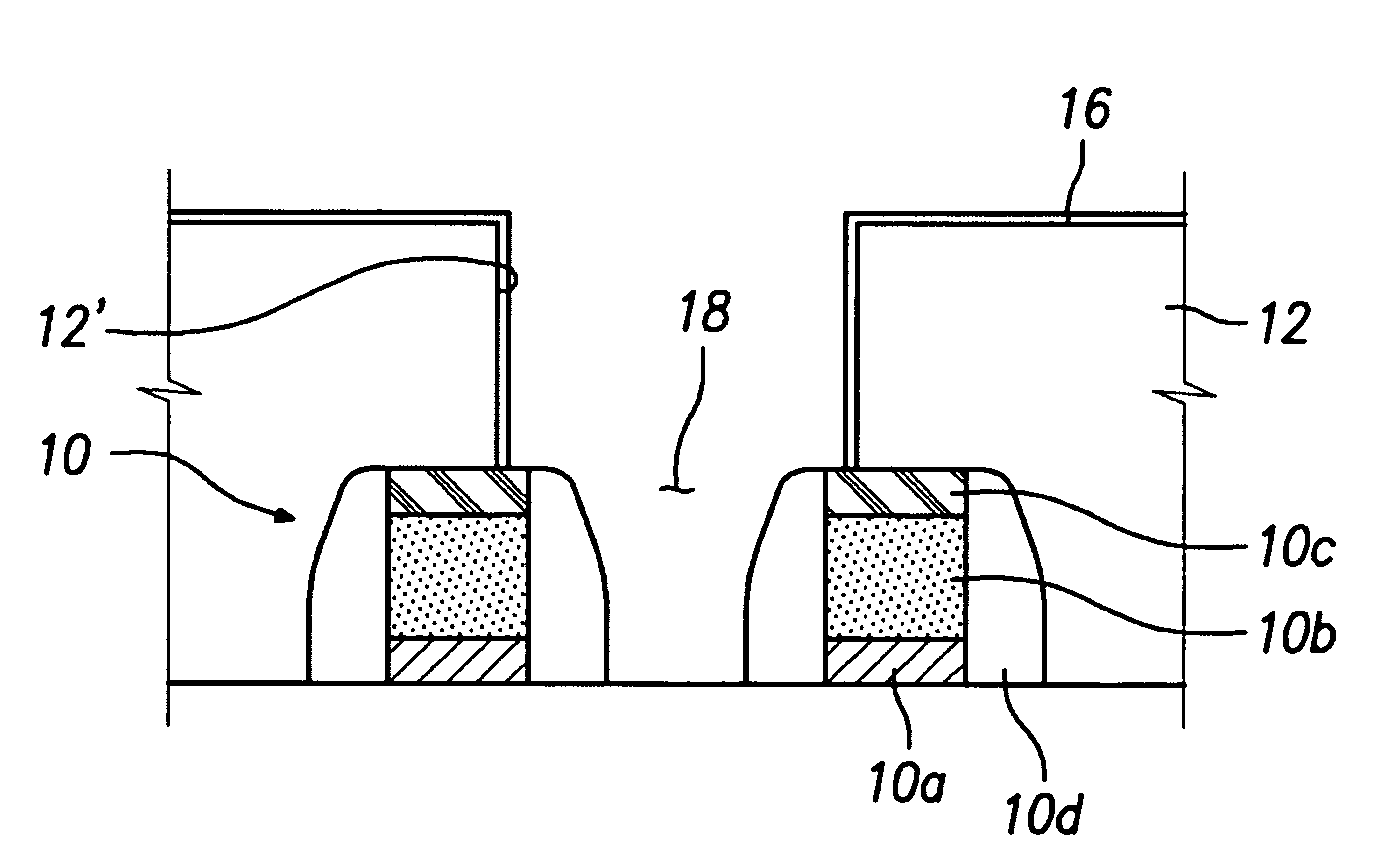

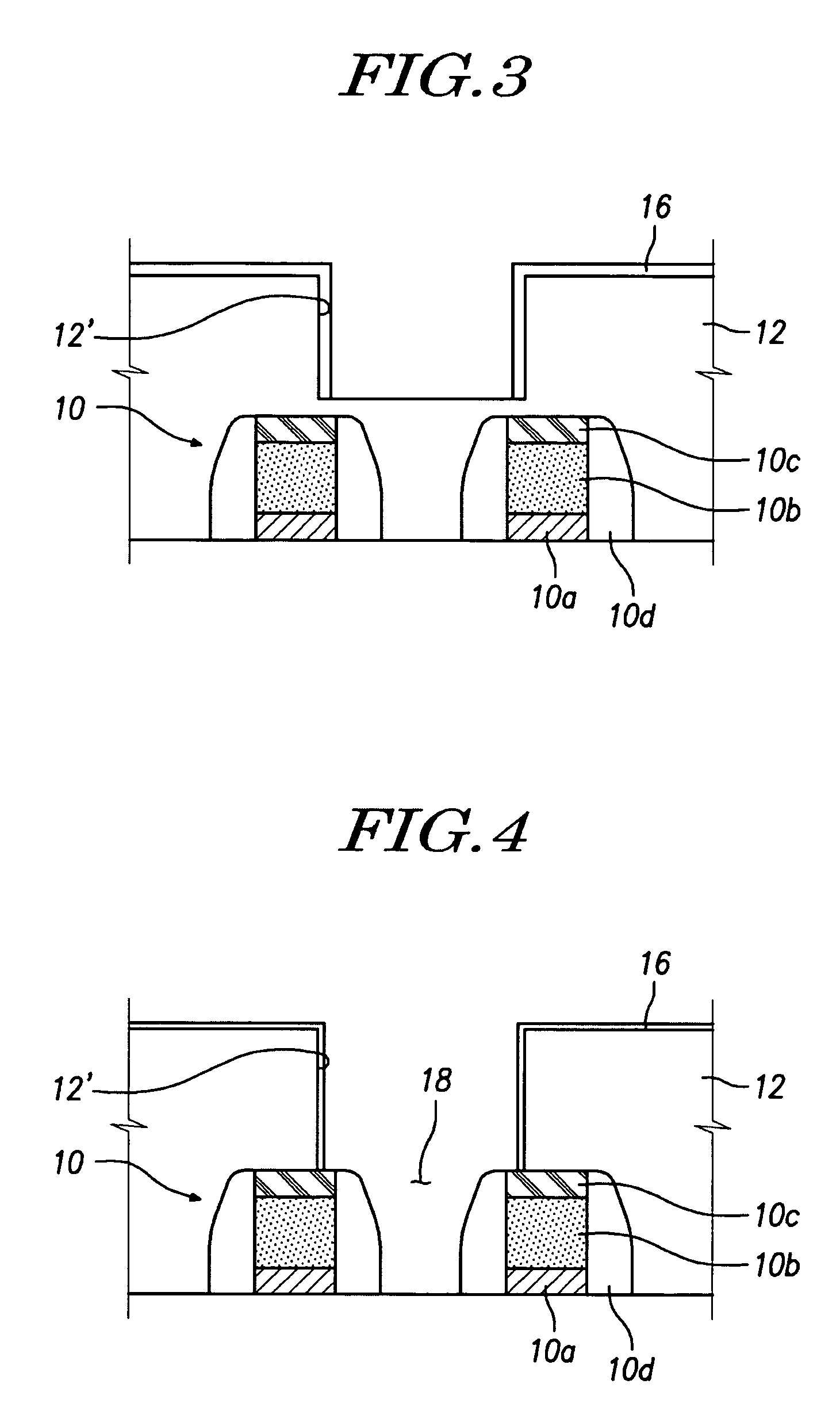

Method for fabricating self-aligned contact hole

InactiveUS20060160356A1Improve etch selectivityEfficient etchingSemiconductor/solid-state device detailsSolid-state devicesDevice materialGate oxide

Disclosed are: (i) a method for fabricating self-aligned contact hole in a semiconductor device, and (ii) a semiconductor device having a self-aligned contact. The method comprises the steps of: (a) forming an oxide layer covering a gate structure on a semiconductor substrate, the gate structure including a gate oxide pattern, a gate electrode pattern, a hard-mask nitride pattern, and a spacer nitride on sidewalls thereof; (b) forming a mask pattern on the oxide layer; (c) forming a contact trench by removing a portion of the oxide layer, exposed by the mask pattern, to a predetermined depth; (d) forming a buffer layer on the oxide layer, including in the contact trench; (e) etching a portion of the buffer layer at a bottom of the contact trench to expose a portion of the oxide layer; and (f) forming a contact hole by etching the exposed oxide layer using a remaining buffer layer as an etching mask.

Owner:DONGBU ELECTRONICS CO LTD

Dry etching agent and dry etching method

ActiveUS9017571B2Less effectImprove efficiencyOrganic chemistryDecorative surface effects1,3,3,3-TetrafluoropropeneDry etching

Owner:CENT GLASS CO LTD

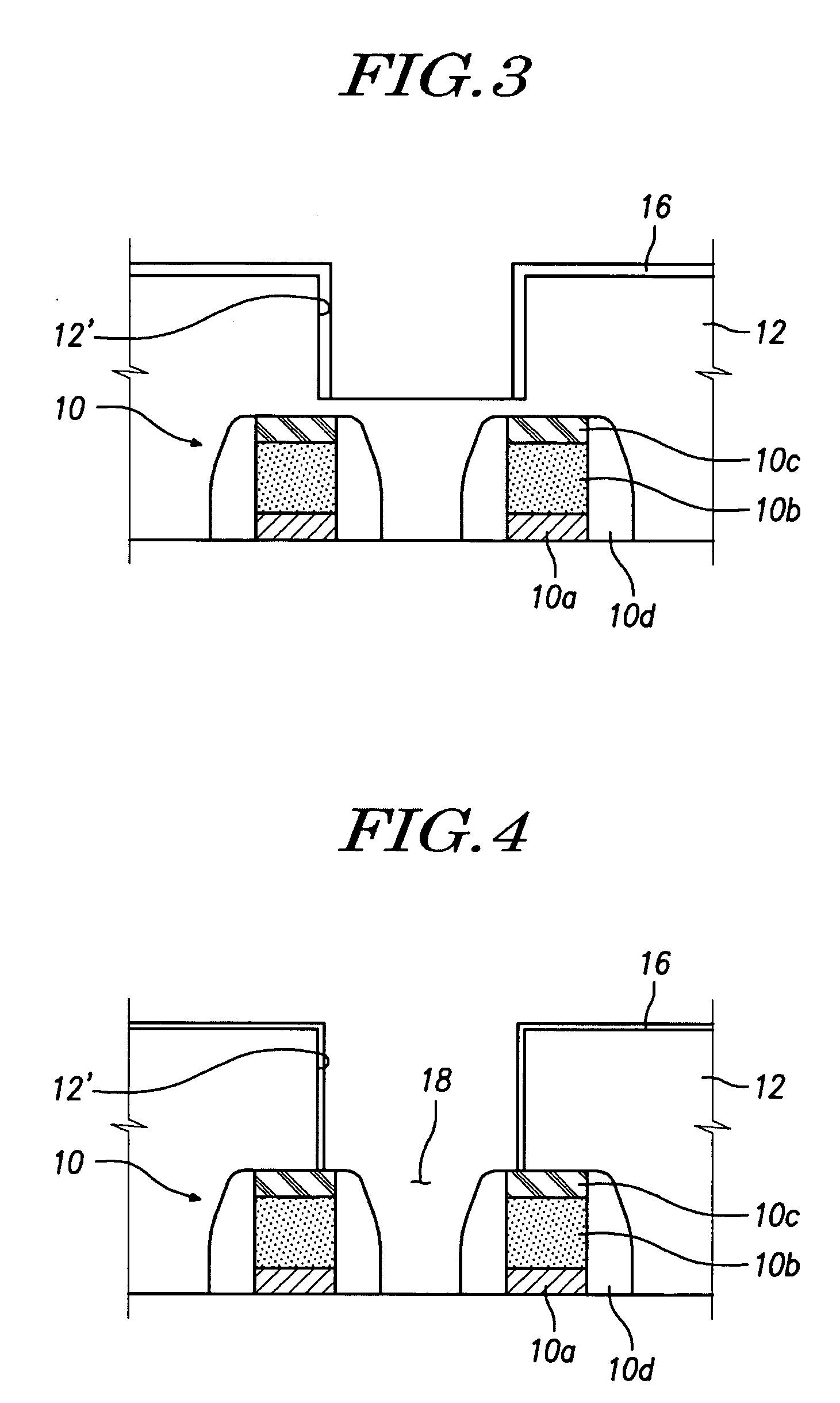

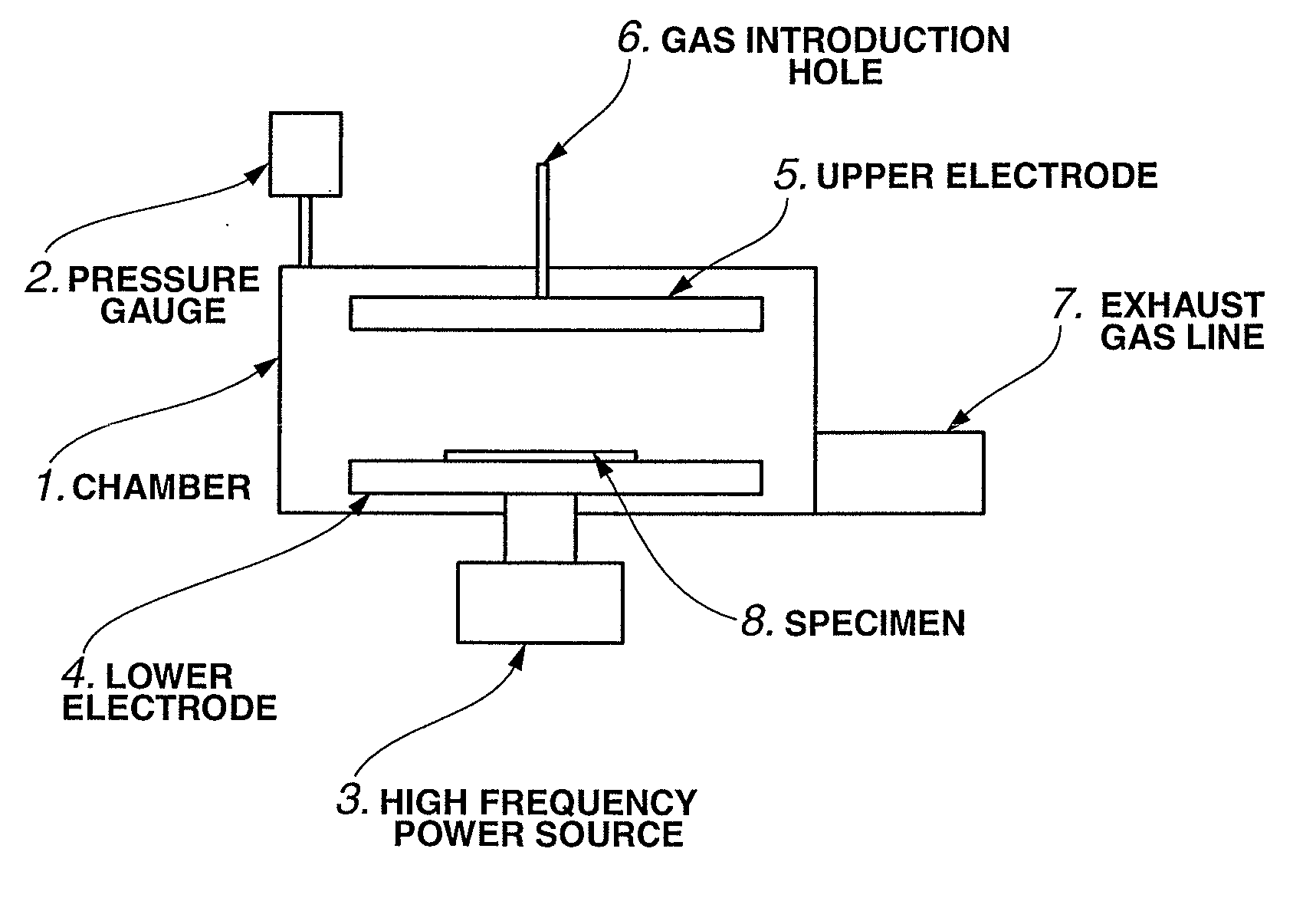

Plasma etching method of insulating layer containing silicon

InactiveCN101789372ABest etching precisionEfficient etchingSemiconductor/solid-state device manufacturingPlasma etchingPolymer

The invention discloses a plasma etching method of an insulating layer containing silicon, comprising an etching step and a side wall passivation step which are mutually independent, wherein the etching step and the wall passivation step are alternated and recycled in the etching process until the target depth is obtained by etching. The etching step comprises: etching gas is provided to etch an insulating material layer containing silicon under the action of plasma to a certain depth so as to expose one etching interface, wherein the etching interface comprises a side wall; and the side wall passivation step comprises: reaction gas containing carbon and hydrogen is provided, polymer containing carbon and hydrogen is formed on the side wall of the etching interface under the action of plasma and is deposited or attached to the side wall surface of the etching interface. The etching method of the invention quickly etches the insulating layer containing silicon and protects the side wall, obtains better appearance outline and solves the problems that the arc-shaped side wall and critical dimension when channels or through holes are etched in the prior art are offset.

Owner:ADVANCED MICRO FAB EQUIP INC CHINA

Texturization technology of solar battery

InactiveCN102751380AEfficient etchingGuaranteed open circuit voltageFinal product manufactureCleaning using liquidsEngineeringSolar battery

The invention discloses a texturization technology of a solar battery, which adopts reactive ion etching, and comprises the following steps of: a. selecting the radio-frequency power of 25-30Kw, filling gases including Cl2, SF6 and O2 into a reaction cavity, and carrying out plasma bombardment on the surface of a silicon slice, wherein the technology time is 60-80s; b. selecting the radio-frequency power of 12-18Kw, filling gases including Cl2 and SF6 into the reaction cavity, and carrying out plasma bombardment on the surface of the silicon slice, wherein the technology time is 20-30s; and c. cleaning the silicon slice etched in the step by mixed liquid of HF, HNO3 and CH3COOH. Based on the original reactive ion etching (RIE) technology, one-step low radio-frequency power etching can be added, the plasma bombardment is carried out on the surface of the silicon slice, and the gases including Cl2 and SF6 are only filled in the process, so that Cl2 and SF6 have the function of effectively etching a damaged layer under the condition of low power radio frequency since the gas of O2 does not exist; and therefore, on the premise of guaranteeing the open-circuit voltage, the short-circuit current is improved, and higher component efficiency can be obtained.

Owner:TRINA SOLAR CO LTD

Method and apparatus for increasing local plasma density in magnetically confined plasma

ActiveUS8449731B1Easily damagedLow reliabilityElectric discharge tubesDecorative surface effectsHigh densityPlasma density

Local plasma density, e.g., the plasma density in the vicinity of the substrate, is increased by providing an ion extractor configured to transfer ions and electrons from a first region of magnetically confined plasma (typically a region of higher density plasma) to a second region of plasma (typically a region of lower density plasma). The second region of plasma is preferably also magnetically shaped or confined and resides between the first region of plasma and the substrate. A positively biased conductive member positioned proximate the second region of plasma serves as an ion extractor. A positive bias of about 50-300 V is applied to the ion extractor causing electrons and subsequently ions to be transferred from the first region of plasma to the vicinity of the substrate, thereby forming higher density plasma. Provided methods and apparatus are used for deposition and resputtering.

Owner:NOVELLUS SYSTEMS

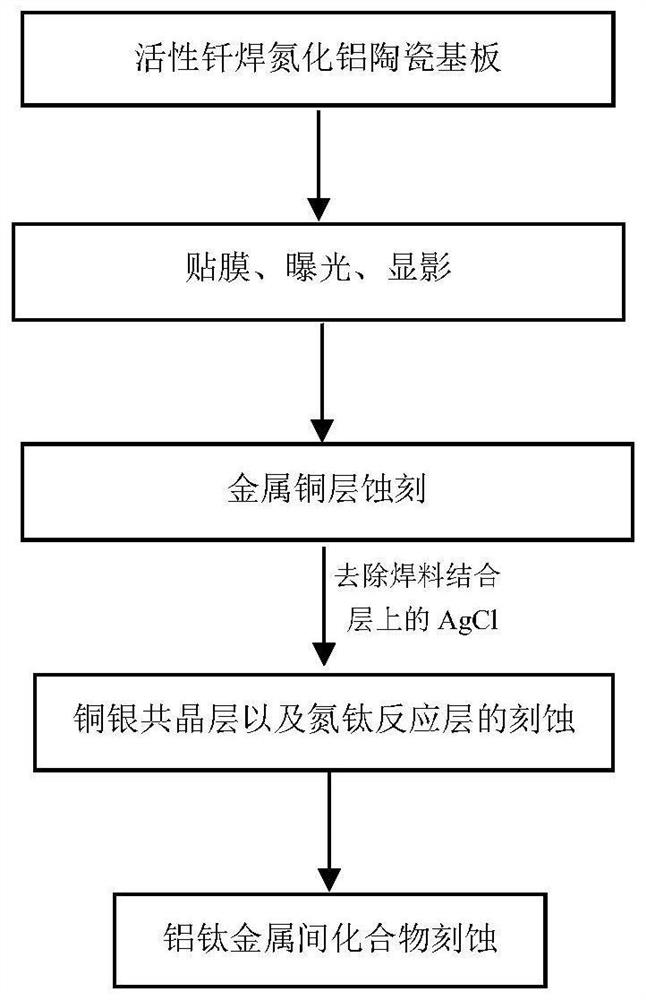

Etching liquid system and etching method of aluminum nitride substrate

ActiveCN111621787AImprove thermal conductivityImprove etching efficiencySemiconductor/solid-state device manufacturingSurface treatment compositionsReaction layerEtching

The invention discloses an etching liquid system and an etching method of an aluminum nitride substrate. The etching liquid system comprises first etching liquid and second etching liquid, wherein thefirst etching liquid comprises the following components according to mass percent: 1% to 5% of ammonium hydroxide, 3% to 8% of strong oxidant, 0.5% to 5% of complexing agents and the balance of water, and the second etching liquid comprises the following components according to mass percent: 1% to 5% of alkali, 2% to 8% of hydrogen peroxide and the balance of water. According to the etching method of the aluminum nitride substrate, a solder bonding layer is etched in two steps of etching a copper-silver eutectic layer and a nitrogen-titanium reaction layer by using the first etching liquid and etching aluminum-titanium intermetallic compounds by using the second etching liquid. The etching liquid system has the advantages of high selectivity and high etching power; the etching method hasthe advantages of high etching efficiency and good etching quality; and the efficient high-precision etching of the aluminum nitride ceramic substrate with high thermal conductivity is realized.

Owner:江苏富乐华半导体科技股份有限公司

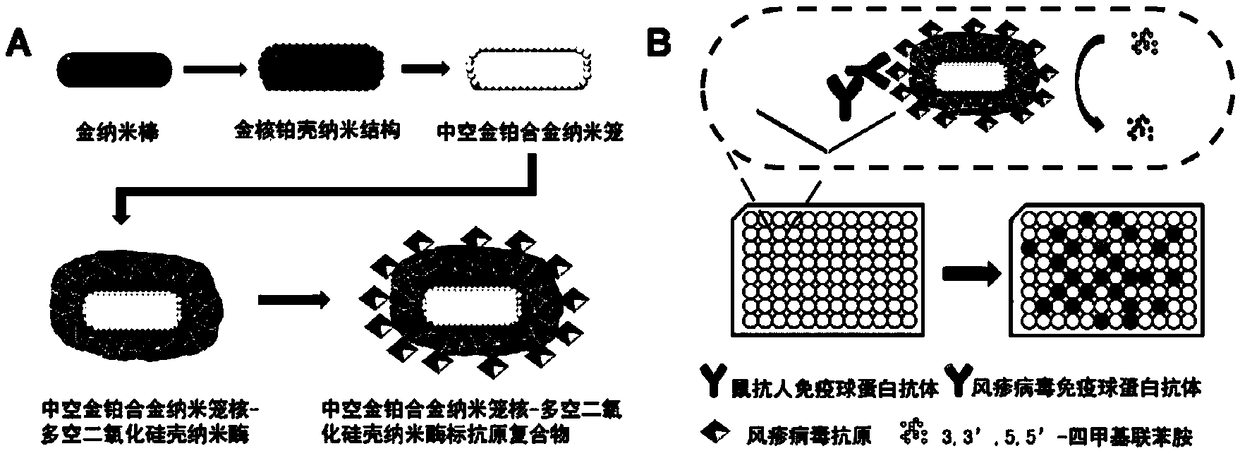

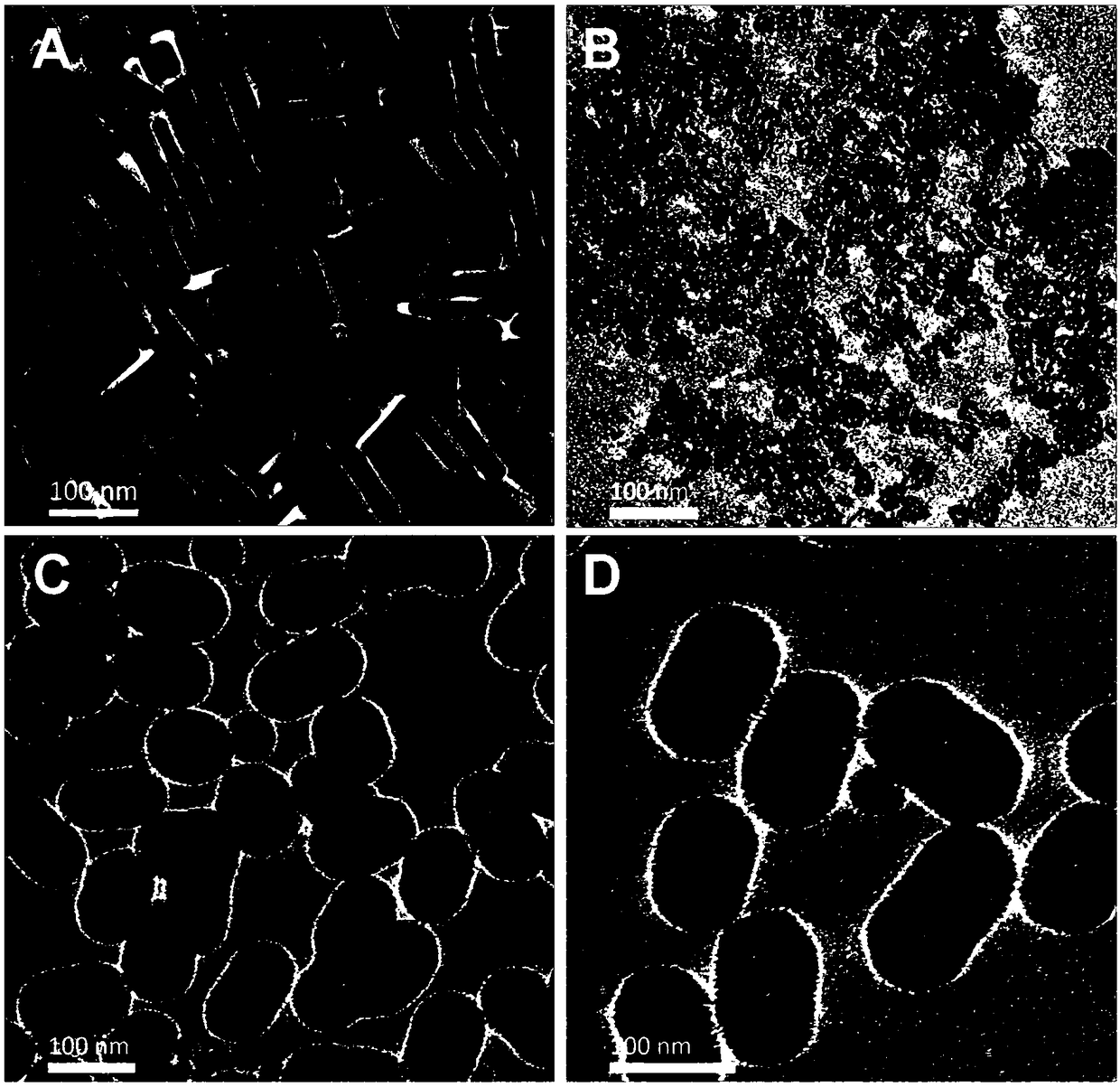

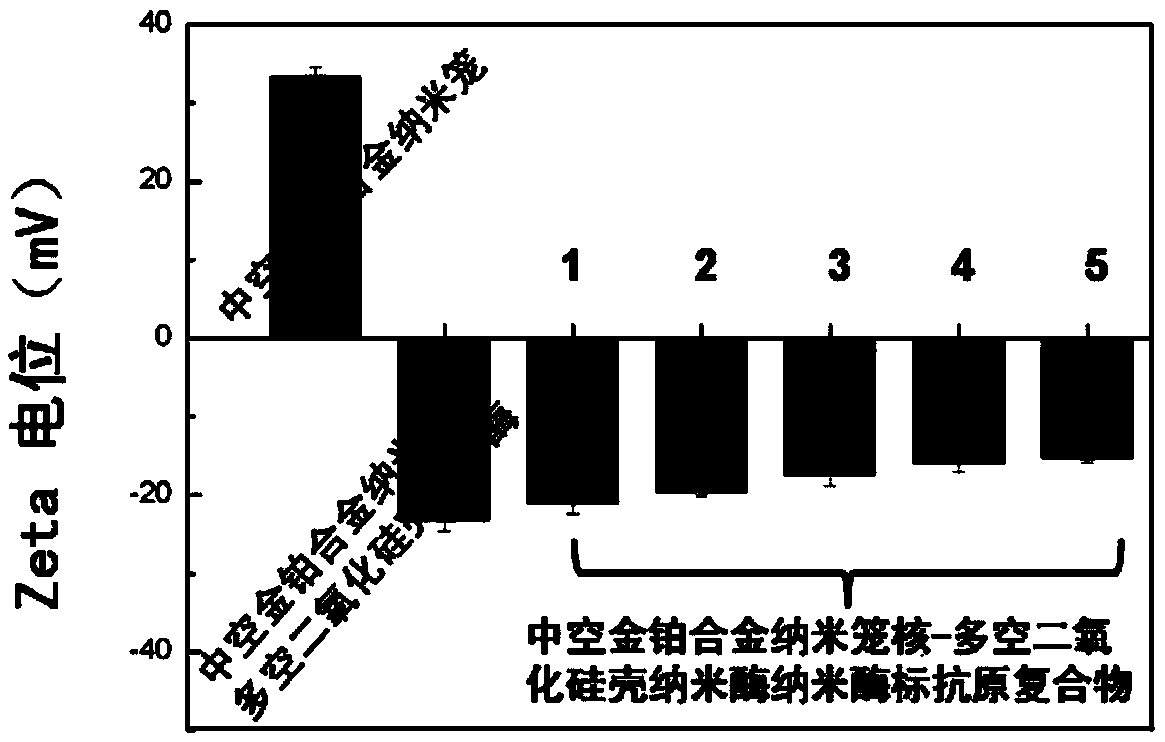

Nano enzyme with nanometer cage core of hollow gold-platinum alloy and shell of porous silicon dioxide, preparation method and application thereof

The invention provides a nano enzyme with a nanometer cage core of a hollow gold-platinum alloy and a shell of a porous silicon dioxide, a preparation method and an application thereof, and belongs tothe field of nanometer materials. The preparation method comprises the following steps: etching a gold core platinum shell nanostructure through potassium hexachloroplatinate to obtain a nanocage ofhollow gold-platinum alloy; coating silicon dioxide on the surface of the nanocage through tetraethyl silicate; and obtaining the nano enzyme taking the nanometer cage, in a round rod shape, of the hollow gold-platinum alloy as a core, and a silicon dioxide shell as the periphery of the core. The length of the core is 80 to 100 nm, and the diameter is 20 to 25 nm. The shell is provided with a channel of 3 to 5 nm. The nano enzyme is negatively charged. The antigen can be bound by an attractive effect of positive and negative electric charges to form a nano enzyme label antigen complex, which is used for performing enzyme linked immunoassay. According to the nano enzyme with the nanometer cage core of the hollow gold-platinum alloy and the shell of the porous silicon dioxide, the preparation method and the application thereof, the cost of a reagent of the natural enzyme label antigen complex is reduced, the working environment of enzyme linked immunodetection is extended, the defects that the natural enzyme is easy to deactivate and denature, etc., are overcame, and the nano enzyme can be widely applied to various enzyme linked immunodetection.

Owner:ZAOZHUANG UNIV

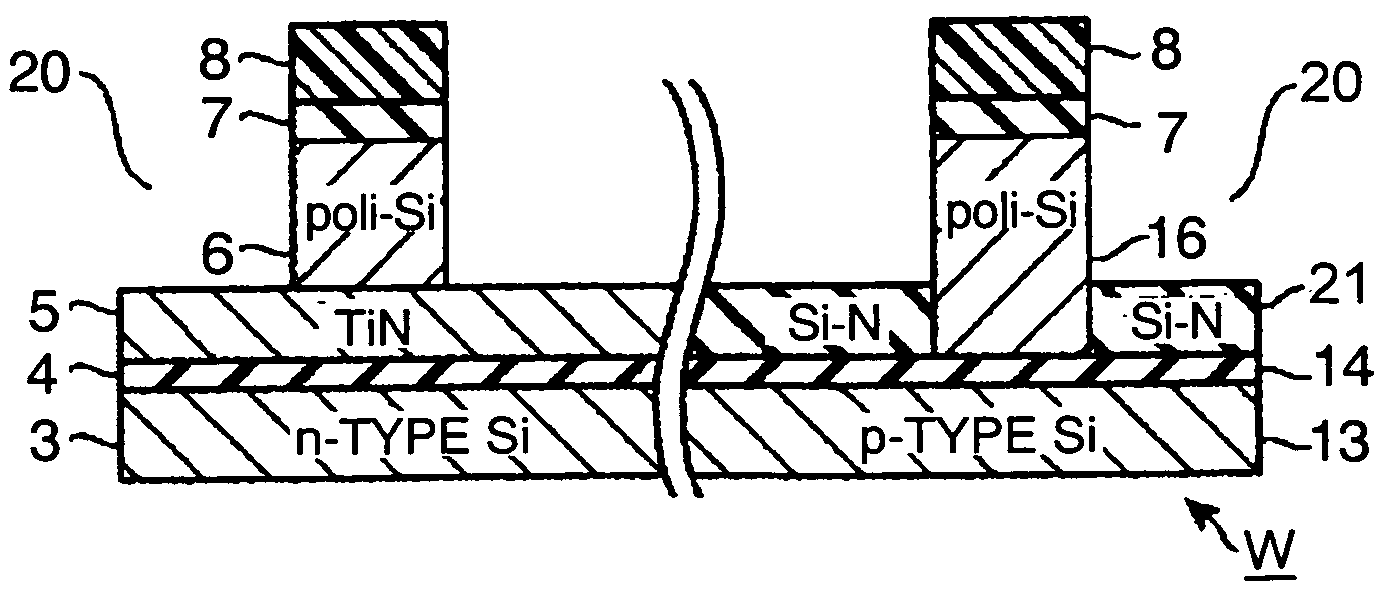

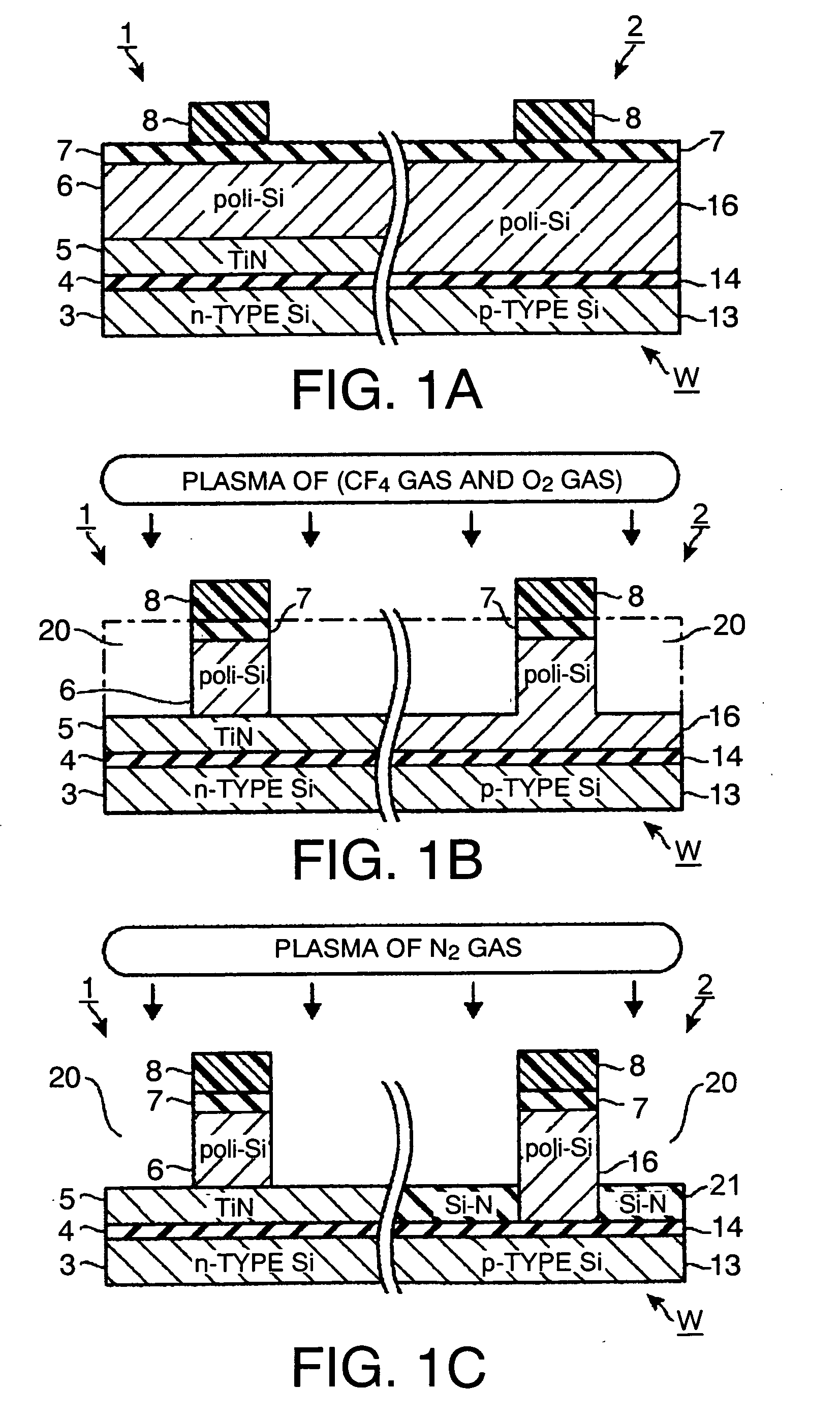

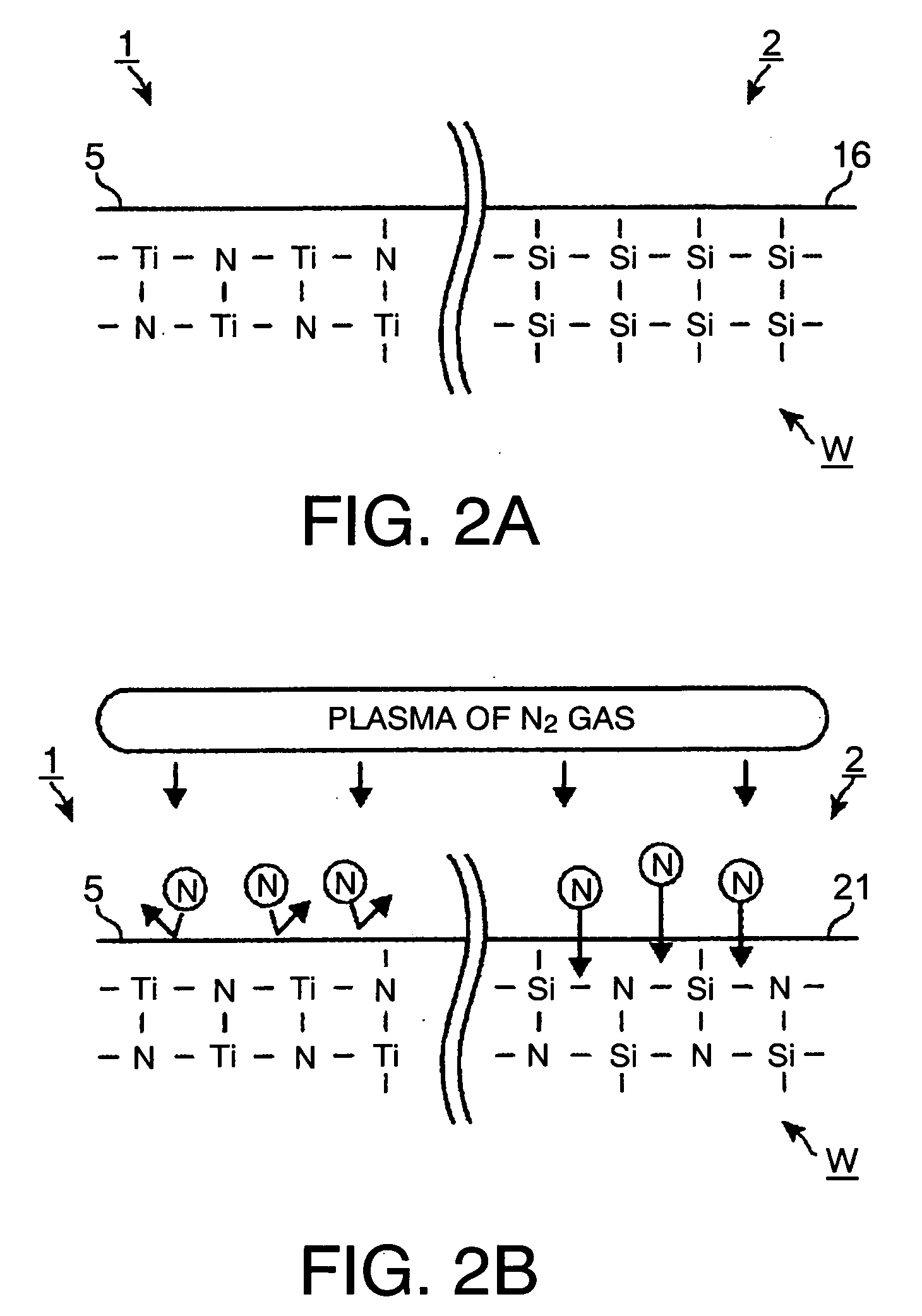

Plasma etching method

ActiveUS20090233446A1Big ratioHigh hardnessSemiconductor/solid-state device manufacturingSemiconductor devicesNitrideSilicon

The present invention is a plasma etching method for etching a surface of a substrate in which a metal nitride film and a silicon film have been respectively formed on a first base film and a second base film that had been side-by-side arranged, with surfaces of the metal nitride film and the silicon film being exposed. At least a surface area of the silicon film is nitrided. A first etching plasma is supplied onto the surface of the substrate so as to etch the metal nitride film and to expose the first base film. A second etching plasma is supplied onto the surface of the substrate so as to etch the silicon film and to expose the second base film.

Owner:TOKYO ELECTRON LTD

Method of etching copper on cards

InactiveUS20050082257A1Reduce defective rateEfficient etchingElectrolysis componentsDecorative surface effectsOxidation-Reduction AgentRedox

Etching of copper on a card is achieved by applying an electrical voltage between a cathode (102) and the card (42), the card (42) thereby forming an anode. The cathode (102) and the card (42) are immersed in an electrolyte comprising a first component, which may be reduced from a first state in the form of an ion having a metal atom with a first positive oxidation number to a second state in the form of an ion having said metal atom with a second positive oxidation number, which is less than said first positive oxidation number. A first redox potential in the electrolyte for reduction from the first to the second state is larger than a second redox potential in the electrolyte for reduction of divalent copper ions to metallic copper. During the etching metallic copper on the card is oxidised and transferred into positively charged copper ions while the first component is reduced from its first state to its second state. The quality of the etched structures on the card is improved since no metallic copper is precipitated on the cathode.

Owner:OBDUCAT AB SE

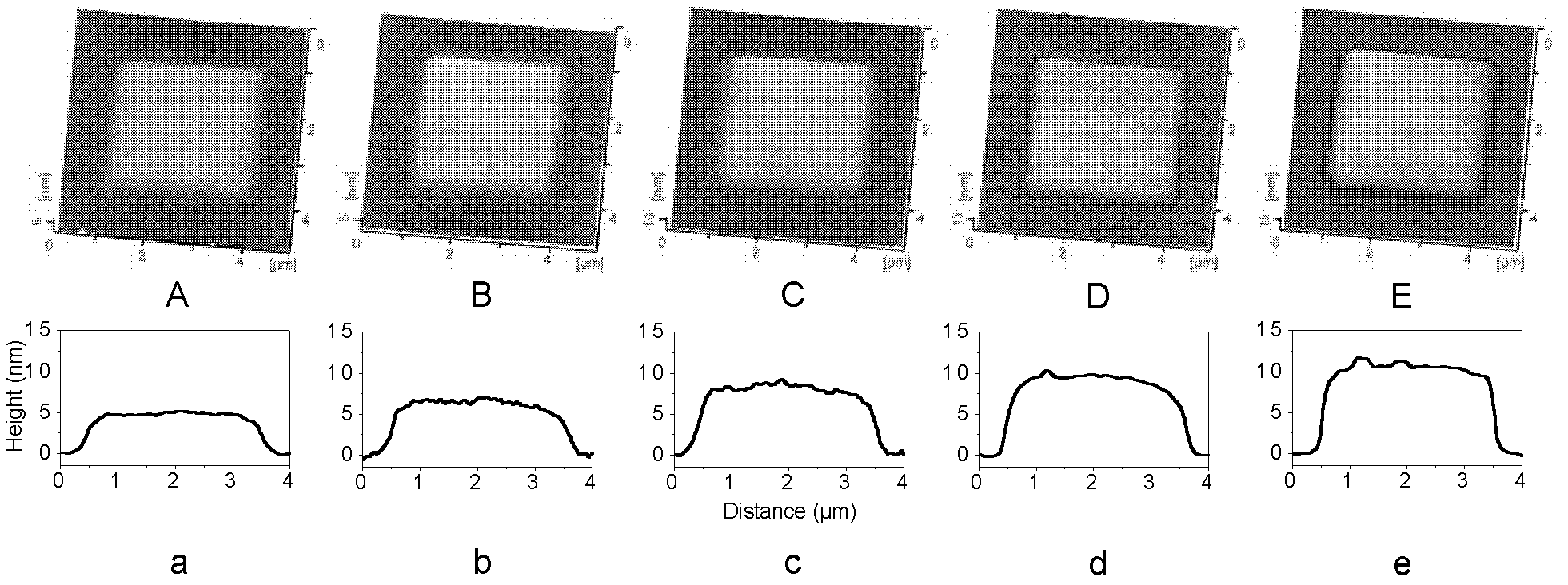

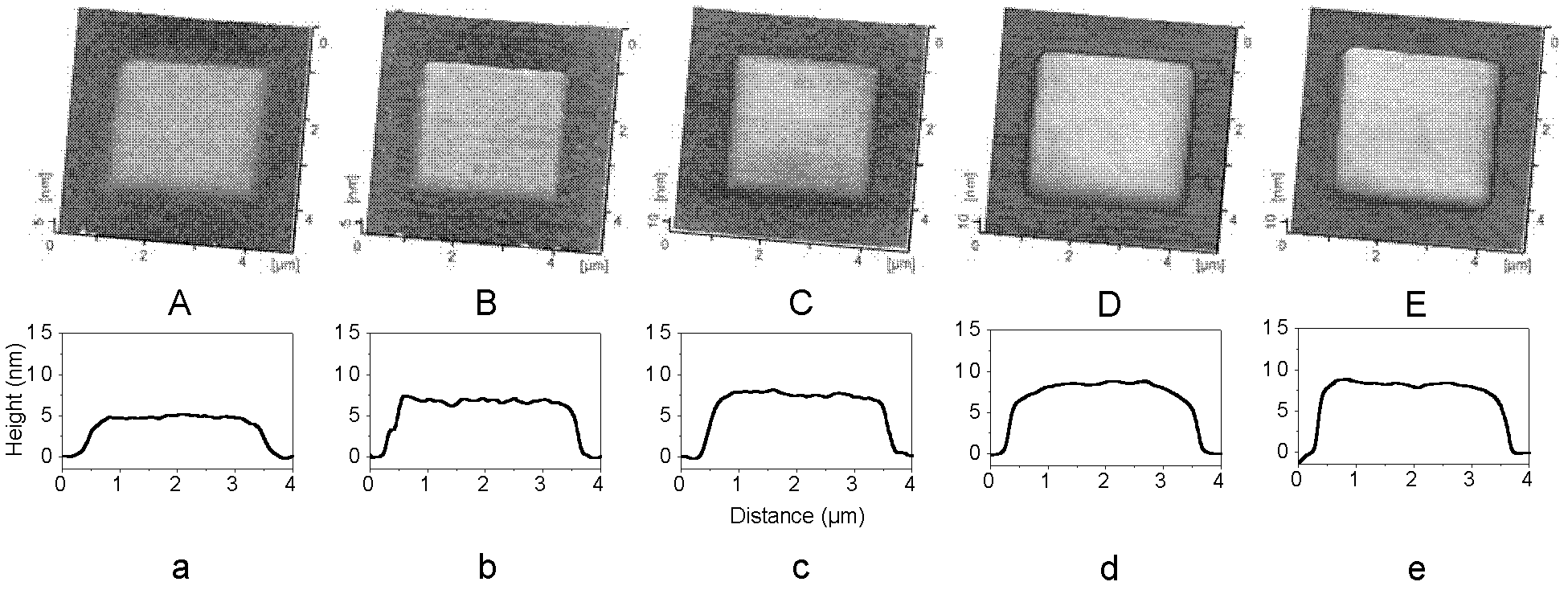

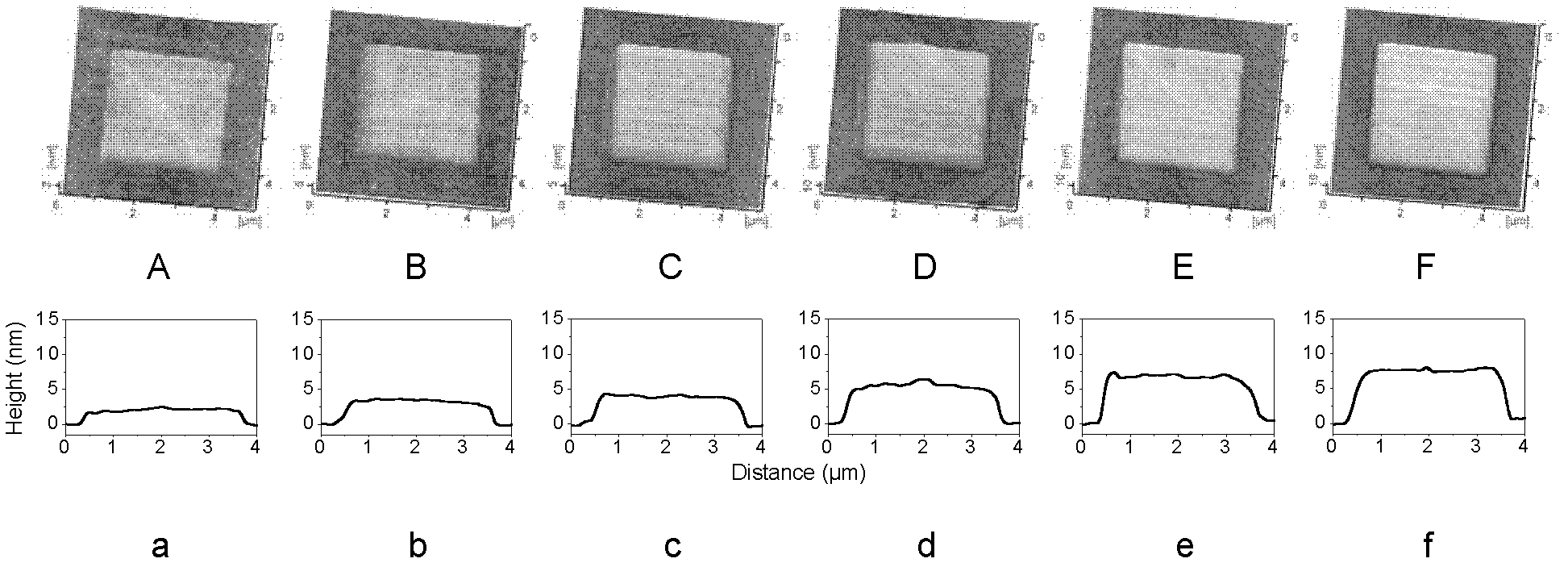

Glass surface nanofabrication method based on friction-induced selective etching

ActiveCN102503155AReduce processReduce the difficulty of operationDecorative surface effectsNanotechnologyConstant loadEtching

The invention discloses a glass surface nanofabrication method based on friction-induced selective etching, which is mainly applied in the processing of the glass surface micro-nanostructure. The specific operation method comprises the following steps of: installing a probe of which the tip is spherical on an atomic force microscope, fixing the cleaned glass on a sample stage, starting the atomic force microscope, applying a constant load F or a variable load F' on the probe, using the probe to scan on the glass surface along a set scanning track according to the cycle number N and the scanning speed v; and after scanning, placing the glass in an HF solution of which mass concentration is 10-20%, and finally corroding for 5-10 seconds. The method does not require a template or mask, three-dimensional nano-patterns such as slopes, steps and arrays are processed on the glass surface through one-time corrosion; and the processing flow is extremely simple, the corrosion rate is extremely high, and the glass surface nanofabrication method is simple, accurate and efficient.

Owner:SOUTHWEST JIAOTONG UNIV

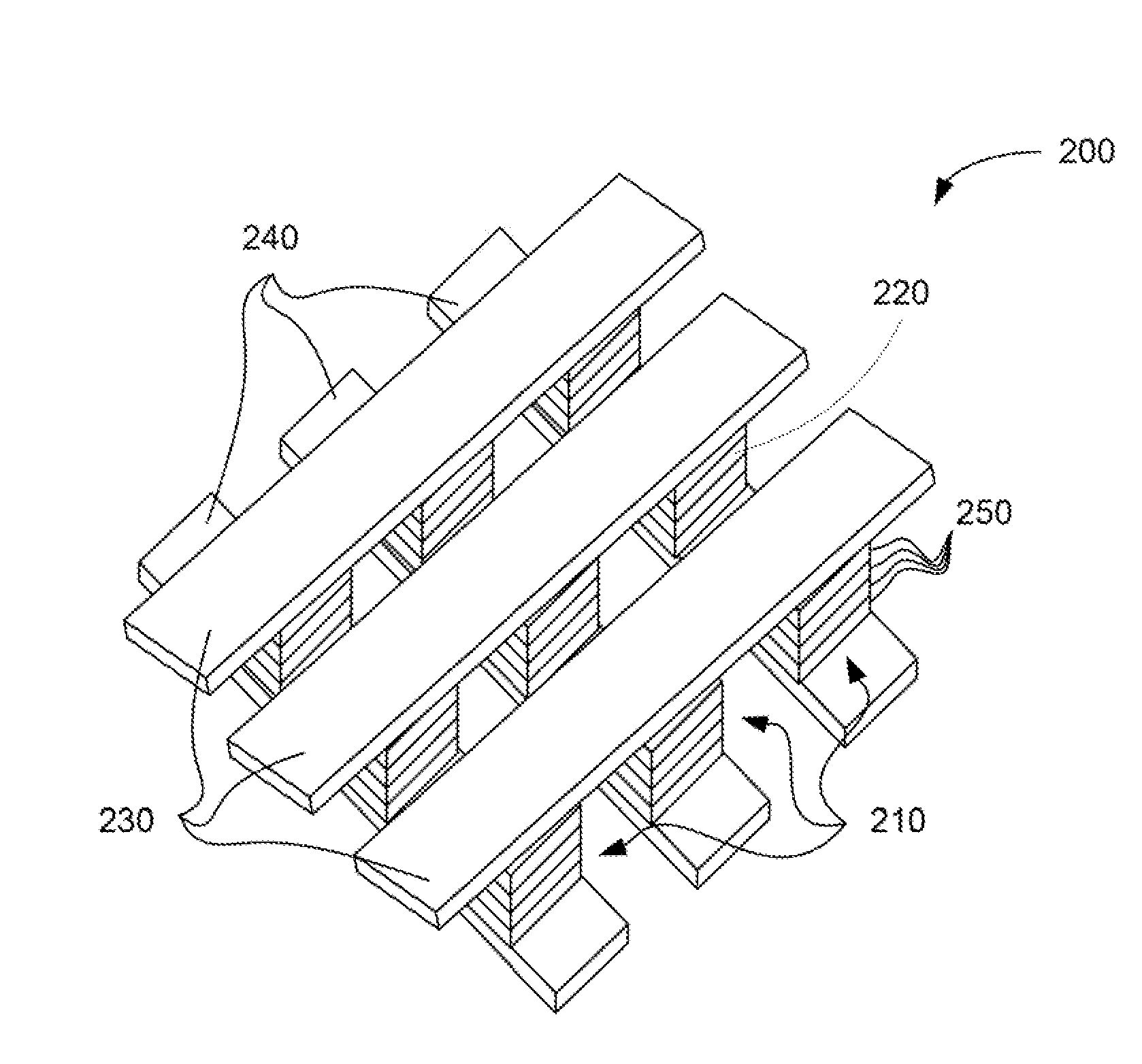

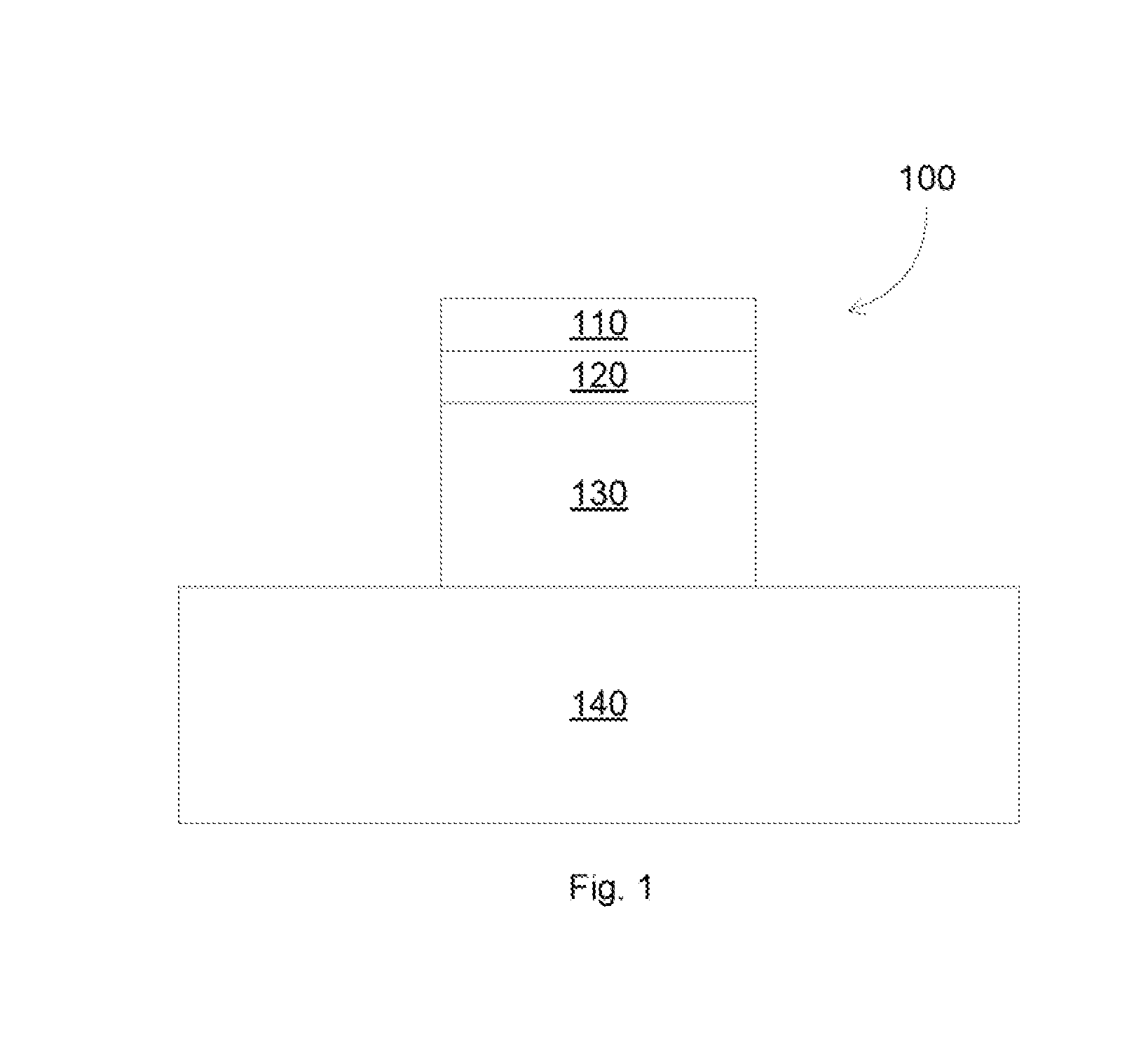

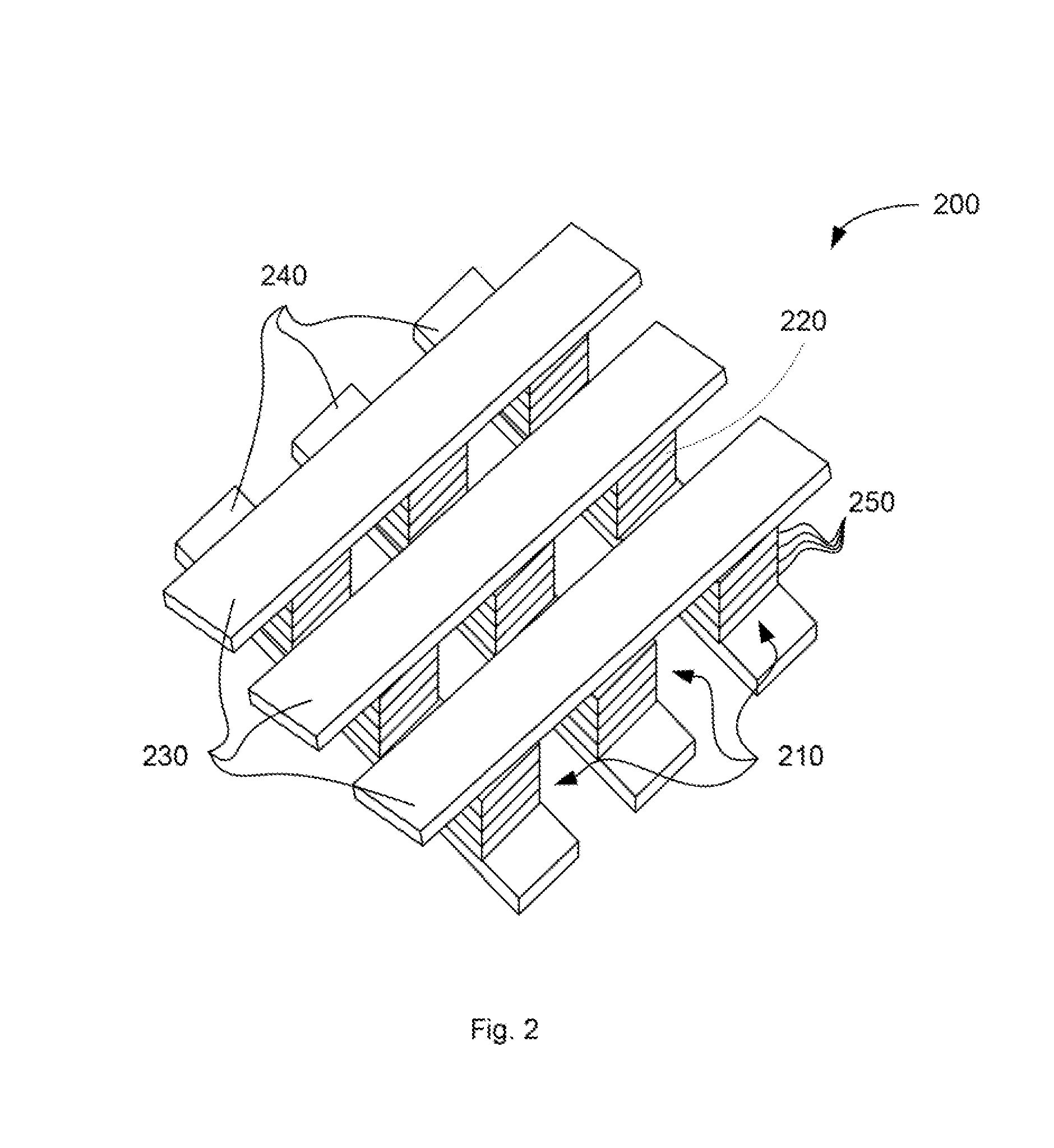

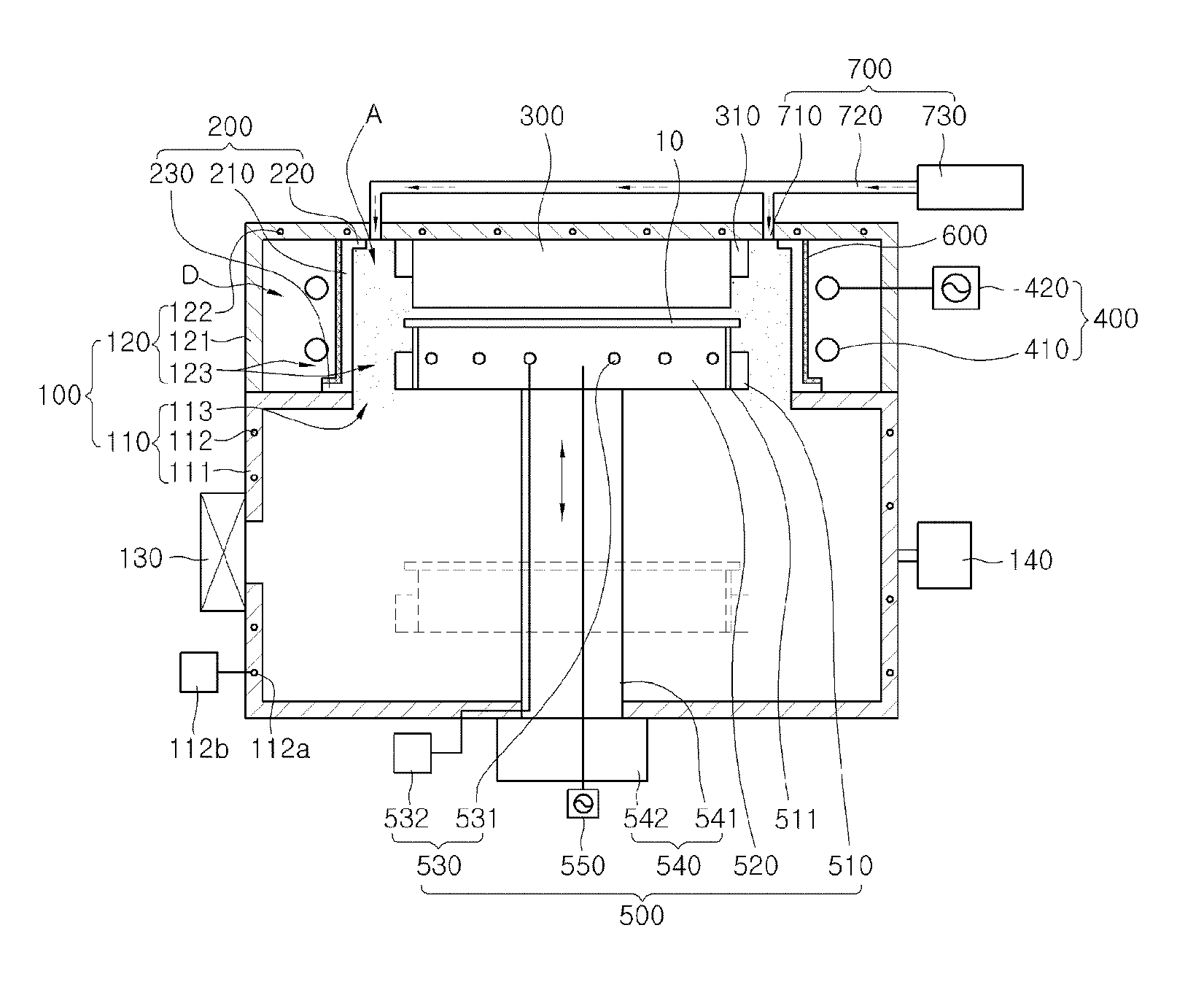

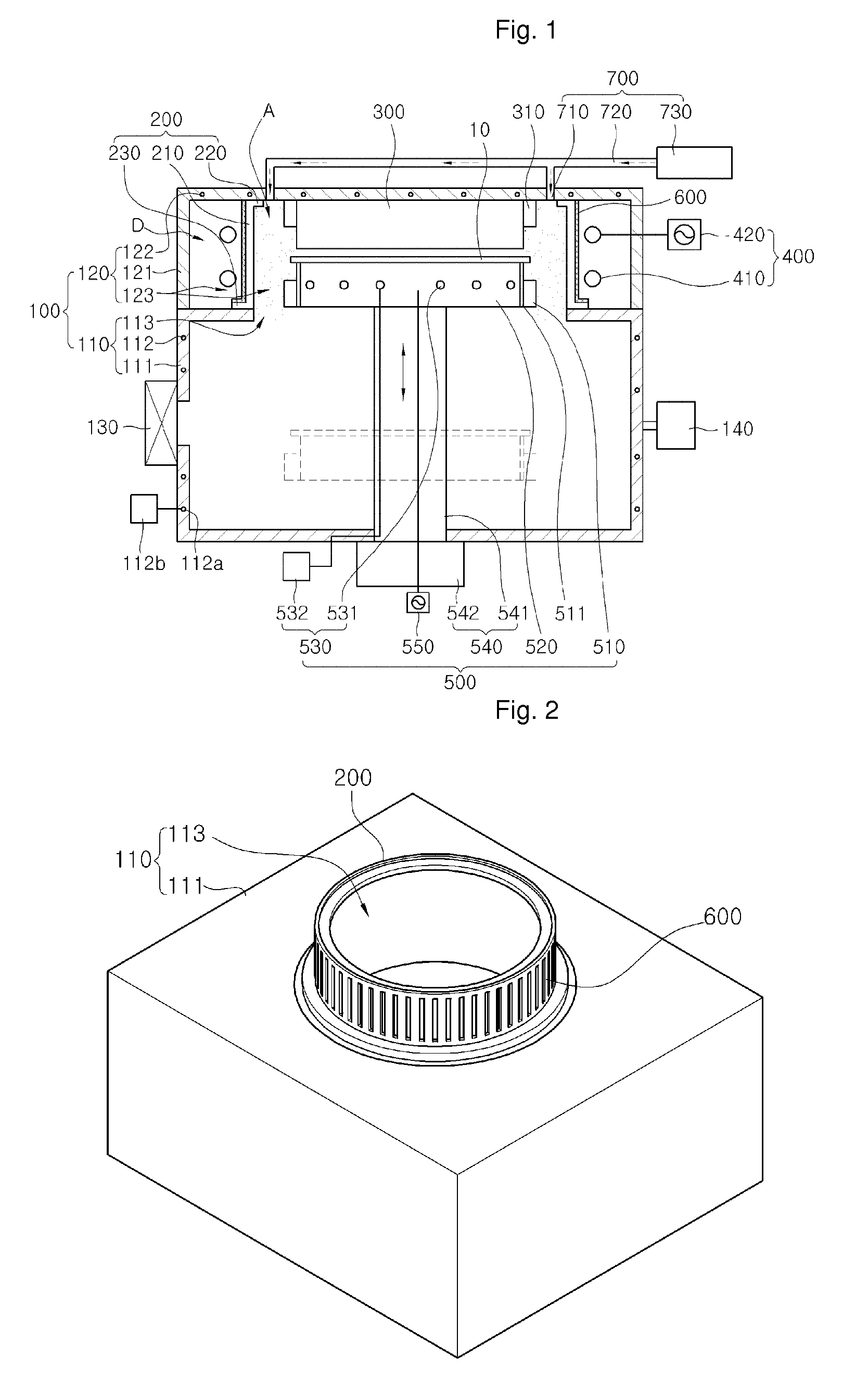

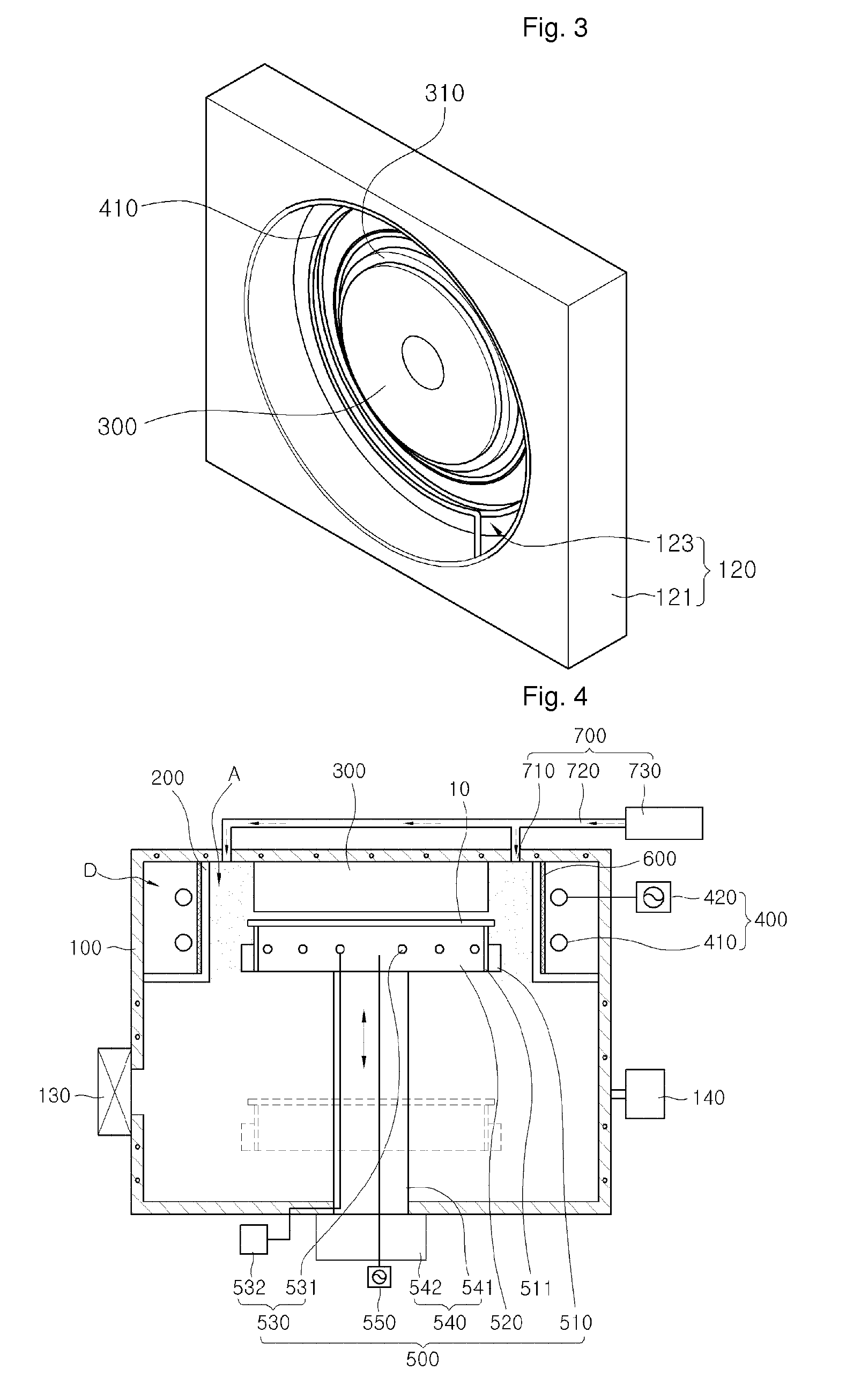

Apparatus for supporting substrate and plasma etching apparatus having the same

InactiveUS8980049B2Etched more efficientlyEfficient etchingSemiconductor/solid-state device manufacturingChemical vapor deposition coatingEngineeringRadio frequency

Provided are a substrate supporting apparatus and a plasma etching apparatus having the same. There is provided a substrate supporting apparatus that can separately provide powers to a central region and an edge region by disposing an electrode supporting a substrate at the central region of the substrate supporting apparatus, and disposing an electrode receiving radio frequency (RF) power at the edge region of the substrate supporting apparatus. There is provided a substrate edge etching apparatus having the substrate supporting apparatus for removing layers or particles deposited in an edge region of a semiconductor substrate and preventing damage of a center region of the semiconductor substrate during an etching process of the substrate edge.

Owner:SOSUL

Method for fabricating self-aligned contact hole

InactiveUS7557038B2Improve etch selectivityEfficient etchingSemiconductor/solid-state device detailsSolid-state devicesDevice materialGate oxide

Disclosed are: (i) a method for fabricating self-aligned contact hole in a semiconductor device, and (ii) a semiconductor device having a self-aligned contact. The method comprises the steps of: (a) forming an oxide layer covering a gate structure on a semiconductor substrate, the gate structure including a gate oxide pattern, a gate electrode pattern, a hard-mask nitride pattern, and a spacer nitride on sidewalls thereof; (b) forming a mask pattern on the oxide layer; (c) forming a contact trench by removing a portion of the oxide layer, exposed by the mask pattern, to a predetermined depth; (d) forming a buffer layer on the oxide layer, including in the contact trench; (e) etching a portion of the buffer layer at a bottom of the contact trench to expose a portion of the oxide layer; and (f) forming a contact hole by etching the exposed oxide layer using a remaining buffer layer as an etching mask.

Owner:DONGBU ELECTRONICS CO LTD

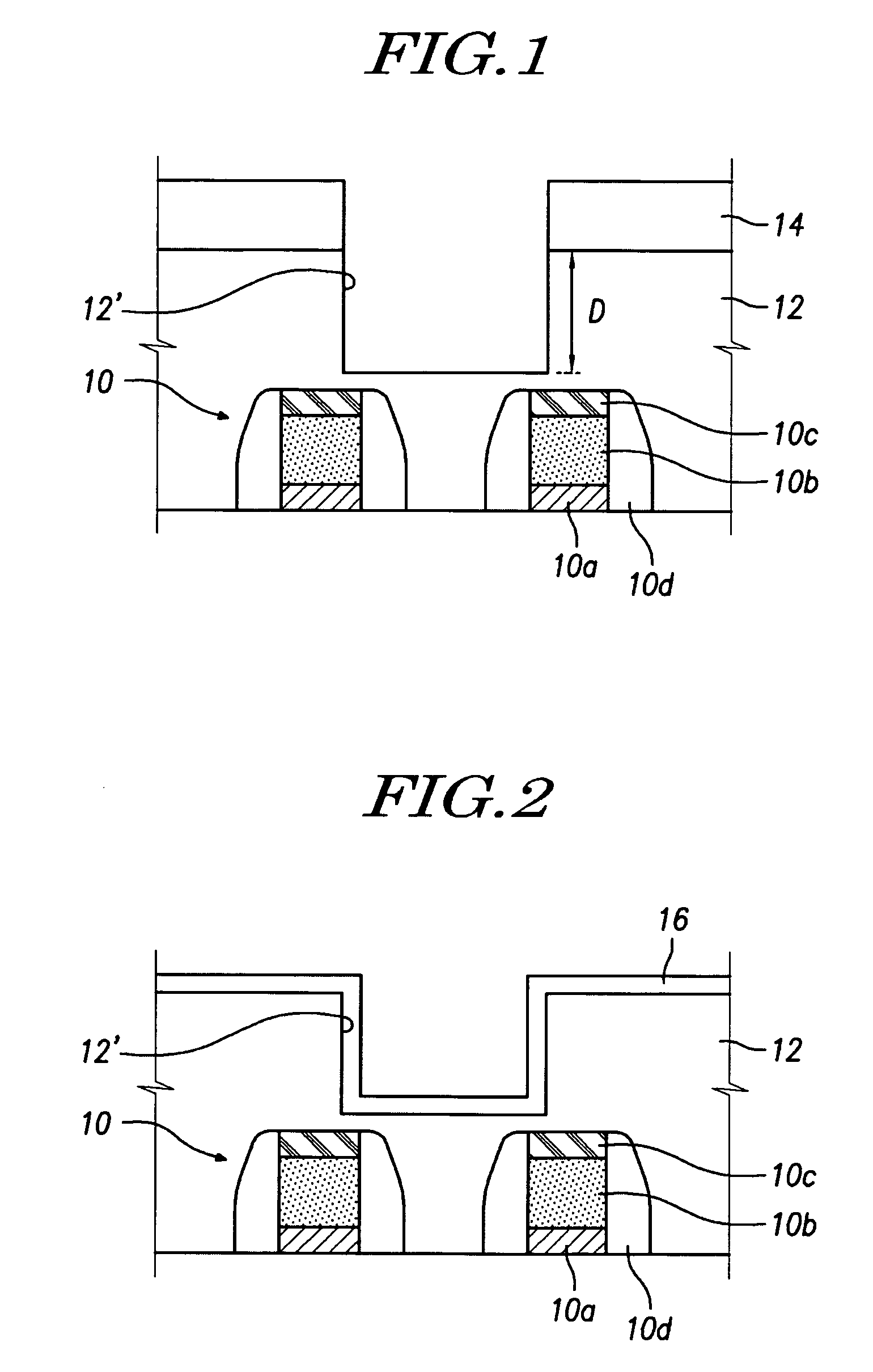

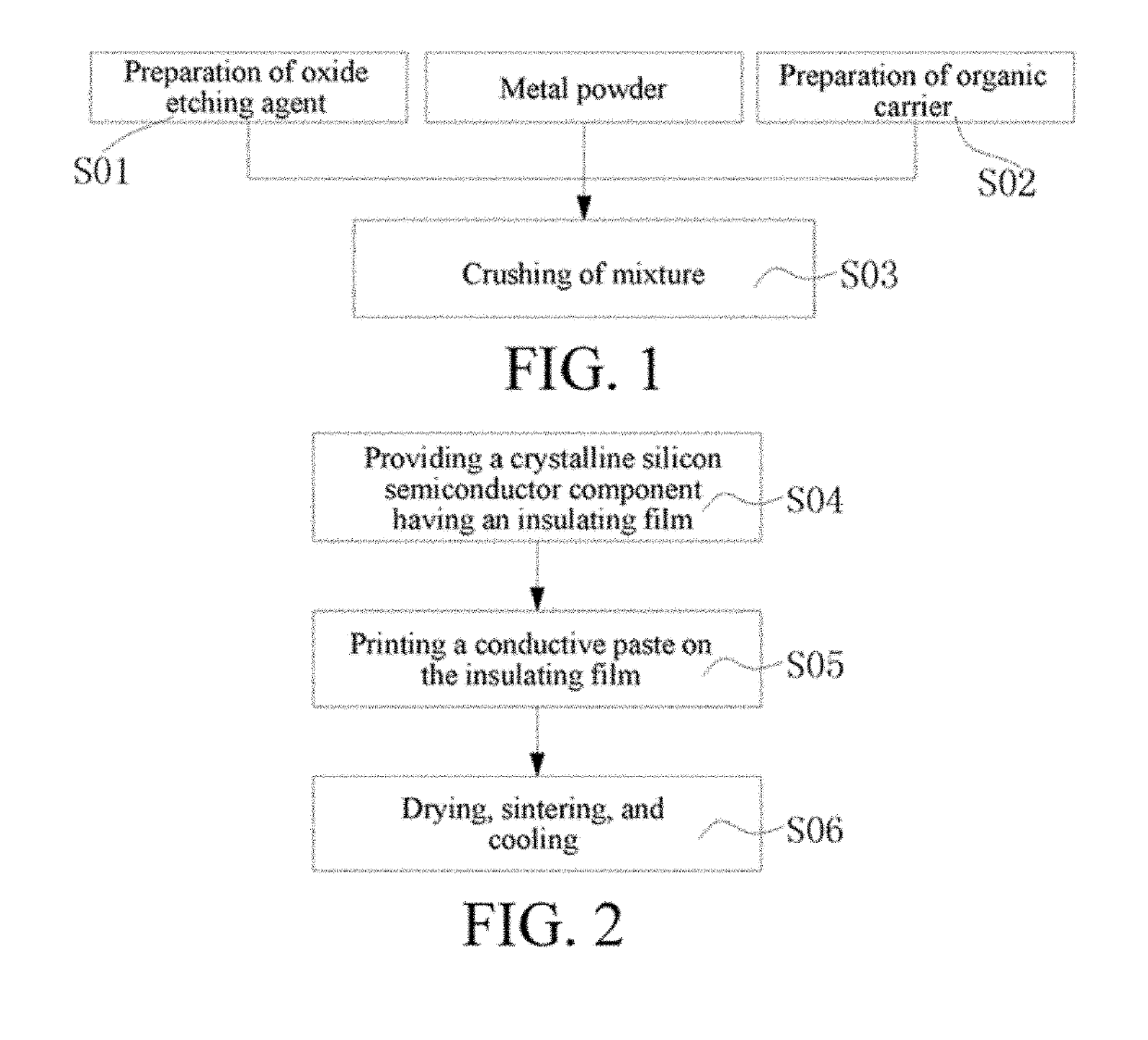

Front-side conductive paste for crystalline silicon solar cell, preparation method therefor, and solar cell

ActiveUS20190305150A1Excellent dissolving and etching propertyPromote sinteringTransportation and packagingMetal-working apparatusConductive pasteMetal powder

A front-side conductive paste for a crystalline silicon solar cell is provided. The front-side conductive paste for a crystalline silicon solar cell includes, in parts by weight, 80.0-93.0 parts of a metal powder, 6.0-15.0 parts of an organic carrier, and 1.0-5.0 parts of an oxide etching agent, where based on 100% by mole of the oxide etching agent, the oxide etching agent includes 15-30% of PbO; 25-40% of TeO2; 8.0-15.0% of Li2O; 9.0-20.0% of SiO2; 5.0-15.0% of Bi2O3; 0.5-10.0% of ZnO; and either one or both of 0.1-10.0% of MgO and 0.1-10.0% of CaO; and no more than 5.0% of an oxide of additional metal elements. The metal powder forms good ohmic contact with crystalline silicon substrate during the sintering process of the front-side conductive paste applied overlying an insulation film on the substrate. Finally, a front-side electrode of low contact resistance, good electrical conductivity, and strong adhesion is obtained.

Owner:SOLTRIUM ADVANCED MATERIALS TECH LTD SUZHOU

Molybdenum aluminum molybdenum etching solution

The invention relates to a molybdenum aluminum molybdenum etching solution. Based on a total weight, the molybdenum aluminum molybdenum etching solution comprises: 35-45% of phosphoric acid, 1-3% of nitric acid, 8-12% of glacial acetic acid, 0.5-1.0% of additives and 39-55.5% of deionized water. The additives comprise organic polybasic phosphonic acid substance, amine substance and salt substance.The molybdenum aluminum molybdenum etching solution provided by the invention can meet the customers' requirements for etching angle and etching amount, improves the product's excellent and good rate, at the same time greatly lowers the phosphoric acid content, and reduces the problem of uneven local etching caused by excessive phosphoric acid concentration.

Owner:SHENZHEN CAPCHEM TECH CO LTD