Multi-rate compatible ldpc code encoder

An LDPC code and encoder technology, applied in coding, coding elements, error detection coding using multi-bit parity bits, etc., can solve the problems of large logic resource consumption and low RAM resource utilization, and reduce resource consumption. , The effect of saving FPGA logic resources and reducing the number of

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

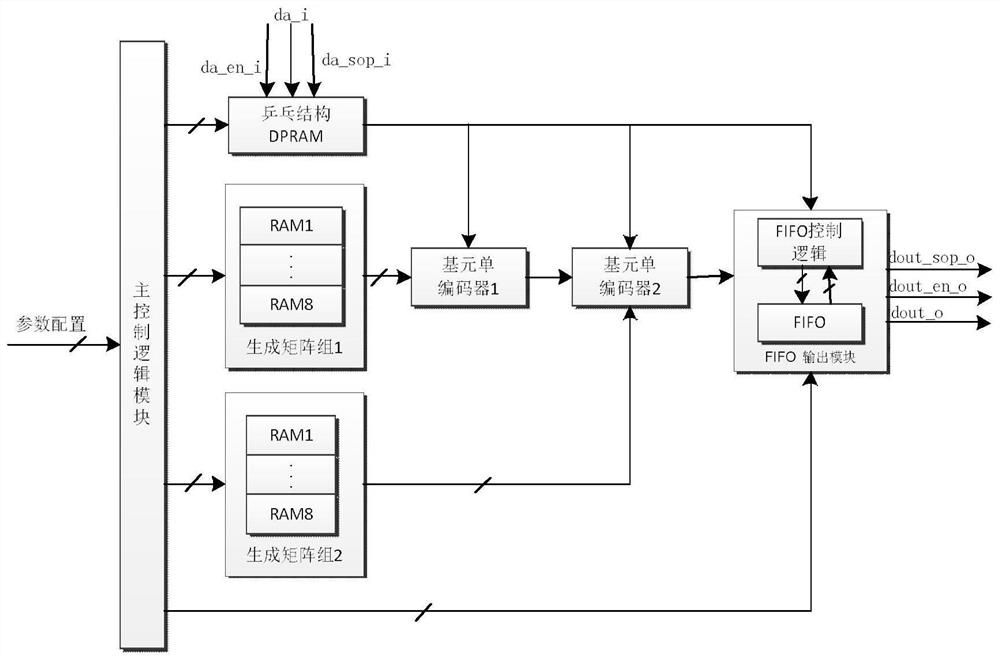

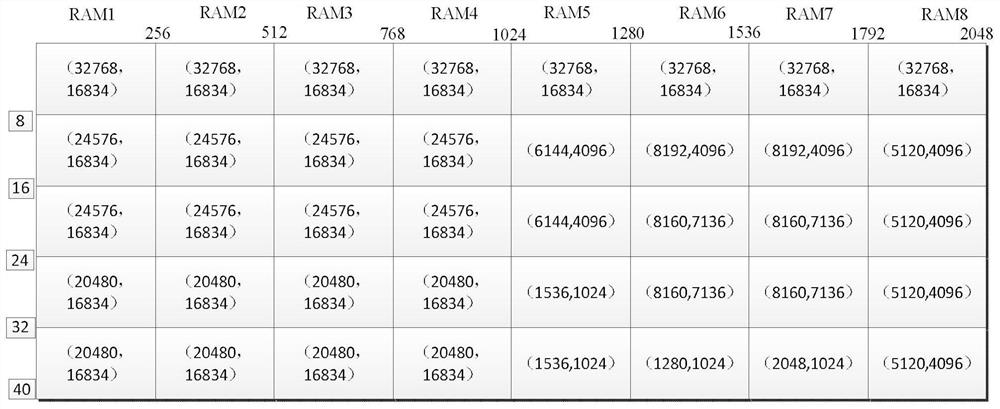

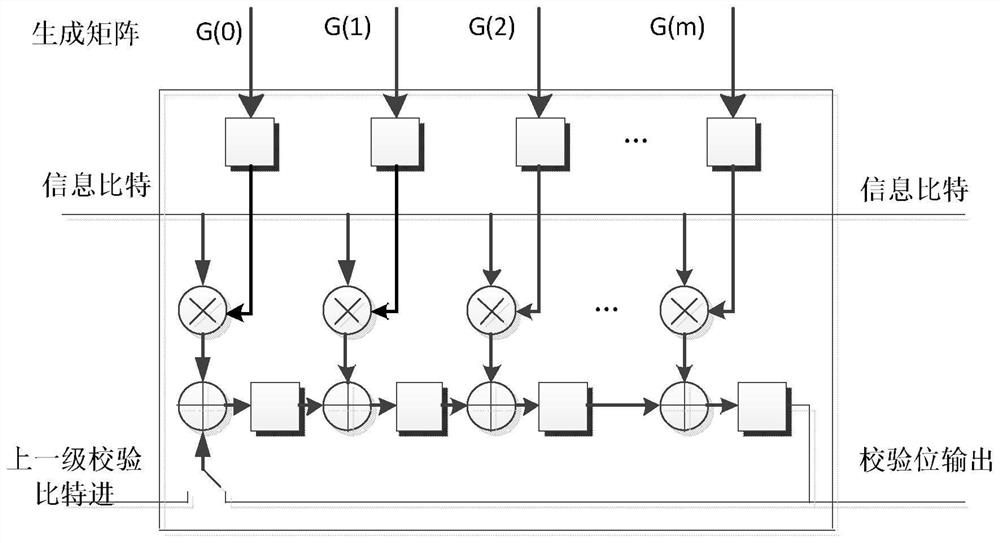

[0019] refer to figure 1 . In the embodiment described below, the multi-code-rate compatible LDPC encoder mainly includes: a main control logic module, a ping-pong DPRAM module, two groups of generating matrix group modules, a primitive single encoder module, a logic module controlled by a FIFO and a first-in-first-out FIFO output module composed of dequeue data buffer FIFO. The main control logic module receives the configuration parameters passed by the superior module, and provides timing control logic for the ping-pong DPRAM module, the generation matrix group module, the basic unit single encoder module, and the FIFO output module according to the configuration parameters; the generation matrix group module stores the standard data of the LDPC encoder The elements in the first row of the circulant matrix, the generator matrix is composed of multiple quasi-circulant matrices, and it is used as the input signal of the basic unit single encoder module under the control of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More