Access method, device and medium on FPGA accelerator card, and medium

An access method and accelerator card technology, applied in the field of cloud computing, to achieve the effect of ensuring accuracy and high availability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

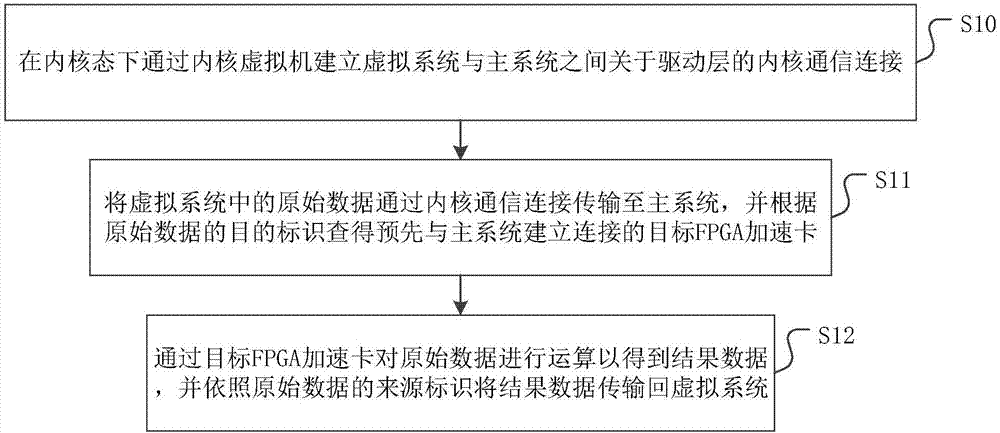

[0044] figure 1 It is a flowchart of a method for accessing an FPGA accelerator card provided by an embodiment of the present invention. Please refer to figure 1 , the specific steps of the method for accessing the FPGA accelerator card include:

[0045] Step S10: Establish a kernel communication connection between the virtual system and the main system on the driver layer through the kernel virtual machine in the kernel state.

[0046] Wherein, the kernel virtual machine is installed in the main system, and the virtual system is installed in the kernel virtual machine.

[0047] It should be noted that the kernel state is the state in which the CPU has the most authority, and can access all data in the memory, including data in peripheral devices such as hard disks and network cards. data interaction. The kernel virtual machine is usually installed in the main system of the server. The virtual system can be carried by the kernel virtual machine, which is equivalent to cont...

Embodiment 2

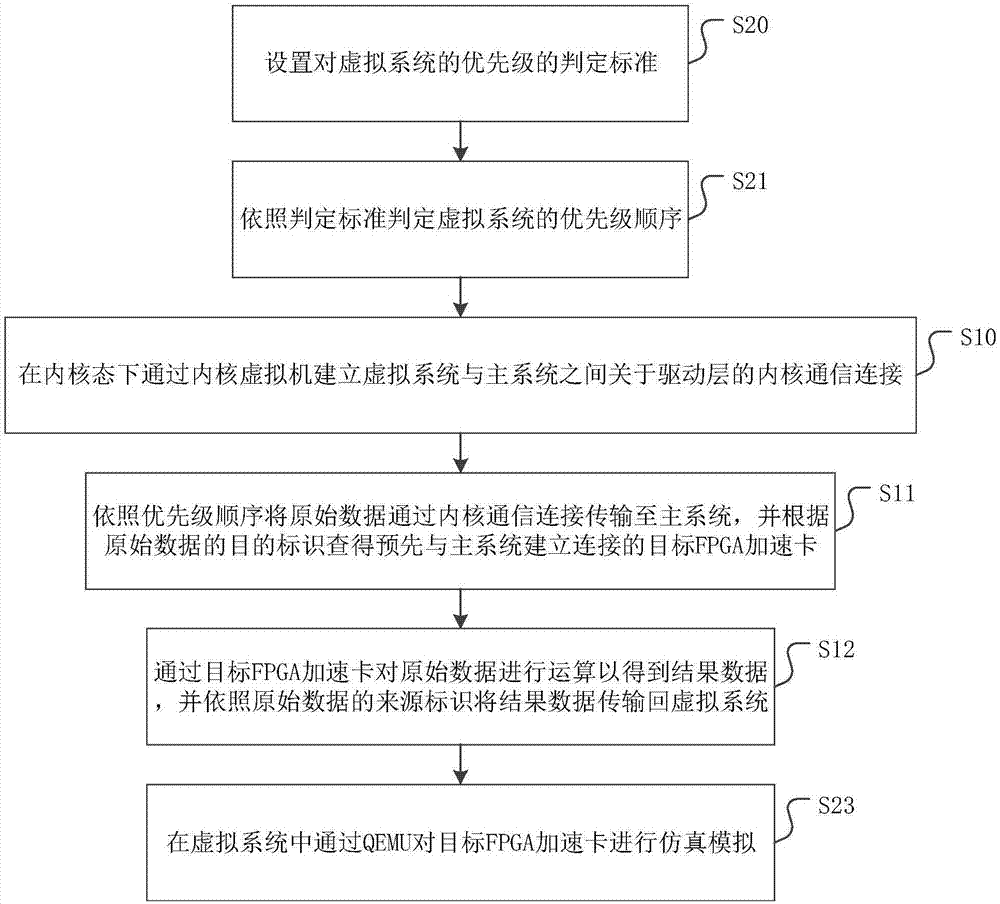

[0054] figure 2 It is a flow chart of another method for accessing the FPGA accelerator card provided by the embodiment of the present invention. figure 2 In steps S10 and S12 and figure 1 Same, no more details here.

[0055] Such as figure 2 As shown, as a preferred implementation manner, before the original data in the virtual system is transmitted to the main system through the kernel communication connection, the method further includes:

[0056] Step S20: setting a criterion for judging the priority of the virtual system.

[0057] Step S21: Determine the priority order of the virtual systems according to the determination criteria.

[0058] Correspondingly, step S11 is specifically:

[0059] Step S22: According to the order of priority, the original data is transmitted to the main system through the kernel communication connection, and the target FPGA accelerator card that has established a connection with the main system in advance is searched according to the pu...

Embodiment 3

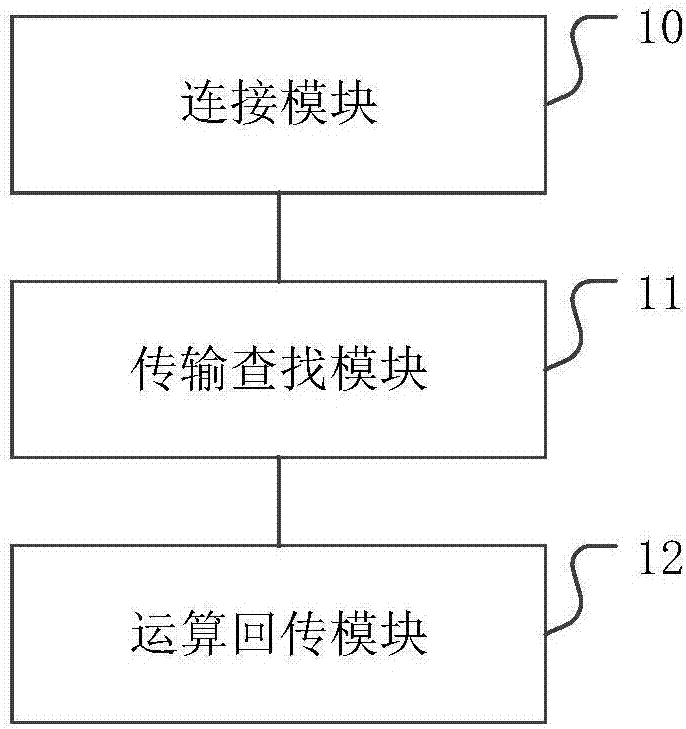

[0075] The embodiment of the method for accessing the FPGA accelerator card has been described in detail above, and the present invention also provides a device for accessing the FPGA accelerator card corresponding to the method, due to the implementation of the embodiment of the device part and the method part The examples correspond to each other, so for the embodiments of the device part, please refer to the description of the embodiments of the method part, and details will not be repeated here.

[0076] image 3 A structural diagram of an access device for an FPGA accelerator card provided by an embodiment of the present invention. The access device to the FPGA accelerator card provided by the embodiment of the present invention specifically includes:

[0077] The connection module 10 is configured to establish a kernel communication connection between the virtual system and the main system on the driver layer through the kernel virtual machine in the kernel mode.

[00...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More