FPGA aging test system and circuit configuration method thereof

A test system and circuit configuration technology, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., can solve the problems of FPGA volatility, loss of chip functions, poor compatibility, etc., to ensure safety, fewer terminals, and reasonable definite effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

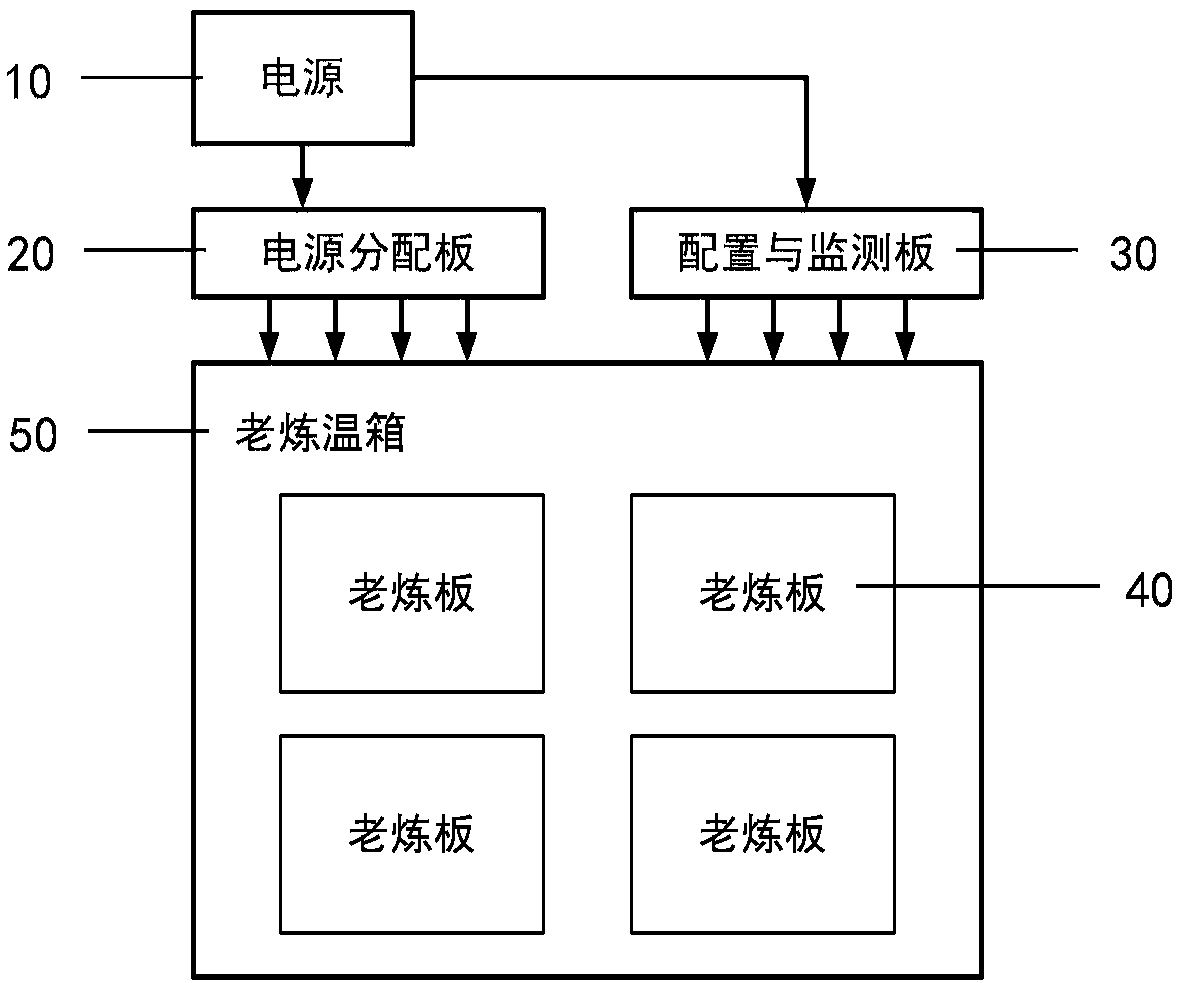

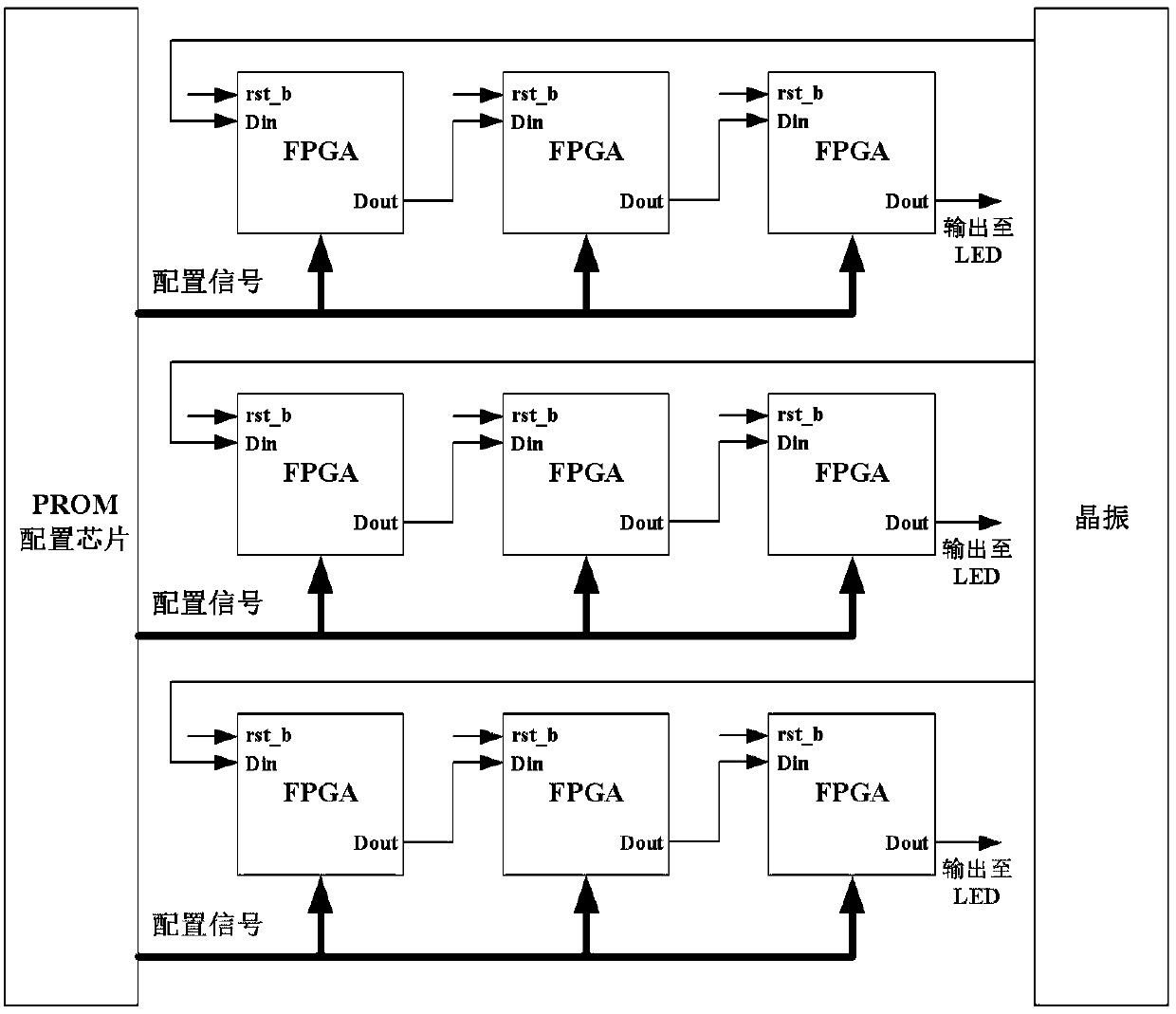

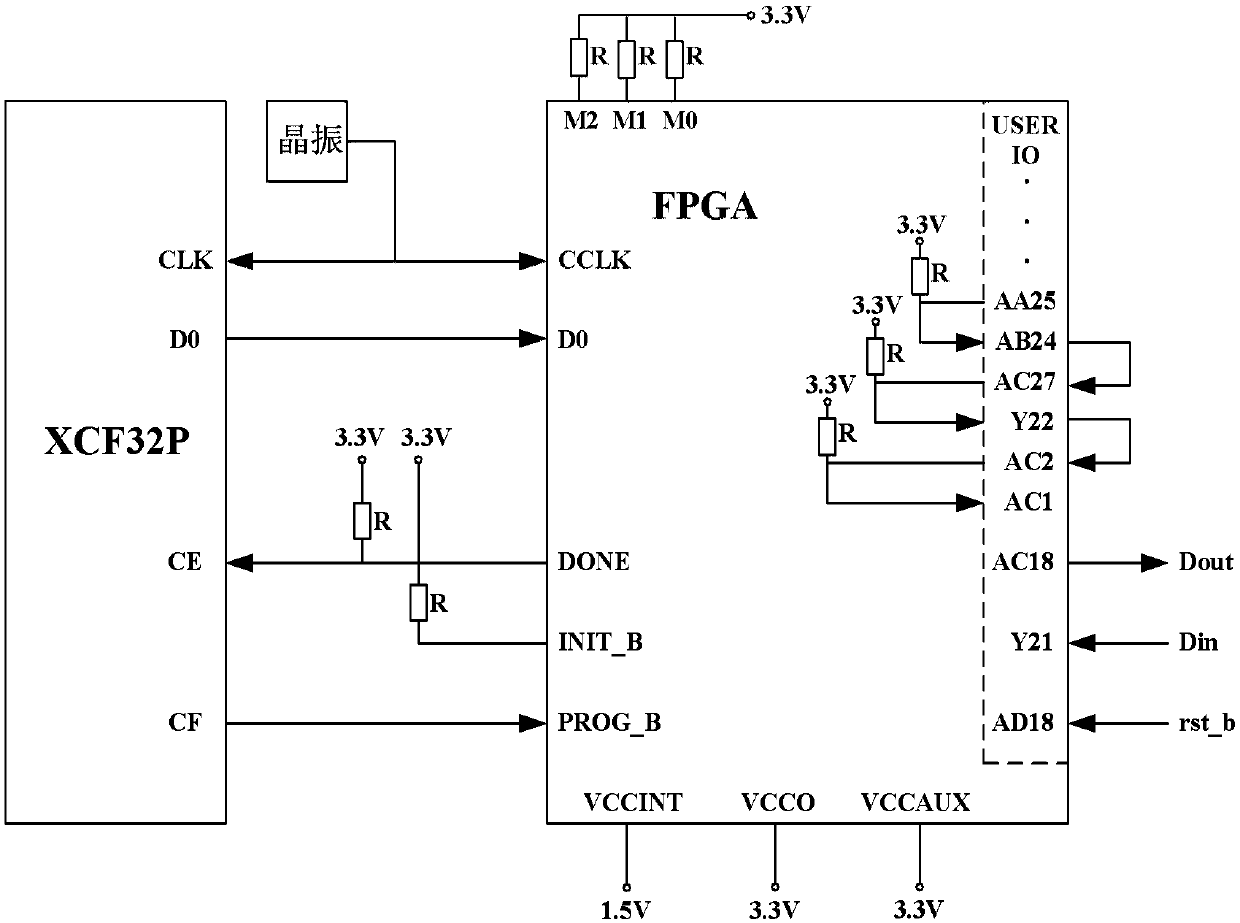

[0034] The present disclosure provides an FPGA burn-in test system and its circuit configuration method, based on a programmable read-only memory (PROM, Programmable Read-Only Memory) configuration method, adopting a passive serial configuration mode, through configuration and monitoring outside the incubator The board configures the FPGA, and the status of the device during the burn-in process can be monitored in real time; according to the rich characteristics of the built-in IP core of the FPGA device, the burn-in circuit is designed, and the working frequency of the burn-in circuit is reasonably determined through the calculation of the device junction temperature. There are few lead-out terminals on the board, and the connection structure with the outside of the incubator is simple and convenient; the burn-in test system can adaptively update the configuration circuit according to the needs of the FPGA chip, and is suitable for different FPGA chips in the same package, whic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More