Array substrate, manufacturing method thereof, and display device

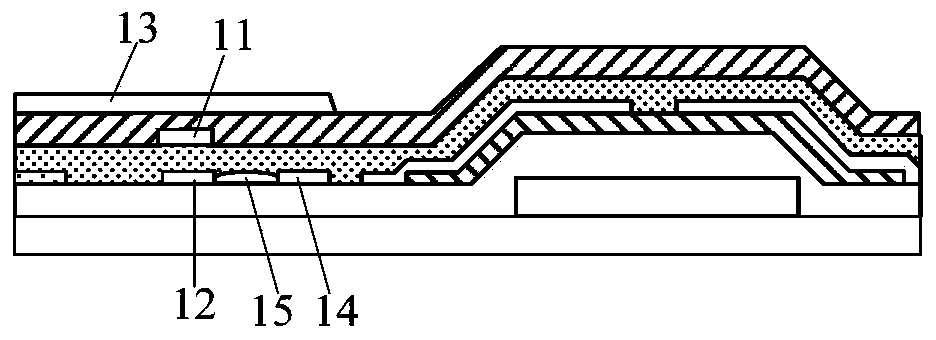

A technology of an array substrate and a manufacturing method, which is applied to semiconductor/solid-state device parts, instruments, semiconductor devices, etc., and can solve the problem of short circuit of data lines 14 and parallel signal lines 12, failure of sub-pixels to provide data voltage, and failure of sub-pixels to display normally and other problems, to achieve the effect of reducing the occurrence of short circuits, improving the display effect, and reducing the grid phenomenon

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. It should be understood that the specific embodiments described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention.

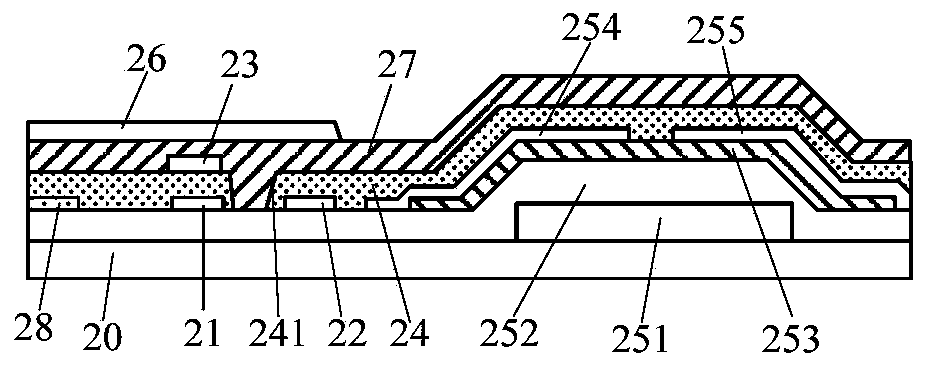

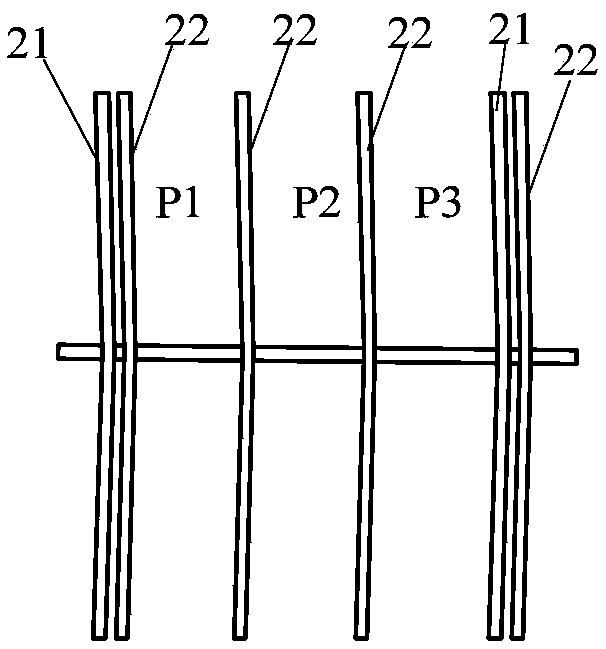

[0039] As an aspect of the present invention, an array substrate is provided, such as figure 2 As shown, it includes a substrate 20 , a first signal line 21 and a second signal line 22 disposed on the substrate 20 , and an insulating layer 24 . Wherein, the first signal line 21 and the second signal line 22 are arranged on the same layer and spaced apart from each other, the insulating layer 24 covers the first signal line 21 and the second signal line 22, and a groove 241 penetrating through the insulating layer 24 is formed on the insulating layer 24 , the position of the groove 241 corresponds to the interval area between the first signal line 21 and the se...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More