Clock frequency dividing circuit and frequency dividing method thereof

A clock frequency division and clock technology, which is applied in the clock frequency division circuit and its frequency division field, can solve the problems of failure to meet the design requirements, chip power consumption and speed, etc., and achieve a balance between chip power consumption and performance, The effect of multiple frequency selection

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

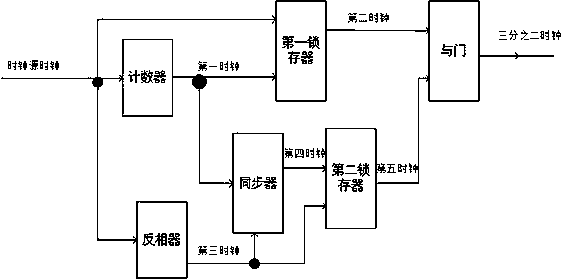

[0022] Such as figure 2 As shown, it is a structural diagram of a clock frequency division circuit implemented in the present invention. The specific components of the clock frequency division circuit include a counter, a first latch, a second latch, an inverter, a synchronizer and an AND gate, wherein the output of the counter is connected to the input of the first latch, and the second The output terminal of a latch is connected to the input terminal of the AND gate, the output terminal of the counter is connected to the input terminal of the synchronizer, the output terminal of the synchronizer is connected to the input terminal of the second latch, and the output terminal of the second latch is connected to the AND gate The input end of the inverter, the output end of the inverter is connected to the input end of the second latch, and the external input signal is used as a clock source to input the clock into the counter, the first latch, and the inverter.

[0023] The i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More