An adaptive digital background calibration circuit and method with adjustable down-sampling rate

A technique for downsampling rate and calibrating circuits, applied in analog/digital conversion calibration/testing, energy-saving methods, electrical components, etc., can solve the problems of power consumption redundancy of digital processing circuits, and reduce power consumption redundancy , low power consumption, guaranteed speed and accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

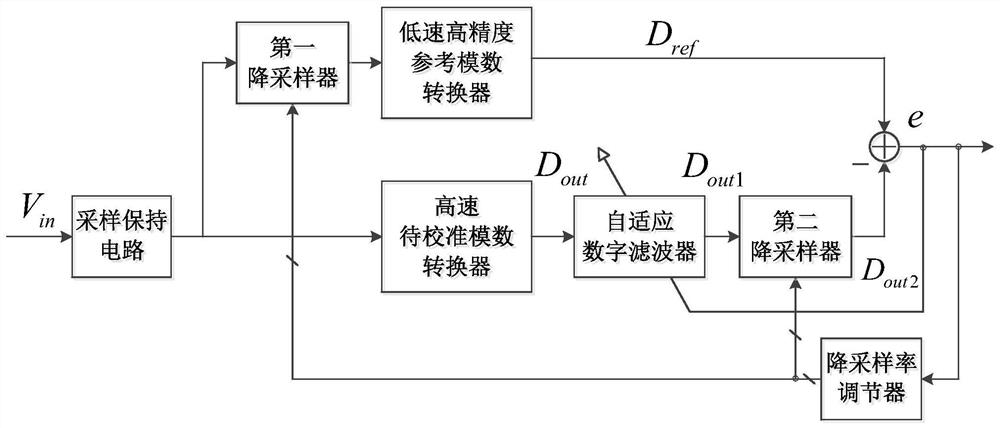

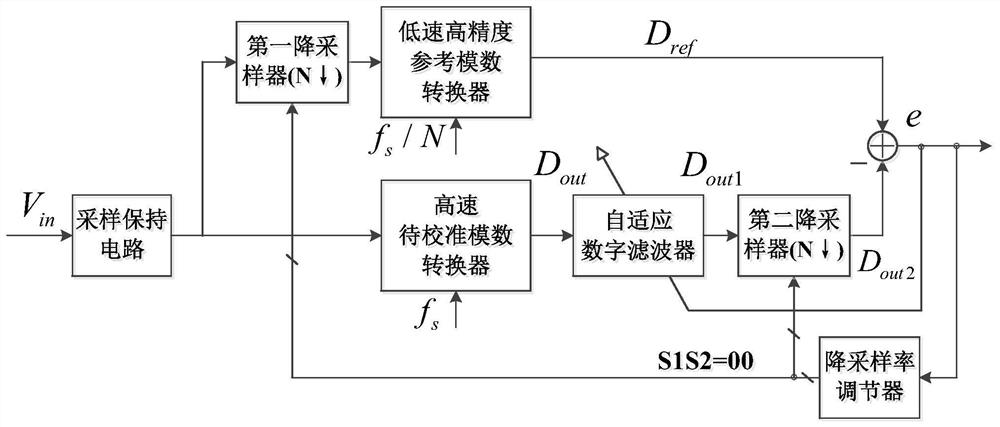

[0030] Such as figure 1 As shown, an adaptive digital background calibration circuit with adjustable downsampling rate, including:

[0031] A sample-and-hold circuit samples the analog input signal and keeps the sampled signal unchanged during subsequent analog-to-digital conversion;

[0032] The first downsampler performs downsampling processing on the data sent to the reference branch to ensure that the low-speed high-precision reference analog-to-digital converter of the reference branch can work normally;

[0033] A low-speed high-precision reference analog-to-digital converter provides an accurate reference source for calibration;

[0034] The high-speed analog-to-digital converter to be calibrated refers to a high-speed analog-to-digital converter that needs to be processed by a calibration circuit;

[0035] Adaptive digital filter, according to the value of the calibration error output by the subtractor, according to the adaptive filtering algorithm, continuously update...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More