Task mapping method for information security of multi-core processor

A multi-core processor, task mapping technology, applied in the fields of electrical digital data processing, computer security devices, instruments, etc., can solve the problem of reducing the success rate, hot side channel leakage, reducing command information and the correlation between transient temperature and space temperature, etc. problems, to achieve the effect of reducing the success rate and reducing the relevance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] Exemplary embodiments of the present invention will now be described in detail with reference to the accompanying drawings. It should be understood that the implementations shown and described in the drawings are only exemplary, intended to explain the principle and spirit of the present invention, rather than limit the scope of the present invention.

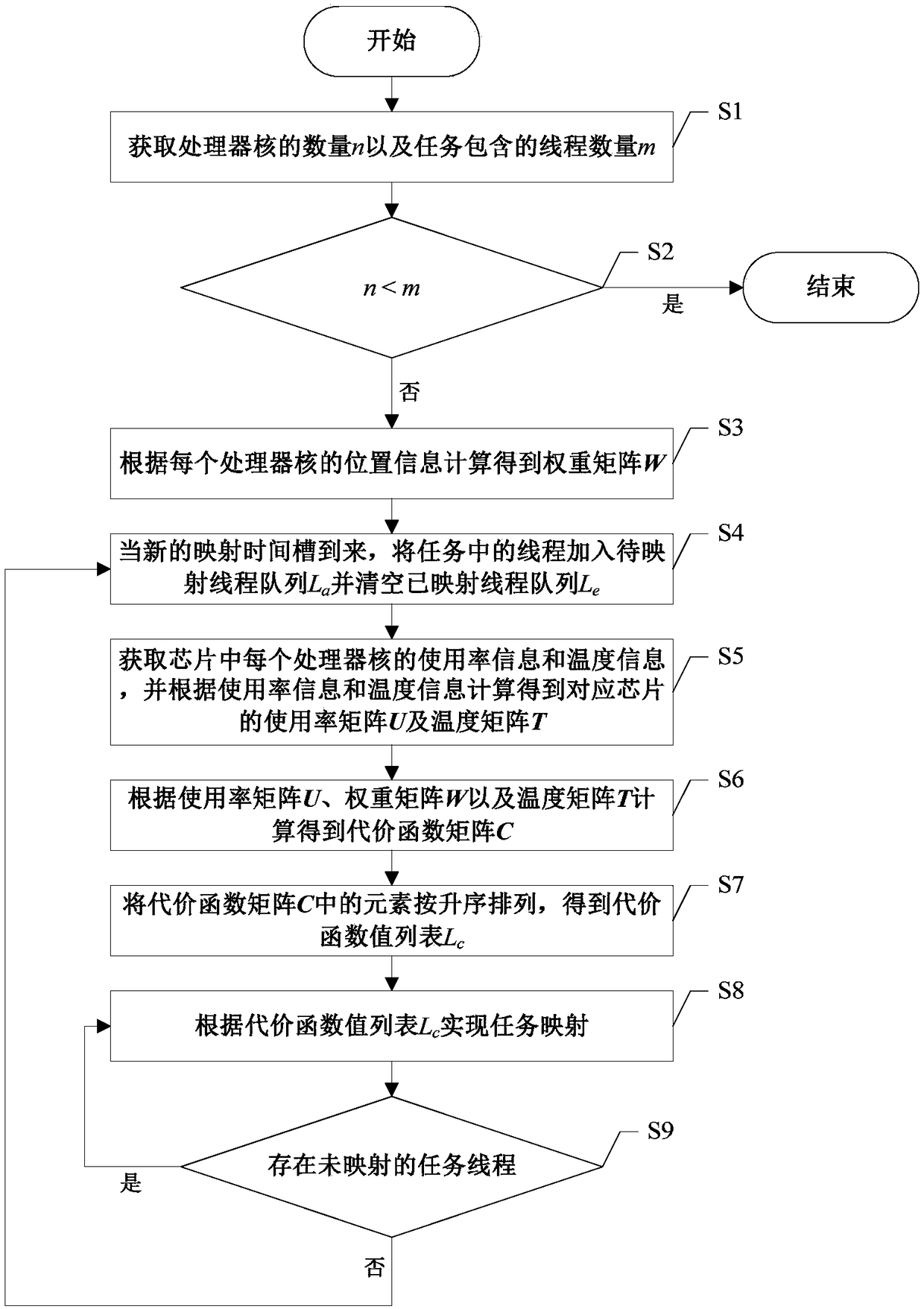

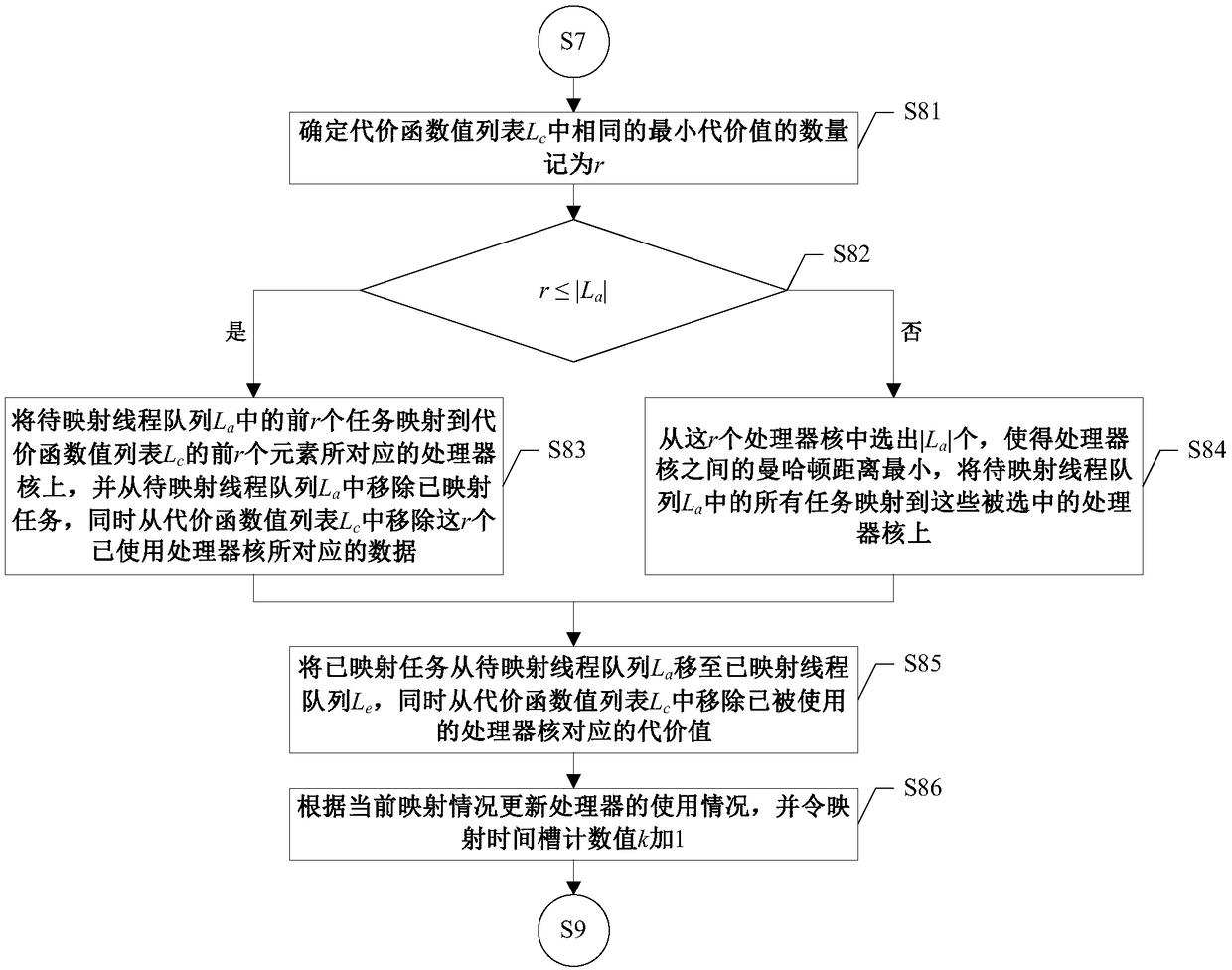

[0047] The embodiment of the present invention provides a task mapping method for multi-core processor information security, such as figure 1 As shown, including the following steps S1-S9:

[0048] S1. Obtain the number n of processor cores and the number m of threads included in the task.

[0049] S2. Judging whether n

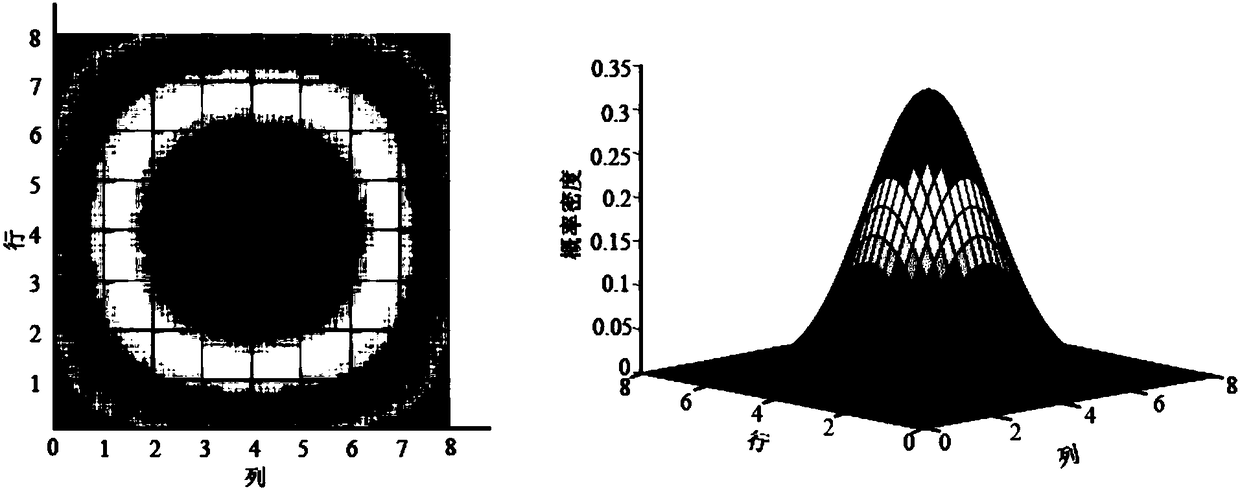

[0050] S3. Calculate and obtain a weight matrix W according to the location information of each processor core.

[0051] The i-th element of the weight matrix W is the weight value W of processor i (xi,yi)...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More