A bidirectional false gate deep well electrostatic protection device for increasing failure voltage and a manufacturing method thereof

An electrostatic protection and device technology, applied in the field of bidirectional false gate deep well electrostatic protection devices, can solve problems such as insufficient protection capability, device latch-up effect, low maintenance voltage, etc., to avoid thermal breakdown, prevent latch-up effect, maintain Effects of current density and leakage current density reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

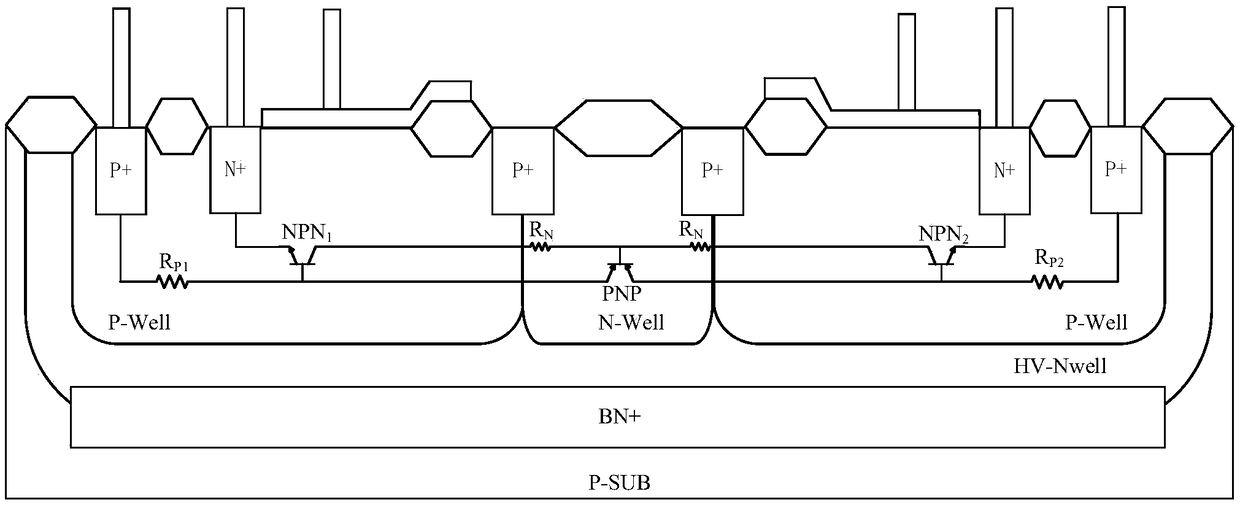

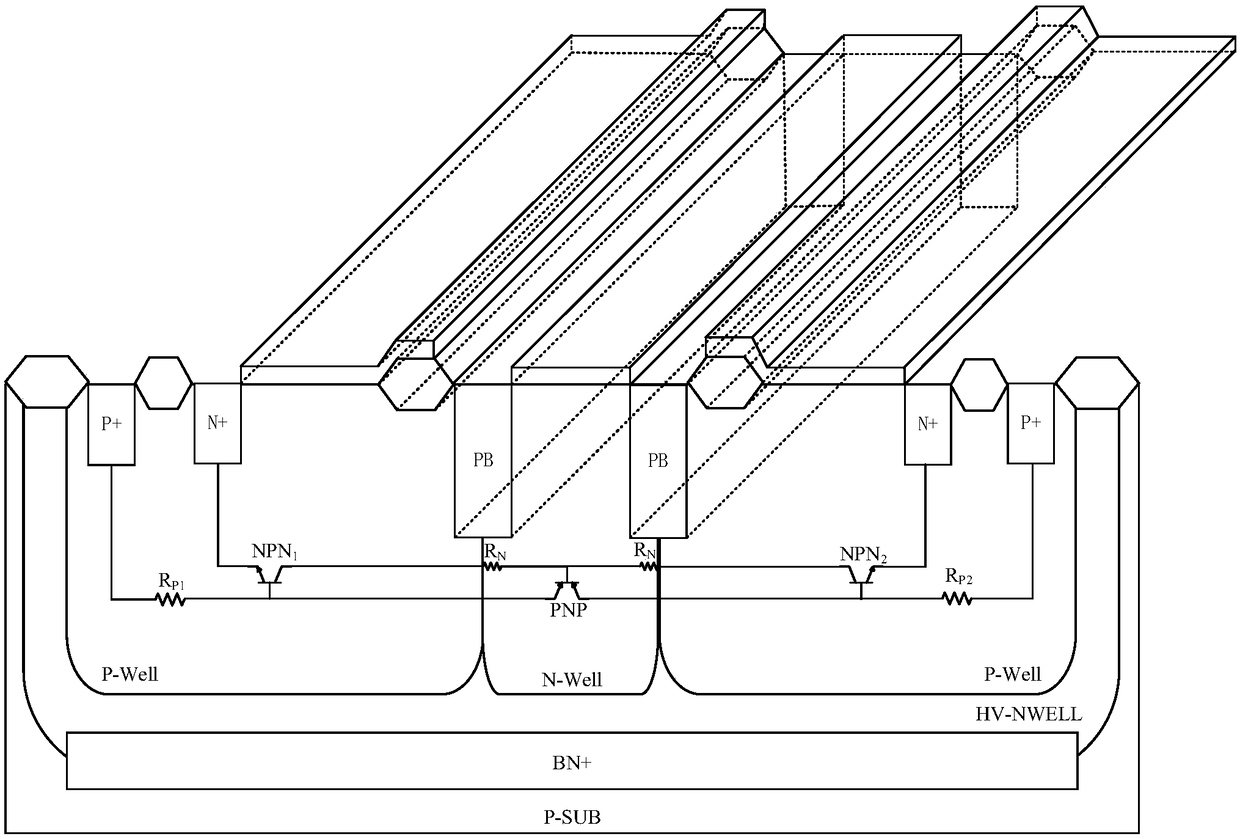

[0034] Such as Figure 2-Figure 4 As shown, a bidirectional dummy gate deep well electrostatic protection device with improved failure voltage includes a P-type substrate 101; an N-type buried layer 102 and a high-voltage N well 103 are arranged in the P-type substrate 101, and the high-voltage N well 103 is located above the N-type buried layer 102; the first P well 104, N well 105 and second P well 106 are arranged in the high-voltage N well 103 from left to right, and the left and right ends of the N well 105 are close to the first P well 104, second P well 106; the first P well 104 is provided with a first P+ implantation region 107 and a first N+ implantation region 108 from left to right; the first P well 104 and the N well 105 A first PB implantation region 109 is straddled between them; a second PB implantation region 110 is straddled between t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More