A kind of manufacturing method of depletion mode field effect transistor

A field-effect transistor and manufacturing method technology, which is applied in the manufacture of semiconductor/solid-state devices, electrical components, circuits, etc., can solve the problems of difficult to precisely control the doping concentration of the channel region, serious lateral and vertical diffusion, and influence on ion distribution, etc. Achieve the effect of saving lithography levels, meeting different requirements and ensuring stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0053] The specific embodiments of the present invention will be further described below in conjunction with the accompanying drawings.

[0054] This application optimizes the manufacturing process of depletion-type field effect transistors and provides a new method of manufacturing depletion-type field-effect transistors. Please refer to Figure 9 The schematic diagram of the production process is shown, and the production method is as follows:

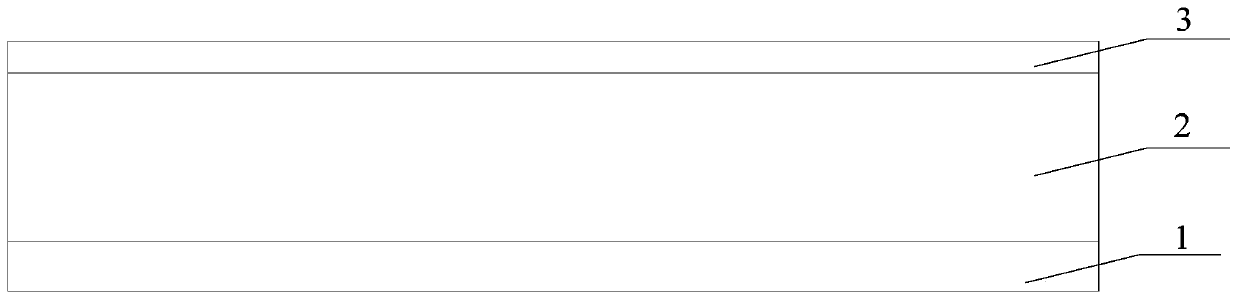

[0055] Step S01, providing a substrate 10, growing an epitaxial layer 20 on the substrate 10, the epitaxial layer 20 is doped with ions of a first conductivity type, where the first conductivity type ions are N-type ions or P-type ions, so that the epitaxial layer 20 Formed as an N-type epitaxial layer or a P-type epitaxial layer, the present application takes the substrate 10 as an N-type substrate and the epitaxial layer 20 doped with N-type ions to form an N-type epitaxial layer as an example.

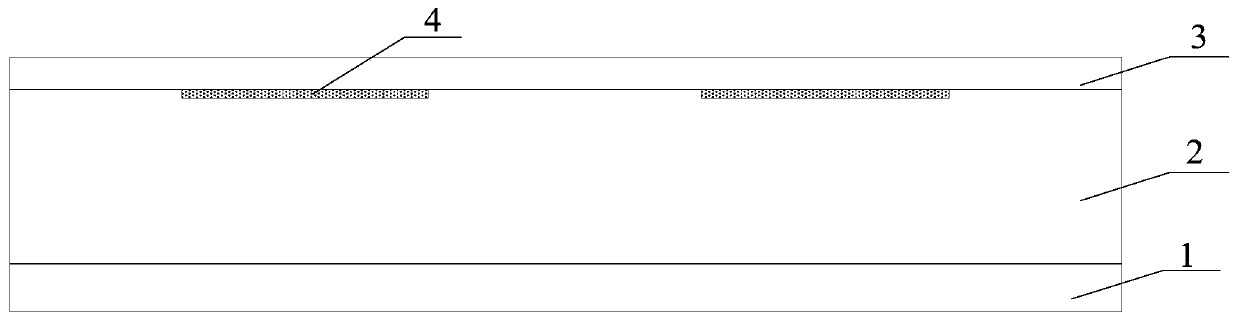

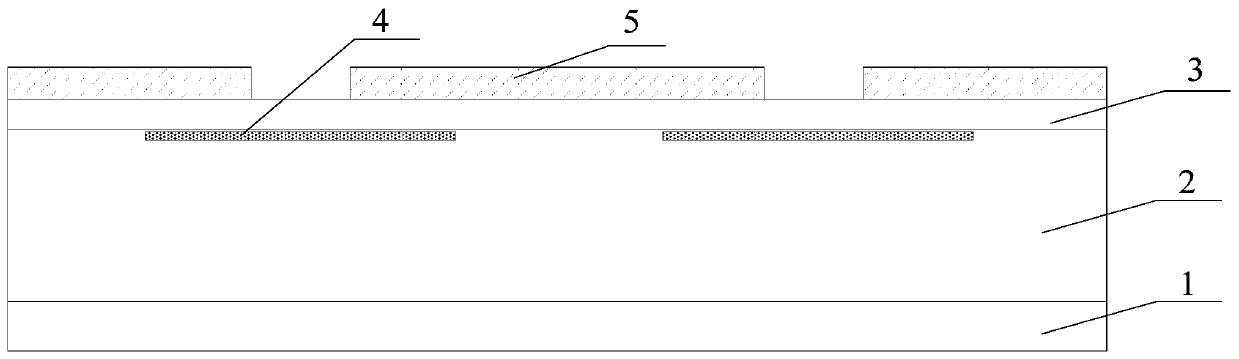

[0056] Step S02 , forming a thick ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More