Phase compensation method and related phase locked loop module

A phase-locked loop, phase compensation technology, applied in the direction of automatic power control, electrical components, etc., can solve the problems of the phase-locked loop circuit 10 calibration speed drop, deviating from the real phase of known data, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

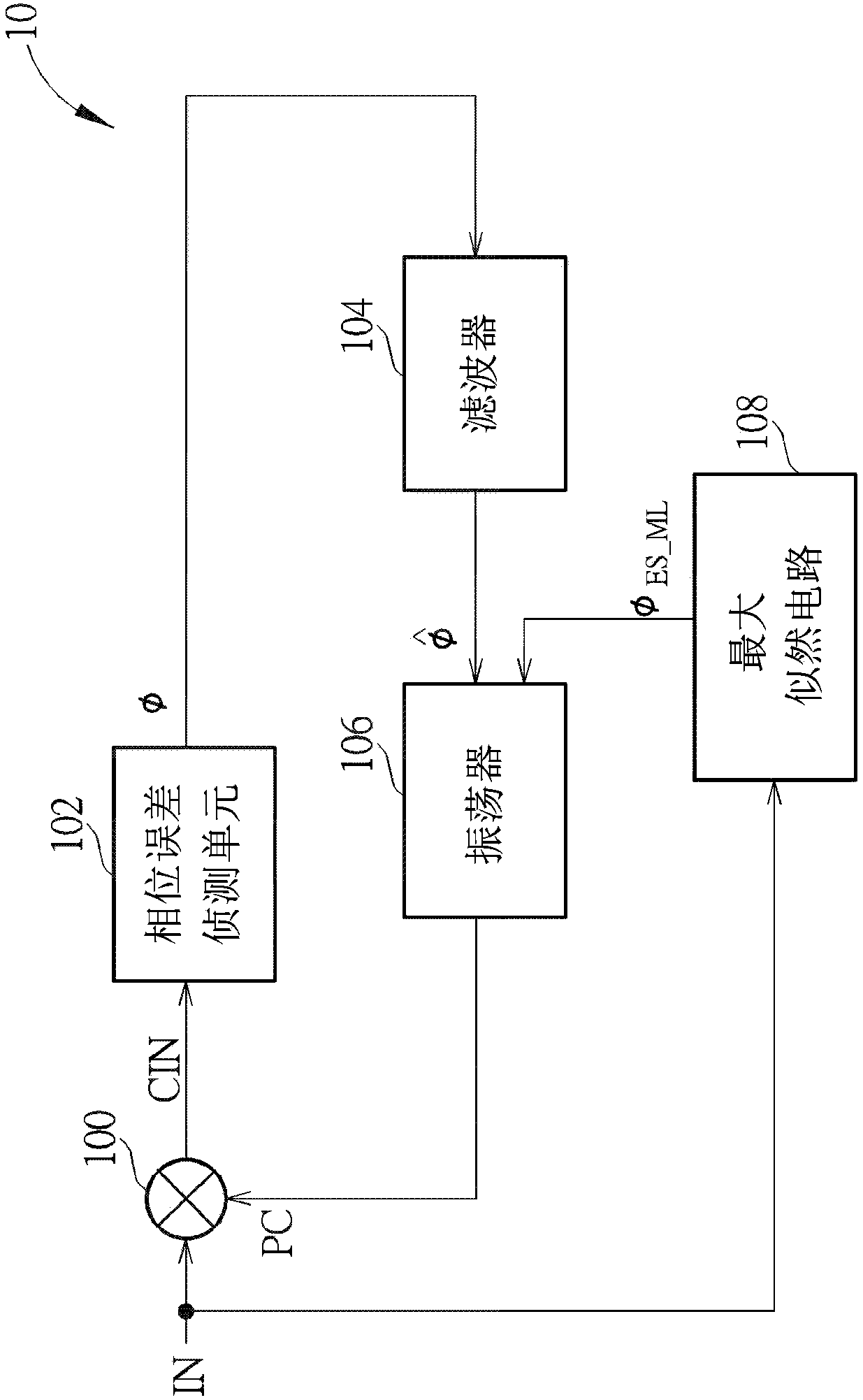

[0034] Please refer to figure 2 , figure 2 It is a schematic diagram of a phase-locked loop module 20 according to an embodiment of the present invention. The PLL module 20 can be installed in a communication device for correcting the phase error φ of an input signal IN. The communication device can be, for example, a smart phone, a tablet computer, a notebook computer, and a set-top box, but is not limited thereto. like figure 2 As shown, the PLL module 20 includes a multiplier 200, a phase error detection unit 202, a filter 204, an oscillator 206, a maximum likelihood circuit 208, a data auxiliary circuit 210, a monitoring unit 212 and A multiplexer 214. The operation mode of the multiplier 200, the phase error detection unit 202, the filter 204, the oscillator 206 and the maximum likelihood circuit 208 in the phase-locked loop module 20 is the same as that of the multiplier 100, the phase error detection in the phase-locked loop circuit 10 The unit 102 , the filter ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com