SiP system based on JTAG test and JTAG test method of inside chip of SiP system

A test method and technology of the chip under test, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., can solve the problems of high test plan planning efficiency, complex testing, and various types of functional tests in SiP modules, so as to improve accessibility. , the effect of improving controllability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The present invention will be described in detail below in conjunction with the accompanying drawings and embodiments.

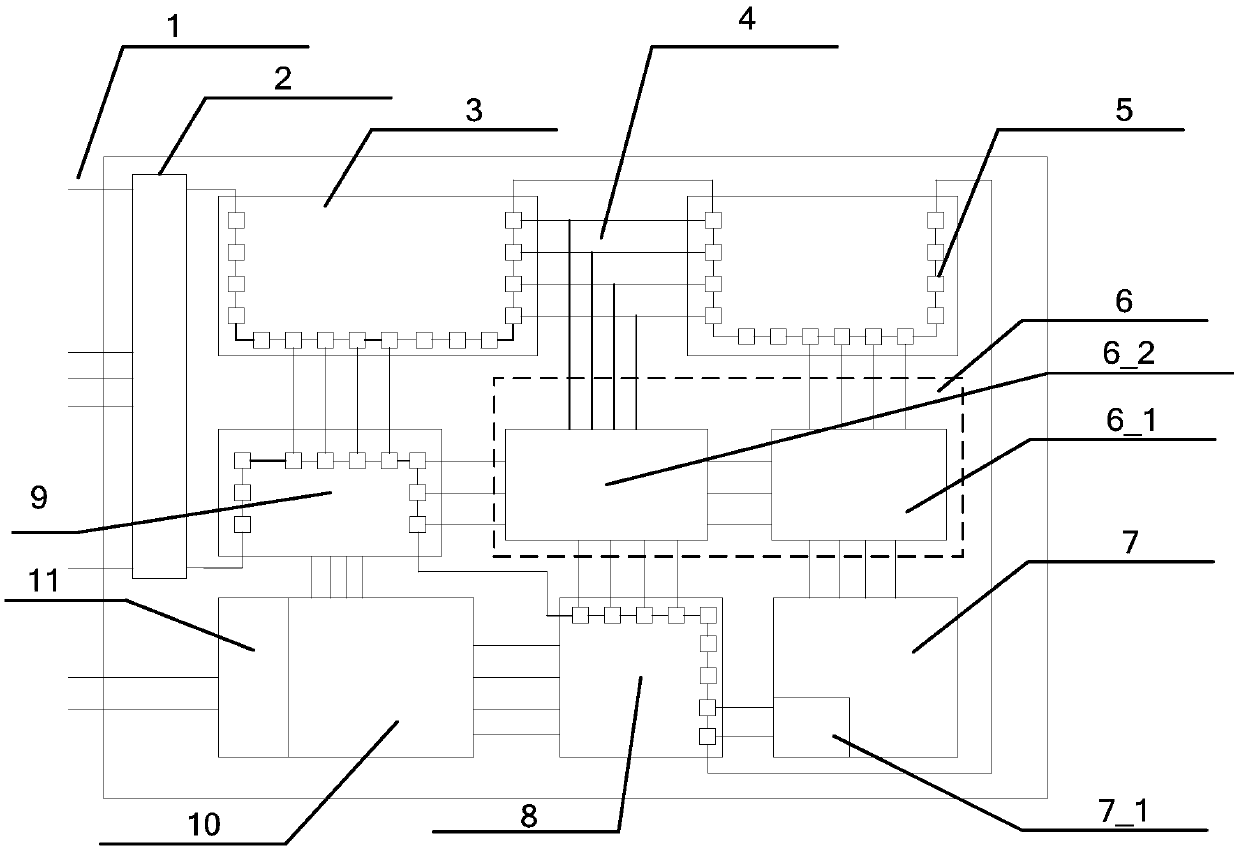

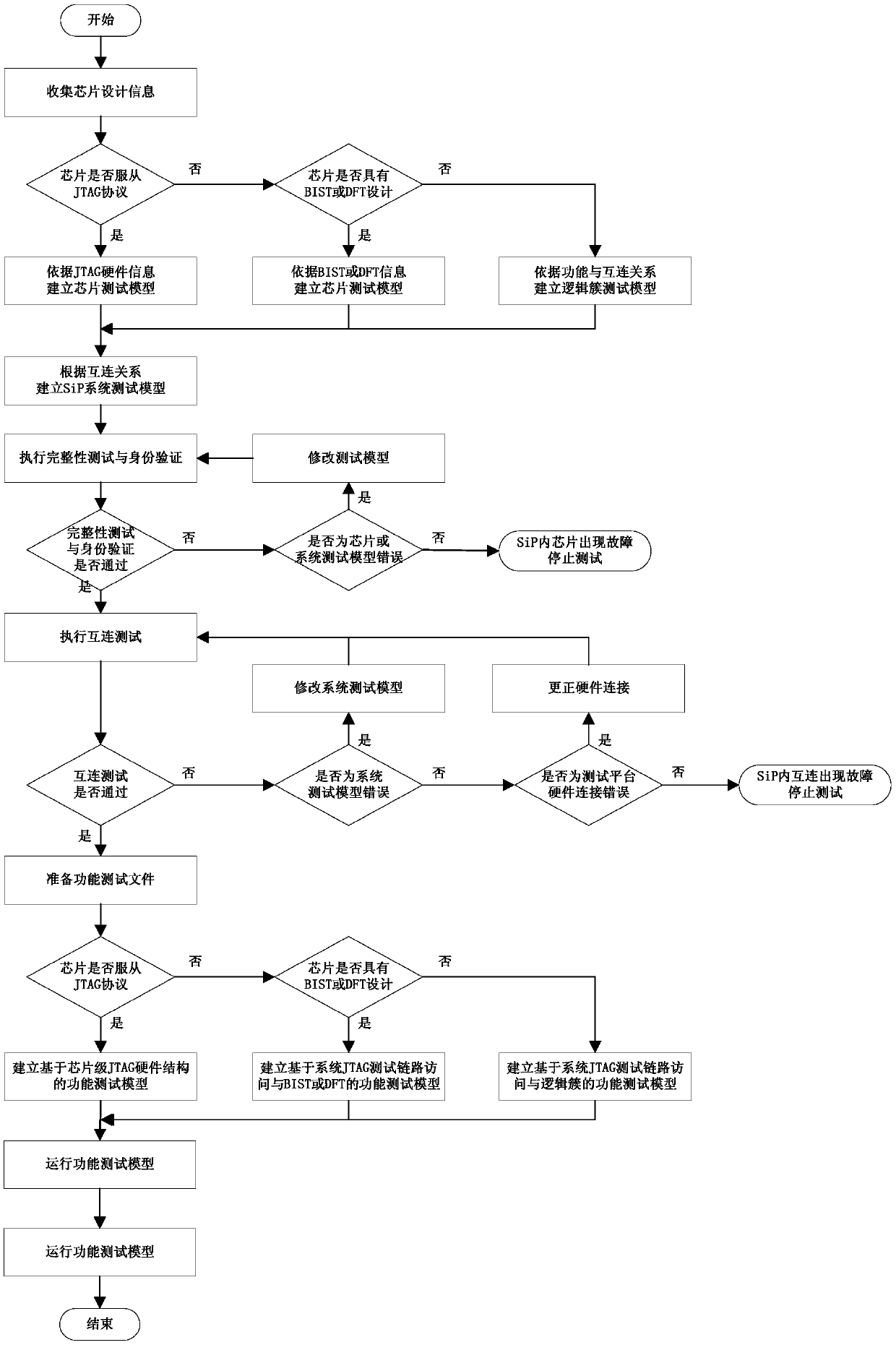

[0027] The invention proposes a JTAG test method for a SiP system based on JTAG test and its internal chips. This method aims at the characteristics that the chip in the SiP module is completely enclosed or semi-completely enclosed in the system package, and realizes the test of the internal chip of the SiP module through the interconnection design of the chip embedded in the SiP module, and uses the boundary scan unit of the chip and the JTAG test port. Implement the data path.

[0028] The SiP system based on JTAG test includes a JTAG test access port, at least two chips subject to the JTAG protocol, which are recorded as the first JTAG chip and the last JTAG chip, and the test input terminal TDI of the JTAG test access port is connected to the JTAG test input of the first JTAG chip On the terminal TDI, the JTAG test output terminal TDO of the firs...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com