Multi-chip simultaneous measurement structure and method

A multi-chip and chip technology, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., can solve the problems of excessive judgment and failure to test a single DUT power consumption parameter, and achieve the effect of reducing misjudgment and increasing the number of simultaneous measurements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

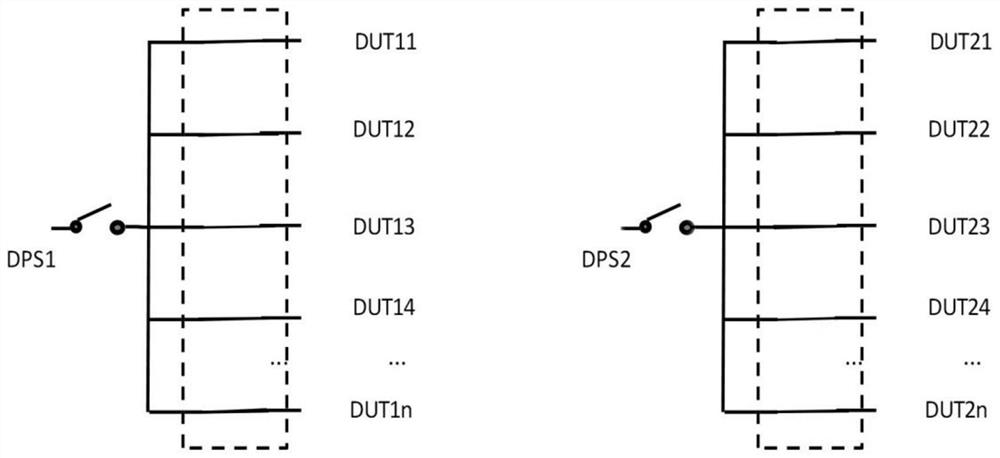

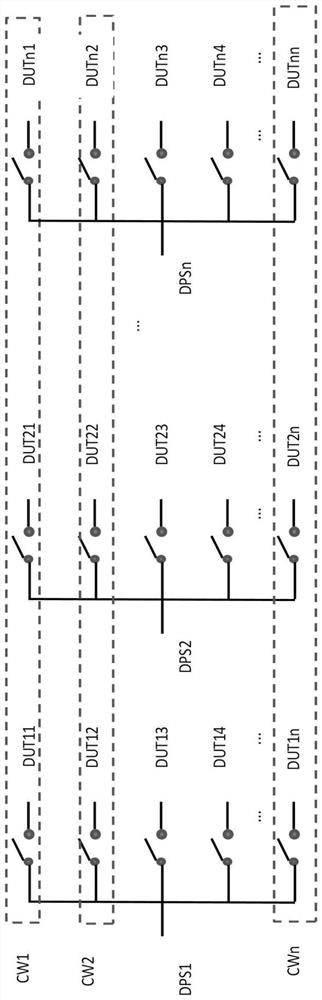

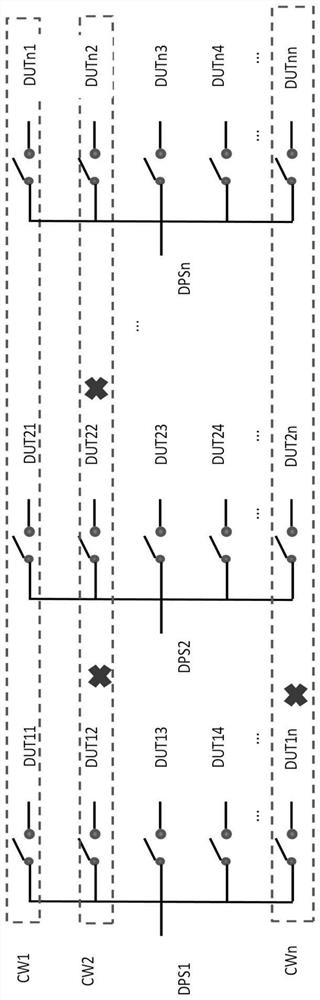

[0030] A kind of multi-chip simultaneous testing structure described in the present invention is for conducting electrical tests on the chips on the wafer, such as figure 2 As shown, the chip DUT to be tested on the wafer is divided into rows and columns to form a test array, and the chips to be tested on the same column are connected in parallel to form a test port of each column; the test port is connected to the power channel DPS of the tester, Contains DPS1~DPSn.

[0031] The chips to be tested on the same row share a control switch CW, from CW1 to CWn.

[0032] A tester, the tester has a plurality of power channels, one power channel of the tester corresponds to a row of test ports of the chips to be tested.

[0033] The chip to be tested includes a plurality of test pins; the number of rows of the test array is determined by the number of test pins of the chip to be tested, and the number of columns of the test array is determined by the number of power supply channels...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com