multi-core parallel signal processing system and method based on an SRIO bus

A signal processing, multi-core technology, applied in electrical digital data processing, instruments, etc., to achieve the effect of improving the real-time performance of the system and optimizing the operating efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] The present invention discloses a multi-core parallel signal processing system and method based on the SRIO bus. In order to make the present invention more obvious and understandable, the present invention will be further described below in conjunction with the accompanying drawings and specific implementation methods.

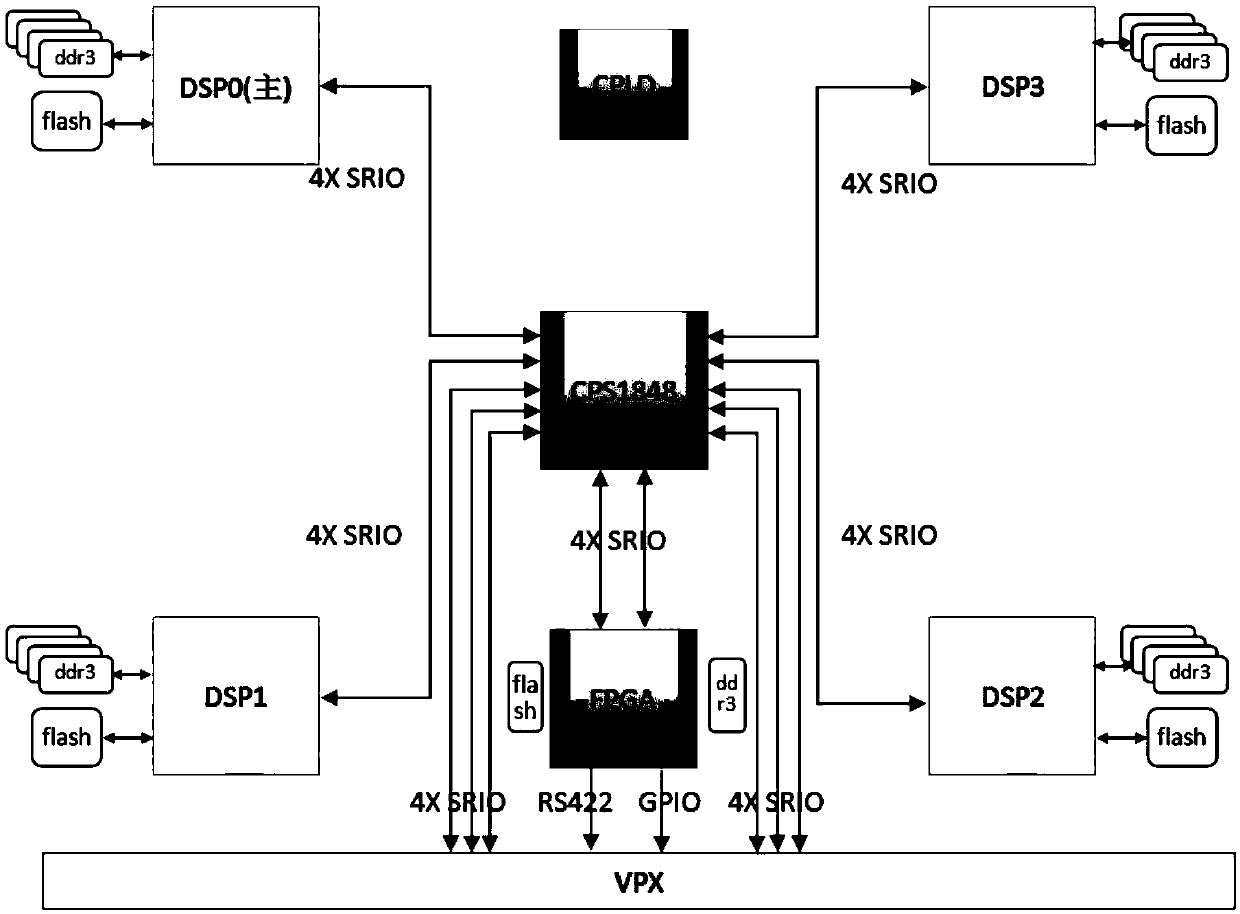

[0040] like figure 1 Shown, the multi-core parallel signal processing system based on SRIO bus of the present invention is provided with the plate card that comprises multi-chip multi-core DSP, and this plate card comprises 4 slices of DSP, a slice of CPS1848 high-speed interconnect exchange chip, a VPX interface, a slice of CPLD, a slice of FPGA chip.

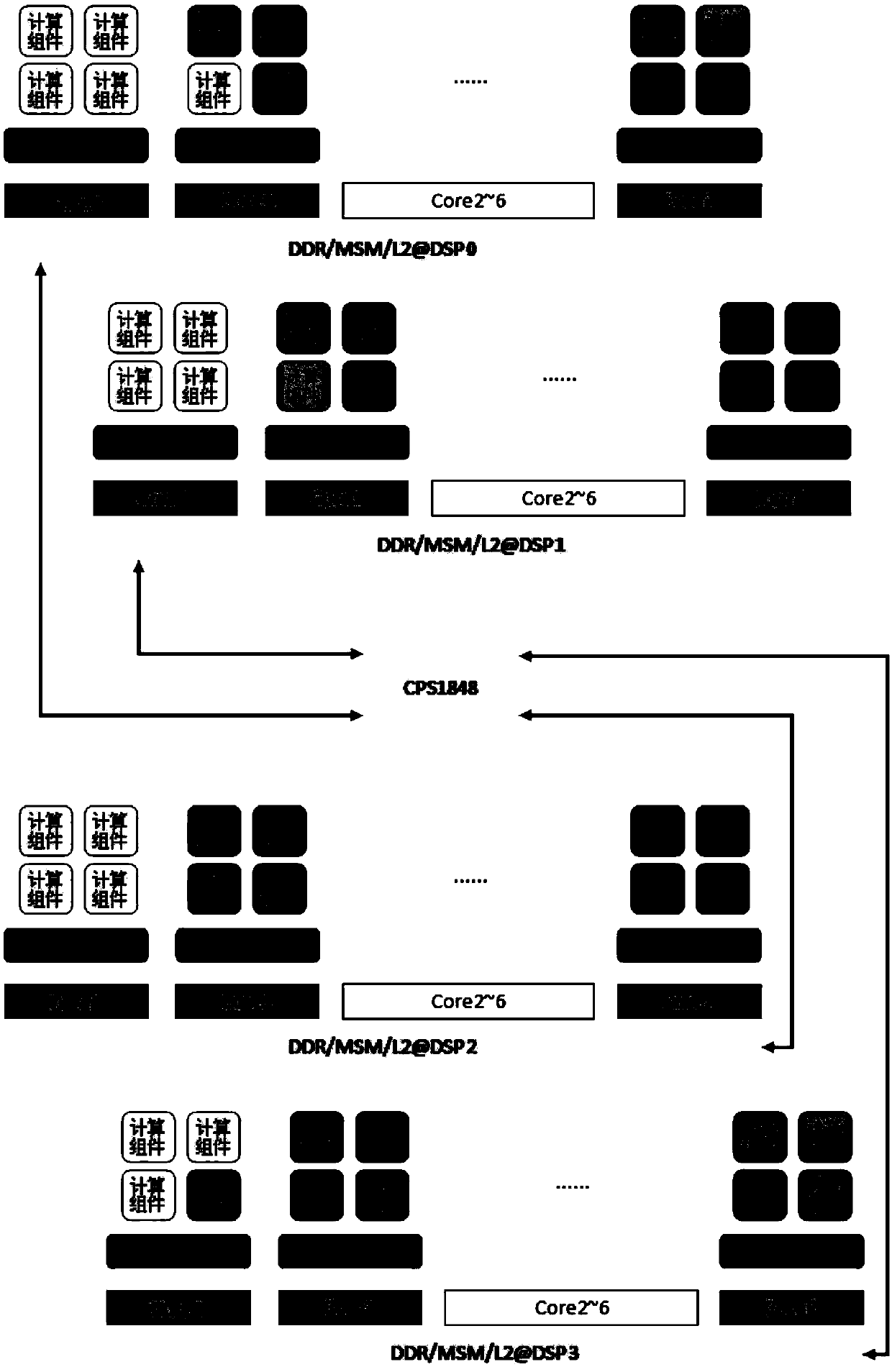

[0041] Each DSP contains 8 processor cores inside, and the processor core adopts VLIW (very long instruction word) architecture, which can theoretically execute up to 8 instructions in parallel.

[0042] The role of the CPS1848 high-speed interconnection switch chip is: the DSPs with built-in SRIO com...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More