Three-dimensional memory and manufacturing method thereof

A manufacturing method and memory technology, applied in the direction of electric solid-state devices, semiconductor devices, electrical components, etc., can solve the problems of poor performance of three-dimensional memory, and achieve the effects of enhancing stability and improving programming and erasing performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment approach

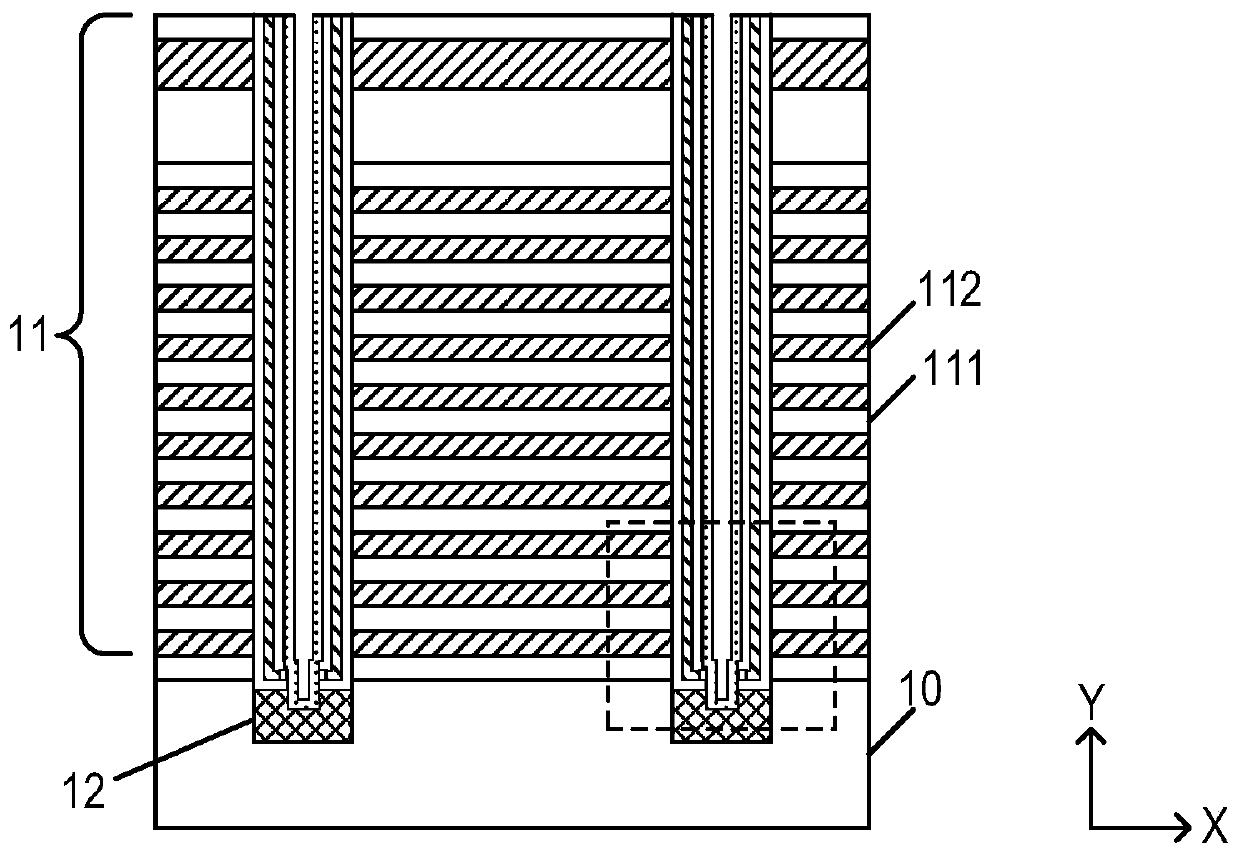

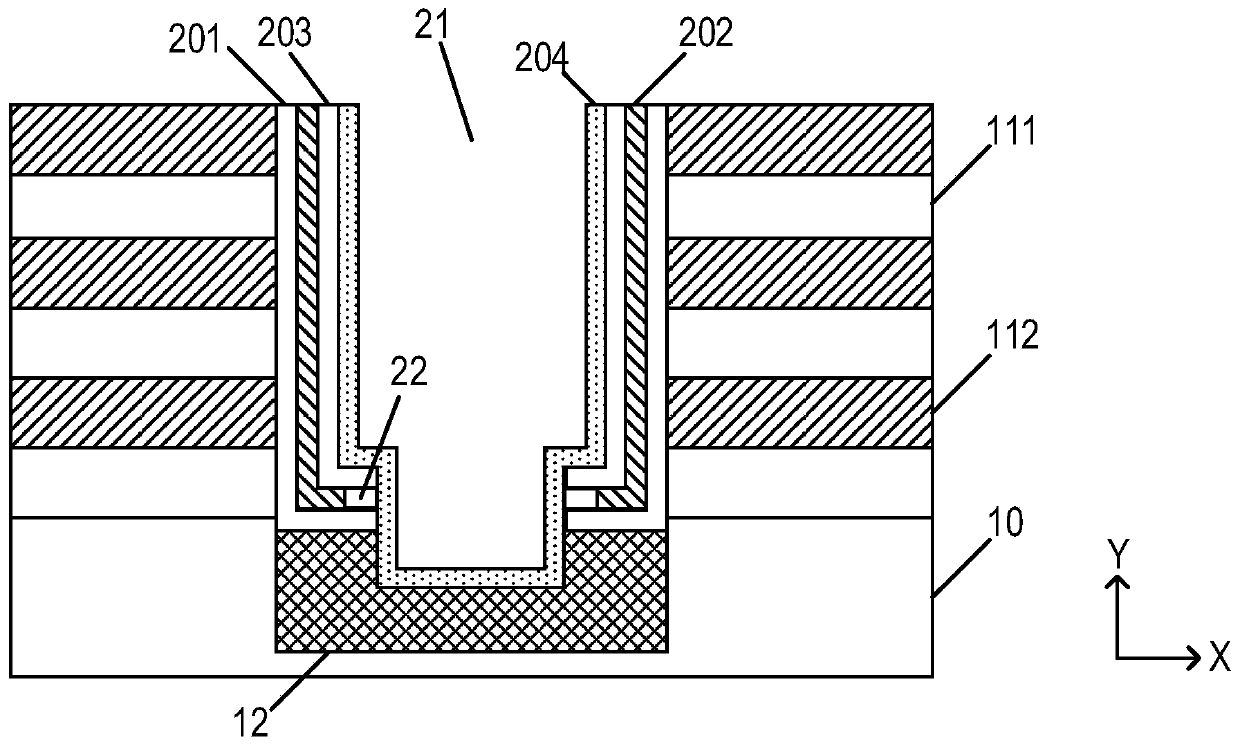

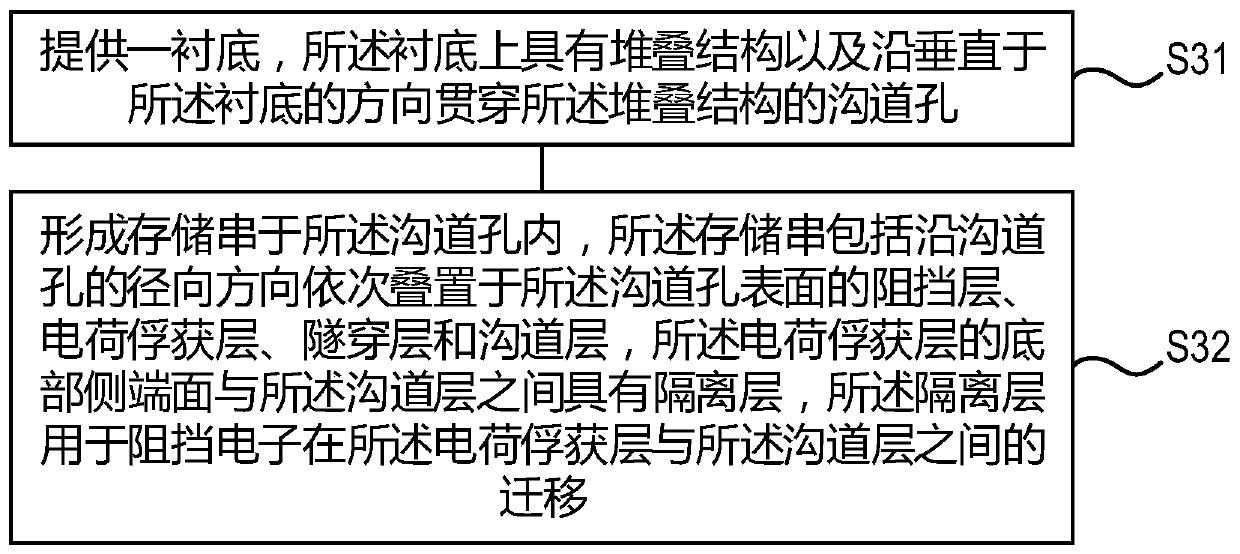

[0056] In three-dimensional memories such as 3D NAND, the storage unit as its key storage structure is composed of a storage string (that is, a NAND string) and its corresponding gate, wherein the storage string includes sequentially stacked gates along the radial direction of the channel hole. Barrier layer, charge trapping layer, tunneling layer and channel layer. After completing the deposition of the blocking layer, the charge trapping layer and the tunneling layer in the channel hole, the blocking layer, the charge trapping layer and the tunneling layer are etched to open the The bottom of the channel hole is exposed to expose the epitaxial semiconductor layer; and then the channel layer is deposited to form a channel channel.

[0057]As the market's requirements for storage density continue to increase, the number of stacked layers in the stacked structure in the three-dimensional memory continues to increase, which leads to a corresponding reduction in the size of the c...

no. 2 Embodiment approach

[0094] This specific embodiment provides a three-dimensional memory and its manufacturing method, with Figure 5 It is a structural schematic diagram of the three-dimensional memory in the second specific embodiment of the present invention. For the same parts as the first specific embodiment, this specific embodiment will not repeat it, and the differences from the first specific embodiment will be mainly described below.

[0095] Such as Figure 5 As shown, the three-dimensional memory provided in this specific embodiment includes:

[0096] a substrate 50, on which there is a stack structure and a channel hole penetrating through the stack structure along a direction perpendicular to the substrate 50;

[0097] The storage string, located in the channel hole, includes a blocking layer 521, a charge trapping layer 522, a tunneling layer 523 and a channel layer 524 stacked on the surface of the channel hole in sequence along the radial direction of the channel hole;

[0098]...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More