Memory testing device and method

A technology of memory testing and memory, which is applied in the direction of faulty hardware testing methods, error detection/correction, and detection of faulty computer hardware. Test production delays and other issues to achieve the effects of improving test efficiency, reliable design principles, and cost savings

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

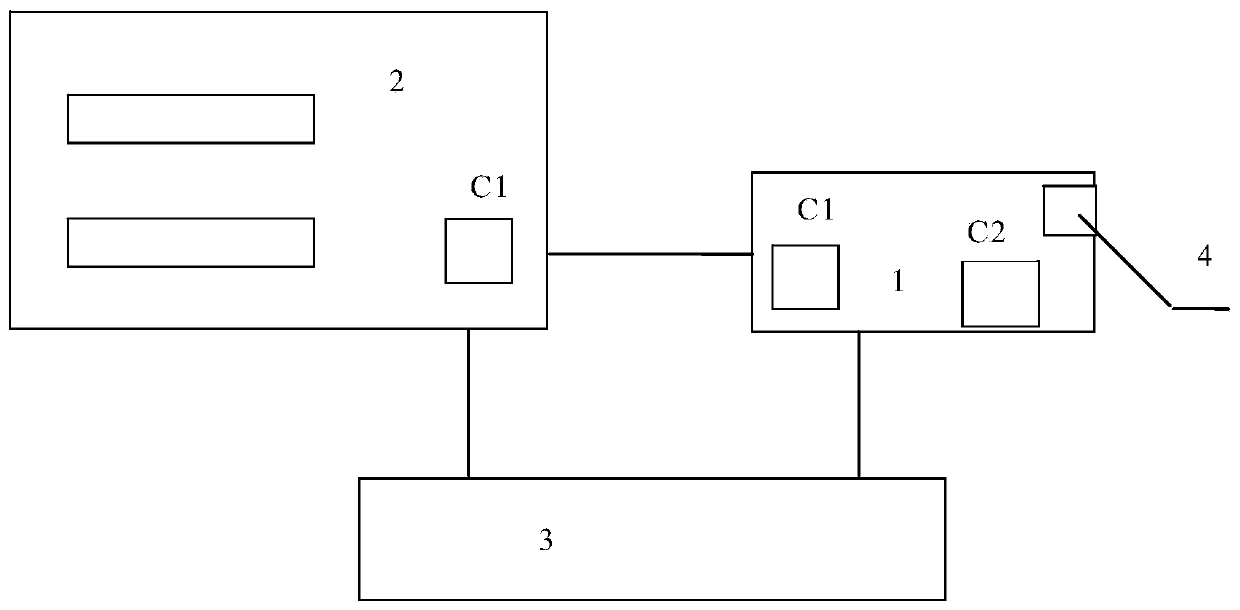

[0025] like figure 1 As shown, this embodiment provides a memory testing device, including a test control module 1 , a test execution module 2 and a power supply, and the power supply supplies power to the test control module 1 and the test execution module 2 . The test control module includes a control chip C2 and a first communication chip C1, and the control chip C2 is communicatively connected with the first communication chip C1. The test control module is also provided with a serial port 4, and the serial port is electrically connected to the control chip C2 as an I / O device of the control chip C2. The test execution module includes a second communication chip C1 and six memory test servers, each memory test server is communicatively connected to the second communication chip C1, and each memory test server can mount 4 memory sticks. The first communication chip C1 is electrically connected to the second communication chip C1 to realize communication between the test co...

Embodiment 2

[0027] This embodiment provides a memory testing device, including a test control module 1 and a test execution module 2, each of which has its own power supply. The test control module includes a control chip C2 and a first communication chip C1, and the control chip C2 is communicatively connected with the first communication chip C1. The test control module is also provided with a serial port 4, and the serial port is electrically connected to the control chip C2 as an I / O device of the control chip C2. The test execution module includes a second communication chip C1 and six memory test servers, each memory test server is communicatively connected to the second communication chip C1, and each memory test server can mount three memory sticks. The first communication chip C1 and the second communication chip C1 are electrically connected through a synchronous serial bus to realize communication between the test control module 1 and the test execution module 2 .

Embodiment 3

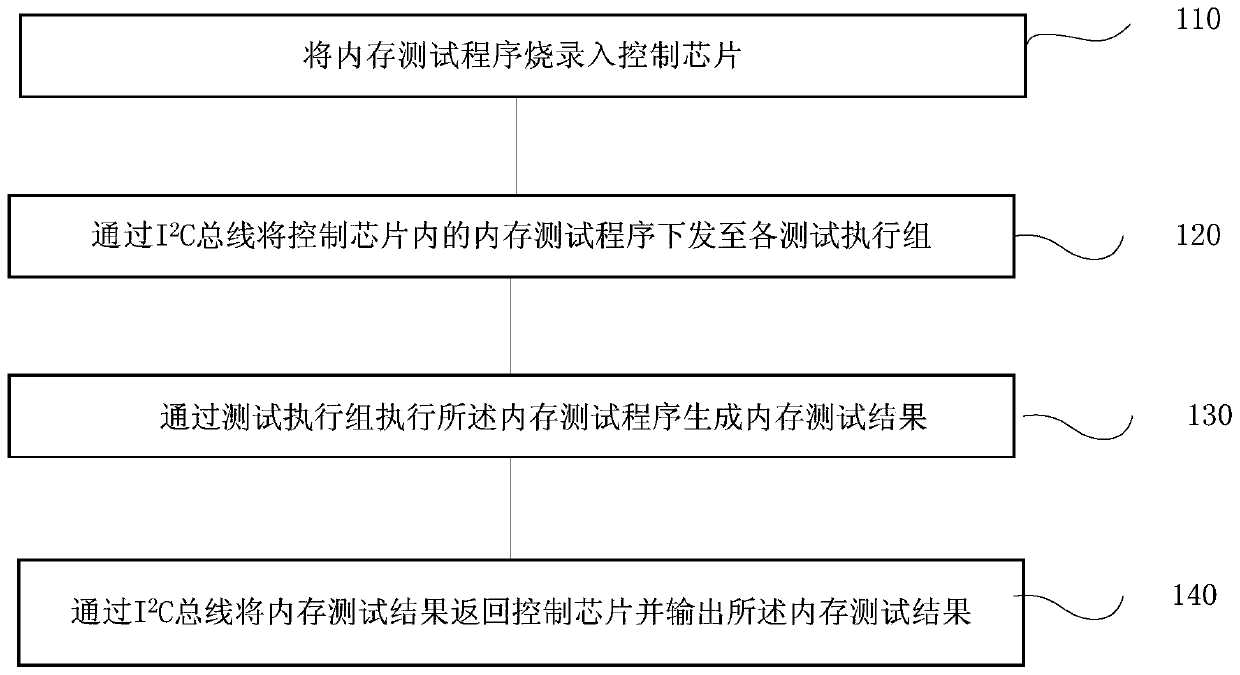

[0029] Please refer to figure 2 , this embodiment provides a memory testing method, which uses two memory test servers A and B, and each memory test server mounts three memory sticks 1, 2, and 3 as an example for illustration, including the following steps:

[0030] S1. Burn the memory test program into the control chip.

[0031] Connect the personal computer and the serial port of the test control module through the data cable. After connecting the personal computer to the serial port, control the control chip C2 of the test control module through the personal computer to start the simulated DOS or UEFI-like operating environment, and import the memory test program through the serial port connection. to the control chip C2.

[0032] S2, through I 2 The C bus sends the memory test program in the control chip to each test execution group.

[0033] The control chip C2 sends the memory test program to the first communication chip C1, and the first communication chip C1 passes...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More