UVM-based large-scale memory read-write verification platform and UVM-based large-scale memory read-write verification method

A verification platform and memory technology, applied in the electronic field, can solve problems such as limited configurable range and insufficient versatility, and achieve the effects of stable design, reduced storage space occupation, and improved simulation speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

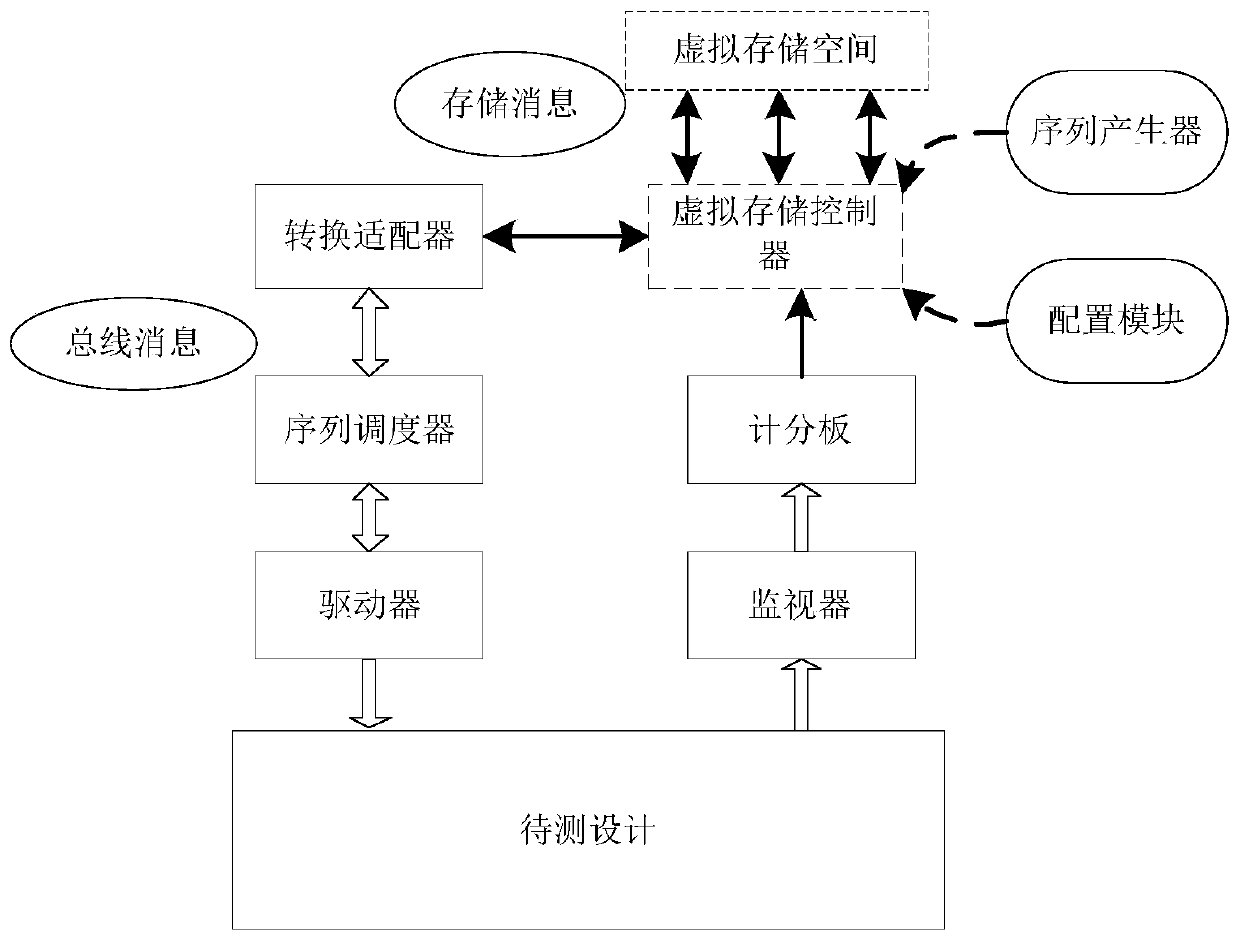

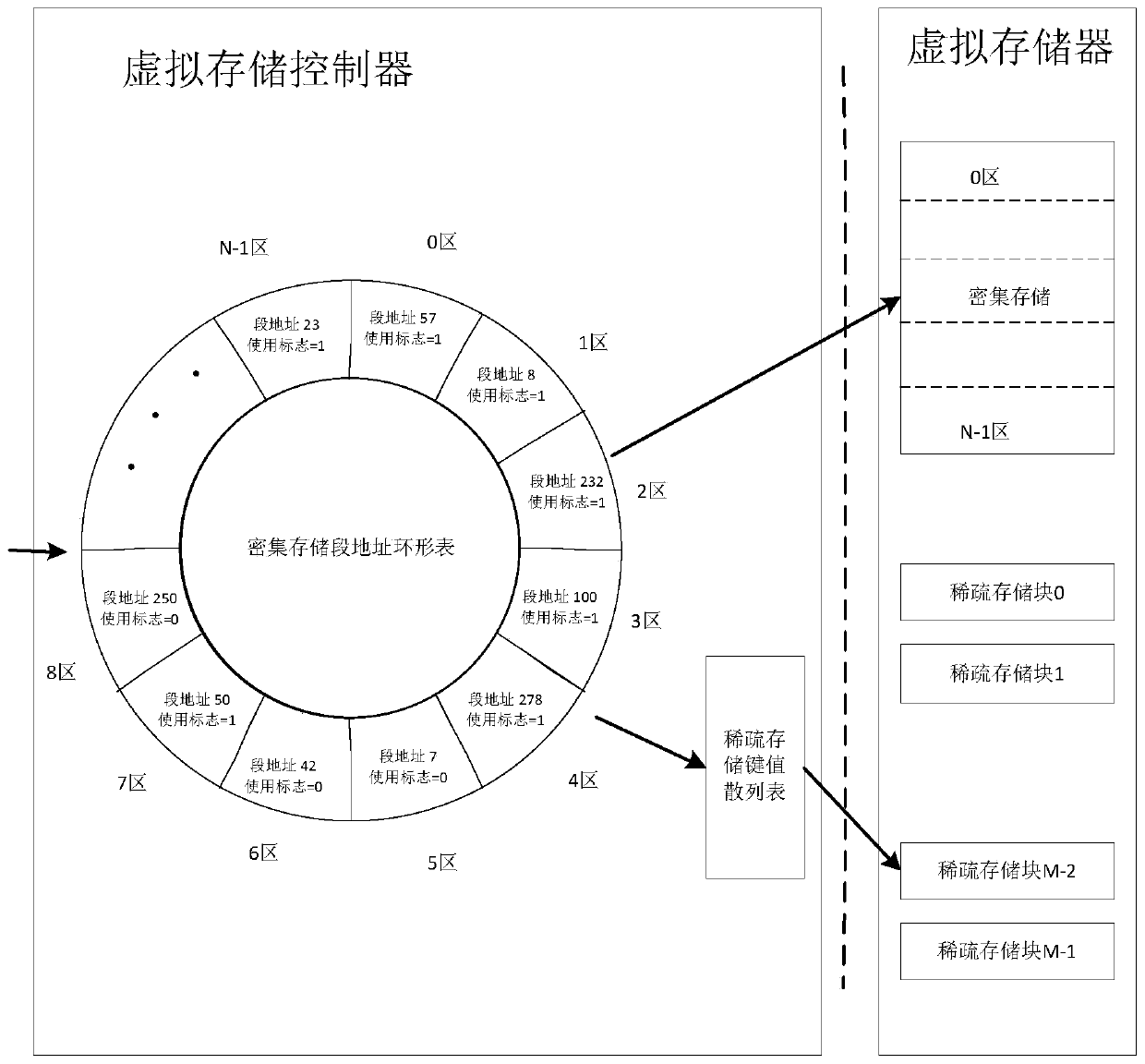

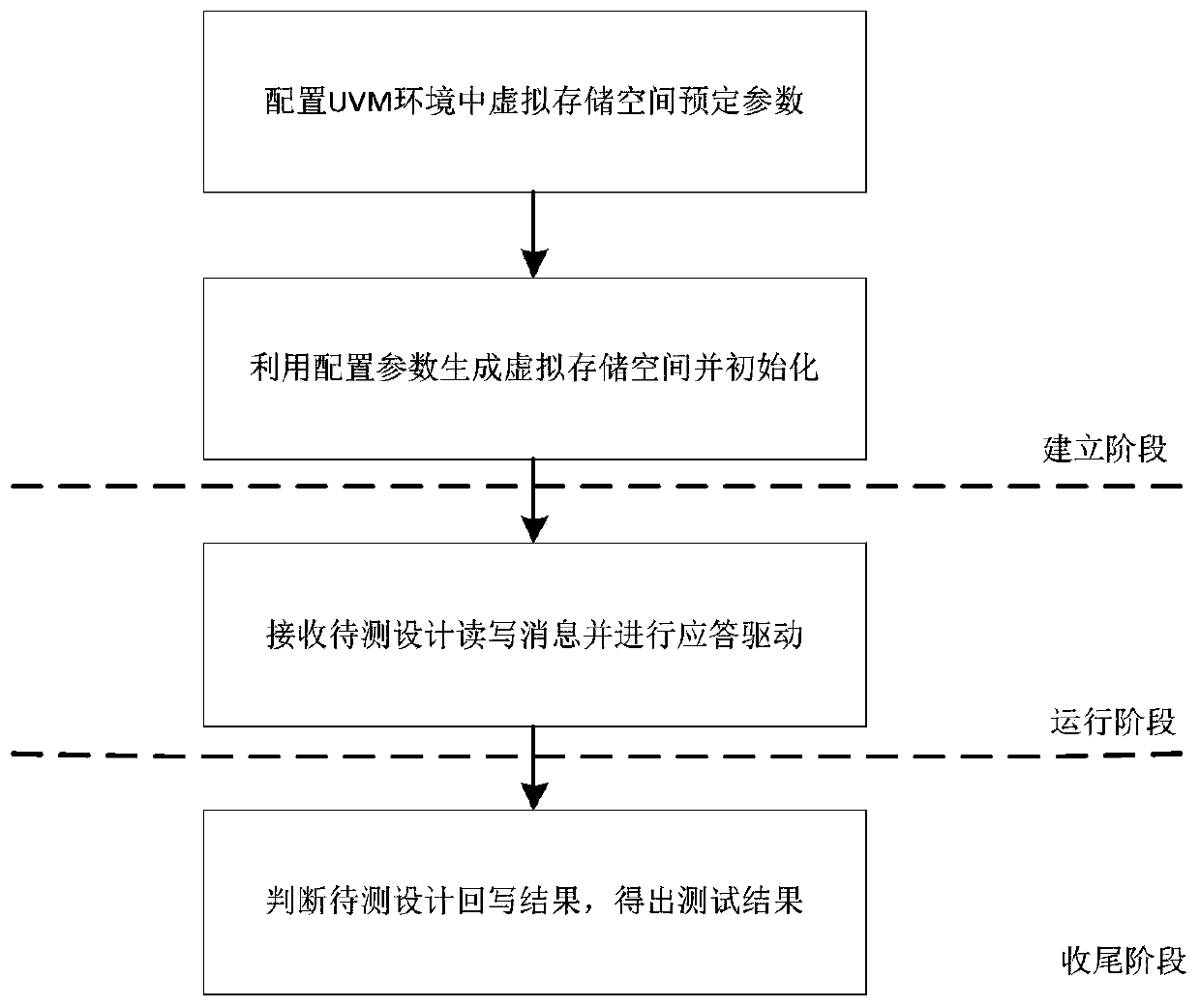

[0036] Such as Figure 1-6 As shown in one of them, the present invention discloses a large-scale memory read-write verification platform based on UVM, which includes a UVM verification test framework and a design module to be tested, the UVM verification test framework includes a sequence scheduler and a sequence generator, and the sequence generation The controller controls the generation and delivery of stored messages and arranges the sequence of stored messages on the time axis. The sequence scheduler drives the design module to be tested through a driver, and the sequence scheduler performs read and write tests on the design module to be tested through the driver. The design module to be tested will The test feedback information is output to the monitor and the scoreboard in sequence; the UVM verification test framework also includes a virtual storage controller and a virtual storage space, and the virtual storage space is used to initialize the virtual storage space and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More