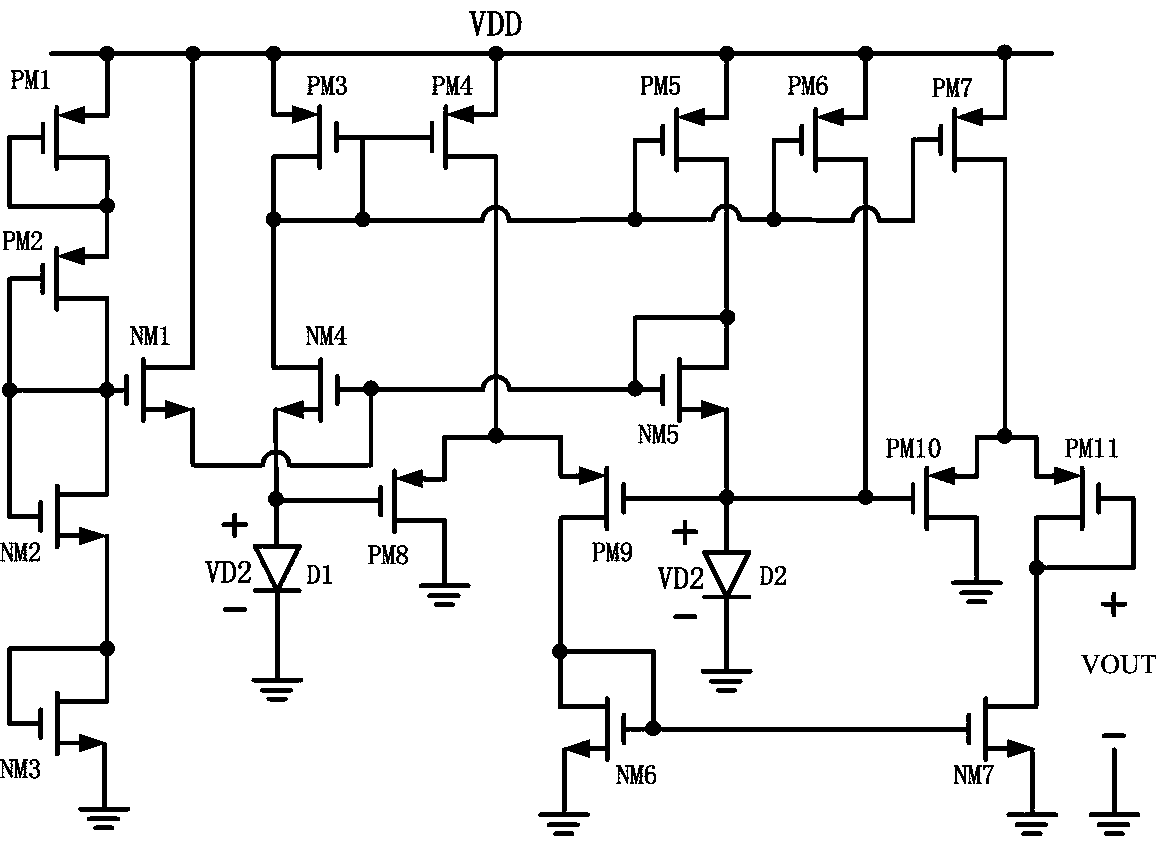

Full CMOS reference circuit

A reference circuit and reference voltage technology, applied in the direction of adjusting electrical variables, control/regulation systems, instruments, etc., can solve problems such as non-subordination

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0011] combine figure 1 As shown, in the following embodiments, the full CMOS reference circuit at least includes: a start-up circuit for starting the reference circuit; a core reference circuit adopts a self-bias structure, and the accuracy of the reference voltage generated is It is also very high and less affected by temperature. Since no resistors are used in the entire circuit, the overall circuit area is also very small.

[0012] The start-up circuit is composed of a first PMOS transistor PM1, a second PMOS transistor PM2, a first NMOS transistor NM1, a second NMOS transistor NM2 and a third NMOS transistor NM3; the PM1 transistor, PM2 transistor, NM2 transistor and NM3 transistor are all diodes In the connection method, when the power supply voltage is applied to the circuit and the core reference circuit is not started, the NM1 tube is turned on, the gate voltage of the NM4 tube is pulled up, the NM4 tube is turned on, and the core reference circuit is started; when th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More