Implementation device of privacy amplification algorithm based on FPGA + RISC-V

A RISC-V and privacy amplification technology, which is applied in the field of implementation devices for privacy amplification algorithms, can solve the problems of insufficient calculation speed of large-scale matrices, and does not support adjustable speed, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

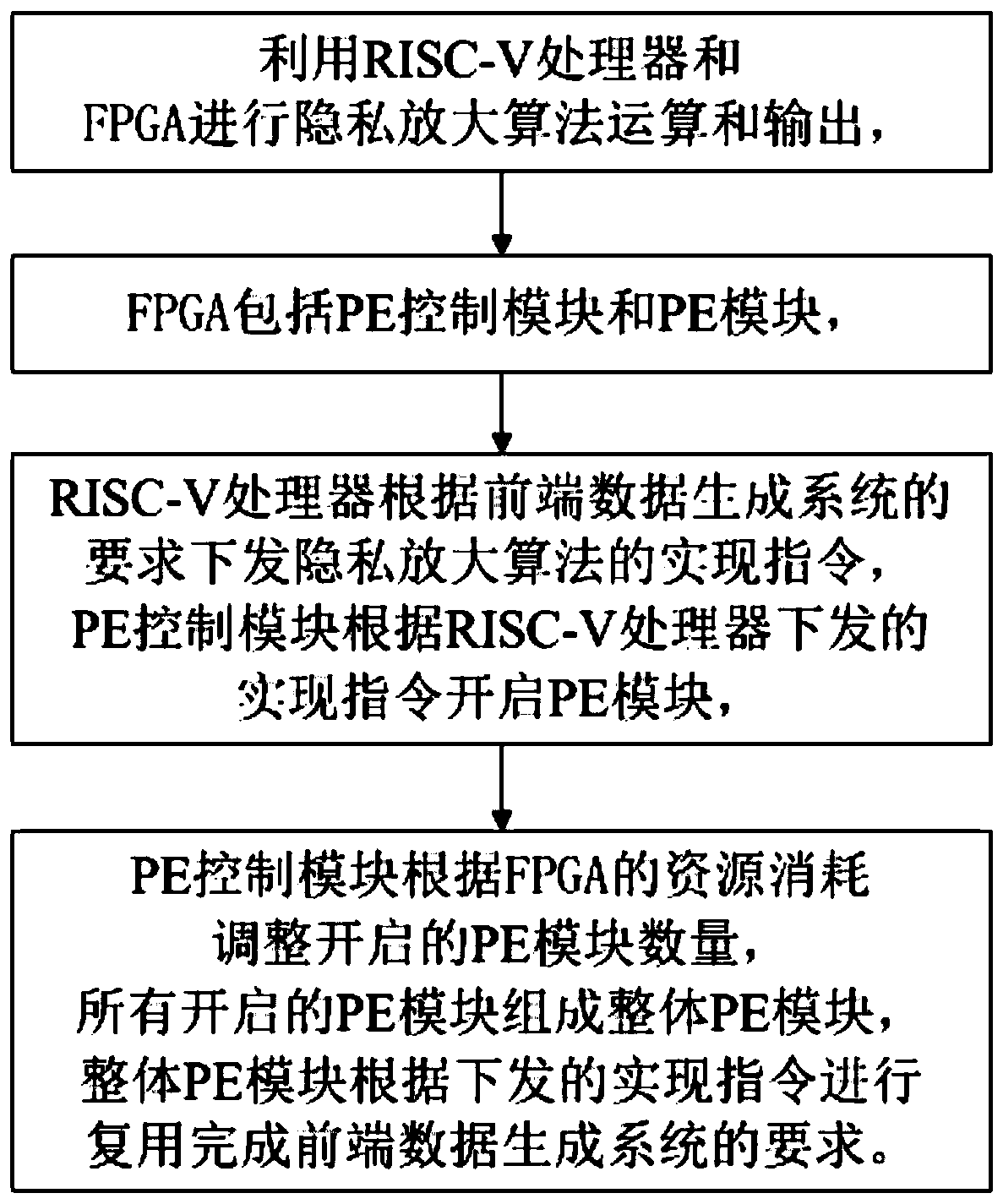

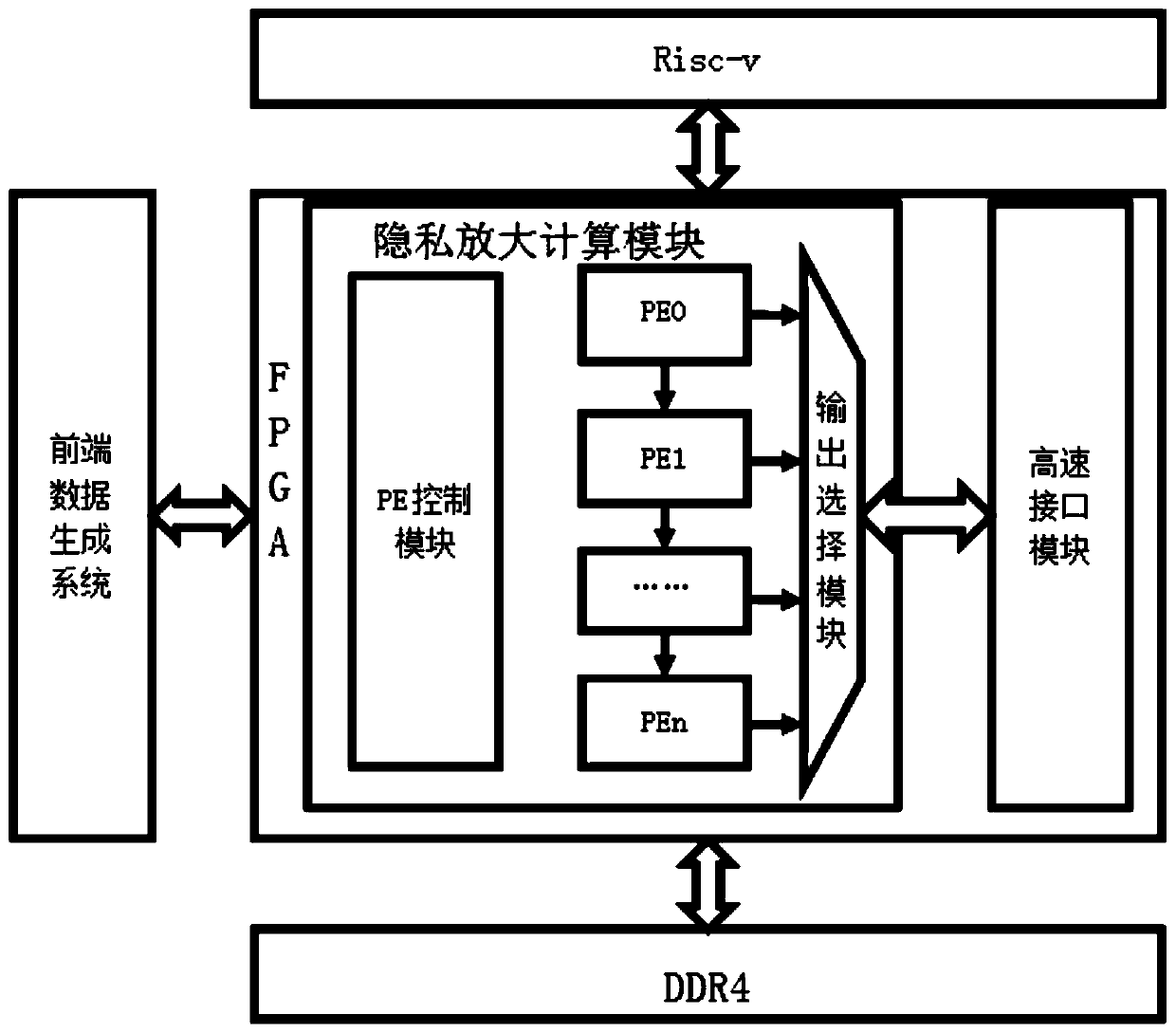

[0021] The invention provides a device for implementing a privacy amplification algorithm based on FPGA+RISC-V, which includes a RISC-V processor and an FPGA. The FPGA includes a privacy amplification calculation module, and the privacy amplification calculation module includes a PE control module and a PE module,

[0022] The RISC-V processor issues the implementation instructions of the privacy amplification algorithm according to the requirements of the front-end data generation system, and the PE control module in the privacy amplification calculation module turns on the PE module according to the implementation instructions issued by the RISC-V processor, and according to the resources of the FPGA Consume and adjust the number of opened PE modules. All opened PE modules form an overall PE module. The overall PE module is multiplexed according to the issued implementation instructions to complete the requirements of the front-end data generation system.

[0023] At the same time...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More