Output circuit

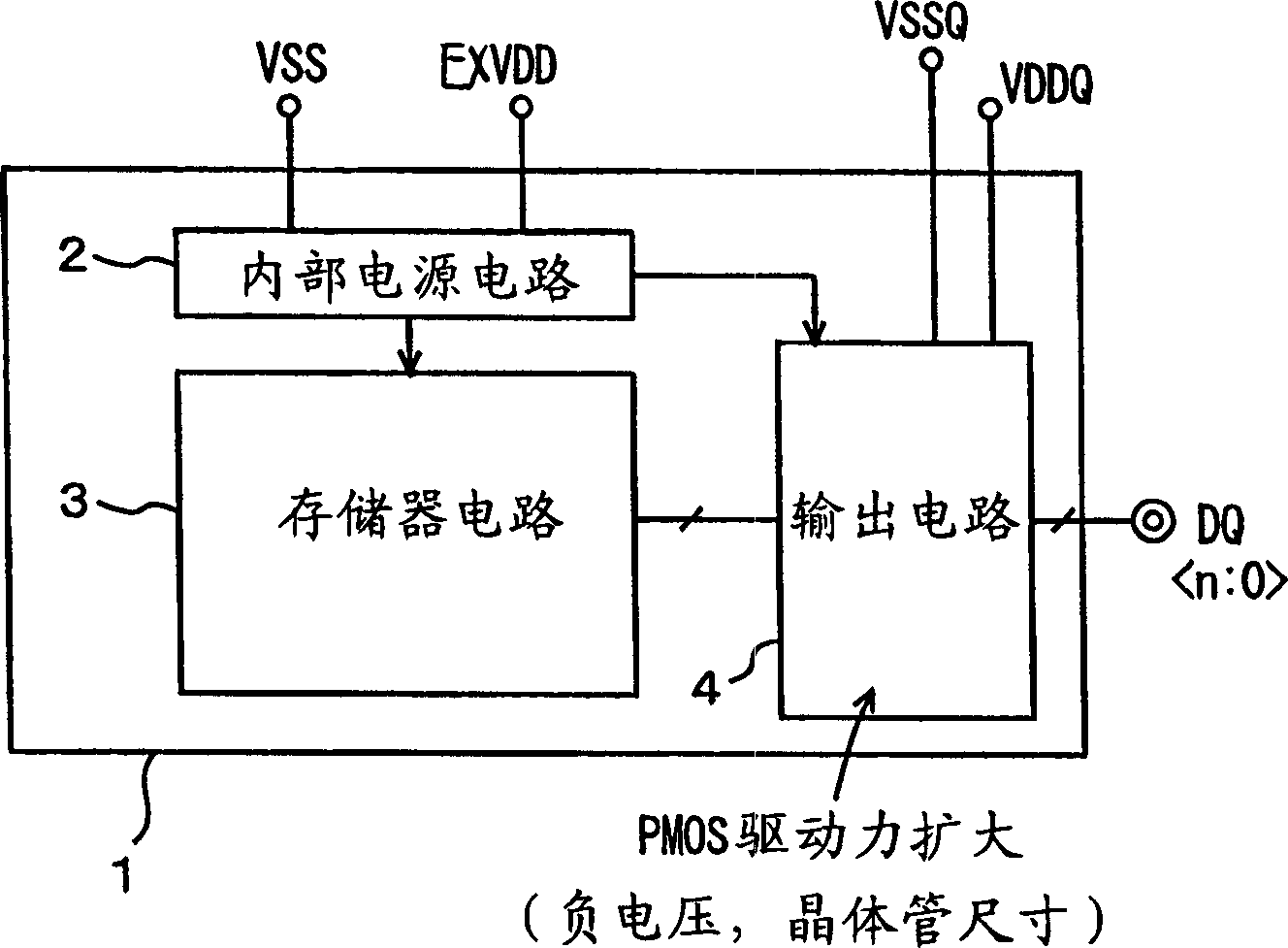

A technology for outputting circuits and outputting power, which is applied in logic circuit connection/interface layout, electronic switches, electrical components, etc., and can solve problems such as inability to operate semiconductor storage devices at high speed, reduction of current drive capability, and acceleration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

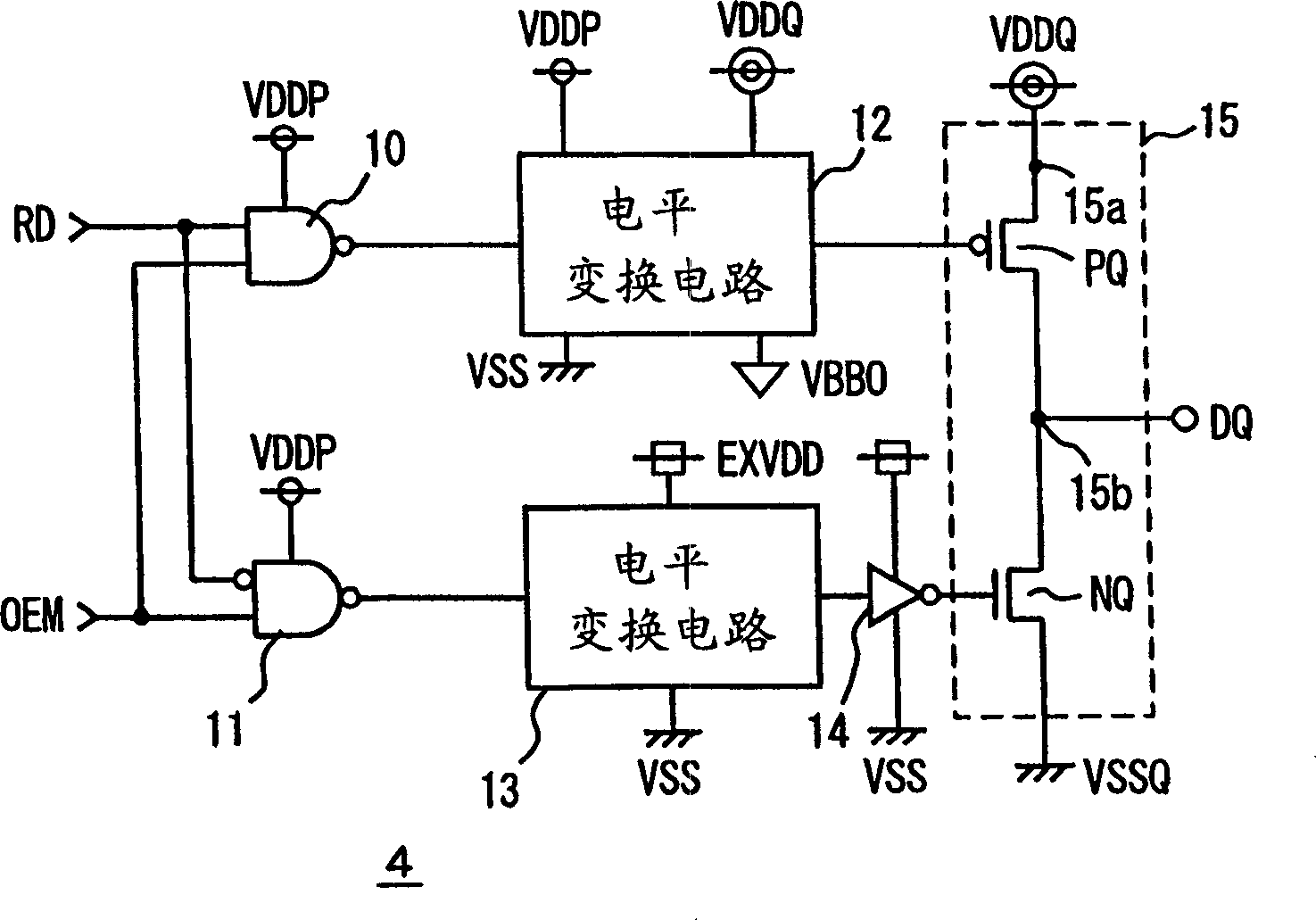

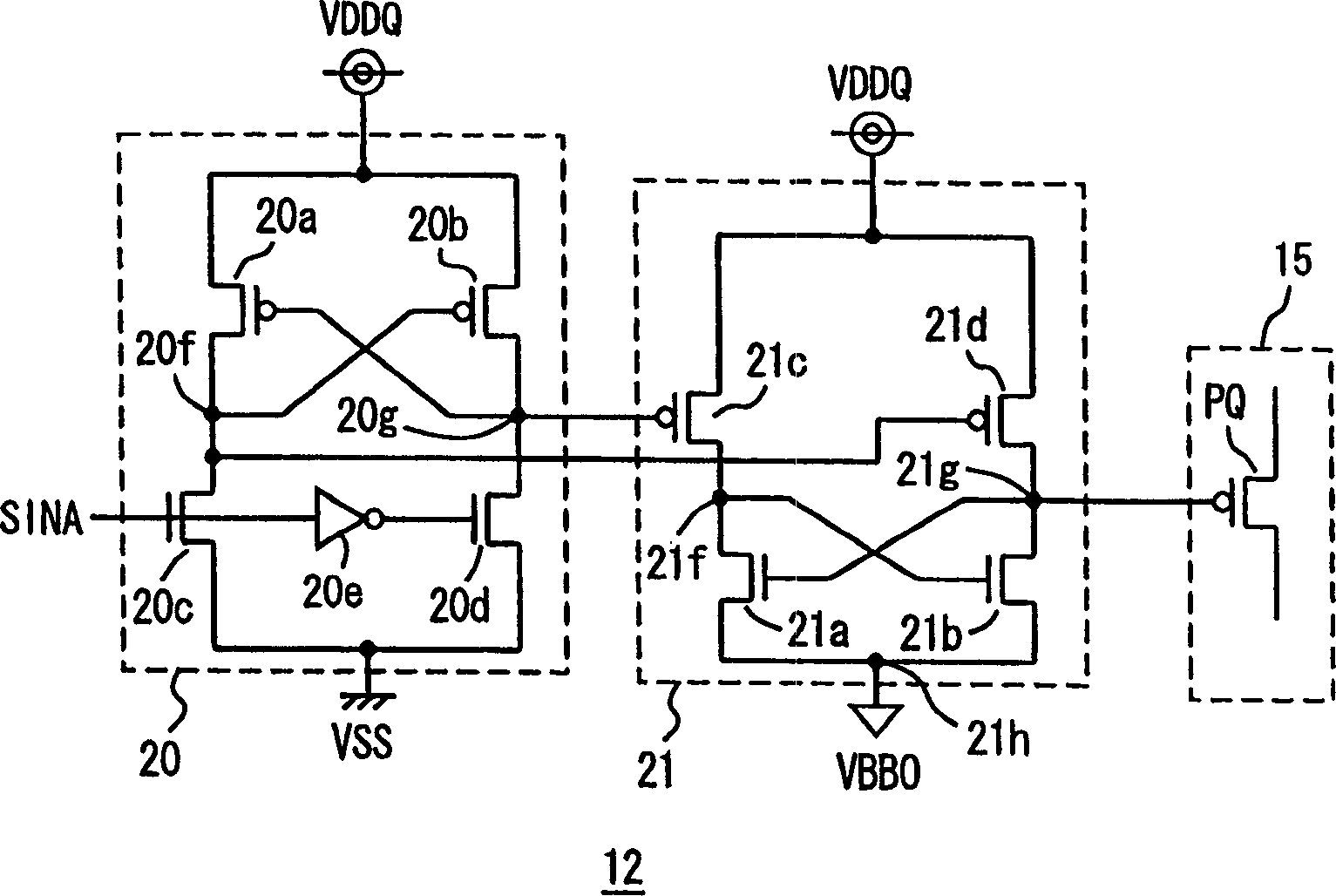

[0059] figure 2 is a diagram schematically showing the configuration of the output circuit 4 according to Embodiment 1 of the present invention. figure 2 Among them, the output circuit 4 includes a NAND circuit 10 that receives the internal read data RD read from the memory circuit 3 and the output permission signal OEM from the output control circuit included in the memory circuit 3, receives the internal read data RD and the output permission signal The gate circuit 11 of the OEM, the level conversion circuit 12 that converts the output signal of the NAND circuit 10 into a signal varying between the output power supply voltage VDDQ and the negative voltage VBB0, and converts the output signal of the gate circuit 11 into an output signal at the external power supply voltage EXVDD A level conversion circuit 13 for signals varying between ground voltage VSS, an inverter 14 receiving the output signal of the level conversion circuit 13, and a device for generating output data ...

Embodiment 2

[0088] Figure 5 is a diagram schematically showing the configuration of an output circuit according to Embodiment 2 of the present invention. Figure 5 In, the circuit portion for driving the pull-down N-channel MOS transistor NQ of the output buffer circuit 15 is the same as figure 2 The structures shown are the same, and the corresponding parts are given the same reference numbers, and the detailed description thereof is omitted.

[0089] Should Figure 5 In the output circuit 4 shown, in order to drive the gate of the pull-up P-channel MOS transistor PQ included in the output buffer circuit 15 to a negative voltage level, a charge pump operation using a capacitor is performed (capacitive coupling).

[0090] which is, Figure 5 Among them, the output circuit 4 includes a level conversion circuit 30 for converting the amplitude of the output signal of the NAND circuit 10 into an output power supply voltage VDDQ level, an inverter 31 for inverting the output signal of the...

Embodiment 3

[0110] Figure 7 is a diagram schematically showing the configuration of an output circuit according to Embodiment 3 of the present invention. Figure 7 In the output circuit 4, the structure of the circuit part that drives the N-channel MOS transistor NQ included in the output buffer circuit 5 is the same as figure 2 The structures of the output circuits shown are the same, and the corresponding parts are given the same reference numbers, and the detailed description thereof is omitted.

[0111] Should Figure 7 In the output circuit 4 shown, a capacitive element 41 is provided between the gate of the pull-up P-channel MOS transistor PQ of the output buffer circuit 5 and the output of the NAND circuit 10 . In order to realize the charge pump operation of the capacitive element 41, the output circuit 4 further includes a level conversion circuit 40 that converts the amplitude of the output signal of the NAND circuit 10 into the amplitude of the output power supply voltage V...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More